#### CHAPTER 1 GENERAL

#### 1.1 Introduction

The  $\mu$ PD30412, 30412L (VR4400MC) processor supports interfaces to secondary cache, system interface, and boot time mode control. This document describes the connection and operation of each of these interfaces.

Remark Please refer also to the following documents when you use this manual.

VR4000<sup>TM</sup>, VR4400<sup>TM</sup> USER'S MANUAL ARCHITECTURE (Document number IEU-1344)

VR4000PC<sup>TM</sup>, VR4400PC<sup>TM</sup> USER'S MANUAL HARDWARE (Document number IEU-1329)

VR4000SC<sup>TM</sup>, VR4400SC<sup>TM</sup> USER'S MANUAL HARDWARE (Document number IEU-1331)

#### 1.2 Operation Fundamentals

A word is the basic data element of the Vn4400MC processor. A word is a thirty-two bit data element. A sixty-four bit data element is referred to as a double word, a sixteen bit data element is referred to as a half word and an eight bit data element is referred to as a byte.

#### 1.3 Clocking Fundamentals

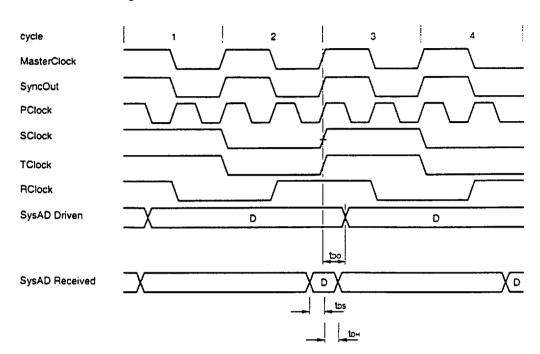

The Va4400MC processor bases all clocking methodology on the single clock input MasterClock at the desired operational frequency for the processor. MasterClock is multiplied by two internally, using phase locked loop techniques, to generate the processor internal clock, PClock. PClock is used by the processor's execution units, and to sequence the secondary cache interface. All secondary cache interface transaction protocol and parameters are specified in terms of PCycles, where a PCycle is the period of PClock or half the period of MasterClock.

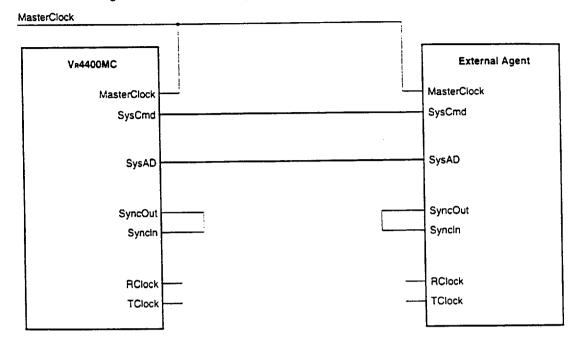

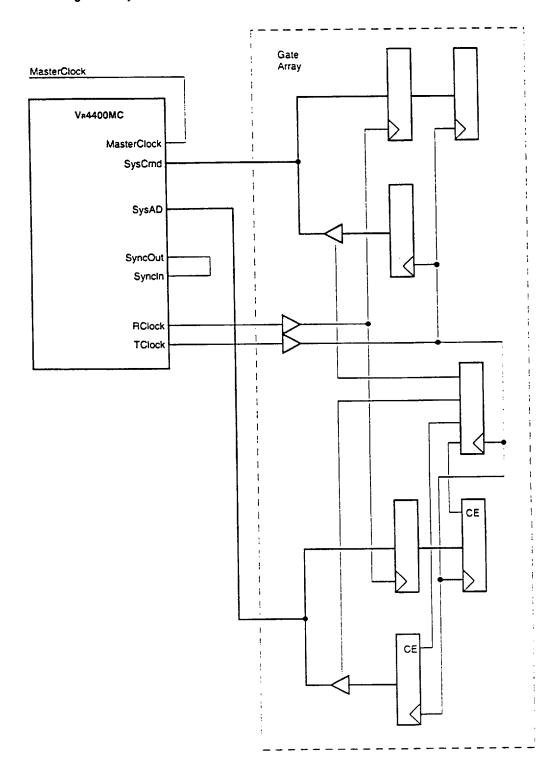

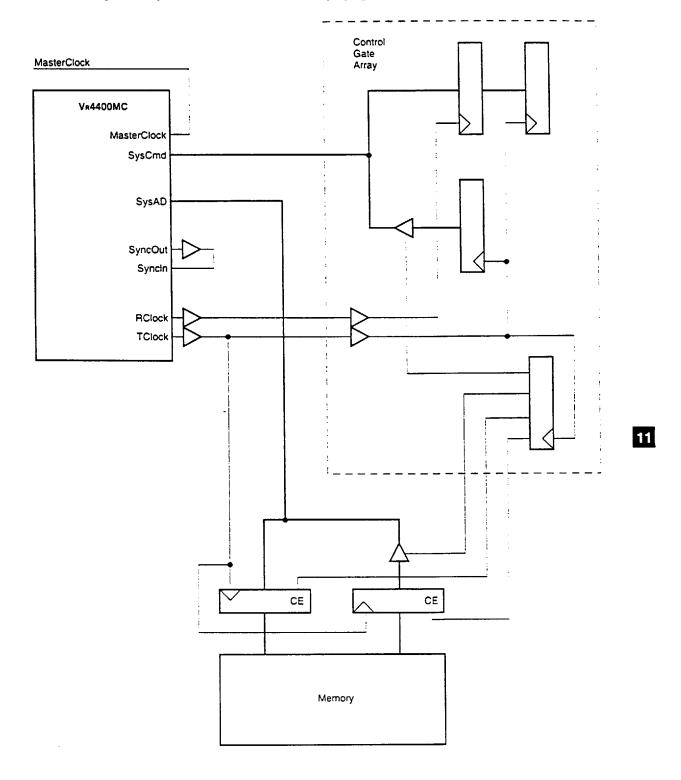

PClock is divided by a programmable divisor to generate the processor internal clock, SClock, and the system interface clocks, TClock and RClock. SClock is used by the processor to clock all internal registers that sample system interface inputs and drive system interface outputs. TClock and RClock are driven off the processor for use by an external agent. The PClock to SClock divisor is programmed via the boot time mode control interface as described in the Boot Time Mode Control Interface section. All system interface transaction protocol and parameters are specified in terms of SCycles, where a SCycle is the period of SClock, unless otherwise specified.

See CHAPTER 11 CLOCKING for further details on the clocking behavior of the VR4400MC processor.

■ 6427525 BD89668 90T ■

7

# ★ 1.4 Ordering Information

|                 |                                       | Max. Operating      | <b>.</b> .  |

|-----------------|---------------------------------------|---------------------|-------------|

| Part Number     | Dockoon                               | Frequency (MHz)     | Supply      |

| Part Number     | Package                               | (Internal/External) | Voltage (V) |

| μPD30412RJ-50   | 447-pin ceramic PGA (metal sealed)    | 100/50              | 5           |

| μPD30412RJ-67   | 447-pin ceramic PGA (metal sealed)    | 133/67              | 5           |

| μPD30412RJ-75   | 447-pin ceramic PGA (metal sealed)    | 150/75              | 5           |

| μPD30412LRJ-75  | 447-pin ceramic PGA (seam welded)     | 150/75              | 3.3         |

| μPD30412LRJ-200 | 447-pin ceramic PGA (seam welded)     | 200/100             | 3.45        |

| μPD30412LRJ-250 | 447-pin ceramic PGA (seam welded)     | 250/125             | 3.45        |

| μPD30412RP-50   | 447-pin ceramic PGA (with metal slug) | 100/50              | 5           |

| μPD30412RP-67   | 447-pin ceramic PGA (with metal slug) | 133/67              | 5           |

| μPD30412RP-75   | 447-pin ceramic PGA (with metal slug) | 150/75              | 5           |

| μPD30412LRP-75  | 447-pin ceramic PGA (with metal slug) | 150/75              | 3.3         |

| μPD30412LRP-200 | 447-pin ceramic PGA (with metal slug) | 200/100             | 3.45        |

| μPD30412LRP-250 | 447-pin ceramic PGA (with metal slug) | 250/125             | 3.45        |

### 1

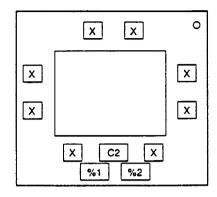

# 1.5 Pin Configuration

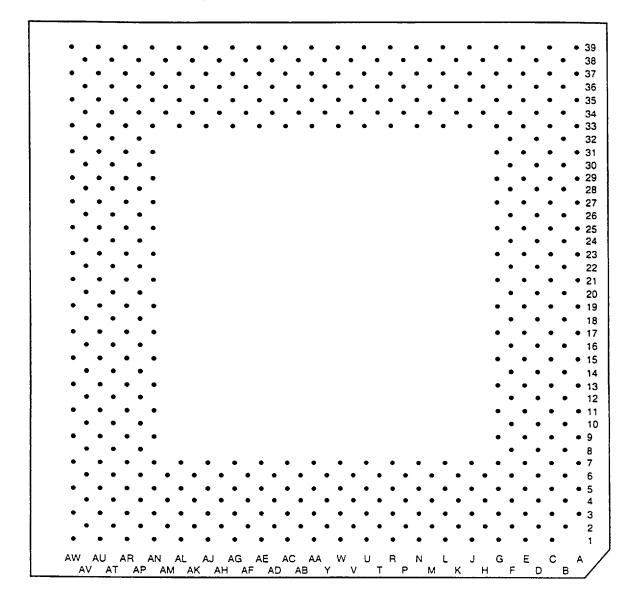

Fig. 1-1 Pin Configuration (Bottom View)

Table 1-1 Pin Configuration (1/3)

| No.  | Name        | No.  | Name     | No.  | Name     | No.  | Name     |

|------|-------------|------|----------|------|----------|------|----------|

| AW37 | ColdReset   | AA3  | SCAddr11 | G25  | SCData10 | AF4  | SCData48 |

| AV2  | ExtRqst     | W3   | SCAddr12 | E29  | SCData11 | AJ3  | SCData49 |

| C39  | Fault       | Y6   | SCaddr13 | G31  | SCData12 | AJ7  | SCData50 |

| AV24 | Open Note   | W5   | SCAddr14 | C35  | SCData13 | AP8  | SCData51 |

| AV20 | Voo         | W7   | SCAddr15 | K36  | SCData14 | AT10 | SCData52 |

| AV32 | IOIn        | W1   | SCAddr16 | N35  | SCData15 | AR13 | SCData53 |

| AV28 | IOOut .     | U3   | SCAddr17 | AE3  | SCData16 | AR15 | SCData54 |

| AL1  | Int0        | AN7  | SCAddr0W | AG5  | SCData17 | AT18 | SCData55 |

| AA35 | ÍvdAck      | AN5  | SCAddr0X | AK4  | SCData18 | AU23 | SCData56 |

| AA39 | lvdErr      | AM6  | SCAddr0Y | AN9  | SCData19 | AT26 | SCData57 |

| U39  | JTCK        | AL7  | SCAddr0Z | AU9  | SCData20 | AR27 | SCData58 |

| N39  | JTDI        | M6   | SCDCS    | AN13 | SCData21 | AN29 | SCData59 |

| J39  | JTDO        | G19  | SCDChk0  | AT14 | SCData22 | AP32 | SCData60 |

| G37  | JTMS        | T34  | SCDChk1  | AR17 | SCData23 | AN35 | SCData61 |

| AA37 | MasterClock | AP20 | SCDChk2  | AT22 | SCData24 | AJ35 | SCData62 |

| AJ39 | MasterOut   | AD34 | SCDChk3  | AU25 | SCData25 | AE33 | SCData63 |

| B8   | ModeClock   | C19  | SCDChk4  | AN27 | SCData26 | V4   | SCData64 |

| AV8  | Modeln      | R37  | SCDChk5  | AR29 | SCData27 | R5   | SCData65 |

| AV16 | NMI         | AU19 | SCDChk6  | AN31 | SCData28 | N5   | SCData66 |

| AM34 | RClock0     | AE37 | SCDChk7  | AR35 | SCData29 | E5   | SCData67 |

| AL33 | RClock1     | C17  | SCDChk8  | AK36 | SCData30 | G9   | SCData68 |

| AW7  | RdRdy       | N37  | SCDChk9  | AG35 | SCData31 | E11  | SCData69 |

| AV12 | Release     | AU17 | SCDChk10 | Т6   | SCData32 | G13  | SCData70 |

| AU39 | Reset       | AG37 | SCDChk11 | L3   | SCData33 | D14  | SCData71 |

| Y2   | Open Note   | E19  | SCDChk12 | L7   | SCData34 | C21  | SCData72 |

| U5   | SCAPar0     | R35  | SCDChk13 | E7   | SCData35 | D22  | SCData73 |

| U1   | SCAPar1     | AR19 | SCDChk14 | G11  | SCData36 | E25  | SCData74 |

| P4   | SCAPar2     | AE35 | SCDChk15 | E13  | SCData37 | G27  | SCData75 |

| AL5  | SCAddr1     | R3   | SCData0  | E15  | SCData38 | C31  | SCData76 |

| AG1  | SCAddr2     | R7   | SCData1  | G17  | SCData39 | F32  | SCData77 |

| AE7  | SCAddr3     | L5   | SCData2  | C23  | SCData40 | J35  | SCData78 |

| AC1  | SCAddr4     | F8   | SCData3  | F24  | SCData41 | M34  | SCData79 |

| AC5  | SCAddr5     | C9   | SCData4  | E27  | SCData42 | AC7  | SCData80 |

| AC3  | SCAddr6     | F12  | SCData5  | D30  | SCData43 | AE5  | SCData81 |

| AA1  | SCAddr7     | G15  | SCData6  | C33  | SCData44 | AG7  | SCData82 |

| AB4  | SCAddr8     | E17  | SCData7  | E35  | SCData45 | AR5  | SCData83 |

| AA5  | SCAddr9     | G21  | SCData8  | L35  | SCData46 | AR9  | SCData84 |

| AA7  | SCAddr10    | C25  | SCData9  | R33  | SCData47 | AR11 | SCData85 |

Note Leave unconnected.

Remark See CHAPTER 15 PIN SUMMARY for pin functions.

Table 1-1 Pin Configuration (2/3)

| No.  | Name      | No.  | Name      | No.  | Name    | No.  | Name    |

|------|-----------|------|-----------|------|---------|------|---------|

| AN15 | SCData86  | AL37 | SCData126 | U33  | Status0 | AM38 | SysAD30 |

| AP16 | SCData87  | AG33 | SCData127 | U35  | Status1 | AH38 | SysAD31 |

| AU21 | SCData88  | N1   | SCOE      | V36  | Status2 | R1   | SysAD32 |

| AN23 | SCData89  | J1   | SCTCS     | W35  | Status3 | L1   | SysAD33 |

| AR25 | SCData90  | AN21 | SCTChk0   | W37  | Status4 | H2   | SysAD34 |

| AP28 | SCData91  | AN19 | SCTChk1   | AC37 | Status5 | E1   | SysAD35 |

| AU31 | SCData92  | AU15 | SCTChk2   | AC35 | Status6 | C3   | SysAD36 |

| AR33 | SCData93  | AP12 | SCTChk3   | AC33 | Status7 | A5   | SysAD37 |

| AL35 | SCData94  | AU7  | SCTChk4   | W39  | Syncin  | A11  | SysAD38 |

| AH34 | SCData95  | AR7  | SCTChk5   | AN39 | SyncOut | A15  | SysAD39 |

| U7   | SCData96  | AH6  | SCTChk6   | T2   | SysAD0  | A23  | SysAD40 |

| N3   | SCData97  | K4   | SCTag0    | M2   | SysAD1  | A27  | SysAD41 |

| N7   | SCData98  | G7   | SCTag1    | J3   | SysAD2  | A31  | SysAD42 |

| C5   | SCData99  | C7   | SCTag2    | G3   | SysAD3  | A35  | SysAD43 |

| E9   | SCData100 | D10  | SCTag3    | C1   | SysAD4  | C37  | SysAD44 |

| C11  | SCData101 | C15  | SCTag4    | A3   | SysAD5  | E39  | SysAD45 |

| C13  | SCData102 | D18  | SCTag5    | A9   | SysADf  | H38  | SysAD46 |

| F16  | SCData103 | F20  | SCTag6    | A13  | SysAD7  | M38  | SysAD47 |

| E21  | SCData104 | E23  | SCTag7    | A21  | SysAD8  | AE1  | SysAD48 |

| G23  | SCData105 | D26  | SCTag8    | A25  | SysAD9  | AJ1  | SysAD49 |

| C27  | SCData106 | C29  | SCTag9    | A29  | SysAD10 | AM2  | SysAD50 |

| F28  | SCData107 | G29  | SCTag10   | A33  | SysAD11 | AR1  | SysAD51 |

| E31  | SCData108 | E33  | SCTag11   | B38  | SysAD12 | AU3  | SysAD52 |

| G33  | SCData109 | G35  | SCTag12   | E37  | SysAD13 | AW5  | SysAD53 |

| J37  | SCData110 | L33  | SCTag13   | G39  | SysAD14 | AW11 | SysAD54 |

| N33  | SCData111 | L37  | SCTag14   | L39  | SysAD15 | AW15 | SysAD55 |

| AD6  | SCData112 | P36  | SCTag15   | AD2  | SysAD16 | AW23 | SysAD56 |

| AG3  | SCData113 | AF36 | SCTag16   | AH2  | SysAD17 | AW27 | SysAD57 |

| AJ5  | SCData114 | AJ37 | SCTag17   | AL3  | SysAD18 | AW31 | SysAD58 |

| AU5  | SCData115 | AJ33 | SCTag18   | AN3  | SysAD19 | AW35 | SysAD59 |

| AN11 | SCData116 | AN37 | SCTag19   | AU1  | SysAD20 | AU37 | SysAD60 |

| AU11 | SCData117 | AU35 | SCTag20   | AW3  | SysAD21 | AR39 | SysAD61 |

| AU13 | SCData118 | AR31 | SCTag21   | AW9  | SysAD22 | AL39 | SysAD62 |

| AN17 | SCData119 | AU29 | SCTag22   | AW13 | SysAD23 | AG39 | SysAD63 |

| AR21 | SCData120 | AN25 | SCTag23   | AW21 | SysAD24 | A17  | SysADC0 |

| AP24 | SCData121 | AR23 | SCTag24   | AW25 | SysAD25 | R39  | SysADC1 |

| AU27 | SCData122 | J5   | SCWrW     | AW29 | SysAD26 | AW17 | SysADC2 |

| AT30 | SCData123 | J7   | SCWrX     | AW33 | SysAD27 | AD38 | SysADC3 |

| AU33 | SCData124 | Н6   | SCWrY     | AV38 | SysAD28 | A19  | SysADC4 |

| AN33 | SCData125 | G5   | SCWrZ     | AR37 | SysAD29 | T38  | SysADC5 |

Remark See CHAPTER 15 PIN SUMMARY for pin functions.

Table 1-1 Pin Configuration (3/3)

| No.  | Name     | No.  | Name            | No.  | Name | No.  | Name |

|------|----------|------|-----------------|------|------|------|------|

| AW19 | SysADC6  | H36  | Voo             | B22  | Gnd  | AP30 | Gnd  |

| AC39 | SysADC7  | K6   | V <sub>DD</sub> | B30  | Gnd  | AP34 | Gnd  |

| G1   | SysCmd0  | K38  | Vpo             | B36  | Gnd  | AP36 | Gnd  |

| E3   | SysCmd1  | P2   | Voo             | D2   | Gnd  | AT2  | Gnd  |

| B2   | SysCmd2  | P34  | Voo             | D6   | Gnd  | AT6  | Gnd  |

| B12  | SysCmd3  | T4   | Voo             | D12  | Gnd  | AT12 | Gnd  |

| B16  | SysCmd4  | T36  | Voo             | D20  | Gnd  | AT20 | Gnd  |

| B20  | SysCmd5  | V6   | Voo             | D28  | Gnd  | AT28 | Gnd  |

| B24  | SysCmd6  | V38  | Voo             | D34  | Gnd  | AT34 | Gnd  |

| B28  | SysCmd7  | Y38  | Voo             | D38  | Gnd  | AT38 | Gnd  |

| B32  | SysCmd8  | AB2  | Von             | F4   | Gnd  | AV4  | Gnd  |

| A37  | SysCmdP  | AB34 | Voo             | F6   | Gnd  | AV10 | Gnd  |

| H34  | TClock0  | AD4  | Voo             | F10  | Gnd  | AV18 | Gnd  |

| J33  | TClock1  | AD36 | Voo             | F18  | Gnd  | AV26 | Gnd  |

| AE39 | VppOk    | AF6  | Voo             | F26  | Gnd  | AV36 | Gnd  |

| AN1  | Validln  | AF38 | Voo             | F34  | Gnd  |      |      |

| AR3  | ValidOut | AK2  | Voo             | F36  | Gnd  |      |      |

| A7   | WrRdy    | AK34 | Voo             | K2   | Gnd  |      |      |

| W33  | VooSense | AM4  | Voo             | K34  | Gnd  |      |      |

| U37  | GndSense | AM36 | Voo             | M4   | Gnd  |      |      |

| AA33 | VooP     | AP2  | Voo             | M36  | Gnd  |      |      |

| Y34  | GndP     | AP10 | Voo             | P6   | Gnd  |      |      |

| A39  | Voo      | AP18 | Voo             | P38  | Gnd  |      |      |

| B6   | Voo      | AP26 | Voo             | V2   | Gnd  |      |      |

| B10  | Voo      | AP38 | Voo             | V34  | Gnd  |      |      |

| B18  | Voo      | AT4  | Voo             | Y4   | Gnd  |      |      |

| B26  | Voo      | AT8  | Voo             | Y36  | Gnd  |      |      |

| B34  | Voo      | AT16 | Voo             | AB6  | Gnd  |      |      |

| D4   | Vaa      | AT24 | Voo             | AB36 | Gnd  |      |      |

| D8   | Vaa      | AT32 | Voo             | AB38 | Gnd  |      |      |

| D16  | Voo      | AT36 | Voo             | AF2  | Gnd  |      |      |

| D24  | Voo      | AV6  | Voo             | AF34 | Gnd  |      |      |

| D32  | Voo      | AV14 | Voo             | AH4  | Gnd  |      |      |

| D36  | VDD      | AV22 | VDD             | AH36 | Gnd  |      |      |

| F2   | Voo      | AV30 | Vdd             | AK6  | Gnd  |      |      |

| F14  | Vaa      | AV34 | Voo             | AK38 | Gnd  |      |      |

| F22  | Vco      | AW1  | Voo             | AP4  | Gnd  |      |      |

| F30  | Voo      | AW39 | Voo             | AP6  | Gnd  |      |      |

| F38  | Voo      | B4   | Gnd             | AP14 | Gnd  |      |      |

| H4   | Vασ      | B14  | Gnd             | AP22 | Gnd  |      |      |

Remark See CHAPTER 15 PIN SUMMARY for pin functions.

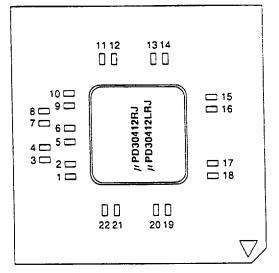

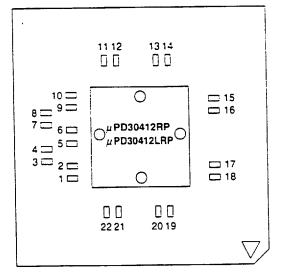

447-pin ceramic PGA (metal sealed) 447-pin ceramic PGA (seam welded) 447-pin ceramic PGA (with metal slug)

Caution The voltage of the metal seal on the top of the package is equal to VDD.

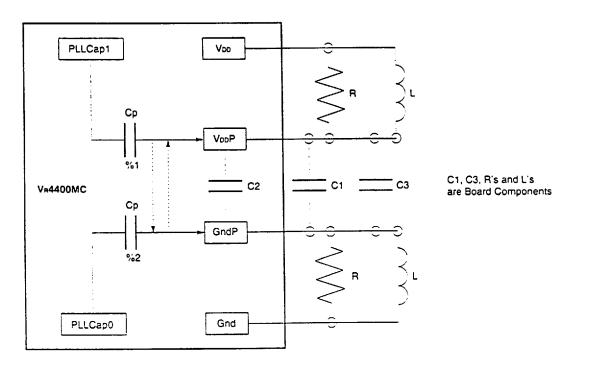

Table 1-2 Pad Configuration

| No. | Name    | No. | Name    | No. | Name | No. | Name |

|-----|---------|-----|---------|-----|------|-----|------|

| 1   | Vod     | 7   | VooP    | 13  | VDD  | 19  | Voo  |

| 2   | Gnd     | 8   | PLLCap1 | 14  | Gnd  | 20  | Gnd  |

| 3   | PLLCap0 | 9   | Voo     | 15  | Voo  | 21  | Voo  |

| 4   | GndP    | 10  | Gnd     | 16  | Gnd  | 22  | Gnd  |

| 5   | GndP    | 11  | Voo     | 17  | Voo  |     |      |

| 6   | VooP    | 12  | Gnd     | 18  | Gnd  |     |      |

Table 1-3 Capacitance of Chip Capacitors

| Pads    | Capacitance [μF]    | Pads        | Capacitance [µF] |

|---------|---------------------|-------------|------------------|

| 1 – 2   | 0.1                 | 13 - 14     | 0.1              |

| 3 – 4   | 3 – 4 0.001 15 – 16 |             | 0.1              |

| 5 – 6   | 0.1                 | 17 – 18     | 0.1              |

| 7 – 8   | 0.001 19 – 20       |             | 0.1              |

| 9 – 10  | 0.1                 | 21 – 22 0.1 |                  |

| 11 - 12 | 0.1                 |             |                  |

Remark Chip capacitors are incorporated at delivery.

7

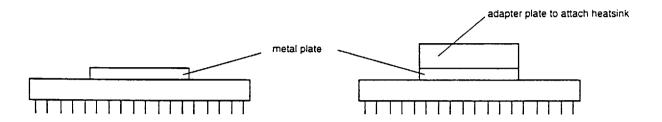

Fig. 1-3 Package Side View

447-pin ceramic PGA (metal sealed)

447-pin ceramic PGA (seam welded)

447-pin ceramic PGA (with metal slug)

#### CHAPTER 2 CACHE COHERENCY

The Vn4400MC processor manages its primary and secondary caches using a write back methodology, that is, stores write data into the caches, but a modified cache line is not written back to memory until the cache line is replaced, or until the cache line is exported or flushed from the secondary cache. When the contents of a cache line is not consistent with memory, it is said to be dirty. Many systems, in particular multiprocessor systems, or systems that employ input/output (IO) devices that are capable of direct memory access (DMA), may require the system to behave as if the caches are always consistent with memory and each other. Schemes for maintaining consistency between multiple write back caches or between write back caches and memory are referred to as cache coherency protocols.

The processor, in its secondary cache mode, provides a set of cache states and mechanisms for manipulating the contents and state of the cache that are sufficient to implement a variety of cache coherency protocols, both snoopy and directory based. In particular, the processor supports both the write invalidate and write update protocols simultaneously.

The coherency protocol for lines in the cache is controllable via bits in the translation look-aside buffer (TLB) on a per TLB page basis. Specifically, the TLB contains three bits per entry that control the coherency attributes of a page. The three bits are encoded to provide five possible coherency attributes per page, uncached, cacheable noncoherent, cacheable coherent exclusive (exclusive), cacheable coherent exclusive on write (sharable), and cacheable coherent update on write (update). A processor in the no-secondary cache mode supports only the uncached and noncoherent coherency attributes. The supported page attributes depend on the configuration of the processor as illustrated below.

Table 2-1 Allowed Page Attributes

| Configuration      | Uncached  | Cacheable<br>Noncoherent | Exclusive | Sharable  | Update    |

|--------------------|-----------|--------------------------|-----------|-----------|-----------|

| VR4000PC, VR4400PC | Supported | Supported                | NA        | NA        | NA        |

| VR4000SC, VR4400SC | Supported | Supported                | Supported | NA        | NA        |

| Va4400MC           | Supported | Supported                | Supported | Supported | Supported |

If a page has the coherency attribute uncached, the processor will issue a word or partial word read or write directly to main memory for any load or store to a location within that page. Lines within an uncached page are assumed never to be cache resident.

If the coherency attribute is sharable, the processor will issue a coherent block read for a load miss to a location within the page, and a coherent block read that requests exclusivity for a store miss to a location within the page. In most systems, coherent reads require snoops or directory checks to occur while noncoherent reads do not. A coherent read that requests exclusivity implies that the processor will function most efficiently if the requested cache line is returned to it in an exclusive state, but the processor will still perform correctly if the cache line is returned in a shared state. Cache lines within the page will be managed with a write invalidate protocol, that is the processor will issue an invalidate on a store hit to a shared cache line.

If the coherency attribute is update, the processor will issue a coherent block read for a load or store miss to a location within the page. Cache lines within the page will be managed with a write update protocol, that is the processor will issue an update on a store hit to a shared cache line.

If the coherency attribute is exclusive, the processor will issue a coherent block read that requests with a write invalidate protocol. Load linked store conditional instruction sequences must insure that the link location is not in a page managed with the exclusive coherency attribute.

If the coherency attribute is noncoherent, the processor will issue a noncoherent block read for a load or store miss to a location within the page.

The encoding of the coherency attributes in the TLB is specified in Va4000, Va4400 User's Manual Architecture. The behavior of the processor on load misses, store misses, and store hits to shared cache lines for each of the coherency attributes is summarized in Table 2-2 Coherency Attributes and Processor Behavior.

Table 2-2 Coherency Attributes and Processor Behavior

| <u>Attribute</u> | Load Miss               | Store Miss              | Store Hit Shared |

|------------------|-------------------------|-------------------------|------------------|

| uncached         | Main memory read        | Main memory write       | NA               |

| noncoherent      | Noncoherent read        | Noncoherent write       | Invalidate Note  |

| exclusive        | Coherent read exclusive | Coherent read exclusive | invalidate Note  |

| sharable         | Coherent read           | Coherent read exclusive | Invalidate       |

| update           | Coherent read           | Coherent read           | Update           |

The following sections describe the primary and secondary cache states provided by the processor, the cache state transitions performed by the processor during execution, and the mechanisms provided for an external agent to manipulate the state and contents of the primary and secondary cache.

#### 2.1 Cache States

The Vn4400MC maintains four primary cache states and five secondary cache states. The five secondary cache states are:

- Invalid

- Shared

- · Dirty shared

- Clean Exclusive

- · Dirty Exclusive

The four primary cache states are:

- Invalid

- Shared

- Clean Exclusive

- · Dirty Exclusive

The primary cache state shared corresponds to the secondary cache states shared and dirty shared.

The cache states and line attributes are illustrated below.

Table 2-3 Primary and Secondary Cache States and Line Attributes

(a) Primary Cache

| Cache State             | Line Attributes                                                                                                                                                                  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Invalid                 | The cache line does not contain valid information.                                                                                                                               |

| Valid                   | The cache line contains valid information (primary instruction cache only).                                                                                                      |

| Shared                  | The cache line contains valid information and may be present in another processor's cache. The cache line may or may not be consistent with memory, and may or may not be owned. |

| Glean Exclusive<br>(CE) | The cache line contains valid information and is not present in any other processor's cache. The cache line is consistent with memory and owned.                                 |

| Dirty Exclusive<br>(DE) | The cache line contains valid information and is not present in any other processor's cache. The cache line is inconsistent with memory and owned.                               |

#### (b) Secondary Cache

| Cache State             | Line Attributes                                                                                                                                                       |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Invalid                 | The cache line does not contain valid information.                                                                                                                    |

| Shared                  | The cache line contains valid information and may be present in another processor's cache. The cache line may or may not be consistent with memory, and is not owned. |

| Dirty Shared            | The cache line contains valid information and may be present in another processor's cache. The cache line is inconsistent with memory and owned.                      |

| Clean Exclusive<br>(CE) | The cache line contains valid information and is not present in any other processor's cache. The cache line is consistent with memory and owned.                      |

| Dirty Exclusive<br>(DE) | The cache line contains valid information and is not present in any other processor's cache. The cache line is inconsistent with memory and owned.                    |

The cache state of a line in the processor's primary or secondary cache indicates the validity, shared, dirty and ownership attributes of the cache line. A cache line that does not contain valid information must be marked invalid; a cache line in any state other than invalid contains valid information. A cache line that is present in more than one cache in the system is said to be shared and must be in one of the shared states. A cache line that is present in exactly one cache in the system is said to be exclusive and may be in one of the exclusive states. A cache line that contains data that is consistent with memory is said to be clean and may be in one of the clean states. A cache line that contains data that is not consistent with memory is said to be dirty and must be in one of the dirty states, or in the shared state. The processor has a concept of ownership for cache lines. When the processor is the owner of a particular cache line it is responsible for writing the cache line back to memory when it is replaced in the course of satisfying a cache miss, or during the execution of a cache instruction. A cache line is owned by the processor if its secondary cache state is dirty exclusive or dirty shared. Note that the cache states have no distinction between clean and dirty in the primary instruction cache, since the processor does not use a write back methodology in managing the primary instruction cache.

The primary and secondary cache states have been chosen to maintain all of the state information that the processor may need during execution in the primary cache, while maintaining all of the state information that an external agent may need to manage a cache coherency protocol in the secondary cache.

The allowed cache states for the primary cache are illustrated below.

Table 2-4 Allowed Primary and Secondary Cache States

| VR4000PC, VR4400PC |                                                                                                                                                                                                                                                                                                                                                                                       | VR4000SC, VR4400SC |                     | VR4400MC      |                   |            |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------|---------------|-------------------|------------|--|

| <u>  Ir</u>        | nstruction Cache                                                                                                                                                                                                                                                                                                                                                                      | Data Cache         | Instruction Cache   | Data Cache    | Instruction Cache | Data Cache |  |

| Primary            | Invalid                                                                                                                                                                                                                                                                                                                                                                               | Invalid            | Invalid             | Invalid       | Invalid           | Invalid    |  |

| Cache              | Valid                                                                                                                                                                                                                                                                                                                                                                                 | DE Note 1          | Valid Note 2        | CE            | Valid Note 2      | Shared     |  |

|                    |                                                                                                                                                                                                                                                                                                                                                                                       |                    |                     | DE            |                   | CE         |  |

|                    |                                                                                                                                                                                                                                                                                                                                                                                       |                    |                     |               |                   | DE         |  |

| Seconda            | ry N                                                                                                                                                                                                                                                                                                                                                                                  | Α                  | Inv                 | /alid         | Inv               | alid       |  |

| Cache              |                                                                                                                                                                                                                                                                                                                                                                                       |                    |                     | Œ             | Shared            |            |  |

|                    |                                                                                                                                                                                                                                                                                                                                                                                       |                    |                     | Œ             | Dirty S           | Shared     |  |

|                    |                                                                                                                                                                                                                                                                                                                                                                                       |                    |                     |               | C                 | E .        |  |

|                    |                                                                                                                                                                                                                                                                                                                                                                                       |                    |                     |               | D                 | E          |  |

| 2.                 | <ol> <li>Notes 1. Used with the W bit of the primary cache tag to indicate whether the current line is modified and must be written back to memory or secondary cache (W = 0 clean; W = 1 modified).</li> <li>The Valid state of the Primary Instruction Cache is mapped to any valid Secondary Cache states (Clean Exclusive, Dirty Exclusive, Shared, and Dirty Shared).</li> </ol> |                    |                     |               |                   |            |  |

| Remark             | DE: Dirty Exclusi                                                                                                                                                                                                                                                                                                                                                                     | ive, CE: Clea      | in Exclusive, NA: N | lot Available |                   |            |  |

### 2.2 Cache State Changes During Processor Execution

The initial state of a cache line is specified by an external agent when it supplies the cache line. During the course of processor execution, the processor may change the state of a cache line. The following events will cause changes to the state of the cache:

A store to the primary cache will write the data in the primary cache and change the W bit to one. The processor will also change the secondary cache state from a clean state to a dirty state without changing the data. The processor will not access the secondary cache on any subsequent stores to the same cache line in the primary cache.

A store to a shared cache line, that is a line marked shared in the primary cache and either shared or dirty shared in the secondary cache, will cause the processor to issue either an invalidate request or an update request depending on the coherency attribute in the TLB entry for the page that contains the cache line. Upon successful completion of an invalidate, the processor will complete the store and change the state of the cache line to dirty exclusive in both the primary and secondary caches. Upon successful completion of an update, the processor will complete the store and change the state of the cache line to shared in the primary cache and dirty shared in the secondary cache if dirty shared mode (ModeBit [3]) is enabled. Dirty shared mode is programmable via the boot time mode control interface. If dirty shared mode is not enabled, the state of the primary and secondary caches will be left unchanged after successful completion of an update.

#### 2.3 Cache Line Write Back

The processor will write a cache line back to memory when it is replaced, or written back to memory as the result of executing a cache instruction, if the cache line is in the state dirty exclusive or dirty shared in the secondary cache. When the processor writes a cache line back to memory, it does not ordinarily retain a copy of the cache line, and the state of the cache line is changed to invalid. However, if a cache line is written back to memory using the hit writeback cache instruction, the processor will retain a copy of the cache line. If the cache line is retained, the processor will change its state to clean exclusive if the secondary cache state was dirty exclusive before the write or shared if the seconday cache state was dirty shared before the write.

Whether or not the processor is retaining the line is signaled by the processor during a write.

### 2.4 Manipulation of the Caches by an External Agent

The VR4400MC provides mechanisms for an external agent to examine and manipulate the state and contents of the primary and secondary caches:

An external agent must specify the state in which data, supplied in response to a processor read request, is to be loaded into the processor's caches. Data may be loaded in any of the four valid secondary cache states. Data returned by the external agent must not be marked as invalid. The secondary cache state will be mapped to a primary cache state as described previously.

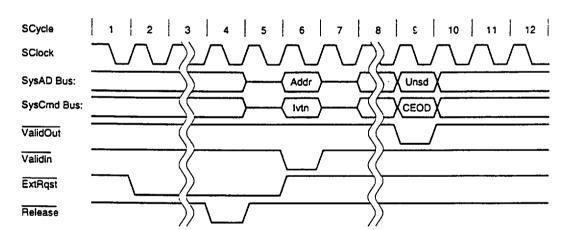

An external agent may issue a snoop request to the processor which will cause the processor to return the secondary cache state of the specified cache line. At the same time it will change the state of the specified cache line in both the primary and secondary caches, according to a state change function specified by the external agent, atomically with respect to the response to the snoop request.

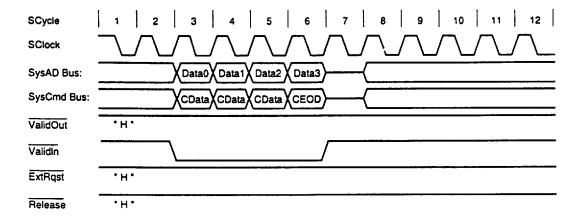

An external agent may issue an invalidate request or an update request to the processor. An invalidate request will cause the processor to change the state of the specified cache line to invalid in both the primary and secondary caches. An update request will cause the processor to write the specified data element into the specified cache line, and either change the state of the cache line to shared in both the primary and secondary caches, or leave the state of the cache line unchanged, depending on the nature of the update request. An external agent may issue updates, without changing the state of the cache line, to cache lines that are either in exclusive or shared states. If an update request is issued to the primary instruction cache, the secondary cache line and primary instruction cache line are updated.

An external agent may issue an intervention request which will cause the processor to return the secondary cache state of the specified cache line, and the contents of the specified secondary cache line under certain conditions related to the state of the cache line and the nature of the intervention request. At the same time the processor will change the state of the specified cache line in both the primary and secondary caches, according to a state change function specified by the external agent, atomically with respect to the response to the intervention request.

### 2.5 Cache Line Ownership

The Vn4400MC has a concept of ownership for cache lines. The ownership of a cache line is maintained as follows:

A processor assumes ownership of a cache line when the state of the cache line transitions to dirty shared or dirty exclusive. For responses to processor coherent read requests in which the data is returned with an indication that it must be loaded in the dirty shared or dirty exclusive state, the cache state is set at the completion of the read response when the last word of read response data is returned. Therefore, the processor will assume ownership of the cache line when the last word of read response data is returned.

The processor gives up ownership of a cache line when the state of the cache line transitions to invalid, shared, or clean exclusive. For processor write requests the state of the cache line will transition to invalid if the cache line is replaced, or clean exclusive or shared if the cache line is retained. In either case, the cache state transition will occur at the completion of the write request when the last word of write data is transmitted to the external agent. Therefore, the processor will give up ownership of the cache line when the last word of write data is transmitted to the external agent.

For external requests, other than read responses, any cache state change associated with the external request will occur at the completion of the external request and therefore any change of ownership resulting from the cache state change will occur at the completion of the external request.

### 2.6 Ordering Considerations

Many cache coherent multiprocessor systems must obey ordering constraints or stores to shared data such that they exhibit the same behavior as a uniprocessor system in a multi-programming environment. A multiprocessor system that exhibits such behavior is said to be strongly ordered.

An algorithm typically used to test for strong ordering is the following: Processor A does a store to location X at the same time processor B does a store to location Y. Locations X and Y have no particular relationship, i.e. they are not in the same cache line. Next processor A does a load from location Y at the same time that processor B does a load from location X. In order for the system to be strongly ordered either processor A must load the new value of Y, or processor B must load the new value of Y, or processor B must load the new value of Y and X respectively under all conditions. If both processors A and B load the old values of Y and X, under any conditions, the system does not meet the requirements for strong ordering. The algorithm to test for strong ordering is summarized below.

| Processor A          | Processor B          |

|----------------------|----------------------|

| Store to location X  | Store to location Y  |

| Load from location Y | Load from location X |

In order for the above test algorithm for strong ordering to succeed stores must have a global ordering in time; that is, every processor in the system must agree that either the store to location X preceded the store to location Y, or the store to location Y preceded the store to location X. If this global ordering is enforced the above test algorithm for strong ordering will succeed as described.

In a system employing the VR4400MC processor the requirements to achieve strong ordering translate to a need to precisely control when the processor restarts after completion of a processor coherence request with respect to cache state changes stemming from external coherence requests. Specifically, a system designer must make sure that any cache state changes, resulting from external coherence requests that occur before a processor coherence request, are completed before the processor is allowed to restart after completion of the processor coherence request.

The Vn4400MC processor obeys the following paradigms for restart after issuing a coherence request:

For coherent read requests, the processor will restart after the requested double word is transmitted to the processor if sub-block ordering is enabled or after the last word in the block is transmitted to the processor if sequential ordering is enabled, unless a processor invalidate or update request is unacknowledged. Any external requests that must be completed before the read is complete must be issued to the processor before the read response is issued.

For write requests, the processor will restart after the write request is complete, that is, after the last double word of data associated with the write request has been transmitted to the external agent unless a processor read request is pending or a processor invalidate or update request is unacknowledged.

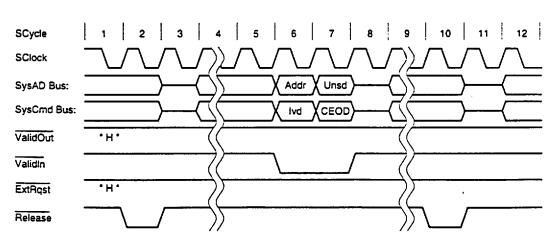

For invalidate and update requests, the processor will restart after the assertion of IvdAck or IvdErr unless a processor read request is pending or unless it is processing an external request when IvdAck or IvdErr is asserted. If IvdAck or IvdErr is asserted during or after the first cycle that the external agent asserts ExtRqst, the processor will accept the external request and complete any cache state changes associated with it before the processor restarts, otherwise, the processor will restart before beginning the external request. For any external requests that must be completed before a processor invalidate or update completes, the external agent must assert ExtRqst before or during the cycle that signal IvdAck or IvdErr is asserted.

# 3

### CHAPTER 3 SECONDARY CACHE INTERFACE

The VR4400MC is designed to operate with an external secondary cache. The secondary cache is accessible by the processor and to the system interface. The cache contains data, cache tags and cache line state bits.

# 3.1 Secondary Cache Overview

The Vn4400MC secondary cache is assumed to consist of one bank of industry standard static RAMs with output enables. The Vn4400MC secondary cache consists of quad-word (128 bit) wide data array and a 25-bit wide tag array. Check fields are added to both the data and tag arrays to improve data integrity. The secondary cache may be configured as joint or split instruction/data. The maximum secondary cache size is 4 Mbytes and the minimum secondary cache size is 128 Kbytes for joint and 256 Kbytes for split instruction/data. The secondary cache is direct-mapped, and is addressed with the lower part of the physical address.

### 3.2 Secondary Cache Interface Signal Description

The signals that connect the Va4400MC processor to its secondary cache are described in this section.

#### 3.2.1 Secondary Cache Interface Signal Summary

SCAddr0W:

| SCData(127:0): | (i/o) | A 128-bit bus used to read or write cache data from/to the secondary | cache. |

|----------------|-------|----------------------------------------------------------------------|--------|

| (.=).          | (" ") | The second to read or trine each control the economically            |        |

| SCDChk(15:0): | (i/o) A 16-bit bus which conveys two ECC fields that cover the upper or lower 64 bits of the |

|---------------|----------------------------------------------------------------------------------------------|

|               | SCData from/to the secndary cache.                                                           |

| SCTag(24:0): | (i/o) A 25-bit bus used to read or write cache tags from/to the secondary cache. |

|--------------|----------------------------------------------------------------------------------|

| 31           | ,                                                                                |

| SCAddr(17:1) | (0) | A 17-bit bus which addresses the secondary cache. |

|--------------|-----|---------------------------------------------------|

| SCAddr0Z:    | (o) | Bit 0 of the secondary cache address.             |

|           | (-/ |                                       |

|-----------|-----|---------------------------------------|

| SCAddr0Y: | (0) | Bit 0 of the secondary cache address. |

| SCAddr0X: | (0) | Bit 0 of the secondary cache address. |

| S | CAPar(2) | 7 bits: | SCWr, SCAddr(17:12) |

|---|----------|---------|---------------------|

| S | CAPar(1) | 7 bits: | SCDCS, SCAddr(11:6) |

| 9 | CAPar(0) | 7 hits: | SCTCS SCAddr(5:0)   |

(o) Bit 0 of the secondary cache address.

| SCOE:  | (o) | A signal which enables the outputs of the secondry cache RAMs. |

|--------|-----|----------------------------------------------------------------|

| 2011/2 |     |                                                                |

| SCWrZ: | (0) | Secondary cache write enable. |

|--------|-----|-------------------------------|

| SCWrY: | (0) | Secondary cache write enable. |

| SCWrX: | (0) | Secondary cache write enable. |

| SCWrW: | (0) | Secondary cache write enable. |

SCTCS: (o) A signal which enables the chip select pins of the secondary cache RAMs associated with SCTag and SCTChk.

#### 3.2.2 Details of Secondary Cache Interface Signals

The interface to the VR4400MC secondary cache is designed to maximize the efficiency of servicing primary cache misses. The width of the data portion of secondary cache interface is chosen to be 128 bits to support a data rate into the primary cache that is near the processor to primary cache bandwidth during normal operation. To assure that this bandwidth is maintained, each data, tag and check pin must be connected to only one static RAM device. The SCAddr bus, the SCOE signal, the SCDCS signal and the SCTCS drive a large number of static RAM devices, so one level of external buffering between the VR4400MC and the cache array is necessary.

The speed of the secondary cache interface is limited by buffered control signals. Critical control signals are duplicated to minimize this effect. The SCWr signal and SCAddr(0) are duplicated four times so that external buffering will not be required. When an 8-word (256-bit) primary cache line is used, these signals can be controlled significantly faster to reduce the time of the two back-to-back transfers. These duplicated control signals are specified to drive 11 parts each, so that a total of 44 RAM packages can be used in the cache array. This permits a cache design using 64 Kbyte by 4 bit or 256 Kbyte by 4 bit standard static RAMs. Other cache designs are also acceptable, for example a smaller cache design using 228 Kbyte by 8 bit static RAMs as it would present less load on the address pins and control signals. Note that duplicated signals like SCWrW, SCWrX, SCWrY and SCWrZ will be described in this document as though they were a single signal, which in this case is called SCWr.

The benefit of duplicating SCAddr(0) will be greater if fast sequential static cache RAMs become available. If SCAddr(0) is attached to a static RAM address bit that effects column decode only, the read cycle time with respect to that pin should approximate the output enable time of the RAM and for fast static RAMs should be half that of the nominal read cycle time.

When the split instruction/data cache mode is enabled, assertion of the top SCAddr bit, SCAddr(17) will enable the instruction half of the cache instead of the data half.

It is possible to design a cache that supports both joint and split instruction/data configurations with less than the maximum cache size. SCAddr(12:0) must be used to address the cache in all configurations. SCAddr(17) must be used to support the split instruction/data configuration. Any of SCAddr(16:13) may be omitted because of the fixed width of the physical tag array.

The SCDChk bus is divided into two fields to cover the upper and lower 64 bits of SCData. This form is required to keep the width of internal data paths to 64 bits.

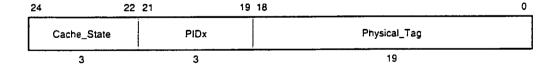

The SCTag bus is divided into three fields, as shown in Fig. 3-1 SCTag Fields. The lower 19 bits consist of the upper physical address bits. The upper three bits consist of cache state, which can be one of Invalid (I), Clean Exclusive (CE), Dirty Exclusive (DE). Bits 19 – 21 are used to maintain information about the virtual address used for caching parts of a secondary cache line in the primary cache. This field holds bits 14 through 12 of the virtual address.

Fig. 3-1 SCTag Fields

Bits 19 – 21 of SCTag are needed to locate entries in the primary caches. The VR4400MC has two primary caches, one for instruction and one for data, which are direct-mapped and are indexed using a subset of the lower 15 bits of the virtual address (implementation dependent, based on primary cache size). If a cache coherency request is processed that requires a cache state change or invalidation, the middle three bits of the SCTag portion of the secondary cache allow primary cache lines affected by that cache coherency request to be found. The three bits of information stored are bits 14 through 12 of the virtual address. This information is loaded during secondary cache misses. On each secondary cache access the virtual address bits are compared with the values found in the secondary

cache tag. If a mismatch occurs, a trap is taken and the trap handler can modify the bits in the secondary cache tag to hold the new values, and the old values are used by the trap handler to purge primary cache locations, so that all primary cache lines holding valid data have indexes known to the secondary cache. This mechanism also helps preserve the integrity of cached accesses to a physical address using differing virtual addresses known as virtual synonyms.

The SCDCS and SCTCS are needed to disable reads or writes of the data array or tag array when the other array is being accessed. These signals are useful for saving power on snoop and invalidate requests, as accesses to the data array are not necessary. These signals are also useful for writing data from the data primary cache to the secondary cache, as the secondary cache state cannot always be determined from the primary cache state.

### 3.3 Control of Secondary Cache Interface

The control of the secondary cache is configurable for various clock rates and static RAM speeds. All configurable parameters are specified in multiples of PClock, which runs at twice the frequency of the external system clock, MasterClock. Boot time mode control registers will hold the various configuration parameters, so that they can be specified when initializing the Va4400MC. The table below shows the number of PClock cycles that those parameters can be specified.

Table 3-1 Secondary Cache Read/Write Cycle Parameters

| Parameter    | Settable Number of PCycles |

|--------------|----------------------------|

| tAd1Cyc      | 4 – 15                     |

| tRd2Cyc      | 3 – 15                     |

| <b>t</b> Dis | 2 – 7                      |

| twnDiy       | 1 – 3                      |

| tw/2Diy      | 1 – 3                      |

| twrRC        | 0 – 1                      |

| twrsup       | 3 – 15                     |

#### 3.3.1 Read Cycles

Each secondary cache read sequence begins with the driving of the address pins. The output enable signal SCOE is asserted at the same time.

There are two basic read cycles: a four-word read, and an eight-word read.

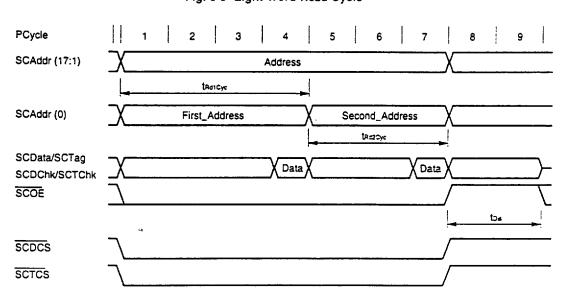

For the four-word read, there are two parameters of interest. The first parameter is read sequence cycle time, TRd1Cyc, which specifies the time from the driving of the SCAddr bus to the sampling of the SCData bus. The second parameter is the cache output disable time TDis, which specifies the time from the end of a read cycle to the start of the next write cycle. Fig. 3-2 Four-Word Read Cycle illustrates the four-word read sequence.

PCycle 1 2 3 4 5 6

SCAddr Bus Address

SCData/SCTag SCDChk/SCTChk

SCOE

SCOE

SCTCS:

Fig. 3-2 Four-Word Read Cycle

For the eight-word read, there is one additional parameter of interest: the time from the first sample point to the second sample point, TRd2Cyc. The lower order address bit, SCAddr(0) is changed at the same time as the first read sample point. Fig. 3-3 Eight-Word Read Cycle illustrates the eight-word read sequence.

Fig. 3-3 Eight-Word Read Cycle

All read cycles can be aborted by changing the address. A new cycle starts beginning with the edge on which the address is changed. Additionally, the period TDis after a read cycle can be interrupted any time by the start of a new read cycle. If a read cycle is aborted by a write cycle, SCOE must be deasserted for the TDis period, before the write cycle can commence. Read cycles can also be extended indefinitely. There is no requirement to change the address at the end of a read cycle.

### 3.3.2 Write Cycles

Like the read sequence, the secondary cache write sequence begins with the driving of the address pins.

There are two basic write cycles: a four-word write, and an eight-word write.

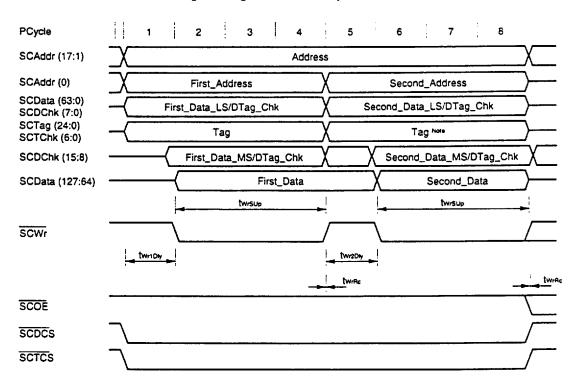

For the four-word write, there are several parameters of interest. The first parameter, TWr1Dly is the time from driving address to the assertion of SCWr. The second parameter, TWrSUp is the time from driving the second data double-word to the deassertion of SCWr. The final parameter, TWrRc, is the time from the deassertion of SCWr to the beginning of the next cycle. TWrRc will be zero for most cache designs. Note that the upper data double word and the lower data double word will normally be driven one cycle apart. This reduces the peak current consumption in the output drivers, Fig. 3-4 Four-Word Write Cycle illustrates the four-word write sequence. The order of driving the upper versus the lower halves of SCData are not fixed, either the upper or the lower halves might be driven first.

**PCycle** 2 3 SCAddr Bus Address SCData (63:0) Data SCDChk (7:0) SCTag (24:0) Data SCTChk (6:0) SCData (127:64) Data SCDChk (15:8) twisup SCWr twnDw twine SCOE SCDCS SCTCS

Fig. 3-4 Four-Word Write Cycle

The eight-word write has one new parameter. The parameter, TWr2Dly, is the time from changing the low-order address bit SCAddr(0) to the assertion of SCWr the second time. The lower half of SCData will be driven out on the same edge as the change in SCAddr(0). Fig. 3-5 Eight-Word Write Cycle illustrates the eight-word write sequence.

Fig. 3-5 Eight-Word Write Cycle

Note The secondary cache tag and tag check are identical for both four-word write cycles.

When receiving data from the system interface, it is possible that the first data double word will arrive several cycles before the second. In this case, the cache state machine will simply wait until that data is available before asserting SCWr and will extend the SCWr until TWrSUp after the driving of the second data item.

#### CHAPTER 4 SYSTEM INTERFACE

The system interface allows the processor access to external resources required to satisfy cache misses while also allowing an external agent access to certain processor internal resources. In the Va4400MC, the system interface also provides the processor mechanisms with which to maintain the cache coherency of shared data, while providing an external agent mechanisms with which to maintain system wide multiprocessor cache coherency.

### 4.1 System Interface Overview

An event that occurs within the processor that requires access to external system resources will be referred to as a system event. System events include, a load that misses in both the primary and secondary caches, a store that misses in both the primary and secondary caches, a store that hits in either the primary or secondary data cache on a shared line, and an uncached load or store. A miss in both caches will require the write back to memory of the cache line that is being replaced if it is in one of the dirty cache states. cache instructions will also cause system events under certain circumstances. For more details on VR4400MC cache instructions see VR4000, VR4400 USER'S MANUAL—ARCHITECTURE.

When a system event occurs, the processor will issue a request or a series of requests called processor requests through the system interface to access some external resource and service the event. The processor's system interface must be connected to some external agent that understands the system interface protocol and can coordinate the access to system resources.

Processor requests include read, write, null write, invalidate, and update requests. Reads are requests for a block, double word, word or partial word of data from main memory or another system resource. Writes provide a block, double word, word or partial word of data to be written to main memory or another system resource. Null writes indicate that an expected write has been obviated as a result of some external request. Invalidates are requests to invalidate the specified cache line in every other cache in the system. Updates are requests to update every other cache in the system with the specified double word, word, or partial word of data.

An external agent may require access to the processor's caches or to some processor internal resource. In this event the external agent will issue a request to the processor through the system interface called an external request to provide the access.

External requests include read, write, invalidate, update, snoop, intervention, and null requests. Reads are requests for a word of data from some processor internal resource. Writes provide a word of data to be written to some processor internal resource. Invalidates specify a cache line that must be marked invalid in the processor 's primary and secondary caches. Updates provide a double word, word or partial word of data to be written to the processor's primary and secondary caches. Snoop requests are used to interrogate the processor's secondary cache to discover if the processor has a valid copy of a particular cache line and if so what cache state the line is in. Snoop requests require the processor to return an indication of the state of the cache line at the specified physical address in the secondary cache if it is present. Intervention requests require the processor to return an indication of the state of the cache line at the specified physical address in the secondary cache and the contents of the cache line from the primary and secondary caches under certain conditions related to the state of the cache line and the nature of the intervention request. Null requests require no action by the processor, rather they simply provide a mechanism for an external agent to either return control of the secondary cache to the processor, or to return control of the system interface to the processor.

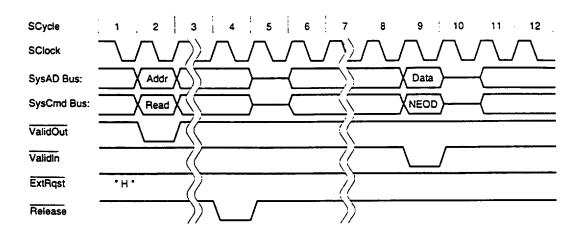

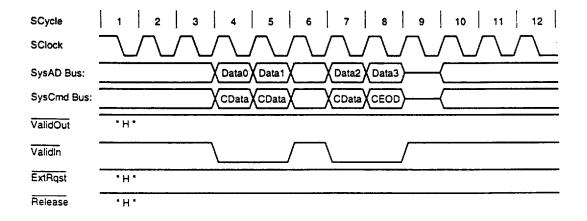

When the processor or an external agent receives a read request, it must access the specified resource and return the requested data. For external read requests, the data will be returned directly in response to the read request. For processor read requests the read request and the return of data by an external agent in response to the read request are disconnected or split. The response data may be returned at any time after the read request, and the system interface is not in use by the read during the time between the read request and the return of response data.

An external agent may initiate an unrelated external request before it returns the response data for a processor read. The return of data in response to a processor read request will be accomplished via a read response. While a read response is technically also an external request, read responses have different characteristics from all other external requests in that arbitration for the system interface must not be performed for read responses. For this reason, read responses will be treated separately from all other external requests, and will be called simply read responses.

Processor read requests that have been issued but for which data has not yet been returned are said to be pending. A read is pending until the read data has been returned. Note that the data identifier associated with the response data may signal that the returned data is erroneous, causing the processor to take a bus error.

External read requests are not split. The system interface is in use between the read request and the return of data by the processor.

A processor read request is complete after the last word of response data has been received from the external agent. A processor write request is complete after the last word of data has been transmitted. A processor invalidate or update request requires a completion acknowledge via the invalidate acknowledge signals IvdAck or IvdErr, unless the invalidate or update is canceled by the external agent. Invalidate or update cancellation is signaled to the processor during external invalidate, update, snoop, and intervention requests. External invalidate, update, snoop and intervention requests, as a group are referred to as external coherence requests. IvdAck is used to signal that a processor invalidate or update request has succeeded. IvdErr is used to signal that a processor invalidate or update request has failed. Since the completion acknowledge for processor invalidate and update requests is signaled through the system interface on dedicated pins, the completion acknowledge may occur in parallel with processor and external requests. A processor invalidate or update request that has been issued but for which the processor has not yet received an acknowledge or a cancellation is said to be unacknowledged.

An external read request is complete after the processor returns the requested word of data. An external write request is complete after the word of data has been transmitted. An external invalidate or update request is complete after the request has been transmitted. An external snoop request is complete after the processor returns the state of the specified cache line. An external intervention request is complete after the processor returns the state of the specified cache line, if the processor does not return the contents of the cache line, or after the processor returns the last word of data for the specified cache line.

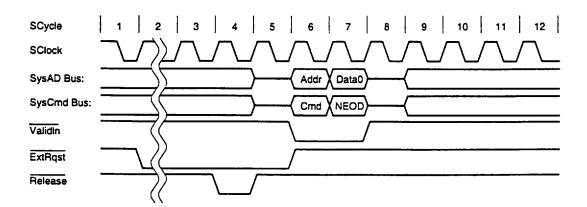

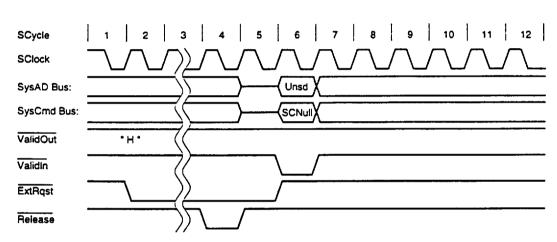

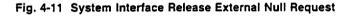

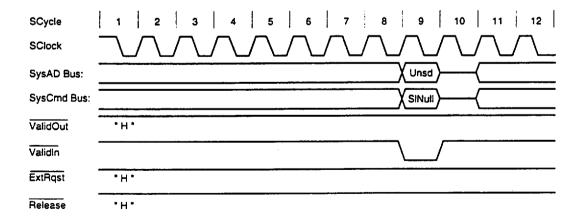

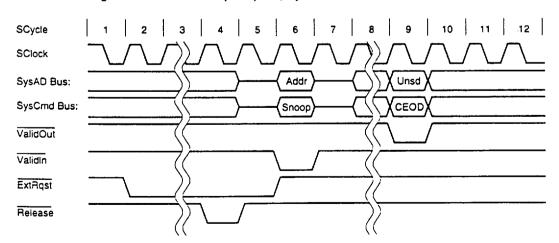

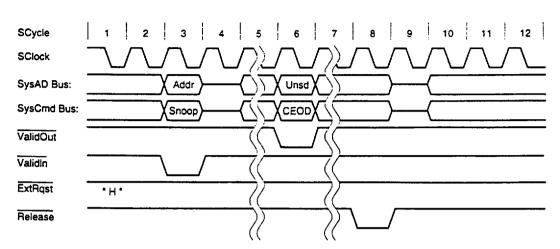

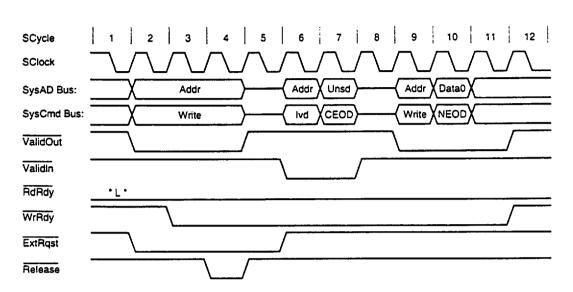

The processor must manage the flow of processor requests and external requests. The flow of external requests is controlled by the processor via the external request arbitration signals ExtRqst, and Release. An external agent must acquire mastership of the system interface before it is allowed to issue an external request by asserting ExtRqst and waiting for the processor to assert Release for one cycle. The processor will not assert Release until it is ready to accept an external request. Mastership of the system interface is always returned to the processor after an external request has been issued, and the processor will not accept a subsequent external request until it has finished the current one.

Processor requests are managed by the processor in two distinct modes, secondary cache mode and no-secondary cache mode, which reflect the presence or absence of a secondary cache, programmable via the boot time mode control interface. The allowed modes of operation are dependent on the package configuration for the processor. A processor in the large configuration package may be programmed to run in secondary cache mode or no-secondary cache mode.

In no-secondary cache mode, the processor will issue requests in a strict sequential fashion; that is, the processor is only allowed to have one request pending at any time. The processor will issue a read request and wait for the read response before issuing any subsequent requests. The processor will issue a write request only if there are no reads pending.

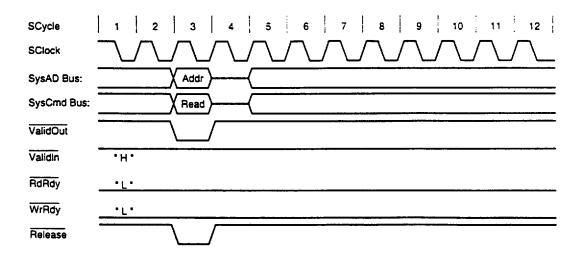

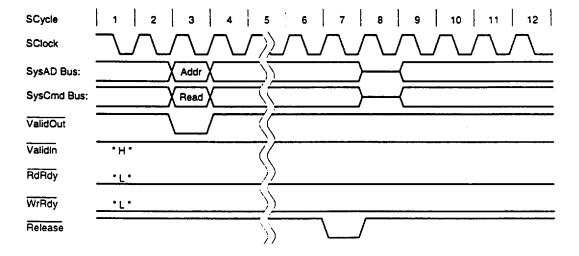

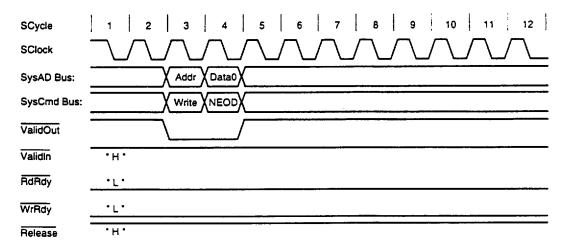

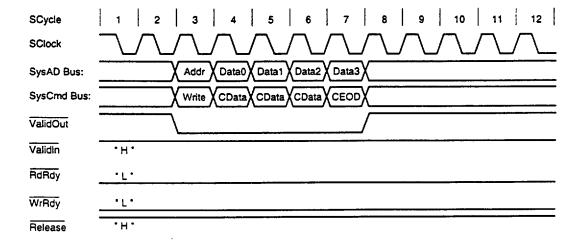

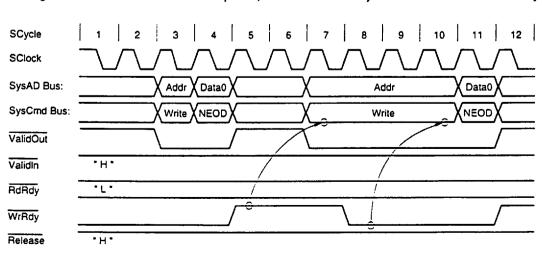

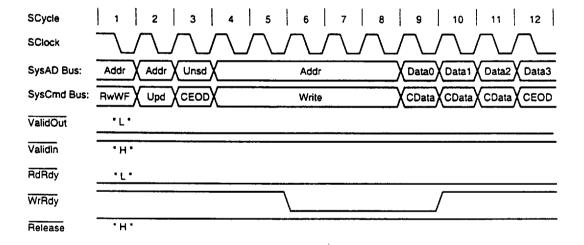

The processor provides the signals RdRdy and WrRdy to allow an external agent to manage the flow of processor requests. RdRdy controls the flow of processor read, invalidate, and update requests while WrRdy controls the flow of processor write requests. Processor null write requests must always be accepted, they cannot be delayed by either RdRdy or WrRdy. The processor samples the signal RdRdy to determine the issue cycle (cycle in which the address cycle is accomplished and the data cycle can be issured next) for a processor read, invalidate, or update request

and the processor samples the signal WrRdy to determine the issue cycle for a processor write request. The issue cycle for a processor read, invalidate or update request is defined to be the first address cycle for the request for which the signal RdRdy was asserted two cycles previously. The issue cycle for a processor write request is defined to be the first address cycle for the write request for which the signal WrRdy was asserted two cycles previously. If the processor wishes to issue a request but is unable to because one of the signals RdRdy or WrRdy is de-asserted, the processor will repeat the address cycle for the request until the issue cycle is accomplished. Once the issue cycle is accomplished, data transmission will begin for a request that includes data. There will always be one and only one issue cycle for any processor request.

The processor will accept external requests while attempting to issue a processor request by releasing the system interface to slave state in response to an assertion of ExtRqst. Note that the rules governing the issue cycle of a processor request are strictly applied to determine the action the processor is taking. The processor will either accomplish the issue of the processor request, in which case the processor request will be completed in its entirety before an external request will be accepted, or the processor will release the system interface to slave state without accomplishing the issue of the processor request. In the latter case, the processor will attempt to issue the processor request again after the external request is completed, and the rules governing issue cycle will again apply.

In the no-secondary cache mode an external agent must be capable of accepting a processor read request at any time there are no processor read requests pending and the signal RdRdy has been asserted for two or more cycles. An external agent must be capable of accepting a processor write request at any time there are no processor read requests pending and the signal WrRdy has been asserted for two or more cycles.

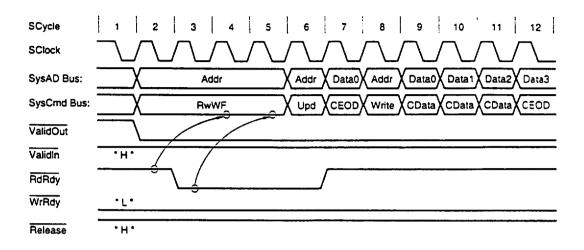

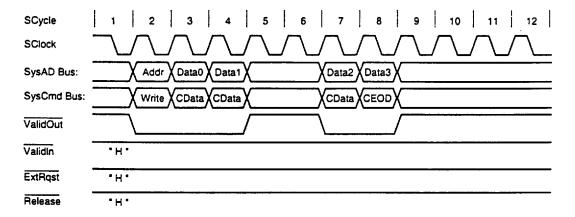

In the secondary cache mode, the processor will issue requests both individually as in no-secondary cache mode and in groups that begin with processor read requests called clusters. Specifically, the processor will issue individual read requests, invalidate or update requests, and write requests and the processor will issue clusters. A cluster consists of a processor read request followed by one or two additional processor requests issued while the read request is pending. All of the requests that are part of a cluster must be accepted before the response to the read request that begins the cluster may be returned to the processor. A cluster will consist of a processor read request followed by a write request, a processor read request followed by a potential update request, or a processor read request followed by a potential update request, followed by a write request.

The issue of potential update requests within a cluster can be disabled via the boot time mode control interface. A processor potential update request is defined to be any update request that is issued while a processor read request is pending. In addition, a bit in the command for processor updates identifies potential updates. Potential updates are issued in conjunction with a processor read request. That is, once the processor accomplishes the issue of a read request, a potential update request will follow if one is required regardless of the state of RdRdy. Potential update requests do not obey the RdRdy flow control rules for issue, but rather issue with a single address cycle regardless of the state of RdRdy.

A write request that is part of a cluster does obey the WrRdy rules for issue, and the processor will accept external requests between the issue of a processor read request, or a processor read request followed by a potential update request, and the issue of a processor write request within a cluster. The processor signals that it is issuing a cluster that contains a processor write request by issuing a read with write forthcoming request instead of an ordinary read request to start the cluster. The read with write forthcoming request is identified by a bit in the command for processor read requests. The external agent must accept all of the requests that form a cluster before it may return a response to the read request that began the cluster. The behavior of the processor is undefined if the external agent returns a response to a processor read request that begins a cluster before accepting all of the requests that form the cluster.

Since the processor will accept external requests between the issue of a read with write forthcoming request that begins a cluster and the issue of the write request that completes the cluster, it is possible for an external request to obviate the need for the write request within the cluster. For instance, if the external agent were to issue an external invalidate request that targeted the cache line the processor was attempting to write back, the state of the cache line would be changed to invalid, and the write back for the cache line would no longer be needed. In this event, the processor will issue a processor null write request after completing the external request to complete the cluster.

Processor null write requests do not obey the WrRdy flow control rules for issue, but rather issue with a single address cycle regardless of the state of WrRdy. Any external request that changes the state of a cache line from dirty exclusive or dirty shared to clean exclusive, shared, or invalid will obviate the need for a write back of that cache line.

A processor potential update request remains potential until the response to the pending processor read request that began the cluster is received. If the read response data is returned in one of the shared states, shared or dirty shared, the potential update is no longer potential and must receive an acknowledge via either the signal IvdAck or IvdErr. If the read response data is returned in one of the exclusive states, clean exclusive or dirty exclusive, the potential update is nullified and the processor will neither expect nor require an acknowledge.

In secondary cache mode, an external agent must be capable of accepting a processor read request followed by a potential update request at any time there are no processor read requests pending, no unacknowledged processor invalidate or update requests, and the signal RdRdy has been asserted for two or more cycles. An external agent must be capable of accepting a processor write request at any time there are no processor read requests pending, there is a processor read with write forthcoming request pending, no unacknowledged processor invalidate or update requests that are compulsory, and the signal WrRdy has been asserted for two or more cycles.

After issuing a processor read request, the processor will not attempt to issue a subsequent read request until it has received a read response for the read request, whether it began a cluster or not. After issuing a processor invalidate or update request, or after a potential update request becomes compulsory, the processor will not attempt to issue a subsequent request until it has received an acknowledge for the invalidate or update request. After the processor has issued a write request, the processor will not attempt to issue a subsequent request until at least four cycles after the issue cycle of the write request.

The following sections detail the sequence, protocol and syntax of processor and external requests. Sequence refers to the precise series of requests that a processor generates to service a system event. Protocol refers to the cycle by cycle signal transitions that occur on the processor's system interface pins to realize a processor or external request. Syntax refers to the precise definition of bit patterns on encoded buses such as the command bus.

#### 4.2 Processor Request Sequencing

The processor will generate a request or a series of requests through the system interface to satisfy system events. Processor requests are managed in two distinct modes, secondary cache mode and no-secondary cache mode. The following sections detail the sequence of requests generated by the processor for each system event in secondary cache and no-secondary cache mode.

#### 4.2.1 Primary and Secondary Cache Miss on a Load

When the processor misses in both the primary and secondary caches on a load, it must obtain the cache line that contains the data element to be loaded from an external agent before it can proceed. If the new cache line will replace a current cache line that is in the state dirty exclusive or dirty shared, the current cache line must be written back before the new line can be loaded in the primary and secondary caches.

The processor will examine the coherency attribute in the TLB entry for the page that contains the requested cache line and if the coherency attribute is exclusive it will issue a coherent read request that also requests exclusivity.

If the coherency attribute is sharable or update the processor will issue a coherent read request and if the coherency attribute is noncoherent the processor will issue a noncoherent read request.

In no-secondary cache mode, the processor will issue a read request for the cache line that contains the data element to be loaded, wait for an external agent to provide the read data in response to the read request, and then, if the current cache line must be written back, the processor will issue a write request for the current cache line.

In secondary cache mode, the processor will issue a read request for the cache line that contains the data element to be loaded if the current cache line does not need to be written back and the coherency attribute for the page that contains the requested cache line is anything other than exclusive. If the current cache line needs to be written back and the coherency attribute for the requested cache line is not exclusive, the processor will issue a cluster consisting

of a read with write forthcoming request for the cache line that contains the data element to be loaded followed by a write request for the current cache line. If the current cache line needs to be written back and the coherency attribute for the page that contains the requested cache line is exclusive, the processor will issue a cluster consisting of an exclusive read with write forthcoming request followed by a write request for the current cache line. If the current cache line needs to be written back and the coherency attribute for the page that contains the requested cache line is update on write, the processor will issue a cluster consisting of a read with write forthcoming request followed by a write request for the current cache line.

The processor request for a primary and secondary cache miss on a load is tabulated below.

Table 4-1 Primary and Secondary Cache Miss on a Load

| Page Attribute                 |                                 | No Secondary                                | Cache Mode | Secondary Cache Mode |       |  |

|--------------------------------|---------------------------------|---------------------------------------------|------------|----------------------|-------|--|

|                                | Processor<br>Configuration      | State of the Data Cache Line Being Replaced |            |                      |       |  |

|                                | Comiguration                    | Clean/Invalid                               | Dirty      | Clean/Invalid        | Dirty |  |

| Noncoherent                    | All Ve4000 and Ve4400           | NCR                                         | NCR/W      | NCR                  | NCR-W |  |

| Exclusive (Write Invalidate)   | Vn4000SC, Vn4400SC,<br>Vn4400MC | NA                                          | NA         | Rex                  | Rex-W |  |