# 4096 × 1 STATIC NMOS RAM

### DESCRIPTION

The µPD4104 is a high performance 4K static RAM. Organized as 4096 x 1, it uses a combination of static storage cells with dynamic input/output circuitry to achieve high speed and low power in the same device. Utilizing NMOS technology, the  $\mu$ PD4104 is fully TTL compatible and operates with a single +5V ± 10% supply.

- FEATURES Fast Access Time 200 ns (μPD4104-2)

- Very Low Stand-By Power 28 mW Max.

- Low V<sub>CC</sub> Data Retention Mode to +3 Volts.

- Single +5V ±10% Supply.

- Fully TTL Compatible.

- Available in 18 Pin Plastic and Ceramic Dual-in-Line Packages.

- 3 Performance Ranges:

|           |             |           | SUPPLY CURRENT |         |         |  |  |

|-----------|-------------|-----------|----------------|---------|---------|--|--|

|           | ACCESS TIME | R/W CYCLE | ACTIVE         | STANDBY | LOW VCC |  |  |

| μPD4104   | 300 ns      | 460 ns    | 21 mA          | 5 mA    | 5 mA    |  |  |

| μPD4104-1 | 250 ns      | 385 ns    | 21 mA          | 5 mA    | 3,3 mA  |  |  |

| μPD4104-2 | 200 ns      | 310 ns    | 25 mA          | 5 mA    | 3,3 mA  |  |  |

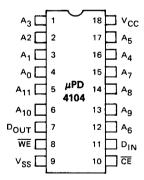

#### **PIN NAMES**

| A <sub>0</sub> -A <sub>11</sub> | Address Inputs |

|---------------------------------|----------------|

| CE                              | Chip Enable    |

| D <sub>IN</sub>                 | Data Input     |

| D <sub>OUT</sub>                | Data Output    |

| v <sub>ss</sub> ·               | Ground         |

| v <sub>cc</sub>                 | Power (+5V)    |

| WE                              | Write Enable   |

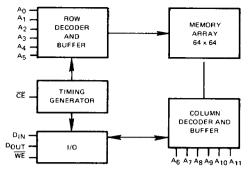

## **BLOCK DIAGRAM**

Operating Temperature

0°C to +70°C

Storage Temperature

−65°C to +150°C

Voltage on Any Pin

−1 to +7 Volts ①

Power Dissipation

1 Watt

Short Circuit Output Current

50 mA

ABSOLUTE MAXIMUM RATINGS\*

Note: 1 With respect to VSS

Ta = 25°C

COMMENT: Stress above those listed under "Absolute Maximum Ratings" may cause permanent

damage to the device. This is a stress rating only and functional operation of the device at these or

any other conditions above those indicated in the operational sections of this specification is not

implied. Exposure to absolute maximum rating conditions for extended periods may affect device

reliability.

$T_a = 0^{\circ} C \text{ to } +70^{\circ} C, V_{CC} = +5 V \pm 10\%$

|                                       |                                              |                  |      | LIMITS |      |            | TEST |

|---------------------------------------|----------------------------------------------|------------------|------|--------|------|------------|------|

| PARAMETE                              | SYMBOL                                       | MIN              | TYP  | MAX    | UNIT | CONDITIONS |      |

| Supply Voltage                        | Supply Voltage                               |                  |      | 5.0    | 5,5  | V          |      |

| Logic "1" Voltage All Ing             | outs                                         | VIH              | 2.2  | -3     | 7.0  | V          | 0    |

| Logic "0" Voltage All Ing             | Logic "0" Voltage All Inputs                 |                  | -1.0 |        | 0.8  | V          |      |

|                                       | μPD4104                                      | Icc1             |      |        | 21   | mA         |      |

| Average V <sub>CC</sub>               | μPD4104-1                                    | Icc1             |      |        | 21   | mA         | 2    |

| Current                               | μPD4104-2                                    | I <sub>CC1</sub> |      |        | 25   | mA         |      |

| Standby V <sub>CC</sub> Power Sup     | Standby V <sub>CC</sub> Power Supply Current |                  |      |        | 5    | mA         | 3    |

| Input Leakage Current (A              | Input Leakage Current (Any Input)            |                  |      |        | 10   | μА         | •    |

| Output Leakage Current                |                                              | lor              | -10  |        | 10   | μА         | 3 5  |

| Output Logic "1" Voltage IOUT -500 µA |                                              | Voн              | 2.4  |        |      | >          |      |

| Output Logic "0" Voltag               | NOUT 5mA                                     | VOL              |      |        | 0.4  | V          |      |

|                                       |                                              |                  |      |        |      |            |      |

DC CHARACTERISTICS 1 6

(1)

|    | CAPACITANCE |

|----|-------------|

| NS |             |

|    |             |

|                    |        | LIMITS |     |     |      |                 |

|--------------------|--------|--------|-----|-----|------|-----------------|

| PARAMETER          | SYMBOL | MIN    | TYP | MAX | UNIT | TEST CONDITIONS |

| Input Capacitance  | CIN    |        | 4   | 6   | ρF   | 0               |

| Output Capacitance | COUT   |        | 6   | 7   | ρF   | 9               |

Notes: 1 All voltages referenced to VSS

$\ensuremath{ \bigcirc }$  IcC1 is related to precharge and cycle times. Guaranteed maximum values for IcC1 may be calculated by

$$I_{CC1}$$

| ma | = (5t<sub>p</sub> + 13 (t<sub>C</sub> - t<sub>p</sub>) + 3420) t<sub>C</sub>

where  $t_{\rm p}$  and  $t_{\rm C}$  are expressed in nanoseconds. Equation is referenced to the -2 device, other devices detate to the same curve.

- 3 Output is disabled (open circuit), CE is at logic 1.

- 4) All device pins at 0 volts except pin under test at 0, VIN = 5.5 volts.

- ⑤  $0V ≤ V_{OUT} ≤ +5.5V$ .

- ⑥ During power up, CE and WE must be at V<sub>1H</sub> for minimum of 2 ms after V<sub>CC</sub> reaches 4.5V, before a valid memory cycle can be accomplished.

- 4.5V, before a valid memory cycle can be accomplished.

Effective capacitance calculated from the equation C = 1 ΔV with ΔV equal to 3V and VCC nominal.

# AC CHARACTERISTICS ② ⑦

Ta = 0°C to +70°C, VCC = +5V ± 10%

|                                          | l               |      |        |        |        |        |        |      |            |

|------------------------------------------|-----------------|------|--------|--------|--------|--------|--------|------|------------|

|                                          |                 | 4104 |        | 4104-1 |        | 4104-2 |        | 1    | TEST       |

| PARAMETER                                | SYMBOL          | MIN  | MAX    | MIN    | MAX    | MIN    | MAX    | UNIT | CONDITIONS |

| Read or Write Cycle Time                 | τc              | 460  |        | 385    |        | 310    |        | ns   | 8          |

| Random Access                            | †AC             |      | 300    |        | 250    |        | 200    | ns   | 3          |

| Chip Enable Pulse Width                  | †CE             | 300  | 10,000 | 250    | 10,000 | 200    | 10,000 | ns   |            |

| Chip Enable Precharge Time               | tp              | 150  |        | 125    |        | 100    |        | ns   |            |

| Address Hold Time                        | tAH.            | 165  |        | 135    |        | 110    | I      | ns   |            |

| Address Set-Up Time                      | <sup>t</sup> AS | 0    |        | 0      |        | 0      |        | ns   |            |

| Output Buffer Turn-Off Delay             | tOFF            | 0    | 75     | 0      | 65     | 0      | 50     | ns   | 9          |

| Read Command Set-Up Time                 | tRS             | 0    |        | 0      |        | 0      |        | ns   | <b>④</b>   |

| Write Enable Set-Up Time                 | tws             | -20  | Ī      | -20    |        | -20    |        | ns   | 4          |

| Data Input Hold Time<br>Referenced to WE | †DIH            | 25   |        | 25     |        | 25     |        | ns   |            |

| Write Enabled Pulse Width                | tww             | 90   |        | 75     |        | 60     |        | ns   |            |

| Modify Time                              | tMOD            | 0    | 10,000 | 0      | 10,000 | 0      | 10,000 | ns   | ⑤          |

| WE to CE Precharge Lead Time             | †WPL            | 105  |        | 85     |        | 70     |        | nş   | 6          |

| Data Input Set-Up Time                   | †DS             | 0    | 1      | 0      |        | 0      |        | ns   |            |

| Write Enable Hold Time                   | twH             | 225  |        | 185    | [      | 150    |        | ns   |            |

| Transition Time                          | tT.             | 5    | 50     | 5      | 50     | 5      | 50     | ns   |            |

| Read-Modify-Write Cycle Time             | tRMW            | 565  |        | 470    |        | 380    |        | ns   | 10         |

- Notes: 1 All voltages referenced to VSS

- Q During power up, CE and WE must be at VIH for minimum of 2 ms after VCC reaches 4.5V, before a valid memory cycle can be accomplished.

- 3 Measured with load circuit equivalent to 2 TTL loads and CL = 100 pF.

- 4) If WE follows CE by more than two then data out may not remain open circuited.

- ⑤ Determined by user. Total cycle time cannot exceed total max.

- Data-in set-up time is referenced to the later of the two falling clock edges \( \overline{CE} \) or \( \overline{WE}. \)

- ① AC measurements assume  $t_T$  = 5 ns. Timing points are taken as  $V_{IL}$  = 0.8V and  $V_{IH}$  = 2.2V on the inputs and  $V_{OL}$  = 0.4V and  $V_{OH}$  = 2.4V on the output waveform.

- 8 t<sub>C</sub> = t<sub>CE</sub> + t<sub>P</sub> + 2 t<sub>T</sub>.

- (9) The true level of the output in the open circuit condition will be determined totally by output load conditions. The output is guaranteed to be open circuit within tOFF.

- 10 TRMW = TAC + TWPL + TP + 3 TT + TMOD.

# STANDBY CHARACTERISTICS

Ta = 0°C to +70°C

|                                             |        | LIMITS |     |        |     |        |     |      | 1          |

|---------------------------------------------|--------|--------|-----|--------|-----|--------|-----|------|------------|

|                                             | SYMBOL | 4104   |     | 4104-1 |     | 4104-2 |     | ŀ    | TEST       |

| PARAMETER                                   |        | MIN    | MAX | MIN    | MAX | MIN    | MAX | UNIT | CONDITIONS |

| V <sub>CC</sub> In Standby                  | VPD    | 3.0    |     | 3.0    |     | 3.0    |     | V    |            |

| Standby Current                             | IPD    |        | 5.0 |        | 3.3 |        | 3.3 | mA   | 0          |

| Power Supply Fall Time                      | TF     | 100    |     | 100    |     | 100    | Γ   | μs   |            |

| Power Supply Rise Time                      | TB     | 100    | 1   | 100    |     | 100    |     | μs   |            |

| Chip Enable Pulse CE Width                  | TCE    | 300    |     | 250    |     | 200    |     | μs   |            |

| Chip Enable Precharge to<br>Power Down Time | ТРРО   | 150    |     | 125    |     | 100    |     | ns   |            |

| "I" Level CE Min Level                      | VIH    | 2.2    |     | 2.2    |     | 2.2    |     | ٧    |            |

| Standby Recovery Time                       | TRC    | 500    | 1   | 500    |     | 500    |     | μς   |            |

Note: 1 Maximum value for  $V_{PD}$  minimum value (= 3 V).

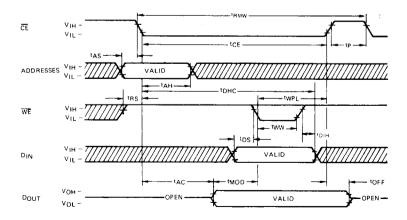

## TIMING WAVEFORMS

# VCC (MIN) VCC VPD - tPPD triangle tri

V<sub>OH</sub> -

VOL -

DOUT

#

TIMING WAVEFORMS (CONT.)

# WRITE CYCLE

- toff

# **READ-MODIFY-WRITE CYCLE**

# OPERATIONAL DESCRIPTION

#### READ CYCLE

The selection of one of the possible 4096 bits is made by virtue of the 12 address bits presented at the inputs. These are latched into the chip by the negative going edge of chip enable ( $\overline{CE}$ ). If the write enable ( $\overline{WE}$ ) input is held at a high level ( $V_{IH}$ ) while the  $\overline{CE}$  input is clocked to a low level ( $V_{IL}$ ), a read operation will be performed. At the access time ( $t_{AC}$ ), valid data will appear at the output. Since the output is unlatched by a positive transition of  $\overline{CE}$ , it will be in the high impedance state from the previous cycle until the access time. It will go to the high impedance state again at the end of the current cycle when  $\overline{CE}$  goes high.

The address lines may be set up for the next cycle any time after the address hold time has been satisfied for the current cycle.

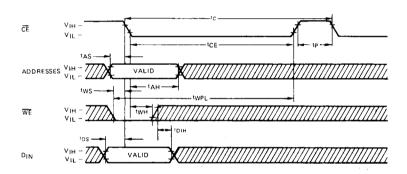

#### WRITE CYCLE

Data to be written into a selected cell is latched into the chip by the later negative transition of  $\overline{CE}$  or  $\overline{WE}$ . If  $\overline{WE}$  is brought low before  $\overline{CE}$ , the cycle is an "Early Write" cycle, and data will be latched by  $\overline{CE}$ . If  $\overline{CE}$  is brought low before  $\overline{WE}$ , as in a Read-Modify-Write cycle, then data will be latched by  $\overline{WE}$ .

If the cycle is an "Early Write" cycle, the output will remain in the high impedance state. For a Read-Modify-Write cycle; the output will be active for the Modify and Write portions of the memory cycle until  $\overline{CE}$  goes high. If  $\overline{WE}$  is brought low after  $\overline{CE}$  but before the access time, the state of the output will be undefined. The desired data will be written into the cell if data-in is valid on the leading edge of  $\overline{WE}$ , toly is satisfied, and  $\overline{WE}$  occurs prior to  $\overline{CE}$  going high by at least the minimum lead time (twpl).

#### **READ-MODIFY-WRITE**

Read and Write cycles can be combined to allow reading of a selected location and then modifying that data within the same memory cycle. Data is read at the access time and modified during a period defined by the user. New data is written between  $\overline{WE}$  low and the positive transition of  $\overline{CE}$ . Data out will remain valid until the rising edge of  $\overline{CE}$ . A minimum R-M-W cycle time can be calculated by  $t_{RMW} = t_{AC} + t_{MOD} + t_{WPL} + t_{P} + 3 t_{T}$ ; where  $t_{RMW}$  is the cycle time,  $t_{AC}$  is the access time,  $t_{MOD}$  is the user defined modify time,  $t_{WPL}$  is the  $\overline{WE}$  to  $\overline{CE}$  lead time,  $t_{P}$  is the  $\overline{CE}$  high time, and  $t_{T}$  is one transition time.

#### POWER DOWN MODE

In power down, data may be retained indefinitely by maintaining V<sub>CC</sub> at +3V. However, prior to V<sub>CC</sub> going below V<sub>CC</sub> minimum ( $\leq$ 4.5V)  $\overline{\text{CE}}$  must be taken high (V<sub>IH</sub> = 2.2V) and held for a minimum time period tppp and maintained at V<sub>IH</sub> for the entire standby period. After power is returned to V<sub>CC</sub> min or above,  $\overline{\text{CE}}$  must be held high for a minimum of t<sub>RC</sub> in order that the device may operate properly. See power down waveforms herein. Any active cycle in progress prior to power down must be completed so that t<sub>CE</sub> min is not violated.

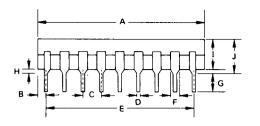

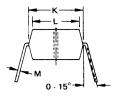

PACKAGE OUTLINES μPD4104C

# Plastic

| ITEM | MILLIMETERS | INCHES    |

|------|-------------|-----------|

| Α    | 23.2 MAX.   | 0.91 MAX. |

| В    | 1.44        | 0.055     |

| С    | 2.54        | 0.1       |

| D    | 0.45        | 0.02      |

| E    | 20.32       | 0.8       |

| F    | 1.2         | 0.06      |

| G    | 2.5 MIN.    | 0.1 MIN.  |

| н    | 0.5 MIN.    | 0.02 MIN. |

| ı    | 4.6 MAX,    | 0.18 MAX. |

| j    | 5.1 MAX.    | 0.2 MAX.  |

| к    | 7.62        | 0.3       |

| L    | 6.7         | 0.26      |

| M    | 0.25        | 0.01      |

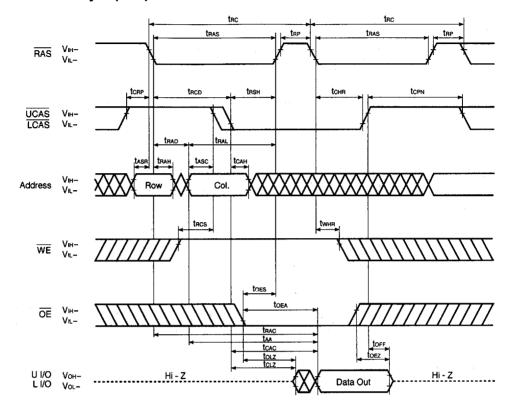

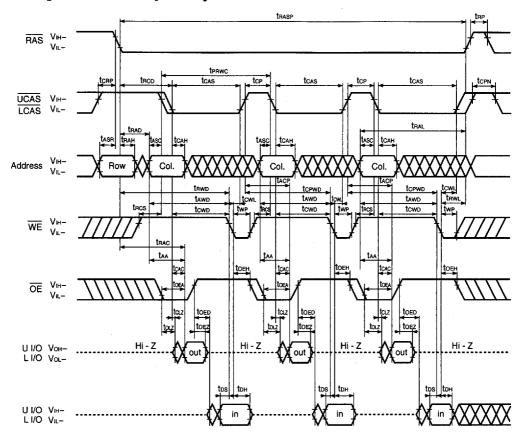

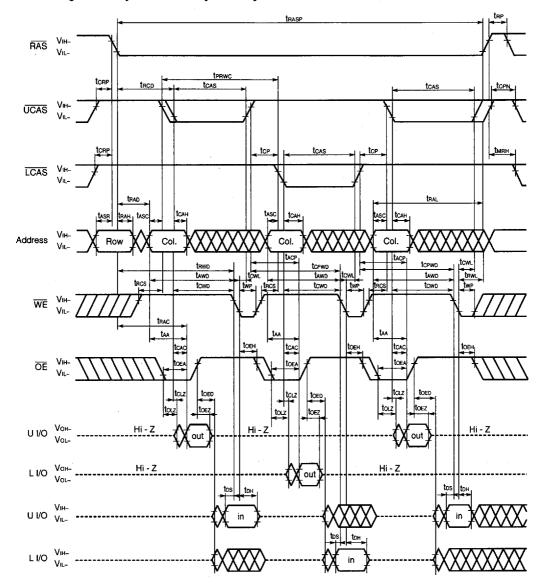

# Fast Page Mode Read Modify Write Cycle

Remark In the fast page mode, read, write and read modify write cycles are available for each of the consecutive CAS cycles within the same RAS cycle.

# Fast Page Mode Byte Read Modify Write Cycle

Remarks 1. In the fast page mode, read, write and read modify write cycles are available for each of the consecutive CAS cycles within the same RAS cycle.

2. This cycle can be used to control either UCAS or LCAS only. Or, it can be used to control UCAS or LCAS simultaneously, or at random.

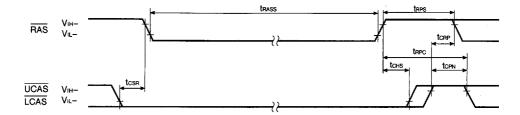

# CAS Before RAS Self Refresh Cycle (Only for the µPD42S18160)

Remark Address, WE, OE: Don't care L I/O, U I/O: Hi-Z

# Cautions on Use of CAS Before RAS Self Refresh

CAS before RAS self refresh can be used independently when used in combination with distributed CAS before RAS long refresh; However, when used in combination with burst CAS before RAS long refresh or with long RAS only refresh (both distributed and burst), the following cautions must be observed.

(1) Normal Combined Use of CAS Before RAS Self Refresh and Burst CAS Before RAS Long Refresh

When CAS before RAS self refresh and burst CAS before RAS long refresh are used in combination, please

perform CAS before RAS refresh as follows just before and after setting CAS before RAS self refresh.

$\mu$ PD42S18160: 1,024 times within a 16 ms interval

(2) Normal Combined Use of CAS Before RAS Self Refresh and Long RAS Only Refresh

When CAS before RAS self refresh and RAS only refresh are used in combination, please perform RAS only refresh as follows just before and after setting CAS before RAS self refresh.

μPD42S18160: 1,024 times within a 16 ms interval

(3) If trass (MIN.) is not satisfied at the beginning of CAS before RAS self refresh cycles (tras < 100 μs), CAS before RAS refresh cycles will be executed one time.</p>

If 10  $\mu$ s < thas < 100  $\mu$ s,  $\overline{RAS}$  precharge time for  $\overline{CAS}$  before  $\overline{RAS}$  self refresh (thes) is applied. And refresh cycles as follows should be met.

μPD42S18160: 1,024 times within a 128 ms interval

For details, please refer to How to use DRAM User's Manual.

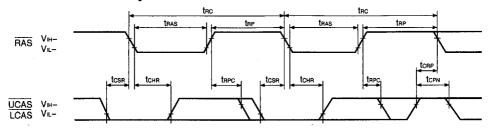

# CAS Before RAS Refresh Cycle

Remark Address, WE, OE: Don't care L I/O, U I/O: Hi-Z

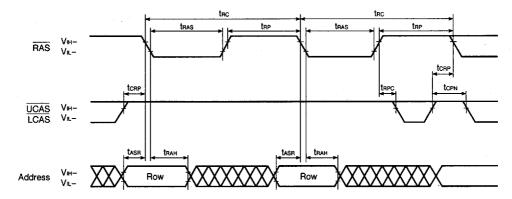

# **RAS** Only Refresh Cycle

Remark WE, OE: Don't care L I/O, U I/O: Hi-Z

# Hidden Refresh Cycle (Read)