### Description

The  $\mu$ PD41101 is a 910-word by 8-bit line buffer fabricated with the N-channel silicon-gate process. The device helps to create an NTSC flicker-free television picture (noninterlaced scan conversion) by providing intermediate storage and very high-speed read and write operation.

The  $\mu$ PD41101 can also be used as a digital delay line. The delay length is variable from 10 bits (at maximum clock speed) to 910 bits.

### **Features**

- ☐ 910-word x 8-bit organization

- ☐ Line buffer for NTSC, 4f<sub>SC</sub> digital television systems

- Asynchronous and simultaneous read/write operation

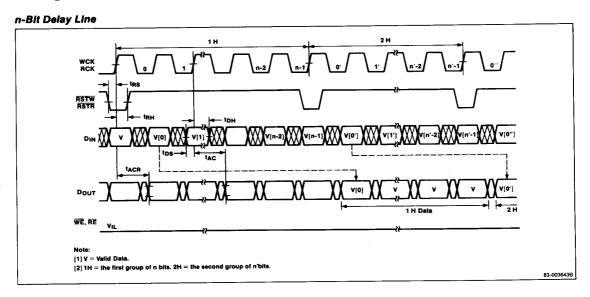

- ☐ 1H (910-bit) delay line capability

- ☐ TTL-compatible inputs and outputs

- ☐ Three-state outputs

- ☐ Single 5-volt ±10% power supply

- 300-mil, 24-pin plastic DIP and 450-mil, 24-pin plastic miniflat packaging

# **Ordering Information**

| Part Number | Read Cycle<br>Time (min) | Write Cycle<br>Time (min) | Package            |  |  |

|-------------|--------------------------|---------------------------|--------------------|--|--|

| μPD41101C-3 | 34 ns                    | 34 ns                     | 24-pin plastic DIP |  |  |

| C-2         | 34 ns                    | 69 ns                     |                    |  |  |

| C-1         | 69 ns                    | 69 ns                     |                    |  |  |

| μPD41101G-3 | 34 ns                    | 34 ns                     | 24-pin plastic     |  |  |

| G-2         | 34 ns                    | 69 ns                     | miniflat           |  |  |

| G-1         | 69 ns                    | 69 ns                     |                    |  |  |

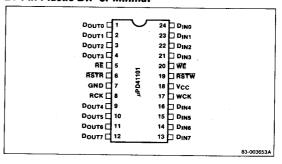

# Pin Identification

| Symbol                               | Function                  |  |  |  |  |  |

|--------------------------------------|---------------------------|--|--|--|--|--|

| D <sub>INO</sub> -D <sub>IN7</sub>   | Write data inputs         |  |  |  |  |  |

| D <sub>OUTO</sub> -D <sub>OUT7</sub> | Read data outputs         |  |  |  |  |  |

| RSTW                                 | Write address reset input |  |  |  |  |  |

| RSTR                                 | Read address reset input  |  |  |  |  |  |

| WE                                   | Write enable input        |  |  |  |  |  |

| RE                                   | Read enable input         |  |  |  |  |  |

| WCK                                  | Write clock input         |  |  |  |  |  |

| RCK                                  | Read clock input          |  |  |  |  |  |

| GND                                  | Ground                    |  |  |  |  |  |

| V <sub>CC</sub>                      | +5-volt power supply      |  |  |  |  |  |

### Pin Configuration

### 24-Pin Plastic DIP or Minifiat

### **Pin Functions**

### DINO-DIN7 [Data Inputs]

In a digital television application, the digital composite signal, luminance, chrominance, etc., information is written into these inputs.

# DOUT0-DOUT7 [Data Outputs]

These tri-state outputs are used to access the stored information. In a simple digital delay line application, a delay of one-half write clock cycle plus a maximum of 300 ns is required to move data from the data inputs to the data outputs.

# RSTW [Write Address Reset Input]

Bringing this signal to a low level resets the internal write address to 0 if  $\overline{\text{WE}}$  is also at a low level. If  $\overline{\text{WE}}$  is at a high level when the  $\overline{\text{RSTW}}$  input is brought low, the internal write address is set to 909. The state of this input is strobed by the rising edge of WCK.

# **RSTR** [Read Address Reset Input]

Strobed by the rising edge of <u>RCK</u>, this signal resets the internal read address to 0 if <u>RE is al</u>so at a low level. If <u>RE</u> is at a high level when the <u>RSTR</u> input is brought low, the internal read address is set to 909.

### WE [Write Enable Input]

This input controls write operation. If  $\overline{WE}$  is at a low level, all write cycles proceed. If  $\overline{WE}$  is at a high level, no data is written to storage cells and the write address stops increasing. The state of  $\overline{WE}$  is strobed by the rising edge of WCK.

# RE [Read Enable Input]

This signal is similar to  $\overline{WE}$  but controls read operation. If  $\overline{RE}$  is at a high level, the data outputs become high impedance and the internal read address stops increasing. The state of  $\overline{RE}$  is strobed by the rising edge of RCK.

### WCK [Write Clock input]

All write cycles are executed synchronously with WCK. The states of both RSTW and WE are strobed by the rising edge of WCK at the beginning of a cycle, and the data inputs are strobed by the rising edge of WCK at the end of a cycle. The internal write address increases with each WCK cycle unless WE is at a high level to hold the write address constant. Unless inhibited by WE, the internal write address will automatically wrap around from 909 to 0 and begin increasing again.

### **RCK [Read Clock Input]**

All read cycles are executed synchronously with RCK. The states of both RSTR and RE are strobed by the

rising edge of RCK at the beginning of a cycle. This same edge of RCK starts internal read operation, and access time is referenced to this edge. The internal read address increases with each RCK cycle unless  $\overline{\text{RE}}$  is at a high level to hold the read address constant. Unless inhibited by  $\overline{\text{RE}}$ , the internal read address will automatically wrap around from 909 to 0 and begin increasing again.

# **Absolute Maximum Ratings**

| Supply voltage, V <sub>CC</sub>               | -1.5 to +7.0 V |

|-----------------------------------------------|----------------|

| Voltage on any input pin, V <sub>I</sub>      | -1.5 to +7.0 V |

| Voltage on any output pin, V <sub>0</sub>     | -1.5 to +7.0 V |

| Short-circuit output current, I <sub>OS</sub> | 20 mA          |

| Operating temperature, T <sub>OPR</sub>       | −20 to +70°C   |

| Storage temperature, T <sub>STG</sub>         | −55 to +125°C  |

|                                               | <del></del>    |

Comment: Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should be operated within the limits specified under DC and AC Characteristics.

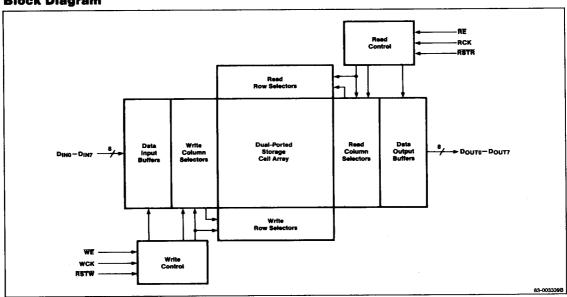

### **Block Diagram**

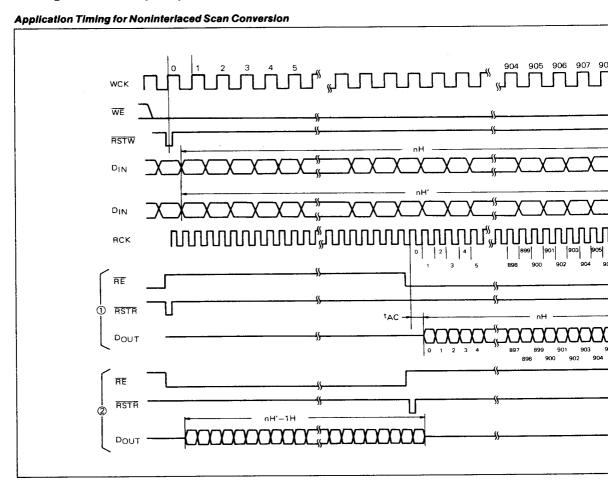

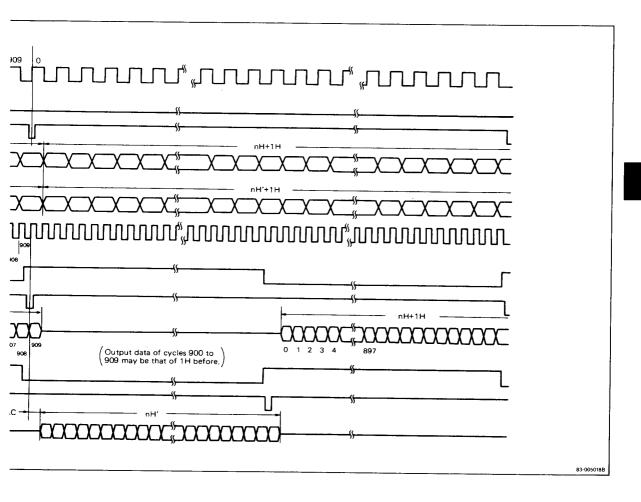

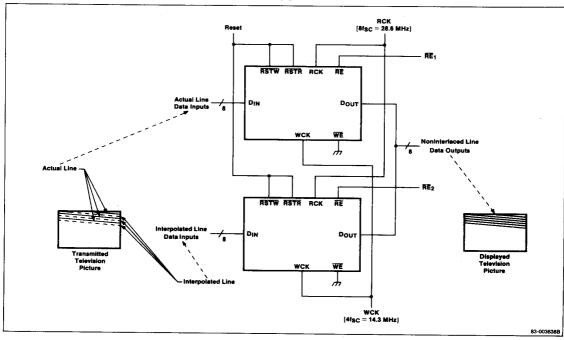

Figure 1. Connection for Noninterlaced Scan Conversion

# Recommended DC Operating Conditions $T_A = -20 \text{ to } +70 \,^{\circ}\text{C}$ ; GND = 0 V

| Parameter           | Symbol          | Min  | Тур | Max | Unit |

|---------------------|-----------------|------|-----|-----|------|

| Supply voltage      | V <sub>CC</sub> | 4.5  | 5.0 | 5.5 | V    |

| Input voltage, high | V <sub>IH</sub> | 2.4  |     | 5.5 | V    |

| Input voltage, low  | V <sub>IL</sub> | -1.5 |     | 0.8 | V    |

### Capacitance

$T_A = -20 \text{ to } +70 \,^{\circ}\text{C}; V_{CC} = 5.0 \text{ V} \pm 10\%; f = 1 \text{ MHz}$

|                    |                | Limits |     |     |      |                                               |  |

|--------------------|----------------|--------|-----|-----|------|-----------------------------------------------|--|

| Parameter          | Symbol         | Min    | Тур | Max | Unit | Pins Under Test                               |  |

| Input capacitance  | CI             |        |     | 5   | pF   | WE, RE, WCK,<br>RCK, RSTW,<br>RSTR, DINO-DIN7 |  |

| Output capacitance | C <sub>0</sub> |        |     | 7   | pF   | D <sub>OUTO</sub> -D <sub>OUT7</sub>          |  |

### Notes:

(1) These parameters are sampled and not 100% tested.

### **DC Characteristics**

$T_{\Delta} = -20 \text{ to } +70 \,^{\circ}\text{C}; V_{CC} = 5.0 \text{ V} \pm 10\%$

| Parameter                          |                 |     | Limita | 3   |      |                                                                                   |

|------------------------------------|-----------------|-----|--------|-----|------|-----------------------------------------------------------------------------------|

|                                    | Symbol          | Min | Тур    | Max | Unit | Test Conditions                                                                   |

| Write/read cycle operating current | Icc             |     |        | 90  | mA   |                                                                                   |

| Input leakage<br>current           | i <sub>l</sub>  | -10 |        | 10  | μΑ   | V <sub>I</sub> = 0 to V <sub>CC</sub> ; all<br>other pins not<br>under test = 0 V |

| Output leakage<br>current          | 10              | -10 |        | 10  | μΑ   | D <sub>OUT</sub> disabled;<br>V <sub>0</sub> = 0 to 5.5 V                         |

| Output voltage,<br>high            | V <sub>OH</sub> | 2.4 |        |     | ٧    | $I_{OH} = -1 \text{ mA}$                                                          |

| Output voltage,<br>low             | V <sub>OL</sub> |     | -      | 0.4 | ٧    | $I_{OL} = 2 \text{ mA}$                                                           |

(1) All voltages are referenced to ground.

### **AC Characteristics**

$T_A = -20 \text{ to } +70 \,^{\circ}\text{C}; V_{CC} = 5.0 \text{ V} \pm 10\%$

|                                      |                   | Limits              |          |                     |          |                     |          |      |                                       |

|--------------------------------------|-------------------|---------------------|----------|---------------------|----------|---------------------|----------|------|---------------------------------------|

|                                      | Symbol            | μ <b>PD4</b> 1101-3 |          | μ <b>PD4110</b> 1-2 |          | μ <b>PD4</b> 1101-1 |          |      |                                       |

| Parameter                            |                   | Min                 | Max      | Min                 | Max      | Min                 | Max      | Unit | Test Conditions                       |

| Write clock cycle time               | twck              | 34                  | 1090     | 69                  | 1090     | 69                  | 1090     | ns   |                                       |

| WCK pulse width                      | twcw              | 14                  |          | 25                  |          | 25                  |          | ns   | · · · · · · · · · · · · · · · · · · · |

| WCK precharge time                   | twcp              | 14                  |          | 25                  |          | 25                  |          | ns   |                                       |

| Read clock cycle time                | trck              | 34                  | 1090     | 34                  | 1090     | 69                  | 1090     | ns   |                                       |

| RCK pulse width                      | t <sub>RCW</sub>  | 14                  |          | 14                  |          | 25                  |          | ns   |                                       |

| RCK precharge time                   | tRCP              | 14                  |          | 14                  |          | 25                  |          | ns   |                                       |

| Access time                          | tAC               |                     | 27       |                     | 27       |                     | 49       | ns   | Figure 5                              |

| Access time after a reset cycle      | tacr              |                     | 27       |                     | 27       |                     | 49       | ns   |                                       |

| Output hold time                     | tон               | 5                   |          | 5                   |          | 5                   |          | ns   |                                       |

| Output hold time after a reset cycle | tohr              | 5                   |          | 5                   |          | 5                   |          | ns   | Figure 5 (Note 7)                     |

| Output active time                   | t <sub>LZ</sub>   | 5                   | 27       | 5                   | 27       | 5                   | 49       | ns   | (Note 4)                              |

| Output disable time                  | tHZ               | 5                   | 27       | 5                   | 27       | 5                   | 49       | ns   |                                       |

| Data-in setup time                   | t <sub>DS</sub>   | 14                  |          | 18                  |          | 18                  |          | ns   |                                       |

| Data-in hold time                    | t <sub>DH</sub>   | 5                   |          | 5                   |          | 5                   |          | ns   |                                       |

| Reset active setup time              | t <sub>RS</sub>   | 14                  |          | 14                  |          | 20                  |          | ns   | (Note 8)                              |

| Reset active hold time               | t <sub>RH</sub>   | 5                   |          | 5                   |          | 5                   |          | ns   |                                       |

| Reset inactive hold time             | t <sub>RN1</sub>  | 5                   |          | 5                   |          | 5                   |          | ns   | (Note 9)                              |

| Reset inactive setup time            | t <sub>RN2</sub>  | 14                  |          | 14                  |          | 20                  |          | ns   |                                       |

| Write enable setup time              | twes              | 14                  |          | 20                  |          | 20                  |          | ns   | (Note 10)                             |

| Write enable hold time               | twen              | 5                   |          | 5                   |          | 5                   |          | ns   |                                       |

| Write enable high delay from WCK     | twen1             | 5                   |          | 5                   |          | 5                   |          | ns   | (Note 11)                             |

| Write enable low delay to WCK        | twen2             | 14                  |          | 20                  |          | 20                  |          | ns   |                                       |

| Read enable setup time               | t <sub>RES</sub>  | 14                  |          | 14                  |          | 20                  |          | ns   | (Note 10)                             |

| Read enable hold time                | treh              | 5                   |          | 5                   |          | 5                   |          | ns   |                                       |

| Read enable high delay from RCK      | t <sub>REN1</sub> | 5                   |          | 5                   |          | 5                   |          | ns   | (Note 11)                             |

| Read enable low delay to RCK         | t <sub>REN2</sub> | 14                  |          | 14                  |          | 20                  |          | ns   |                                       |

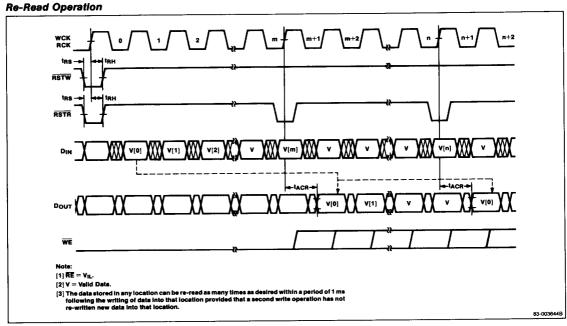

| Write disable pulse width            | twew              | 0                   | (Note 6) | 0                   | (Note 6) | 0                   | (Note 6) | ms   |                                       |

| Read disable pulse width             | trew              | 0                   | (Note 6) | 0                   | (Note 6) | 0                   | (Note 6) | ms   |                                       |

| Write reset time                     | trstw             | 0                   | (Note 6) | 0                   | (Note 6) | 0                   | (Note 6) | ms   |                                       |

| Read reset time                      | trstr             | 0                   | (Note 6) | 0                   | (Note 6) | 0                   | (Note 6) | ms   |                                       |

| Transition time                      | tT                | 3                   | 35       | 3                   | 35       | 3                   | 35       | ns   |                                       |

### Notes:

- (1) All voltages are referenced to ground.

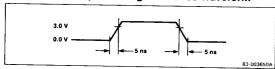

- (2) Input pulse rise and fall times assume  $t_T = 5$  ns. Input pulse levels = GND to 3 V. Transition times are measured between 3 V and 0 V. See figure 3.

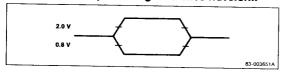

- (3) Output timing reference levels are 0.8 and 2.0 volts. See figure 4.

- (4) This delay is measured at ±200 mV from the steady-state voltage with the load specified in figure 6. Under any conditions, t<sub>LZ</sub> ≥ t<sub>HZ</sub>.

- (5) Input timing reference levels = 1.5 V.

# **AC Characteristics (cont)**

### Notes [cont]:

- (6) twew (max) and t<sub>REW</sub> (max) must be satisfied by the following equations in 1 line cycle operation: twew+t<sub>RSTW</sub> + 910 (t<sub>WCK</sub>) ≤ 1 ms t<sub>REW</sub> + t<sub>RSTW</sub> + 910 (t<sub>RCK</sub>) ≤ 1 ms

- (7) This parameter has meaning when  $t_{RCK} \ge t_{ACR}$  (max).

- (8) If either t<sub>RS</sub> or t<sub>RH</sub> is less than the specified value, reset operations are not guaranteed.

- (9) If either t<sub>RN1</sub> or t<sub>RN2</sub> is less than the specified value, internal reset operations may extend to cycles immediately preceding or following the period of desired reset operations.

Figure 2. Connection for a 1H (910-Bit) Delay Line

Figure 3. AC Input Timing Reference Waveform

Figure 4. AC Output Timing Reference Waveform

- (10) If either  $t_{WES}$  or  $t_{WEH}$  ( $t_{RES}$  or  $t_{REH}$ ) is less than the specified value, write (read) disable operations are not guaranteed.

- (11) If either twen1 or twen2 (tren1 or tren2) is less than the specified value, internal write (read) disable operations may extend to cycles immediately preceding or following the period of desired disable operations.

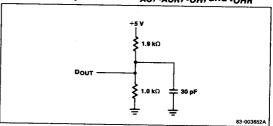

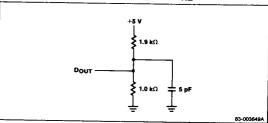

Figure 5. Output Load for  $t_{AC}$ ,  $t_{ACR}$ ,  $t_{OH}$ , and  $t_{OHR}$

Figure 6. Output Load for tLZ and tHZ

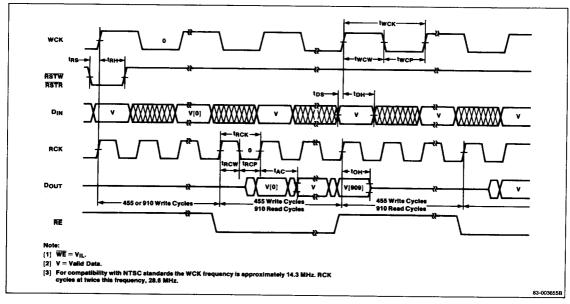

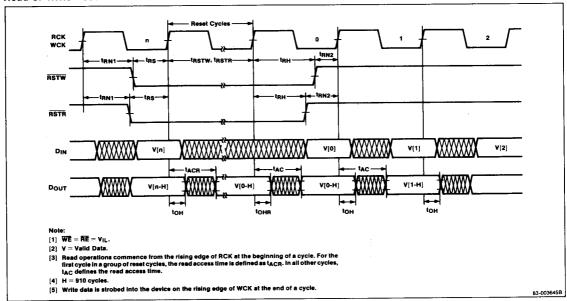

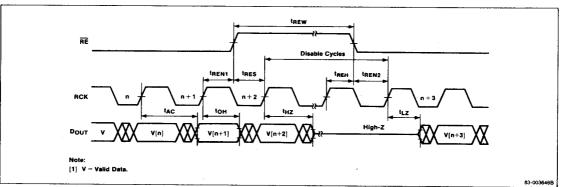

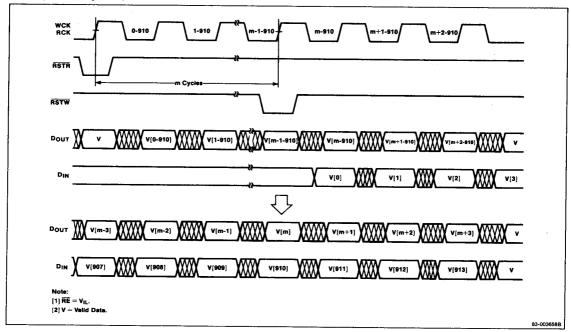

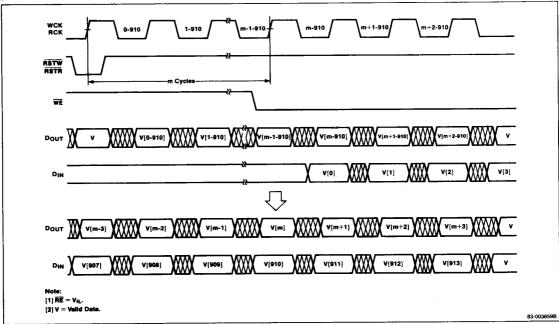

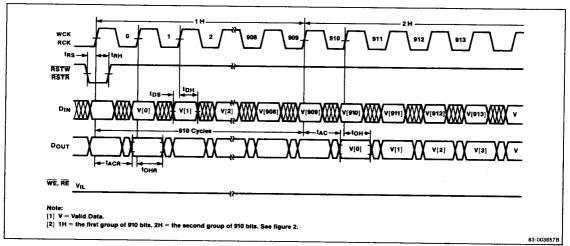

# **Timing Waveforms**

### Read or Write Reset

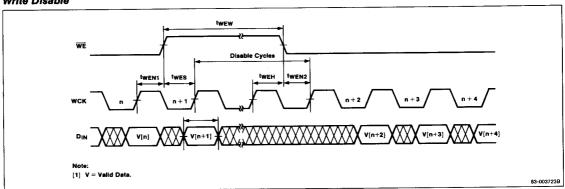

### Write Disable

### Read Disable

# (910-m)-Bit Delay Line, No. 1

# 910-Bit Delay Line

# Basic Timing for Noninterlaced Scan Conversion