05E 21466

T-52-33-09

# **μPD42232**

# TRIPLE-PORT GRAPHICS BUFFER

# PRELIMINARY INFORMATION

## Description

The  $\mu$ PD42232 is a highly integrated triple-port graphics buffer specifically designed for graphics and image processing applications. The device is configured as 32K words by 8 bits with a serial input/output port and a dual port for random access. Asynchronous operation of the serial port allows the random access port to draw graphics while data is output serially. Serial input and output ports may be configured by 8, 4, 2, or 1 bit(s).

The random access port can be used to form a matrix frame buffer with coexistent 8-bit plane and 1-bit pixel operation. In plane operation, data across the screen in one plane (x and y dimension) is accessed. In pixel operation, data in multiple planes (z dimension) is accessed. In the matrix frame buffer architecture, selection of plane or pixel access is made in a special command cycle. Furthermore, a selectable open-drain connection allows the outputs to be wire-ORed.

The µPD42232 supports 256 trinomial raster operations, as well as bit, chip or plane writing and reading. Refreshing is accomplished by means of RAS-only, CAS-before-RAS, and hidden refresh cycles. The device is packaged in a 600-mil, 40-pin plastic shrink DIP and a 400-mil, 40-pin plastic SOJ.

## **Features**

- ☐ Triple-port organization

- 32K x 8-bit random access port

- 8-bit input/output port for plane access

- 1-bit input/output port for pixel access

- 128 x 8-bit serial input/output port

- □ Ten built-in registers

- 256 types of raster operations

- Random access of bit, chip, or plane data

- Compare function

- ☐ Each of 8 serial data registers configured as a split buffer, allowing for relaxed data transfer timing

- ☐ Bidirectional data transfer between random access storage array and serial data registers

- RAS-only, CAS-before-RAS, and hidden refreshing

- ☐ Serial port configuration by 8, 4, 2, or 1 bit(s)

- ☐ Selectable open-drain or three-state random access outputs

- □ Fully TTL-compatible inputs and outputs

- ☐ Standard 40-pin plastic shrink DIP and 40-pin plastic SOJ packaging

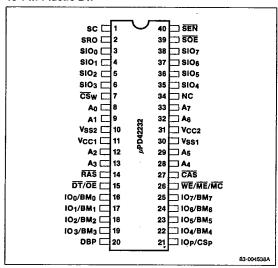

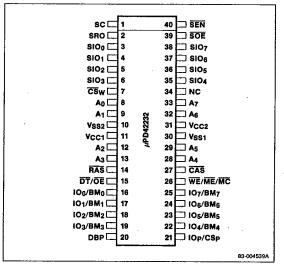

## Pin Configurations

40-Pin Plastic DIP

40-Pin Plastic SOJ

Contact your NEC sales representative for a copy of the complete data sheet.

3-75

# 05E 21467

T-52-33 -09

# $\mu$ PD42232

# **Ordering Information**

| Part Number   | Random<br>Write/Read<br>Cycle Time<br>(min) | Serial<br>Write/Read<br>Cycle Time<br>(max) | RAS<br>Access Time<br>(max) | Package                      |

|---------------|---------------------------------------------|---------------------------------------------|-----------------------------|------------------------------|

| μPD42232CU-12 | 220 ns                                      | 40 ns                                       | 120 ns                      | 40-pin plastic<br>shrink DIP |

| CU-15         | 260 ns                                      | 60 ns                                       | 150 ns                      |                              |

| μPD42232LA-12 | 220 ns                                      | 40 ns                                       | 120 ns                      | 40-pin plastic<br>SOJ        |

| LA-15         | 260 ns                                      | 60 ns                                       | 150 ns                      |                              |

## **Pin Identification**

| Symbol                                                             | Function                                              |  |

|--------------------------------------------------------------------|-------------------------------------------------------|--|

| A <sub>0</sub> /C <sub>0</sub> -A <sub>7</sub> /C <sub>7</sub>     | Address inputs/command code inputs                    |  |

| BM <sub>0</sub> /10 <sub>0</sub> -BM <sub>7</sub> /10 <sub>7</sub> | Bit mask inputs/plane data inputs and outputs         |  |

| CAS                                                                | Column address strobe                                 |  |

| CS <sub>P</sub> /IO <sub>P</sub>                                   | Chip select mask inputs/pixel data inputs and outputs |  |

| <del>CS</del> <sub>W</sub>                                         | Chip select for random access port                    |  |

| DBP                                                                | Data bus precharge (selects open-drain output)        |  |

| DT/OE                                                              | Data transfer control/output enable                   |  |

| RAS                                                                | Row address strobe                                    |  |

| SC                                                                 | Serial clock                                          |  |

| SEN                                                                | Serial port enable                                    |  |

| SI0 <sub>0</sub> -SI0 <sub>7</sub>                                 | Serial data inputs and outputs                        |  |

| SOE                                                                | Serial output enable                                  |  |

| SR0                                                                | Serial runout output                                  |  |

| WE/ME/MC                                                           | Write enable/mask enable/memory command               |  |

| V <sub>SS1</sub> /V <sub>SS2</sub>                                 | Ground                                                |  |

| V <sub>CC1</sub> /V <sub>CC2</sub>                                 | +5-volt power supply                                  |  |

| NC                                                                 | No connection                                         |  |

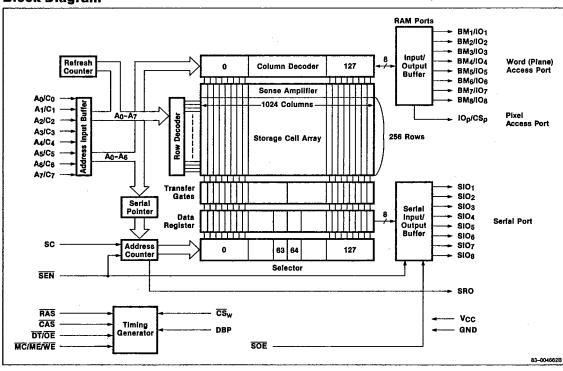

# **Block Diagram**

3-76

6427525 N E C ELECTRONICS INC

05E 21468 D

μ**PD42232**

T-52-33-09

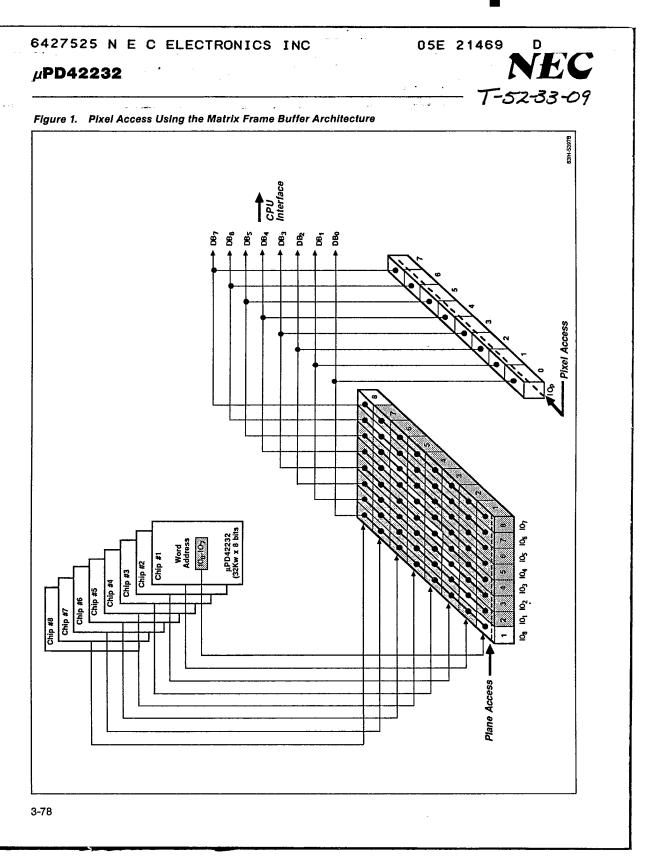

## Example of Matrix Frame **Buffer Architecture**

The following describes the configuration for an 8-plane, 512 x 512 dot matrix frame buffer using one μPD42232 per plane and an 8-bit CPU interface bus. As can be seen in figure 1, the IO0 through IO7 plane access ports on each µPD42232 are connected to DB<sub>0</sub> through DB7 of the CPU interface bus. Pixel access port IOP on the first µPD42232 is connected to DB<sub>0</sub>. IOP on the second µPD42232 is connected to DB1 and so on.

This configuration supports two types of operation, either of which can be selected in a special command cycle:

- Plane-where 8 bits in the same plane are accessed

- Pixel—where 8 bits of the same pixel, 8 planes deep, are accessed

In plane operation, one plane is selected by means of the chip select or plane-mask function, causing the 8 bits of data specified by IO0 through IO7 to be accessed. In pixel operation, one pixel (8 bits) of data from the IOP pin of each chip is accessed using the bit-mask function to select only one of the 8 bits at the specified address.

The example shown in figure 1, where one bit from each chip (plane) in a diagonal line is accessed (IOo through IO7), was chosen for the ease of explaining the pixel access function, which was developed to quickly change the color or shade of each pixel. In most applications, a single pixel at the same  $IO_X$  bit is updated. Since all eight chips are accessed simultaneously, a pixel update can be accomplished in one write cycle.

#### **Split Buffer Configuration**

A split buffer configuration is useful because it greatly relaxes the synchronization of timing between the random access and serial ports during data transfers, making it possible to design a video system where the serial port can be loaded at any time during the display or horizontal retrace period. Furthermore, the ability to perform serial register updates from the random access port during any part of the display time allows the size of the frame buffer to match CRT resolution, reducing the number of data transfers required and making more efficient use of video storage.

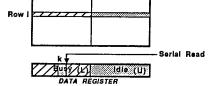

Item 1 of figure 2 shows the initial loading of both the lower (L) and upper (U) halves of the split buffer, which is required as part of the initialization sequence. Item 2 indicates that serial read cycles begin executing at location k and continue through location 63. The SRO serial runout pin goes high after locations 63 and 127. Items 3 and 4 show the beginning of serial reading in the right buffer (U), while the left (L) is being reloaded. Full asynchronous operation is provided by the simultaneous reading of one serial buffer while the opposite side is reloaded.

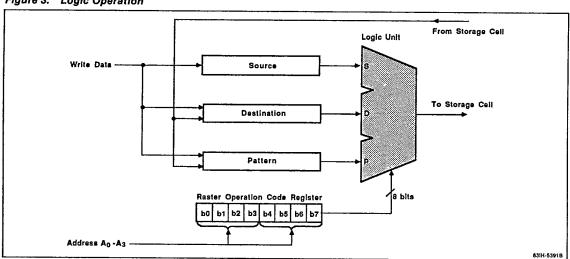

## **Logic Operation**

The  $\mu$ PD42232 is equipped with a function that performs trinomial logic operation for each bit using the internal pattern and destination registers and write data input from the random access port as source data. To select this function, the raster operation code must be set by means of a special command cycle. Once set, it is retained until changed by another special command cycle. In a mask write cycle, this logic operation can be performed in 256 ways using the 8-bit raster operation code register.

The setup and execution of this logic operation takes five cycles (figure 3):

- Loading of pattern or destination register (1 cycle)

- Setting of raster operation code during memory command cycle

- Lower 4 bits (1 cycle)

- Upper 4 bits (1 cycle)

- Setting of raster operation enable function (1 cycle)

- Execution of raster operation by writing in the mask write cycle (1 cycle)

3

Row I +1 Read Data Transfer (Down Load) Serial Read

Busy (U)

DATA REGISTER

2. Serial Read Operation Starts at Location K STORAGE CELL ARRAY

DATA REGISTER

(U)

Figure 3. Logic Operation

3-79