# MOS INTEGRATED CIRCUIT $\mu$ PD485506

# LINE BUFFER 5K-WORD BY 16-BIT/10K-WORD BY 8-BIT

#### Description

The  $\mu$ PD485506 is a high speed FIFO (First In First Out) line buffer. Word organization can be changed either 5,048 words by 16 bits or 10,096 words by 8 bits.

Its CMOS static circuitry provides high speed access and low power consumption.

The  $\mu$ PD485506 can be used for one line delay and time axis conversion in high speed facsimile machines and digital copiers.

Moreover, the  $\mu$ PD485506 can execute read and write operations independently on an asynchronous basis. Thus the  $\mu$ PD485506 is suitable as a buffer for data transfer between units with different transfer rates and as a buffer for the synchronization of multiple input signals.

There are four versions, E, K, P and X. These versions operate with different specifications. Each version is identified with its lot number (refer to 7. **Example of Stamping**).

#### **Features**

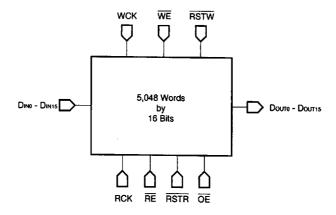

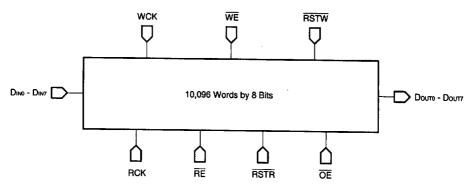

- 5,048 words by 16 bits (Word mode) /10,096 words by 8 bits (Byte mode)

- Full static operation; data hold time = infinity

- · Suitable for sampling one line of A3 size paper (16 dots/mm)

- · Asynchronous read/write operations available

- Variable length delay bits; 21 to 5,048 bits or 10,096 bits (Cycle time: 25 ns)

15 to 5,048 bits or 10,096 bits (Cycle time: 35 ns)

- Power supply voltage Vcc = 5 V ± 10 %

- All input/output TTL compatible

- · 3-state output

#### **Ordering Information**

| Part Number    | R/W Cycle Time | Package                            |

|----------------|----------------|------------------------------------|

| μPD485506G5-25 | 25 ns          | 44-pin plastic TSOP (II) (400 mil) |

| μPD485506G5-35 | 35 ns          |                                    |

The information in this document is subject to change without notice.

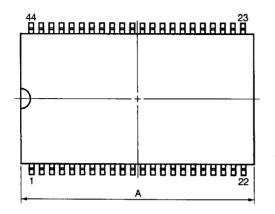

# Pin Configuration (Marking side)

#### 44-pin plastic TSOP (II) (400 mil)

| Dоито  | 0-             | 1   |     |                         |    |         | 44   | <b>├</b> ─○   | Dino  |

|--------|----------------|-----|-----|-------------------------|----|---------|------|---------------|-------|

| Dours  | 0-             | 2   |     |                         |    | ·       | 43   | <b>├</b> ─○   | DIN   |

| Dout2  | O <del>◄</del> | 3   |     |                         |    |         | 42   | <del></del> 0 | DINZ  |

| Dоитз  | 0              | 4   |     |                         |    |         | 41   |               | Dina  |

| Dout4  | 0              | 5   |     |                         |    |         | 40   | <b>←</b>      | DIN4  |

| Douts  | O <del>-</del> | 6   |     |                         |    |         | 39   |               | DINS  |

| Doute  | 0              | 7   |     |                         |    |         | 38   |               | DiNe  |

| Dоит7  | <b>~</b> —     | 8   |     |                         |    |         | 37   |               | DIN7  |

| ŌĒ     | O              | . 9 |     |                         |    |         | 36   |               | WE    |

| RE     | O -            | 10  |     | 9                       |    | , r = r | 35   |               | MD    |

| GND    | 0              | 11  |     | <u>4</u>                |    |         | 34   | <b>├</b> ──   | GND   |

| RSTR   | <b>○</b>       | 12  |     | <sub>u</sub> PD485506G5 |    |         | 33   |               | RSTW  |

| RCK    | <b>○</b>       | 13  | 100 | <br>ĝ                   |    |         | 32   | <b>├</b> ──○  | WCK   |

| Vcc    | <b>О</b>       | 14  |     | -                       |    |         | 31   |               | Vcc   |

| Douтв  | O <del></del>  | 15  |     |                         |    |         | 30   |               | DINB  |

| Dоите  | <b>○</b> -     | 16  |     |                         | 1. |         | . 29 | •             | DINO  |

| Dout10 | <b>○</b>       | 17  |     |                         |    |         | 28   |               | DIN10 |

| Doutti | <b>○</b> -     | 18  |     |                         |    |         | 27   |               | DiN11 |

| Dout12 | <b>○</b>       | 19  |     |                         |    |         | 26   |               | DiN12 |

| Dоита  | 0-             | 20  |     |                         |    |         | 25   |               | DIN13 |

| Dout14 | <b>~</b> —     | 21  |     |                         |    |         | 24   |               | DiN14 |

| Dоит15 | O <del></del>  | 22  |     |                         |    |         | 23   |               | DIN15 |

|        |                |     |     | <br>                    |    |         |      | ł             |       |

DINO to DIN15 : Data Inputs Dουτο to Dουτι5: Data Outputs WCK : Write Clock Input RCK : Read Clock Input WE : Write Enable Input RE : Read Enable Input ŌĒ : Output Enable Input **RSTW** : Reset Write Input RSTR : Reset Read Input MD : Mode Set Input : +5 V Power Supply Vcc GND : Ground

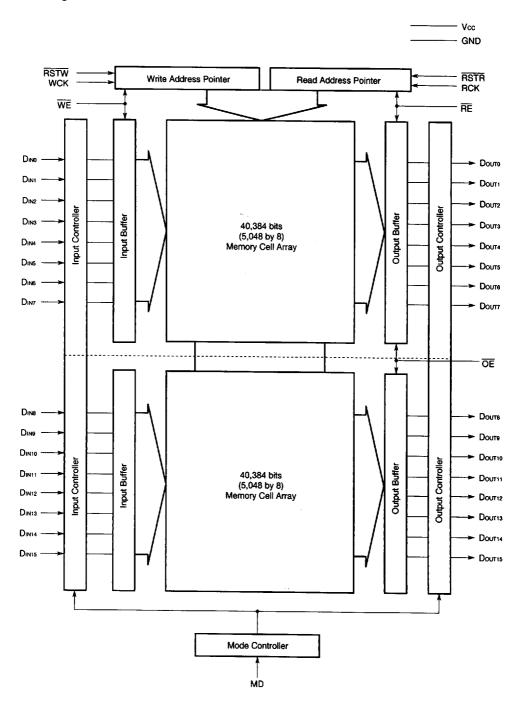

#### **Block Diagram**

# 1. Pin Function

|                    | Pin                  |                           |      |                                                                                                                                                                                                                                                                                                                      |

|--------------------|----------------------|---------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>Number      | Symbol               | Pin<br>Name               | 1/0  | Function                                                                                                                                                                                                                                                                                                             |

| 23 - 30<br>37 - 44 | DINO<br>†<br>DIN15   | Data<br>Input             | In   | Write data input pins.  The data inputs are strobed by the rising edge of WCK at the end of a cycle and the setup and hold times (tos, ton) are defined at this point.                                                                                                                                               |

| 1 - 8<br>15 - 22   | Doute<br>I<br>Doutes | Data<br>Output            | Out  | Read data output pins.  The access time is regulated from the rising edge of RCK at the beginning of a cycle and defined by two.                                                                                                                                                                                     |

| 33                 | RSTW                 | Reset<br>Write<br>Input   | ln   | Reset input pin for the initialization of the write address pointer.  The state of RSTW is strobed by the rising edge of WCK at the beginning of a cycle and the setup and hold times (tss, tsH) are defined.                                                                                                        |

| 12                 | RSTR                 | Reset<br>Read<br>Input    | In   | Reset input pin for the initialization of the read address pointer.  The state of RSTR is strobed by the rising edge of RCK at the beginning of a cycle and the setup and hold times (tas, tah) are defined.                                                                                                         |

| 36                 | WE                   | Write<br>Enable<br>Input  | În   | Write operation control signal input pin.  When $\overline{WE}$ is in the disable mode ("H" level), the internal write operation is inhibited and the write address pointer stops at the current position.                                                                                                           |

| 10                 | RE                   | Read<br>Enable<br>Input   | · In | Read operation control signal input pin.  When RE is in the disable mode ("H" level), the internal read operation is inhibited and the read address pointer stops at the current position. The data outputs remain valid for that address.                                                                           |

| 9                  | ŌĒ                   | Output<br>Enable<br>Input | In   | Output operation control signal input pin. When $\overline{\text{OE}}$ is in the disable mode ("H" level), the data out is inhibited and the output changes to high impedance. The internal read operation is executed at that time and the read address pointer incremented in synchronization with the read clock. |

| 32                 | WCK                  | Write<br>Clock<br>Input   | In   | Write clock input pin.  When WE is enabled ("L" level), the write operation is executed in synchronization with the write clock. The write address pointer is incremented simultaneously.                                                                                                                            |

| 13                 | RCK                  | Read<br>Clock<br>Input    | ln   | Read clock input pin.  When RE is enabled ("L" level), the read operation is executed in synchronization with the read clock. The read address pointer is incremented simultaneously.                                                                                                                                |

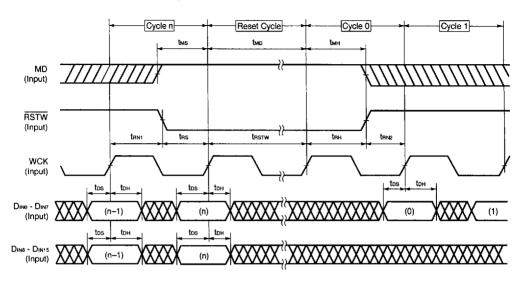

| 35                 | MD                   | Mode<br>Set<br>Input      | In   | Mode set input pin.  The level of MD gives the operation mode. When MD is in "L" level, 5,048 words by 16 bits configuration with DINO - DIN15, DOUTO - DOUT15 is enabled.  When MD is in "H" level, 10,096 words by 8 bits configuration with DINO - DIN7, DOUTO - DOUTT is enabled.                                |

#### 2. Operation Mode

$\mu$ PD485506 is a synchronous memory. All signals are strobed at the rising edge of the clock (RCK, WCK). For this reason, setup time and hold time are specified for the rising edge of the clock (RCK, WCK).

# (1) Mode Set Cycle (5,048 words by 16 bits or 10,096 words by 8 bits organization)

$\mu$ PD485506 has a capability of selecting from two operation modes by judging the MD level when  $\overline{\text{RSTW}}$  or  $\overline{\text{RSTR}}$  is enabled in the reset cycle.

| MD Level      | Bit Configuration      | Data Inputs/Outputs | Control Signal |  |

|---------------|------------------------|---------------------|----------------|--|

| " <u>L</u> ." | 5,048 words by 16 bits | Dino - Din15        | WCK, WE, RSTW  |  |

|               |                        | Doute - Dout15      | RCK, RE, RSTR  |  |

| "H"           | 10,096 words by 8 bits | Dino - Din7         | WCK, WE, RSTW  |  |

|               |                        | Dоито - Dоит7       | RCK, RE, RSTR  |  |

Caution Don't change the MD level during a reset cycle.

#### 5,048 Words by 16 Bits FIFO

#### 10,096 Words by 8 Bits FIFO

Remark Fix Dins - Dins to "L" or "H" level in the 10,096 words by 8 bits mode.

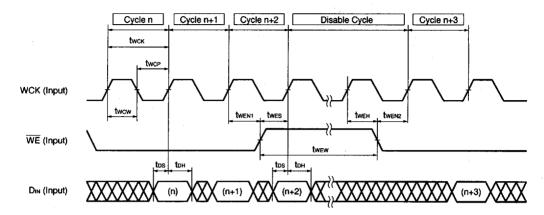

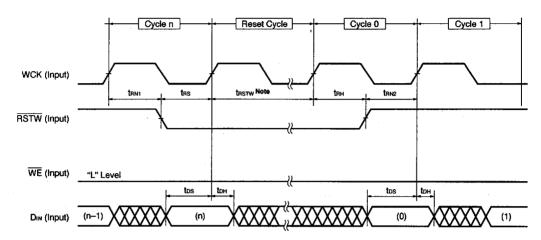

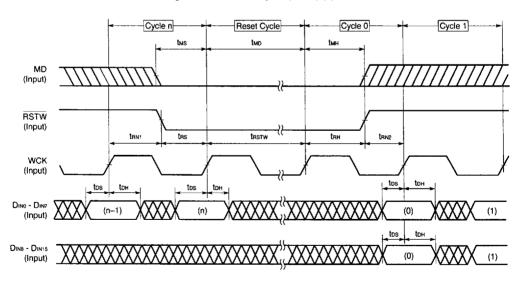

#### (2) Write Cycle

When the  $\overline{\text{WE}}$  input is enabled ("L" level), a write cycle is executed in synchronization with the WCK clock input. The data inputs are strobed by the rising edge of the clock at the end of a cycle so that read data after a one-line (5,048 bits or 10,096 bits) delay and write data can be processed with the same clock. When creating a variable length delay line by controlling  $\overline{\text{WE}}$  or  $\overline{\text{RSTW}}$ , delay bits are as follows.

| Part Number  | Cycle Time | Delay Bits                         |

|--------------|------------|------------------------------------|

| μPD485506-25 | 25 ns      | 21 to 5,048 bits/21 to 10,096 bits |

| μPD485506-35 | 35 ns      | 15 to 5,048 bits/15 to 10,096 bits |

Unless inhibited by  $\overline{\text{WE}}$ , the internal write address will automatically wrap around from 5,047 to 0 and begin incrementing again.

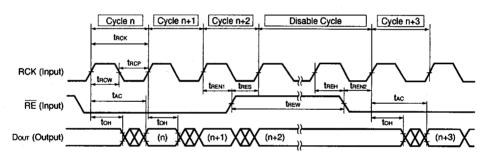

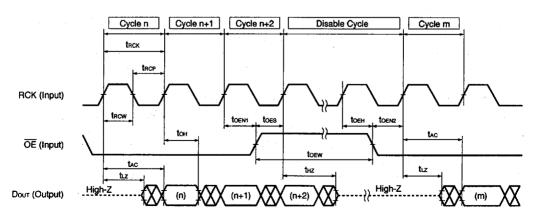

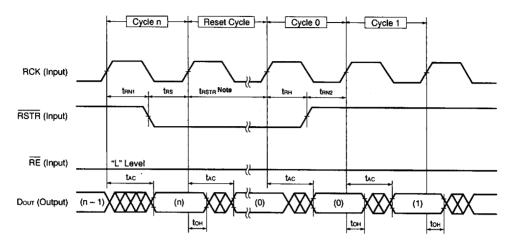

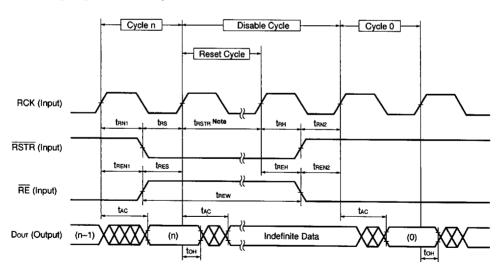

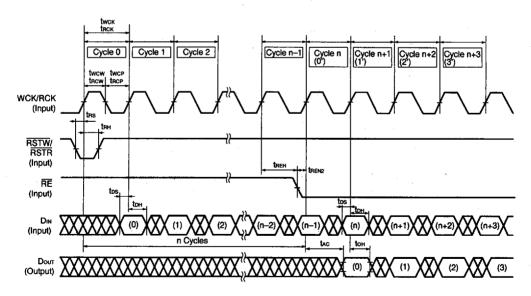

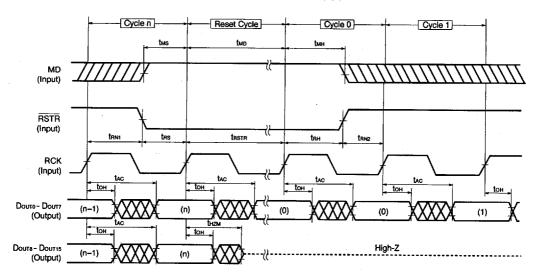

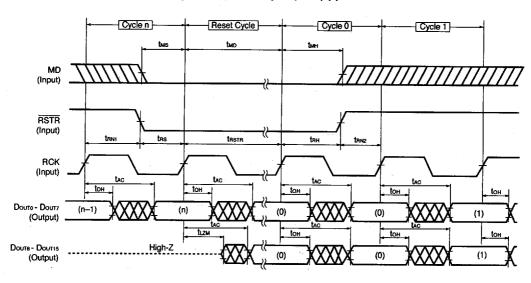

#### (3) Read Cycle

When the  $\overline{\text{RE}}$  input is enabled ("L" level), a read cycle is executed in synchronization with the RCK clock input. When the  $\overline{\text{OE}}$  input is also enabled ("L" level) at that time, data is output at tac.

When creating a variable length delay line by controlling RE or RSTR, delay bits are as follows.

| Part Number  | Cycle Time | Delay Bits                         |

|--------------|------------|------------------------------------|

| μPD485506-25 | 25 ns      | 21 to 5,048 bits/21 to 10,096 bits |

| μPD485506-35 | 35 ns      | 15 to 5,048 bits/15 to 10,096 bits |

When read and write cycles contend for the same line for a time axis conversion, etc., the old data (previous line) may be output for the last 21 bits in the case of 25 ns read cycle time, and the last 15 bits in the case of 35 ns read cycle time.

Unless inhibited by  $\overline{\text{RE}}$ , the internal read address will automatically wrap around from 5,047 to 0 and begin incrementing again.

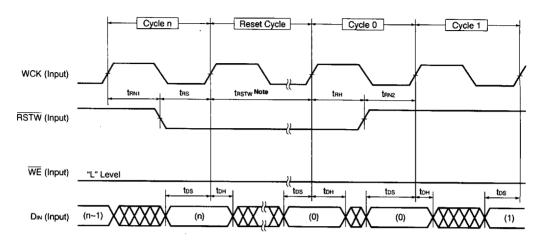

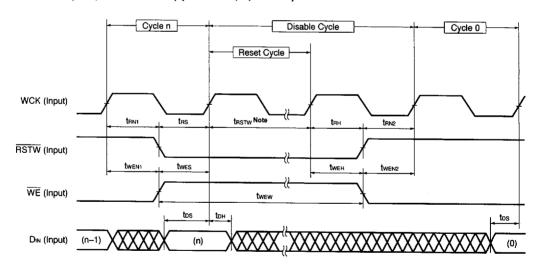

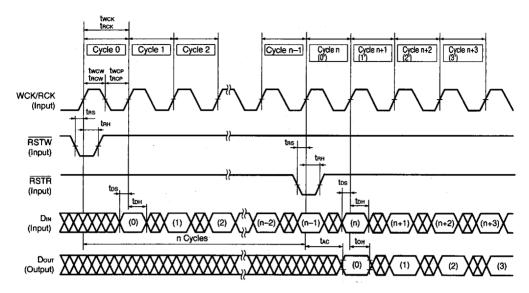

#### (4) Write Reset Cycle/Read Reset Cycle

After power up, the  $\mu$ PD485506 requires the initialization of internal circuits because the read and write address pointers are not defined at that time.

It is necessary to satisfy setup requirements and hold times as measured from the rising edge of WCK and RCK, and then input the RSTW and RSTR signals to initialize the circuit.

Caution Write and read reset cycles can be executed asynchronously. However, 1/2 cycle and 500 ns is required after a write cycle to read the data written in a cycle.

Remark Write and read reset cycles can be executed at any time and do not depend on the state of RE, WE or OE.

# 3. Electrical Specifications

· All voltages are referenced to GND.

#### **Absolute Maximum Ratings**

| Parameter                          | Symbol | Condition | Rating                            | Unit |

|------------------------------------|--------|-----------|-----------------------------------|------|

| Voltage on any pin relative to GND | VT     |           | -0.5 <sup>Note</sup> to Vcc + 0.5 |      |

| Supply voltage                     | Vcc    |           | -0.5 to +7.0                      | ٧    |

| Output current                     | lo     |           | 20                                | mA   |

| Power dissipation                  | Po     |           | 1                                 | W    |

| Operating ambient temperature      | TA     |           | 0 to +70                          | °C   |

| Storage temperature                | Tstg   |           | -55 to +125                       | °C   |

Note -3.0 V MIN. (Pulse width = 10 ns)

Caution Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

#### **Recommended Operating Conditions**

| Parameter                     | Symbol | Condition | MIN.     | TYP. | MAX.     | Unit |

|-------------------------------|--------|-----------|----------|------|----------|------|

| Supply voltage                | Vcc    |           | 4.5      | 5.0  | 5.5      | V    |

| High level input voltage      | ViH    |           | 2.4      |      | V∞ + 0.5 | V    |

| Low level input voltage       | VIL    |           | _0.3Note |      | +0.8     |      |

| Operating ambient temperature | TA     |           | 0        |      | 70       | *c   |

Note -3.0 V MIN. (Pulse width = 10 ns)

# DC Characteristics (Recommended Operating Conditions unless otherwise noted)

| Parameter                 | Symbol | Test Condition                 | MIN. | TYP.         | MAX. | Unit |

|---------------------------|--------|--------------------------------|------|--------------|------|------|

| Operating current         | loc    |                                |      |              | 140  | mA   |

| Input leakage current     | lı     | Vi = 0 to Vcc, Other Input 0 V | -10  |              | +10  | μА   |

| Output leakage current    | lo     | Vo = 0 to Vcc,                 | -10  | <del> </del> | +10  | μА   |

|                           |        | Dour: High Impedance           |      |              |      | ,    |

| High level output voltage | Voн    | lон = −1 mA                    | 2.4  |              |      | V    |

| Low level output voltage  | Vol    | lot = 2 mA                     |      |              | 0.4  | v    |

# Capacitance (T<sub>A</sub> = +25 °C, f = 1 MHz)

| Parameter          | Symbol | Test Condition | MIN. | TYP. | MAX. | Unit |

|--------------------|--------|----------------|------|------|------|------|

| Input capacitance  | Cı     |                |      |      | 10   | рF   |

| Output capacitance | Co     |                |      |      | 10   | pF   |

441

# AC Characteristics (Recommended Operating Conditions unless otherwise noted) Notes 1, 2, 3

|                                          |        | μPD485506-25 |      | μPD485506-35 |      | 11.5 | Natas |

|------------------------------------------|--------|--------------|------|--------------|------|------|-------|

| Parameter                                | Symbol | MIN.         | MAX. | MIN.         | MAX. | Unit | Notes |

| Write clock cycle time                   | twck   | 25           |      | 35           |      | ns   |       |

| Write clock pulse width                  | twcw   | 11           |      | 12           |      | ns   |       |

| Write clock precharge time               | twop   | 11           |      | 12           |      | ns   |       |

| Read clock cycle time                    | trck   | 25           |      | 35           |      | ns   |       |

| Read clock pulse width                   | trow   | 11           |      | 12           |      | ns   |       |

| Read clock precharge time                | trop   | 11           |      | 12           |      | ns   |       |

| Access time                              | tac    |              | 18   |              | 25   | กร   |       |

| Output hold time                         | tон    | 5            |      | 5            |      | ns   |       |

| Output low-impedance time                | tız    | 5            | 18   | 5            | 25   | ns   | 4     |

| Output high-impedance time               | tHZ    | 5            | 18   | 5            | 25   | ns   | 4     |

| Input data setup time                    | tos    | 7            |      | 10           |      | ns   |       |

| Input data hold time                     | tон    | 3            |      | 3            |      | ns   |       |

| MD Set setup time                        | tms    | 20           |      | 20           |      | ns   | . :   |

| MD Set hold time                         | 1мн    | 10           |      | 10           |      | ns   |       |

| MD Set time                              | tMD    | 0            |      | 0            |      | ns   | 5     |

| Output low-impedance time (Mode change)  | tızm   | 5            | 18   | 5            | 25   | ns   | 4     |

| Output high-impedance time (Mode change) | thzm   | 5            | .18  | 5            | 25   | ns   | 4     |

| RSTW/RSTR Setup time                     | trs    | 7            |      | 10           |      | กร   | 6     |

| RSTW/RSTR Hold time                      | tкн    | 3            |      | 3            | ."   | ns   | 6     |

| RSTW/RSTR Deselected time (1)            | trnı   | 3            |      | 3            |      | ns   | 7     |

| RSTW/RSTR Deselected time (2)            | tnn2   | 7            |      | 10           |      | ns   | 7     |

| WE Setup time                            | twes   | 7            |      | 10           |      | ns   | 8     |

| WE Hold time                             | tweн   | 3            |      | 3            |      | ns   | 8     |

| WE Deselected time (1)                   | twen1  | 3            |      | 3            |      | ns   | 9     |

| WE Deselected time (2)                   | twen2  | 7            |      | 0f           |      | ns   | 9     |

| RE Setup time                            | tres   | 7            |      | 10           |      | ns   | 10    |

| RE Hold time                             | tren   | . 3          |      | 3            |      | กร   | 10    |

| RE Deselected time (1)                   | trens  | 3            |      | 3            |      | ns   | 11    |

| RE Deselected time (2)                   | tren2  | 7            |      | 10           |      | ns   | 11    |

| OE Setup time                            | toes   | 7            |      | 10           |      | ns   | 10    |

| OE Hold time                             | tоєн   | 3            |      | 3            |      | ns   | 10    |

| OE Deselected time (1)                   | toen1  | 3            |      | 3            |      | ns   | 11    |

| OE Deselected time (2)                   | toen2  | 7            |      | 10           |      | ns   | 11    |

| WE Disable time                          | twew   | 0            |      | 0            |      | ms   |       |

| RE Disable time                          | trew   | 0            |      | 0            |      | ms   |       |

| OE Disable time                          | toew   | 0            |      | 0            |      | ms   |       |

| Write reset time                         | trstw  | 0            |      | 0            | -    | ms   |       |

| Read reset time                          | teste  | 0            |      | 0            |      | ms   |       |

| Transition time                          | tτ     | 3            | 35   | 3            | 35   | ns   |       |

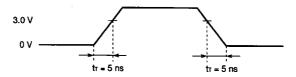

- Notes 1. AC measurements assume  $t\tau = 5$  ns.

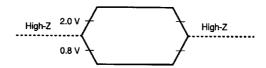

- 2. AC Characteristics test condition

#### Input Timing Specification

#### **Output Timing Specification**

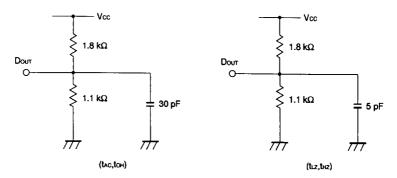

#### Output Loads for Timing

- 3. Input timing reference levels = 1.5 V.

- tLz, tHz, tLzM and tHzM are measured at ±200 mV from the steady state voltage. Under any conditions, tLz ≥ tHz and tLzM ≥ tHzM.

- 5. Mode set signal (MD) must be input synchronously with write reset signal (tastw period) or read reset signal (tastw period). Under this condition, tastw = tmp (tastw = tmp).

- 6. If either tas or tax is less than the specified value, reset operations are not guaranteed.

- If either than or that is less than the specified value, reset operations may extend to cycles preceding or following the period of reset operations.

- 8. If either twes or twen is less than the specified value, write disable operations are not guaranteed.

- 9. If either twent or twenz is less than the specified value, internal write disable operations may extend to cycles preceding or following the period of write disable operations.

- 10. If either tres or treen, toes or toen is less than the specified value, read disable operations are not guaranteed.

- 11. If either trent or trenz, toent or toenz is less than the specified value, internal read disable operations may extend to cycles preceding or following the period of read disable operations.

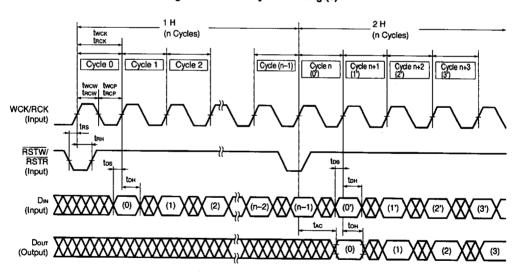

#### **Write Cycle**

Remark RSTW = "H" level

#### Read Cycle (RE Control)

Remark OE = "L" level, RSTR = "H" level

#### Read Cycle (OE Control)

Remark RE = "L" level, RSTR = "H" level

#### Write Reset Cycle (WE Controlled 1) (Versions E, K and P)

Note In write reset cycle, reset operation is executed even without a reset cycle (trestw). WCK can be input any number of times in a reset cycle.

# Write Reset Cycle (WE Controlled 2) (Versions E, K, P and X)

Note In write reset cycle, reset operation is executed even without a reset cycle (thestw). WCK can be input any number of times in a reset cycle.

# Write Reset Cycle (WE Controlled 3) (Version X)

Note In write reset cycle, reset operation is executed even without a reset cycle (trestw).

WCK can be input any number of times in a reset cycle.

#### Read Reset Cycle (RE Controlled 1)

Note In read reset cycle, reset operation is executed even without a reset cycle (trastri). RCK can be input any number of times in a reset cycle.

Remark OE = "L" level

#### Read Reset Cycle (RE Controlled 2)

Note In read reset cycle, reset operation is executed even without a reset cycle (tasta).

RCK can be input any number of times in a reset cycle.

Remark OE = "L" level

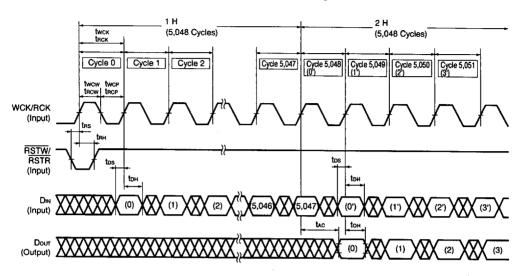

#### 4. Application

#### · 1 H Delay Line

$\mu$ PD485506 easily allows a 1 H (5,048 bits/10,096 bits) delay line (see Figure 1, 2). It is also possible to change the number of delay bits depending on the cycle time as follows.

| Part Number  | Cycle Time | Delay Bits                         |

|--------------|------------|------------------------------------|

| μPD485506-25 | 25 ns      | 21 to 5,048 bits/21 to 10,096 bits |

| μPD485506-35 | 35 ns      | 15 to 5,048 bits/15 to 10,096 bits |

To change the number of delay bits, you can choose the one of the following methods.

#### Adjustments of the number of delay bits

- (1) Reset the cycle proportionate to the delay length (Figure 3).

- (2) Shift the input timing of write reset (RSTW) and read reset signals (RSTR) according to the delay length (Figure 4).

- (3) Shift the address by disabling WE or RE for the period proportionate to the delay length (Figure 5).

Caution After power up, the  $\mu$ PD485506 requires the initialization of internal circuits because the read and write address pointers are not defined at that time.

Figure 1 1 H Delay Line Circuit

Figure 2 1 H Delay Line Timing

Remark RE, WE, OE = "L" level

Figure 3 n-Bit Delay Line Timing (1)

Remark RE, WE, OE = "L" level

Figure 4 n-Bit Delay Line Timing (2)

Remark RE, WE, OE = "L" level

Figure 5 n-Bit Delay Line Timing (3)

Remark WE, OE = "L" level

Figure 6 Mode Set Cycle (Write) (1)

Remark WE = "L" level

Figure 7 Mode Set Cycle (Write) (2)

Remark WE = "L" level

Figure 8 Mode Set Cycle (Read) (1)

Remark RE, OE = "L" level

Figure 9 Mode Set Cycle (Read) (2)

Remark  $\overline{RE}$ ,  $\overline{OE}$  = "L" level .

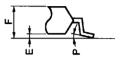

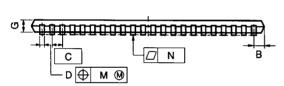

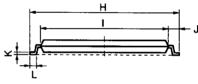

#### 5. Package Drawing

# 44 PIN PLASTIC TSOP(II) (400 mil)

detail of lead end

#### NOTE

Each lead centerline is located within 0.13 mm (0.005 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS                       | INCHES         |

|------|-----------------------------------|----------------|

| Α    | 18.63 MAX.                        | 0.734 MAX.     |

| В    | 0.93 MAX.                         | 0.037 MAX.     |

| С    | 0.8 (T.P.)                        | 0.031 (T.P.)   |

| D    | 0.32 +0.08                        | 0.013±0.003    |

| E    | 0.1±0.05                          | 0.004±0.002    |

| F    | 1.2 MAX.                          | 0.048 MAX.     |

| G    | 0.97                              | 0.038          |

| Н    | 11.76±0.2                         | 0.463±0.008    |

|      | 10.16±0.1                         | 0.400±0.004    |

| J    | 0.8±0.2                           | 0.031 + 0.009  |

| K    | 0.145 <sup>+0.025</sup><br>-0.015 | 0.006±0.001    |

| L    | 0.5±0.1                           | 0.020+0.004    |

| М    | 0.13                              | 0.005          |

| N    | 0.10                              | 0.004          |

| Р    | 3°+7°                             | 3°+7°          |

|      |                                   | S44G5-80-7.1F5 |

S44G5-80-7JF5

# 6. Recommended Soldering Conditions

Please consult with our sales offices for soldering conditions of the µPD485506.

**Type of Surface Mount Device**

$\mu$ PD485506G5: 44-pin plastic TSOP (II) (400 mil)

#### 7. Example of Stamping

Letter E in the fifth character position in a lot number signifies version E, letter K, version K, letter P, version P, and letter X, version X.