# Analog/Digital Mixed ASIC

# MIXED SIGNAL ASIC MA-8A, MA-9 Family

# **CONTENTS**

| Mixed Signal Applications 3       |

|-----------------------------------|

| Mixed Signal ASIC Product Lines 5 |

| MA-8A 8                           |

|                                   |

| MA-9 Family 21                    |

|                                   |

| Packages 36                       |

NEC Electronics' mixed signal solutions Taking on New Challenges Toward the Next Generation

# **Mixed Signal Applications**

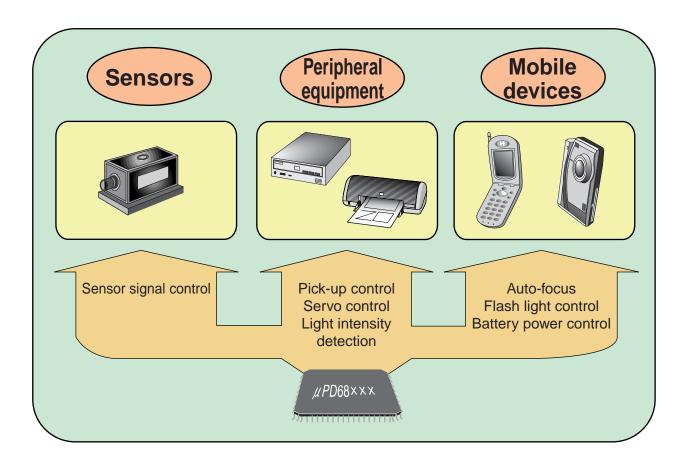

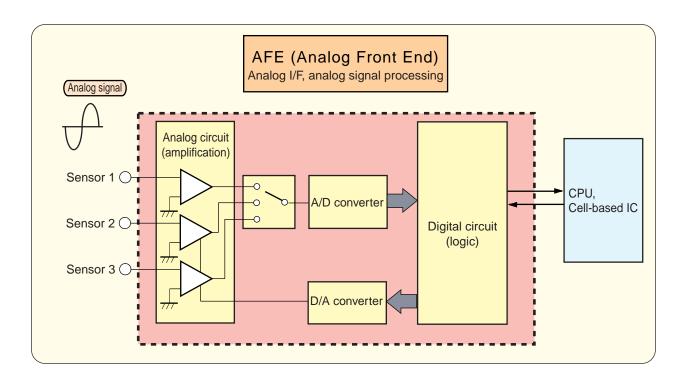

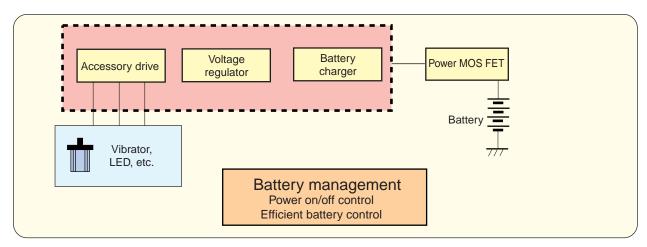

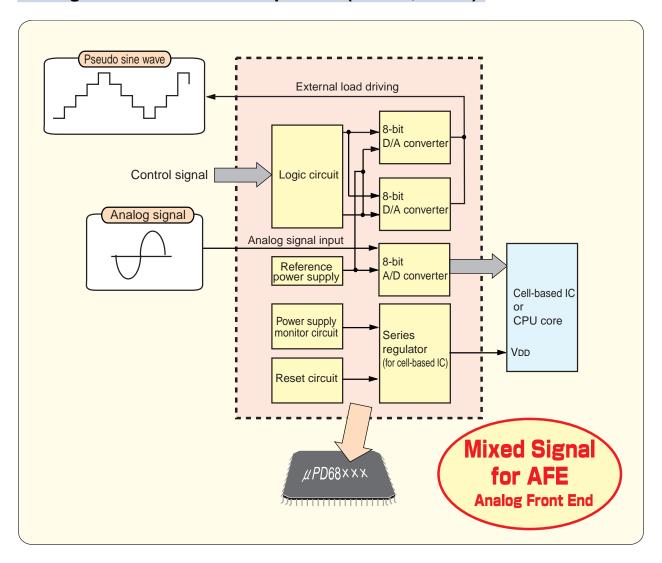

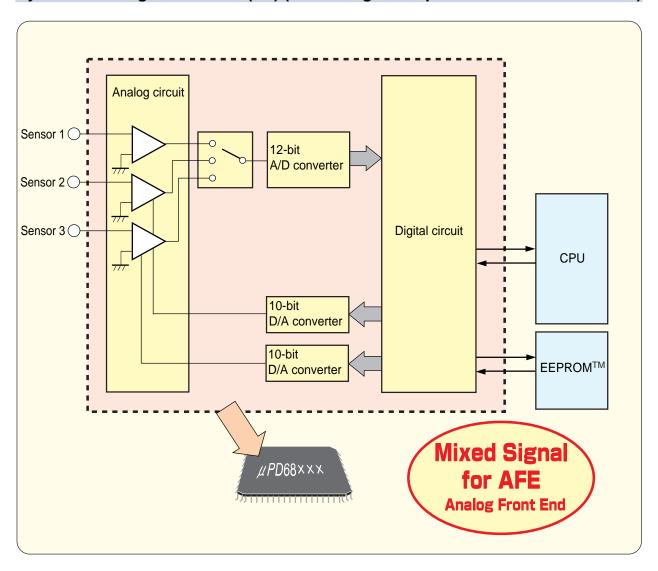

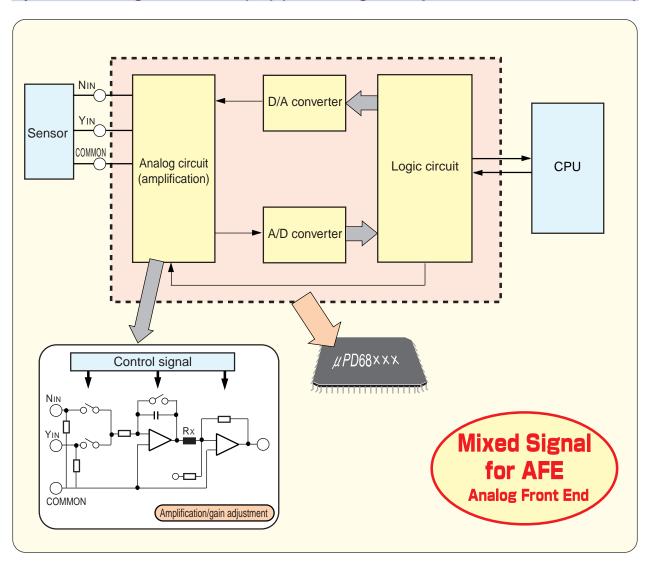

Mixed signal ASICs enable higher quality and a better cost performance in AFE (analog front end) circuits and battery management circuits for applications such as sensors, PC peripheral equipment, and mobile devices.

# **Application Concept**

Applications dealing with "minute analog signal input in a wide band" require signal amplifiers or analog-digital arithmetic circuits (analog front end: AFE) for the analog interface. Also, for mobile equipment, the need to extend the battery life means an improved power efficiency is essential.

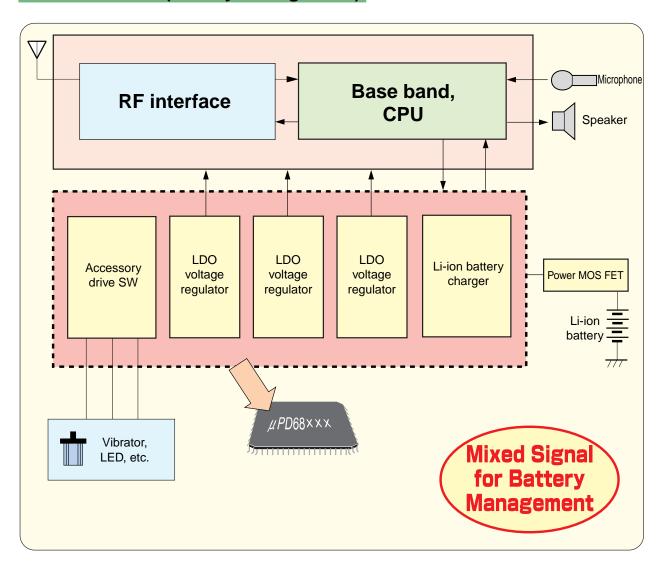

NEC Electronics provides a custom-built battery management IC for cellular phones and other mobile applications.

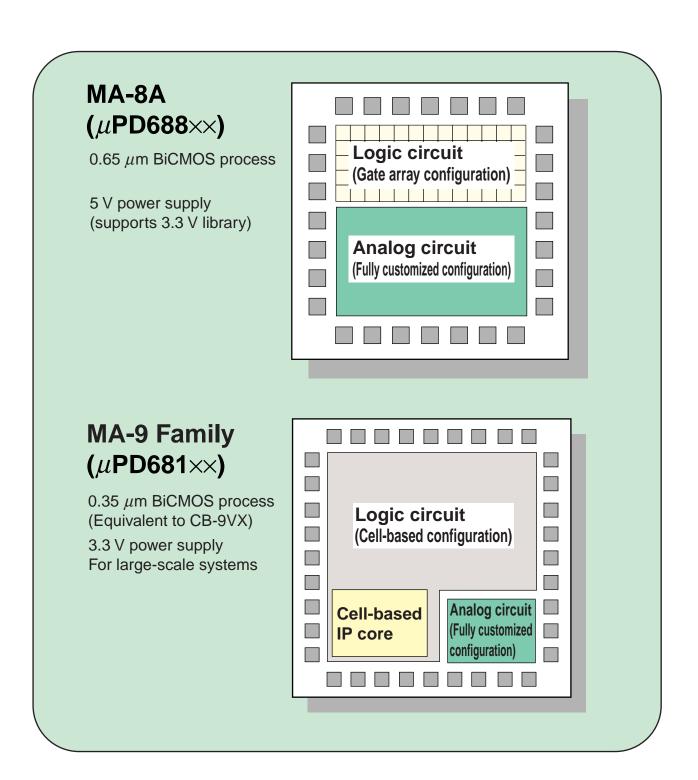

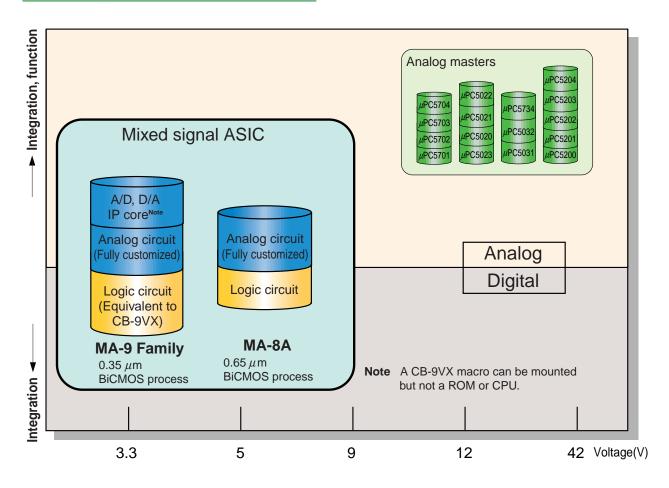

## **Mixed Signal ASIC Product Lines**

NEC Electronics offers mixed signal ASICs that employ a BiCMOS process with a process rule of  $0.65\,\mu\text{m}$  to  $0.35\,\mu\text{m}$ . Furthermore, the  $0.35\,\mu\text{m}$  BiCMOS can incorporate our  $0.35\,\mu\text{m}$  cell-based IC CB-9 Family VX Type analog core.

# **Mixed Signal ASIC Product Lines**

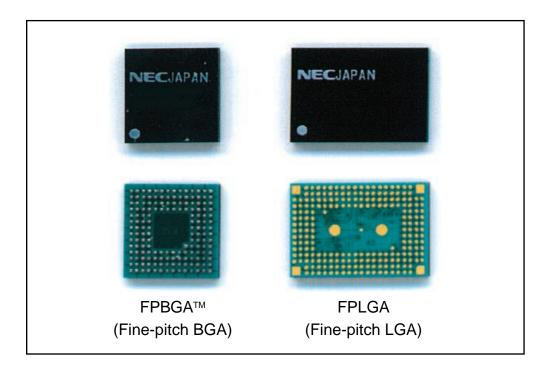

## **Support of Small-Scale Packages**

In addition to conventional mold packages, various CSPs (chip size packages) are available to support set downsizing.

# MA-8A

## **Features**

## Support of digital/analog mixed circuits

By employing the latest BiCMOS process, the MA-8A realizes the integration of a 0.65  $\mu$ m CMOS gate array and analog ASIC (analog master) on a single chip.

## Analog block element configuration prioritizing circuit functions

Analog circuits that mix bipolar transistors and CMOS transistors can be created through the use of the BiCMOS process:

High input impedance operational amplifiers Sample and hold circuits Analog switches, etc.

## Simple design and short development time

The logic block can be easily developed with OPENCAD™ (NEC Electronics' original CAE tool).

Furthermore, a short development time can be achieved, which is another advantage of ASICs.

# **Application Fields**

The MA-8A can be used to integrate analog/digital mixed circuits applied to multimedia and various other fields on one chip.

# PC peripheral equipment

- ODSCs, single-lens reflex cameras Flash light control, zoom lens control

- Storage equipmentServo controller

- OLCD panels (active matrix)

Grayscale power supply controller

### Sensor modules

- Geomagnetic sensors (cellular phone GPS, etc.)

- ○Gyro sensors

(compensating for hand-shake in DSC, DVC)

OMagnetic sensors (DC motor control, etc.)

# **MA-8A Application Examples**

## **Cellular Phones (Battery Management)**

# Impedance conversion (Amplification) Comparison Logic circuit DC motor Crystal 7/7 resonator Oscillator As many as there are motors Reference voltage adjustment Temperature and other detectors DC motor encoder circuit **Mixed Signal** #PD68xxx for AFE **Analog Front End**

## Digital Still Cameras, Single Lens Reflex Cameras (Zoom Lens Control)

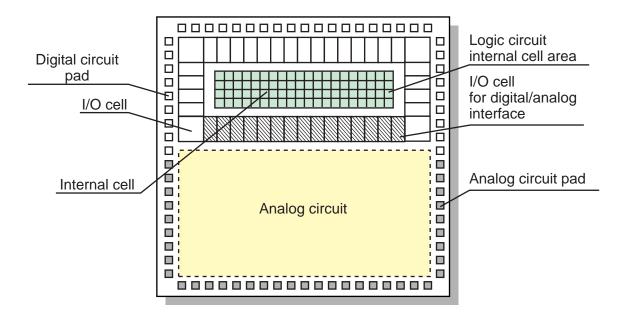

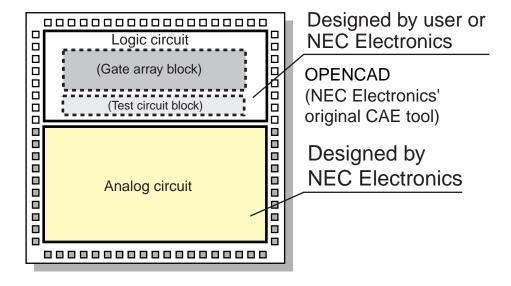

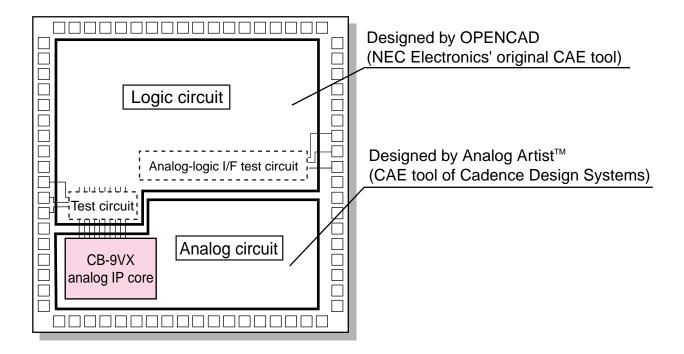

# **Chip Configuration**

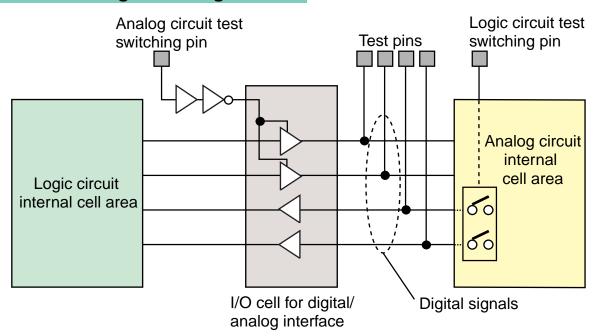

The MA-8A is mainly composed of a logic circuit (gate array block) and an analog circuit. The I/O cells for the digital/analog interface perform input/output of digital signals between the logic circuit and the analog circuit.

## I/O Cells for Digital/Analog Interface

# **Basic Specifications**

## **Logic Circuit**

| Part number    |                                  | $\mu$ PD688XX                            |  |

|----------------|----------------------------------|------------------------------------------|--|

| Process        |                                  | 0.65 μm BiCMOS process                   |  |

| Supply voltage |                                  | 5.0 V ±0.5 V (I/O block, internal gates) |  |

| Interface leve | ıl                               | CMOS, TTL                                |  |

|                | Internal gates <sup>Note 1</sup> | 190 ps (TYP.)                            |  |

| Delay time     | Input bufferNote 2               | 340 ps (TYP.)                            |  |

|                | Output bufferNote 3              | 2.13 ns (TYP.)                           |  |

Notes 1. Value assuming 2-input NAND power gate, fan-out 1, and wiring length 0.6 mm/1 pin pair.

- 2. Value assuming fan-out 2, wiring length 0.6 mm/1 pin pair.

- 3. Value assuming load capacitance 15 pF, block name FO01.

Remark The logic circuit characteristics are the same as those of NEC Electronics' CMOS-8 Family.

## **Analog Circuit**

| Part number                          |                          | μ <b>PD688</b> XX                                            |  |

|--------------------------------------|--------------------------|--------------------------------------------------------------|--|

| Process                              |                          | 0.65 μm BiCMOS process                                       |  |

| Supp                                 | oly voltage              | 5.0 V ±0.5 V                                                 |  |

|                                      | NPN type                 | $f_T$ = 10 GHz, $h_{FE}$ = 80 (all TYP.)                     |  |

| Transistors                          | PNP type (lateral)       | $f_T$ = 10 MHz, $h_{FE}$ = 70 (all TYP.)                     |  |

|                                      | MOS                      | N-ch type, P-ch type for analog circuit                      |  |

| Polysilicon resistor <sup>Note</sup> |                          | Absolute precision: ±20%, relative precision: ±2% (all MAX.) |  |

| Capacitor (MC                        | OS type) <sup>Note</sup> | Absolute precision: ±15%, relative precision: ±2% (all MAX.) |  |

Note Values indicated are for reference only. The relative precision applies only to when the element is positioned in an adjacent location.

# **Electrical Specifications**

## **Absolute Maximum Ratings**

| Item                                 | Symbol  | Conditions              | Ratings                       | Unit |

|--------------------------------------|---------|-------------------------|-------------------------------|------|

| Supply voltage                       | VDD,VCC |                         | -0.5 to +6.0                  | V    |

| Input/output voltage (logic circuit) | Vı/Vo   |                         | −0.5 to V <sub>DD</sub> + 0.5 | V    |

| Input current (logic circuit)        | lı      |                         | 20                            | mA   |

| Output current (logic circuit)       | lo      | IoL = 3 mA              | 10                            | mA   |

|                                      |         | IoL = 6 mA              | 15                            | mA   |

|                                      |         | IoL = 9 mA              | 20                            | mA   |

|                                      |         | loL = 12 mA             | 30                            | mA   |

|                                      |         | lo <sub>L</sub> = 18 mA | 40                            | mA   |

|                                      |         | loL = 24 mA             | 60                            | mA   |

| Operating ambient temperature        | TA      |                         | -40 to +85                    | °C   |

| Storage temperature                  | Tstg    |                         | -65 to +150                   | °C   |

Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

## Definition of absolute maximum rating terms

| Item                          | Symbol                                                                                                                                      | Meaning                                                                                                                 |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Supply voltage                | V <sub>DD</sub>                                                                                                                             | The range of voltage that, if applied to the V <sub>DD</sub> pin, will not cause destruction or lower reliability.      |

| Input voltage                 | Vı                                                                                                                                          | The range of voltage that, if applied to the input pin, will not cause destruction or lower reliability.                |

| Output voltage                | Vo                                                                                                                                          | The range of voltage that, if applied to the output pin, will not cause destruction or lower reliability.               |

| Input current                 | li                                                                                                                                          | The absolute value of current capacity that, if applied to the input pin, will not cause latchup to occur.              |

| Output current                | The absolute value of DC current capacity that, if output from or input to the output pin, will not cause destruction or lower reliability. |                                                                                                                         |

| Operating ambient temperature | TA                                                                                                                                          | Range of ambient temperature in which normal logical operation will occur.                                              |

| Storage temperature           | Tstg                                                                                                                                        | Range of pin temperature that will not cause destruction or lower reliability when voltage and current are not applied. |

14

## **Recommended Operating Range (Logic Circuit)**

## Standard specification CMOS interface conditions

$V_{DD} = 5 \text{ V} \pm 10\%$ ,  $T_A = -40 \text{ to } +85^{\circ}\text{C}$  ( $T_J = -40 \text{ to } +125^{\circ}\text{C}$ )

| Item                     | Symbol          | Conditions                    | MIN                | TYP | MAX                | Unit |

|--------------------------|-----------------|-------------------------------|--------------------|-----|--------------------|------|

| Supply voltage           | V <sub>DD</sub> |                               | 4.5                | 5.0 | 5.5                | V    |

| High-level input voltage | ViH             |                               | 0.7V <sub>DD</sub> |     | V <sub>DD</sub>    | V    |

| Low-level input voltage  | VIL             |                               | 0                  |     | 0.3V <sub>DD</sub> | V    |

| Positive trigger voltage | VP              | CMOS interface                | 1.80               |     | 4.00               | V    |

| Negative trigger voltage | Vn              |                               | 0.60               |     | 3.10               | V    |

| Hysteresis voltage       | Vн              |                               | 0.30               |     | 1.50               | V    |

| High-level input voltage | ViH             |                               | 2.29               |     | V <sub>DD</sub>    | V    |

| Low-level input voltage  | VIL             |                               | 0                  |     | 0.77               | V    |

| Positive trigger voltage | VP              | TTL interface                 | 1.15               |     | 2.54               | V    |

| Negative trigger voltage | Vn              |                               | 0.59               |     | 1.85               | V    |

| Hysteresis voltage       | Vн              |                               | 0.27               |     | 1.50               | V    |

| Input rise time          | tri             | Namedianut                    | 0                  |     | 200                | ns   |

| Input fall time          | tfi             | Normal input                  | 0                  |     | 200                | ns   |

| Input rise time          | tri             | Coloriu i con Note            | 0                  |     | 10                 | ms   |

| Input fall time          | tfi             | Schmitt input <sup>Note</sup> | 0                  |     | 10                 | ms   |

Note Do not use this for the clock signal.

**Remark** If a signal with a long rise/fall time is input, use a Schmitt trigger input buffer to prevent malfunction due to noise superimposed on the signal line.

Fluctuation of power caused by simultaneous operation of output buffers lowers the capability of the Schmitt trigger input buffer, and therefore, care must be exercised in laying out the pins.

Pamphlet A13326EJ2V0PF 15

## Standard specification TTL interface conditions

$V_{DD} = 5 \text{ V} \pm 10\%$ ,  $T_A = 0 \text{ to } +70^{\circ}\text{C} \text{ (T}_J = 0 \text{ to } +100^{\circ}\text{C)}$

| ltem                     | Symbol          | Conditions                    | MIN                | TYP | MAX                | Unit |

|--------------------------|-----------------|-------------------------------|--------------------|-----|--------------------|------|

| Supply voltage           | V <sub>DD</sub> |                               | 4.5                | 5.0 | 5.5                | V    |

| High-level input voltage | ViH             |                               | 0.7V <sub>DD</sub> |     | V <sub>DD</sub>    | V    |

| Low-level input voltage  | VIL             |                               | 0.0                |     | 0.3V <sub>DD</sub> | V    |

| Positive trigger voltage | VP              | CMOS interface                | 1.90               |     | 4.00               | V    |

| Negative trigger voltage | Vn              |                               | 0.63               |     | 3.10               | V    |

| Hysteresis voltage       | Vн              |                               | 0.31               |     | 1.50               | V    |

| High-level input voltage | ViH             |                               | 2.20               |     | V <sub>DD</sub>    | V    |

| Low-level input voltage  | VIL             |                               | 0.0                |     | 0.8                | V    |

| Positive trigger voltage | VP              | TTL interface                 | 1.20               |     | 2.40               | V    |

| Negative trigger voltage | Vn              |                               | 0.60               |     | 1.80               | V    |

| Hysteresis voltage       | Vн              |                               | 0.30               |     | 1.50               | V    |

| Input rise time          | tri             | Normal input                  | 0                  |     | 200                | ns   |

| Input fall time          | tfi             | normal input                  | 0                  |     | 200                | ns   |

| Input rise time          | tri             | Schmitt input <sup>Note</sup> | 0                  |     | 10                 | ms   |

| Input fall time          | tfi             | Sciiiiiii iiput               | 0                  |     | 10                 | ms   |

Note Do not use this for the clock signal.

**Remark** If a signal with a long rise/fall time is input, use a Schmitt trigger input buffer to prevent malfunction due to noise superimposed on the signal line.

Fluctuation of power caused by simultaneous operation of output buffers lowers the capability of the Schmitt trigger input buffer, and therefore, care must be exercised in laying out the pins.

16 Pamphlet A13326EJ2V0PF

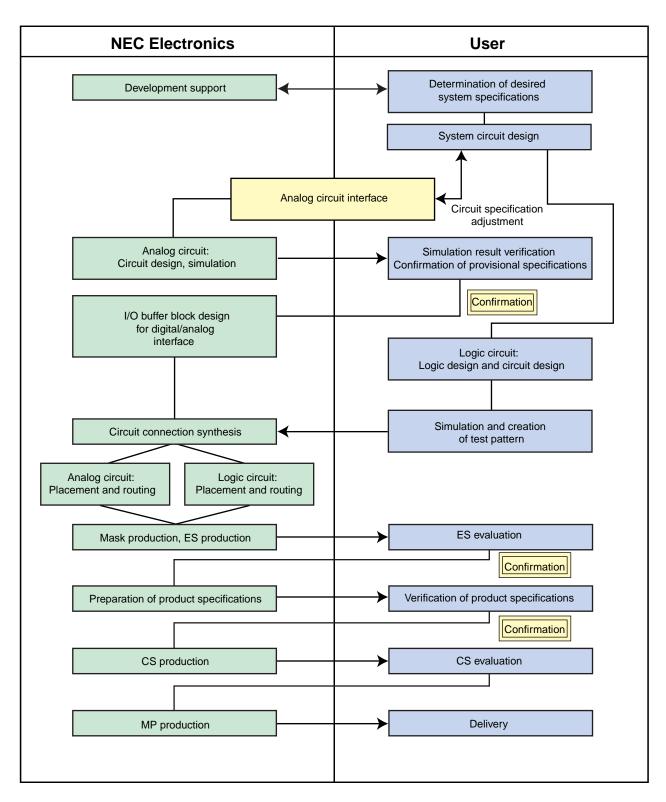

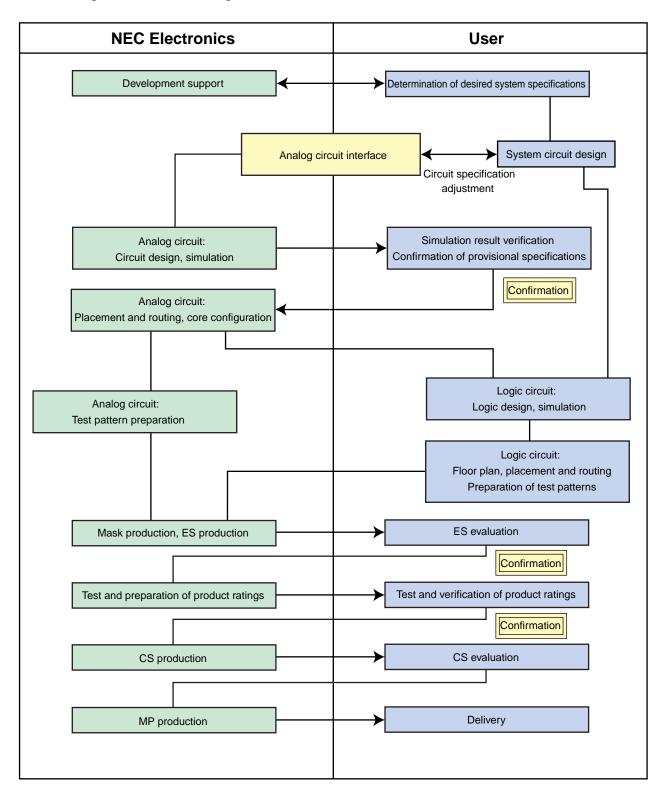

## **MA-8A Development Procedure**

Development of the MA-8A is carried out by both the user and NEC Electronics by dividing the work between gate array design using the design resources of the user and circuit design applying NEC Electronics' analog ASIC technology, which results in a shorter development time.

The transition of development work between the user and NEC Electronics is called "interfacing." The interface level depends on how far the user carries out development work and what data the user provides to NEC Electronics.

- Circuit diagram level interface

In this development method, the user takes care of system circuit design, and the subsequent LSI circuit design and simulation are performed by NEC Electronics.

- Simulation level interface In this development method, the user is in charge of development from circuit design to simulation using engineering workstations (EWS) and CAD system simulation tools, and NEC Electronics is responsible for the rest of the development work.

The MA-8A is divided into a logic circuit and an analog circuit, and two kinds of development methods combining the above-described interface levels are available.

|   | Development Method                                  | System Circuit<br>Design | LSI Circuit<br>Design | Circuit<br>Synthesis | Layout Design          | ES Production |

|---|-----------------------------------------------------|--------------------------|-----------------------|----------------------|------------------------|---------------|

| 1 | [Logic circuit]<br>Simulation level interface       |                          | (User side)           |                      | (NEC Electronics side) |               |

|   | [Analog circuit]<br>Circuit diagram level interface |                          |                       |                      | (NEO Electronics side) |               |

| 2 | [Logic circuit] Circuit diagram level interface     |                          |                       |                      |                        |               |

|   | [Analog circuit] Circuit diagram level interface    |                          |                       |                      |                        |               |

1 Logic circuit: Simulation level interface Analog circuit: Circuit diagram level interface

2 Logic circuit: Circuit diagram level interface Analog circuit: Circuit diagram level interface

## **MA-8A Development Tools**

The MA-8A provides development tools that support ASIC development by the user for the logic circuits. NEC Electronics will take charge of circuit design for the analog circuits according to the user's specifications.

### Caution

A pin should be drawn out as a test pin where the analog circuit is connected to the logic circuit. Configure the area where the analog circuit is connected to the logic circuit, as well as the test circuit of the logic circuit in the test circuit block.

20

# 0.35 μm Mixed Signal ASIC MA-9 Family

## **Features**

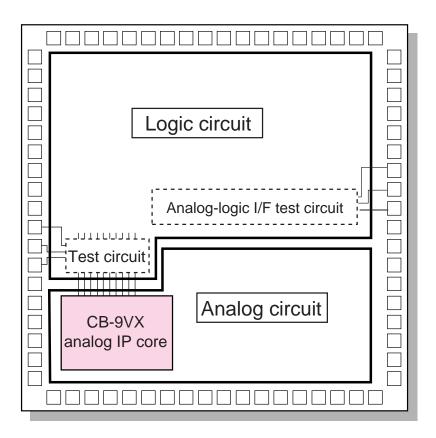

The MA-9 Family ( $\mu$ PD681XX) consists of mixed signal ASICs that aim for system-on-a-chip through the use of a leading-edge 0.35  $\mu$ m BiCMOS process pioneered by NEC Electronics.

### Support of analog IP core

The MA-9 Family can utilize analog circuit design resources such as the A/D converter and D/A converter of NEC Electronics' 0.35  $\mu$ m cell-based IC.

## Leading-edge BiCMOS process

High-speed digital circuits and high-accuracy, sophisticated analog circuits can now be realized on a single chip by employing NEC Electronics' leading-edge 0.35  $\mu$ m BiCMOS process.

## Low power consumption

A low power consumption is achieved for LSIs by employing a low-voltage operation process (3.3 V).

## Flexible mixed signal development environment

NEC Electronics' development environment for the CB-9 Family VX Type cell-based IC can be used for the internal logic.

## **Application Fields**

Since CB-9 and later submicron cell-based ICs cannot configure an analog circuit, they may not support CB solutions. Furthermore, if they incorporate an A/D converter and D/A converter, a good cost performance is not possible due to the restrictions on cell-based IC allocation.

In these cases, by integrating the entire cell-based IC, or the A/D converter, D/A converter, and analog circuit blocks on a single chip, the MA-9 Family provides the user with the best solution.

### Storage equipment

O Servo/write control

DVD-ROM/RAM drives

CD-R/W drives

## PC peripheral terminals

- Analog front end (A/D converter, D/A converter, analog circuit)

- OSensor signal amplification Color LCD panels Printers PDAs

### Sensor modules

- Geomagnetic sensors (cellular phone GPS, etc.)

- ○Gyro sensors (compensating for hand-shake in DSC, DVC)

- OMagnetic sensors (DC motor control, etc.)

# **MA-9 Family Application Examples**

## **Analog Front End for PC Peripherals (Printer, Tablet)**

## Gyro Sensor/Magnetic Sensor (1/2) (Sensor Signal Amplification + A/D Conversion)

## Gyro Sensor/Magnetic Sensor (2/2) (Sensor Signal Amplification + A/D Conversion)

# **Chip Configuration**

## Logic circuit

- OUser logic (logic gates)

- A/D or D/A converter macro (CB-9 Family VX Type)<sup>Note</sup>

- Test circuit

Test circuit including analog-logic I/F block

Note Neither a CPU nor ROM can be mounted.

## **Analog circuit**

Oconfigured by operational amplifier, comparator, reference power supply, analog switch, etc.

NEC Electronics designs the circuit according to the user's circuit specifications.

# **Basic Specifications**

## **Logic Circuit**

| Part number                      |                                  | μ <b>PD681</b> ××                                         |  |

|----------------------------------|----------------------------------|-----------------------------------------------------------|--|

| Process                          |                                  | 0.35 μm BiCMOS process                                    |  |

| Supply voltage                   |                                  | $3.3\text{V}\pm\!0.3\text{V}$ (I/O block, internal gates) |  |

| Maximum integration (logic only) |                                  | 1.7 million gates (usable)                                |  |

| Interface leve                   | I                                | LVTTL                                                     |  |

|                                  | Internal gates <sup>Note 1</sup> | 114 ps (TYP.)                                             |  |

| Delay time                       | Input bufferNote 2               | 169 ps (TYP.)                                             |  |

|                                  | Output bufferNote 3              | 864 ps (TYP.)                                             |  |

- Notes 1. Value assuming 2-input NAND power gate, fan-out 2, and standard wiring length.

- 2. Value assuming fan-out 2 and standard wiring length.

- **3.** Value assuming load capacitance 15 pF, lol = 18 mA.

Remark The logic circuit characteristics are the same as those of NEC Electronics' CB-9 Family.

## **Analog Circuit**

| Part number                          |                          | μ <b>PD681</b> XX                                      |  |

|--------------------------------------|--------------------------|--------------------------------------------------------|--|

| Process                              |                          | 0.35 μm BiCMOS process                                 |  |

| Supp                                 | oly voltage              | 3.3 V ±0.3 V                                           |  |

|                                      | NPN type                 | $f_T = 10 \text{ GHz}, h_{FE} = 70 \text{ (all TYP.)}$ |  |

| Transistors                          | PNP type (vertical type) | $f_T = 2 \text{ GHz}, h_{FE} = 30 \text{ (all TYP.)}$  |  |

|                                      | MOS                      | N-ch type, P-ch type for analog circuit                |  |

| Polysilicon resistor <sup>Note</sup> |                          | Absolute precision: ±20%, relative precision: ±2%      |  |

| Capacitor (MI                        | M type) <sup>Note</sup>  | Absolute precision: ±20%, relative precision: ±2%      |  |

Note Values indicated are for reference only. The relative precision applies only to when the element is positioned in an adjacent location.

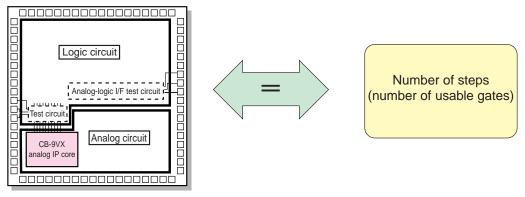

# Number of Steps and Usable Gates

|             | Number of Usable Gates |                |  |  |

|-------------|------------------------|----------------|--|--|

| Step Number | VX                     | Туре           |  |  |

|             | 2-Layer Wiring         | 3-Layer Wiring |  |  |

| B60         | 89,600                 | 131,800        |  |  |

| C02         | 117,700                | 174,200        |  |  |

| C40         | 142,000                | 211,500        |  |  |

| C78         | 176,100                | 264,200        |  |  |

| D01         | 195,700                | 293,600        |  |  |

| D26         | 215,900                | 326,200        |  |  |

| D52         | 242,200                | 365,900        |  |  |

| D90         | 277,900                | 422,900        |  |  |

| E16         | 308,300                | 469,200        |  |  |

| E54         | 344,200                | 535,400        |  |  |

| E80         | 373,300                | 572,400        |  |  |

| F18         | 412,800                | 647,300        |  |  |

| F44         | 448,300                | 703,000        |  |  |

| F70         | 479,800                | 741,500        |  |  |

| G08         | 521,600                | 824,900        |  |  |

| G34         | 554,300                | 876,600        |  |  |

| G72         | 612,600                | 954,500        |  |  |

| H10         | 655,600                | 1,045,900      |  |  |

| H49         | 714,700                | 1,140,200      |  |  |

| H87         | 775,400                | 1,218,600      |  |  |

| J26         | 813,300                | 1,309,300      |  |  |

| J51         | 855,900                | 1,377,800      |  |  |

| K15         | 968,800                | 1,536,000      |  |  |

| K92         | 1,071,600              | 1,741,400      |  |  |

**Remark** The number of usable gates is calculated using 2-input NAND gate conversion.

Moreover, the above-indicated number of usable gates depends on the megafunctions that are provided and the logic use efficiency, and should therefore be treated as a reference value.

**Remark** The number of steps and number of usable gates given for the MA-9 Family indicate the size of the entire internal logic including the mixed signal core.

28

# Electrical Specifications

## **Absolute Maximum Ratings**

| Item                          | Symbol          | Conditions                                               | Rating       | Unit |

|-------------------------------|-----------------|----------------------------------------------------------|--------------|------|

| Supply voltage                | V <sub>DD</sub> |                                                          |              |      |

| 3.3 V                         |                 |                                                          | -0.5 to +4.6 | V    |

| I/O voltage                   | Vı/Vo           |                                                          |              |      |

| LVTTL buffer                  |                 | V <sub>I</sub> /V <sub>O</sub> < V <sub>DD</sub> + 0.5 V | -0.5 to +4.6 | V    |

| Output current                | lo              | loL = 1 mA                                               | 3            | mA   |

|                               |                 | loL = 2 mA                                               | 7            | mA   |

|                               |                 | loL = 3 mA                                               | 10           | mA   |

|                               |                 | loL = 6 mA                                               | 20           | mA   |

|                               |                 | loL = 9 mA                                               | 30           | mA   |

|                               |                 | loL = 12 mA                                              | 40           | mA   |

|                               |                 | loL = 18 mA                                              | 60           | mA   |

|                               |                 | loL = 24 mA                                              | 75           | mA   |

| Operating ambient temperature | Та              |                                                          | -40 to +85   | °C   |

| Storage temperature           | Tstg            |                                                          | -65 to +150  | °C   |

Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter.

That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

## Definition of absolute maximum rating terms

| Item                          | Symbol          | Meaning                                                                                                                                     |

|-------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Supply voltage                | V <sub>DD</sub> | The range of voltage that, if applied to the VDD pin, will not cause destruction or lower reliability.                                      |

| Input voltage                 | Vı              | The range of voltage that, if applied to the input pin, will not cause destruction or lower reliability.                                    |

| Output voltage                | Vo              | The range of voltage that, if applied to the output pin, will not cause destruction or lower reliability.                                   |

| Input current                 | li              | The absolute value of current capacity that, if applied to the input pin, will not cause latchup to occur.                                  |

| Output current                | lo              | The absolute value of DC current capacity that, if output from or input to the output pin, will not cause destruction or lower reliability. |

| Operating ambient temperature | Та              | Range of ambient temperature in which normal logical operation will occur.                                                                  |

| Storage temperature           | Tstg            | Range of pin temperature that will not cause destruction or lower reliability when voltage and current are not applied.                     |

# **MA-9 Family**

# **Recommended Operating Range**

| Item                              | Symbol          | Conditions         | MIN | TYP | MAX             | Unit |

|-----------------------------------|-----------------|--------------------|-----|-----|-----------------|------|

| Supply voltage                    | V <sub>DD</sub> | 3.3 V power supply | 3.0 | 3.3 | 3.6             | ٧    |

| Negative trigger voltage          | Vn              | LVTTL buffer       | 0.6 |     | 1.8             | V    |

| Positive trigger voltage          | VP              | LVTTL buffer       | 1.2 |     | 2.4             | V    |

| Hysteresis voltage V <sub>H</sub> |                 | LVTTL buffer       | 0.3 |     | 1.5             | V    |

| Low-level input voltage           |                 | LVTTL buffer       | 0   |     | 0.8             | V    |

| High-level input voltage          | ViH             | LVTTL buffer       | 2.0 |     | V <sub>DD</sub> | V    |

| Input rise time                   | tri             | Normal input       | 0   |     | 200             | ns   |

| Input fall time                   | tfi             |                    | 0   |     | 200             | ns   |

| Input rise time                   | tri             | Schmitt input      | 0   |     | 10              | ms   |

| Input fall time                   | tfi             |                    | 0   |     | 10              | ms   |

Remark The logic circuit characteristics are the same as those of NEC Electronics' CB-9 Family.

# Analog IP Core

## A/D Converter

| Core Name              | Power<br>Consumption<br>(MAX.) | Differential<br>Linearity Error<br>(MAX.) | Integral<br>Linearity Error<br>(MAX.) | Circuit Type             | Operating<br>Power Supply<br>Voltage |

|------------------------|--------------------------------|-------------------------------------------|---------------------------------------|--------------------------|--------------------------------------|

| 10 bit-100 kHz-1ch     | 18.0 mW                        | ±1.0LSB                                   | ±1.5LSB                               | Successive approximation | 2.7 to 3.6 V                         |

| 10 bit-100 kHz-8ch_Mpx | 18.0 mW                        | ±1.0LSB                                   | ±1.5LSB                               | Successive approximation | 3.0 to 3.6 V                         |

| 12 bit-300 kHz-4ch_Mpx | 20.2 mW                        | ±1.0LSB                                   | ±4.0LSB                               | Successive approximation | 2.7 to 3.6 V                         |

| 6 bit-70 MHz           | 504 mW                         | ±1.0LSB                                   | ±2.0LSB                               | Flash                    | 3.0 to 3.6 V                         |

| 8 bit-200 kHz-1ch      | 28.8 mW                        | ±1.0LSB                                   | ±2.0LSB                               | Successive approximation | 3.3 V (TYP.)                         |

| 8 bit-200 kHz-8ch      |                                |                                           |                                       |                          |                                      |

| 8 bit-50 MHz           | 108 mW                         | ±1.0LSB (TYP.)                            | ±1.0LSB (TYP.)                        | Sub-ranging              | 3.0 to 3.6 V                         |

| 8 bit-8 MHz            |                                |                                           |                                       |                          |                                      |

**Remark**  $T_A = -40 \text{ to } +85^{\circ}\text{C}$

## **D/A Converter**

| Core Name          | Power<br>Consumption<br>(MAX.) | Differential<br>Linearity Error<br>(MAX.) | Integral<br>Linearity Error<br>(MAX.) | Circuit Type    | Operating<br>Power Supply<br>Voltage |

|--------------------|--------------------------------|-------------------------------------------|---------------------------------------|-----------------|--------------------------------------|

| 10 bit-100 kHz-1ch | 3.6 mW                         | ±1.0LSB                                   | ±1.0LSB                               | Resistor string | 3.3 V (TYP.)                         |

| 10 bit-135 kHz-1ch | 374 mW                         | ±1.0LSB                                   | ±1.5LSB                               | Resistor string | 3.0 to 3.6 V                         |

| 10 bit-30 MHz-1ch  | 90 mW                          | ±0.5LSB                                   | ±2.25LSB                              | Resistor string | 3.0 to 3.6 V                         |

| 10 bit-30 MHz-2ch  | 180 mW                         | ±0.5LSB                                   | ±2.25LSB                              | Resistor string | 3.0 to 3.6 V                         |

| 10 bit-30 MHz-3ch  | 266.4 mW                       | ±0.5LSB                                   | ±2.25LSB                              | Resistor string | 3.0 to 3.6 V                         |

| 8 bit-200 kHz-1ch  | 7.2 mW                         | ±1.0LSB                                   | ±1.0LSB                               | Resistor string | 3.3 V (TYP.)                         |

| 8 bit-30 MHz-1ch   | 90 mW                          | ±0.5LSB                                   | ±1.0LSB                               | Resistor string | 3.0 to 3.6 V                         |

| 8 bit-30 MHz-2ch   | 180 mW                         | ±0.5LSB                                   | ±1.0LSB                               | Resistor string | 3.0 to 3.6 V                         |

| 8 bit-30 MHz-3ch   | T.B.D.                         | ±1.0LSB                                   | ±3.0LSB                               | Resistor string | Under development                    |

|                    |                                |                                           |                                       |                 | (Vo = 0.75 V)                        |

**Remark**  $T_A = -40 \text{ to } +85^{\circ}\text{C}$

# **MA-9 Family**

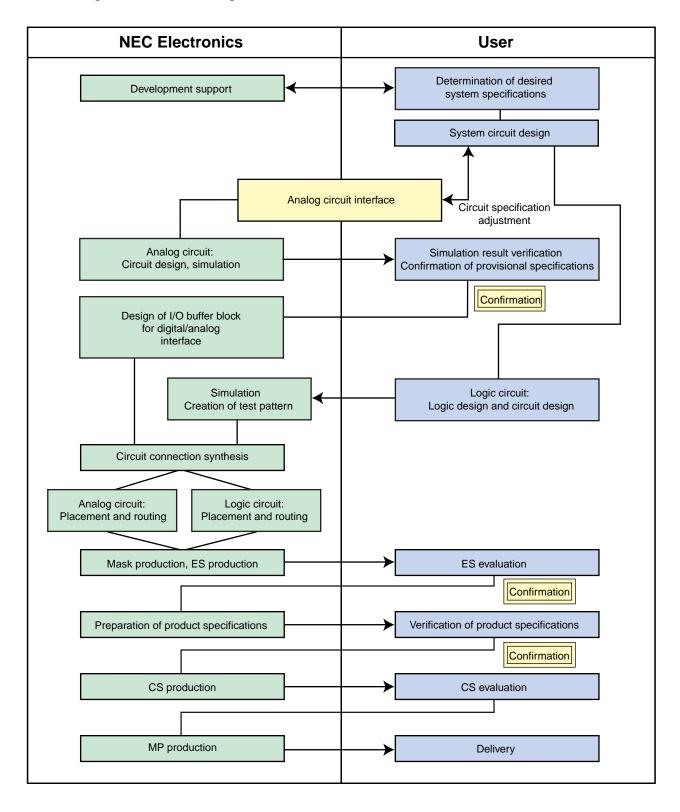

# **MA-9 Family Development Procedure**

The MA-9 Family is developed by separating the logic circuit and analog circuit and combining the circuit diagram level interface and simulation level interface.

| Development Method                               | System<br>Circuit Design | LSI<br>Circuit Design | Circuit<br>Synthesis | Layout<br>Design       | ES Production |

|--------------------------------------------------|--------------------------|-----------------------|----------------------|------------------------|---------------|

| [logic circuit]<br>Simulation level interface    |                          | (User side)           |                      |                        |               |

| [Analog circuit] Circuit diagram level interface |                          |                       |                      | (NEC Electronics side) |               |

Logic circuit: Simulation level interface Analog circuit: Circuit diagram level interface

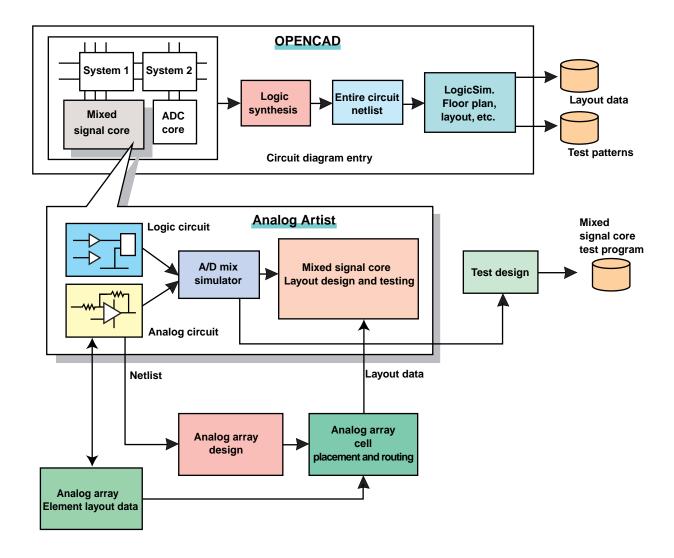

# **MA-9 Family Development Tools**

The MA-9 Family provides development tools that support ASIC development by the user for each logic circuit and analog circuit separately.

For the logic circuits, a simple design environment is enabled by using OPENCAD, NEC Electronics' original CAE tool, and for the analog circuits, the design environment is enabled by using a CAE tool ideal for digital-analog integrated circuits.

## Analog Artist

Circuit diagram entry: Composer™ Simulator: Spectre/Verilog™HDL Layout editor: DLE,Virtuoso

Layout tester: Diva

## **Design Flowchart**

# **Packages**

# MA-8A

The MA-8A supports various packages, enabling users to select the package type and optimum number of pins for their system and circuit scale (chip size).

## **Mold Packages**

| Package | No. of Pins | Lead Pitch (mm) | Nominal Size  | Body Size (mm) | Main Unit Thickness (mm) |

|---------|-------------|-----------------|---------------|----------------|--------------------------|

| SOP     | 20          | 1.27            | 7.62 mm (300) | _              | -                        |

| SSOP    | 16          | 0.65            | 5.72 mm (225) | -              | -                        |

|         | 20          | 0.65            | 5.72 mm (225) | -              | -                        |

|         | 20          | 0.65            | 7.62 mm (300) | -              | -                        |

|         | 24          | 0.65            | 7.62 mm (300) | -              | -                        |

|         | 30          | 0.65            | 7.62 mm (300) | -              | -                        |

|         | 36          | 0.65            | 7.62 mm (300) | -              | -                        |

|         | 38          | 0.65            | 7.62 mm (300) | -              | -                        |

|         | 42          | 0.65            | 9.53 mm (375) | -              | -                        |

|         | 48          | 0.65            | 9.53 mm (375) | -              | -                        |

| QFP     | 44          | 0.8             | -             | 10 X 10        | 2.70                     |

|         | 44          | 0.8             | -             | 10 X 10        | 1.40                     |

|         | 48          | 0.5             | -             | 7 X 7          | 1.00                     |

|         | 48          | 0.65            | -             | 10 X 10        | 2.20                     |

|         | 52          | 0.65            | -             | 10 X 10        | 1.40                     |

|         | 52          | 1.00            | -             | 14 X 14        | 2.55                     |

|         | 64          | 0.5             | -             | 10 X 10        | 1.00                     |

|         | 64          | 0.8             | -             | 14 X 14        | 1.40                     |

|         | 64          | 1.0             | -             | 14 X 20        | 2.00                     |

|         | 68          | 0.65            | -             | 10 X 14        | 2.20                     |

|         | 72          | 0.5             | -             | 10 X 10        | 2.20                     |

|         | 74          | 1.0             | -             | 20 X 20        | 3.70                     |

|         | 80          | 0.5             | -             | 12 X 12        | 1.00                     |

|         | 80          | 0.65            | -             | 14 X 14        | 2.00                     |

|         | 80          | 0.8             | -             | 14 X 20        | 2.70                     |

|         | 100         | 0.4             | -             | 12 X 12        | 1.00                     |

|         | 100         | 0.5             | -             | 14 X 14        | 1.40                     |

|         | 100         | 0.5             | -             | 14 X 14        | 1.00                     |

|         | 100         | 0.65            | -             | 14 X 20        | 2.20                     |

|         | 120         | 0.4             | -             | 14 X 14        | 1.00                     |

|         | 120         | 0.5             | -             | 20 × 20        | 2.70                     |

|         | 144         | 0.5             | -             | 20 X 20        | 1.40                     |

|         | 160         | 0.5             | -             | 24 X 24        | 1.40                     |

|         | 176         | 0.4             | -             | 20 X 20        | 1.40                     |

|         | 208         | 0.5             | -             | 28 × 28        | 1.40                     |

|         | 240         | 0.5             | -             | 32 × 32        | 1.40                     |

## **CSP (Chip Size Package)**

| Package | No. of Pins | Ball Array | Body Size    | Production | Package | No. of Pins | Ball Array | Body Size    | Production |

|---------|-------------|------------|--------------|------------|---------|-------------|------------|--------------|------------|

|         |             |            | (mm)         | Status     |         |             |            | (mm)         | Status     |

| FPBGA   | 61          | 3          | 6 <b>X</b> 6 | 0          | FPLGA   | 64          | 3          | 6 <b>X</b> 6 | 0          |

|         | 80          | 4          | 7 <b>X</b> 7 |            |         | 84          | 4          | 7.5 X 7.5    | 0          |

|         | 161         | 4          | 10 X 10      | 0          |         | 100         | Full       | 8 <b>X</b> 7 | 0          |

|         | 209         | 4          | 12 X 12      | Note       |         | 108         | Full       | 7.5 X 7.5    | 0          |

|         | 225         | 4          | 13 X 13      | 0          |         | 112         | 4          | 8 <b>x</b> 8 | 0          |

|         | 249         | 4          | 13 X 13      | 0          |         | 168         | 4          | 11 X 11      | 0          |

|         | 257         | 4          | 14 X 14      | 0          |         | 192         | 4          | 11 X 11      | Note       |

|         | 273         | 4          | 15 X 15      | Note       |         | 224         | 4          | 13 X 13      | 0          |

|         | 303         | 4          | 16 X 16      | 0          |         | 304         | 4          | 16 X 16      | 0          |

|         | 393         | 4-0-2      | 16 × 16      | Note       |         | 405         | 4-0-2      | 16 X 16      | ○ Note     |

Note Under development

Remarks 1. FPBGA: Fine Pitch Ball Grid Array, FPLGA: Fine Pitch Land Grid Array

- 2. O: Can be produced Blank: In planning

- 3 Development costs, including the board and sorting jig, will be charged for a CSP.

# **Packages**

# **MA-9 Family**

The MA-9 Family supports various packages, enabling users to select the package type and optimum number of pins for their system and circuit scale (chip size).

For packages other than QFP, contact NEC Electronics.

|          | Package             |                          |                       |                            |     | Step Size |     |     |     |     |     |     |     |

|----------|---------------------|--------------------------|-----------------------|----------------------------|-----|-----------|-----|-----|-----|-----|-----|-----|-----|

| Type     | No. of<br>Pins      | External Dimensions (mm) | Lead<br>Pitch<br>(mm) | Resin<br>Thickness<br>(mm) | B60 | C02       | C40 | C78 | D01 | D26 | D52 | D90 | E16 |

| QFP (FP) | 100                 | 14 X 14                  | 0.50                  | 1.45                       | 0   | 0         | 0   |     |     |     | 0   | 0   |     |

|          | 120                 | 20 X 20                  | 0.50                  | 2.70                       | ı   |           |     |     |     |     |     |     |     |

|          | 144                 | 20 X 20                  | 0.50                  | 2.70                       | ı   | _         | -   |     |     |     |     |     |     |

|          | 160 <sup>Note</sup> | 20 X 20                  | 0.50                  | 2.70                       | -   | _         | _   | _   | 0   | 0   | 0   | 0   | 0   |

|          | 176 <sup>Note</sup> | 24 X 24                  | 0.50                  | 2.70                       | -   | -         | -   | -   |     | Δ   | Δ   | 0   | 0   |

|          | 208 <sup>Note</sup> | 28 X 28                  | 0.50                  | 3.20                       | -   | -         | -   | -   |     | 0   | 0   | 0   | 0   |

|          | 240 <sup>Note</sup> | 32 X 32                  | 0.50                  | 3.20                       | -   | -         | -   | -   |     | 0   | 0   | 0   | 0   |

|          | 304 <sup>Note</sup> | 40 × 40                  | 0.50                  | 3.20                       | -   | _         | _   | _   | -   | -   | _   | _   | -   |

| TQFP     | 100                 | 14 X 14                  | 0.50                  | 1.00                       | 0   |           |     |     |     |     | 0   |     | 0   |

Note Low-thermal-resistance type

$\textbf{Remark} \qquad \bigcirc : \textbf{Can be used, } \triangle : \textbf{Under development, } - : \textbf{Cannot be used, Blank: Under study}$

|          | Package             |                          |                       |                            |     | Step Size |     |     |     |     |     |     |

|----------|---------------------|--------------------------|-----------------------|----------------------------|-----|-----------|-----|-----|-----|-----|-----|-----|

| Туре     | No. of<br>Pins      | External Dimensions (mm) | Lead<br>Pitch<br>(mm) | Resin<br>Thickness<br>(mm) | E54 | E80       | F18 | F44 | F70 | G08 | G34 | G72 |

| QFP (FP) | 100                 | 14 X 14                  | 0.50                  | 1.45                       |     |           |     |     |     | -   | -   | -   |

|          | 120                 | 20 X 20                  | 0.50                  | 2.70                       |     |           |     |     |     |     |     |     |

|          | 144                 | 20 X 20                  | 0.50                  | 2.70                       |     |           |     | 0   |     |     |     |     |

|          | 160 <sup>Note</sup> | 20 X 20                  | 0.50                  | 2.70                       | 0   | 0         | 0   | 0   | 0   | 0   |     |     |

|          | 176 <sup>Note</sup> | 24 X 24                  | 0.50                  | 2.70                       | 0   | 0         | 0   | 0   | 0   | 0   | 0   |     |

|          | 208 <sup>Note</sup> | 28 X 28                  | 0.50                  | 3.20                       | 0   | 0         | 0   | 0   | 0   | 0   | 0   | 0   |

|          | 240 <sup>Note</sup> | 32 X 32                  | 0.50                  | 3.20                       | 0   | 0         | 0   | 0   | 0   | 0   | 0   | 0   |

|          | 304 <sup>Note</sup> | 40 × 40                  | 0.50                  | 3.20                       | -   | 0         | 0   | 0   | 0   | 0   | 0   | 0   |

| TQFP     | 100                 | 14 X 14                  | 0.50                  | 1.00                       |     | ·         |     |     |     | _   | _   | _   |

Note Low-thermal-resistance type

$\textbf{Remark} \qquad \bigcirc \text{: Can be used, } \triangle \text{: Under development, } - \text{: Cannot be used, Blank: Under study}$

|          | F                   | Package                  |                       |                            | Step Size |     |     |     |     |     |     |

|----------|---------------------|--------------------------|-----------------------|----------------------------|-----------|-----|-----|-----|-----|-----|-----|

| Туре     | No. of<br>Pins      | External Dimensions (mm) | Lead<br>Pitch<br>(mm) | Resin<br>Thickness<br>(mm) | H10       | H49 | H87 | J26 | J51 | K15 | K92 |

| QFP (FP) | 100                 | 14 X 14                  | 0.50                  | 1.45                       | -         | _   | -   | 1   | ı   | _   | -   |

|          | 120                 | 20 X 20                  | 0.50                  | 2.70                       |           |     |     | -   | _   | _   | -   |

|          | 144                 | 20 X 20                  | 0.50                  | 2.70                       |           |     |     | -   | _   | -   | -   |

|          | 160 <sup>Note</sup> | 20 X 20                  | 0.50                  | 2.70                       |           |     |     |     |     |     |     |

|          | 176 <sup>Note</sup> | 24 X 24                  | 0.50                  | 2.70                       |           |     |     |     |     |     |     |

|          | 208 <sup>Note</sup> | 28 X 28                  | 0.50                  | 3.20                       | 0         | 0   |     |     | 0   |     | 0   |

|          | 240 <sup>Note</sup> | 32 X 32                  | 0.50                  | 3.20                       | 0         | 0   |     |     | 0   |     | 0   |

|          | 304 <sup>Note</sup> | 40 × 40                  | 0.50                  | 3.20                       | 0         | 0   |     |     |     |     | 0   |

| TQFP     | 100                 | 14 X 14                  | 0.50                  | 1.00                       | _         | _   | -   | _   | _   | _   | _   |

Note Low-thermal-resistance type

$\textbf{Remark} \qquad \bigcirc : \textbf{Can be used, } \triangle : \textbf{Under development, -: Cannot be used, Blank: Under study}$

| MEMO _ |  |  |

|--------|--|--|

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

| -      |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

|        |  |  |

| MEMO |  |  |  |  |

|------|--|--|--|--|

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

|      |  |  |  |  |

EEPROM, FPBGA, and OPENCAD are trademarks of NEC Electronics Corporation.

Analog Artist, Composer, and Verilog are trademarks of Cadence Design Systems, Inc.

These commodities, technology or software, must be exported in accordance with the export administration regulations of the exporting country. Diversion contrary to the law of that country is prohibited.

- The information in this document is current as of May, 2003. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior

written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may

appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual

property rights of third parties by or arising from the use of NEC Electronics products listed in this document

or any other liability arising from the use of such NEC Electronics products. No license, express, implied or

otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or

others

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

- The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact NEC Electronics sales representative in advance to determine NEC Electronics's willingness to support a given application.

### (Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

# For further information, please contact:

### **NEC Electronics Corporation**

1753, Shimonumabe, Nakahara-ku, Kawasaki, Kanagawa 211-8668, Japan Tel: 044-435-5111

http://www.necel.com/

### [North America]

### **NEC Electronics America, Inc.**

http://www.necelam.com/

2880 Scott Blvd. Santa Clara, CA 95050-2554, U.S.A. Tel: 408-588-6000 800-366-9782

### [Europe]

### **NEC Electronics (Europe) GmbH**

Oberrather Str. 4 40472 Düsseldorf, Germany Tel: 0211-6503-01 http://www.ee.nec.de/

### Sucursal en España

Juan Esplandiu, 15 28007 Madrid, Spain Tel: 091-504-2787

### Succursale Française

9, rue Paul Dautier, B.P. 52 78142 Velizy-Villacoublay Cédex France

Tel: 01-3067-5800

### Filiale Italiana

Via Fabio Filzi, 25/A 20124 Milano, Italy Tel: 02-667541

### **Branch The Netherlands**

Boschdijk 187a 5612 HB Eindhoven The Netherlands Tel: 040-2445845

### **Tyskland Filial**

P.O. Box 134 18322 Taeby, Sweden Tel: 08-6380820

### **United Kingdom Branch**

Cygnus House, Sunrise Parkway Linford Wood, Milton Keynes MK14 6NP, U.K. Tel: 01908-691-133

### [Asia & Oceania]

### **NEC Electronics Hong Kong Limited**

12/F., Cityplaza 4, 12 Taikoo Wan Road, Hong Kong

Tel: 2886-9318

### Seoul Branch

11F., Samik Lavied'or Bldg., 720-2, Yeoksam-Dong, Kangnam-Ku, Seoul, 135-080, Korea Tel: 02-558-3737

### NEC Electronics Shanghai, Ltd.

7th Floor, HSBC Tower, 101Yin Cheng East Road, Pudong New Area, Shanghai P.R. China P.C:200120 Tel: 021-6841-1138

### **NEC Electronics Taiwan Ltd.**

7F, No. 363 Fu Shing North Road Taipei, Taiwan, R. O. C. Tel: 02-2719-2377

### **NEC Electronics Singapore Pte. Ltd.**

238A Thomson Road, #12-08 Novena Square, Singapore 307684 Tel: 6253-8311

G03.4