#### **Description**

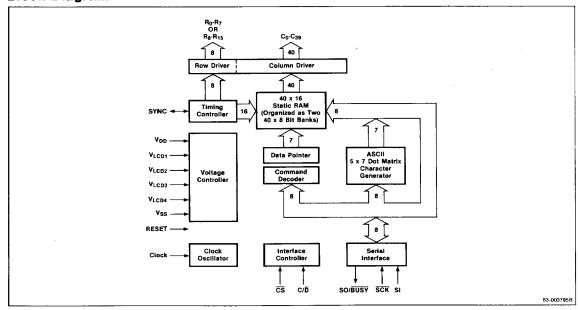

The  $\mu$ PD7227 intelligent dot-matrix LCD controller/driver is a peripheral device designed to interface most microprocessors with a wide variety of dot matrix LCDs. It can directly drive any multiplexed LCD organized as 8 rows by 40 columns, and is easily cascaded up to 16 rows and 280 columns. The  $\mu$ PD7227 is equipped with several hardware logic blocks, such as an 8-bit serial interface, ASCII character generator, 40 x 16 static RAM with full read/write capability, and an LCD timing controller; all of which reduce microprocessor system software requirements. The  $\mu$ PD7227 is manufactured with a single 5 V CMOS process, and is available in a space-saving 64-pin plastic flat package.

#### **Features**

- □ Single-chip LCD controller with direct LCD drive

□ Compatible with most microprocessors

- ☐ Eight row drives

- Designed for dot-matrix LCD configurations up to 280 dots

- Designed for 5 x 7 dot-matrix character LCD configuration up to 8 characters

- Cascadable to 16 row drives

- □ 40 column drives

- Cascadable to 280 column drives

- ☐ Hardware logic blocks reduce system software requirements

- 8-bit serial interface for communication

- ASCII 5 x 7 dot-matrix character generator with 64-character vocabulary

- 40 x 16-bit static RAM for data storage, retrieval, and complete back-up memory capability.

- Voltage controller generates LCD bias voltages

- Timing controller synchronizes column drives with sequentially-multiplexed row drives

- ☐ Single +5 V power supply

- ☐ CMOS technology

## **Ordering Information**

| Part Number | Package Type       | Max Frequency of Operation |

|-------------|--------------------|----------------------------|

| μPD7227G-12 | 64-pin plastic QFP | 1000 kHz                   |

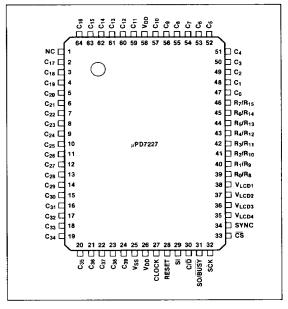

## **Pin Configuration**

#### Pin Identification

| No.                      | Symbol                                                          | Function                       |

|--------------------------|-----------------------------------------------------------------|--------------------------------|

| 1                        | NC                                                              | No connection                  |

| 2-24,<br>47-57,<br>59-64 | C <sub>0</sub> -C <sub>39</sub>                                 | LCD column driver outputs      |

| 25                       | V <sub>SS</sub>                                                 | Ground                         |

| 26, 58                   | V <sub>DD</sub>                                                 | Power                          |

| 27                       | CLOCK                                                           | System clock input             |

| 28                       | RESET                                                           | Reset input                    |

| 29                       | SI                                                              | Serial input                   |

| 30                       | C/D                                                             | Command or data select input   |

| 31                       | S0/BUSY                                                         | Serial output or busy output   |

| 32                       | SCK                                                             | Serial clock input             |

| 33                       | CS                                                              | Chip select input              |

| 34                       | SYNC                                                            | Synchronization port           |

| 35-38                    | V <sub>LCD1</sub> -V <sub>LCD4</sub>                            | LCD bias voltage supply inputs |

| 39-46                    | R <sub>0</sub> /R <sub>8</sub> -R <sub>7</sub> /R <sub>15</sub> | LCD row driver outputs         |

50273 (NECEL-495)

#### Pin Functions

#### C<sub>0</sub>-C<sub>39</sub>

LCD column driver outputs.

#### R0/8-R7/15

LCD row driver outputs.

## V<sub>LCD1</sub>-V<sub>LCD4</sub>

LCD bias voltage supply inputs to the LCD voltage controller. Apply appropriate voltages from a voltage ladder connected across VDD.

#### SI

Serial input from the microprocessor.

### SO/BUSY

Serial output from the  $\mu PD7227$  to the microprocessor when in read mode and  $C/\overline{D}$  is low. When  $\overline{BUSY}$  (active low), handshake output indicates the  $\mu PD7227$  is ready to receive/send the next data byte.

#### SCK

Serial clock input. Synchronizes 8-bit serial data transfer between the microprocessor and µPD7227.

## C/D

Command/data select input. Distinguishes serially input data byte as a command or as display data.

### $\overline{\mathsf{cs}}$

Chip select input. Enables the  $\mu PD7227$  for communication with the microprocessor.

#### SYNC

Synchronization port. For multichip operation, tie all SYNC lines together and configure with the MODE SET command.

## **CLOCK**

System clock input. Connect to external clock source.

## **RESET**

Reset input. RC circuit or pulse initializes the  $\mu$ PD7227 after power-up.

#### $V_{DE}$

Power supply positive. Apply single voltage 5 V  $\pm$  10% for proper operation.

#### $v_{ss}$

Ground.

#### **Block Diagram**

8-14

# **Absolute Maximum Ratings**

$T_A = 25$ °C

| Power supply, V <sub>DD</sub>                          | -0.3 V to +7.0 V                 |

|--------------------------------------------------------|----------------------------------|

| All inputs and outputs with respect to V <sub>CC</sub> | -0.3 V to V <sub>DD</sub> +0.3 V |

| Storage temperature, T <sub>STG</sub>                  | -65°C to +150°C                  |

| Operating temperature, T <sub>OPT</sub>                | -10°C to +70°C                   |

Comment: Exposing the device to stresses above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of this specification. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## Capacitance

$T_A = 25$ °C,  $V_{DD} = 0$ V

|                          |                 | LI  | imits |            | Test                |  |

|--------------------------|-----------------|-----|-------|------------|---------------------|--|

| Parameter                | Symbol          | Min | Max   | Unit       | Conditions          |  |

| Input capacitance        | Cı              |     | 10    | ρF         | fφ = 1 MHz          |  |

| Output capacitance       | Co              |     | 25    | pF         | Unmeasured pins     |  |

| Input/output capacitance | C <sub>IO</sub> |     | 15    | pF<br>SYNC | returned to ground. |  |

## **DC Characteristics**

$T_A = -10^{\circ}C \text{ to } +70^{\circ}C, V_{DD} = +5.0V \pm 10\%$

|                                 | <u>.</u>           |    |     | L               | imits           |                    |        | Test                                                |

|---------------------------------|--------------------|----|-----|-----------------|-----------------|--------------------|--------|-----------------------------------------------------|

| Parameter                       | Symbol             |    | Mi  | n               | Тур             | Max                | Unit   | Conditions                                          |

| Input voltage, high             | VIH                | 0. | 7 ١ | / <sub>DD</sub> |                 | V <sub>DD</sub>    | ٧      |                                                     |

| Input voltage, low              | V <sub>IL</sub>    |    | 0   |                 |                 | 0.3 V <sub>D</sub> | DV     |                                                     |

| Input leakage<br>current, high  | ILIH               |    |     |                 |                 | +10                | μΑ۷    | IH = VDD                                            |

| Input leakage<br>current, low   | LIL                |    |     |                 |                 | -10                | μAV    | / <sub>IH</sub> = 0V                                |

| Output voltage, high            | V <sub>OH1</sub>   | ٧  | DD- | 0.5             |                 |                    |        | 60/BUSY,<br>0H = -400 هـ                            |

|                                 | V <sub>OH2</sub>   | ۷  | DD- | 0.5             |                 |                    |        | SYNC,<br>0H = -100 μA                               |

| Output voltage, low             | V <sub>OL1</sub>   |    |     |                 |                 | 0.45               |        | 0/BUSY,<br>0L = +1.7 mA                             |

|                                 |                    |    |     |                 |                 | 0.45               |        | SYNC,<br>OL = +100 μΑ                               |

| Output leakage<br>current, high | ILOH               |    |     |                 |                 | +10                | μΑ\    | $V_{OH} = V_{DD}$                                   |

| Output leakage<br>current, low  | I <sub>LOL</sub>   |    |     |                 |                 | -10                | μА\    | / <sub>OL</sub> = 0V                                |

| LCD operating voltage           | V <sub>LCD</sub>   |    | 3.  | 0               |                 | V <sub>DD</sub>    | r      | 3-row<br>multiplexed<br>.CD drive<br>configuration  |

|                                 |                    | •  |     |                 | V <sub>DD</sub> |                    | ,<br>! | 16-row<br>multiplexed<br>_CD drive<br>configuration |

| Row drive output impedance      | R <sub>ROW</sub>   |    |     |                 | 4               | 8                  | kΩ     |                                                     |

| Column drive output impedance   | R <sub>COLUM</sub> | N  |     |                 | 10              | 15                 | kΩ     |                                                     |

| Supply current                  | IDD                |    |     |                 | 200             | 400                | μA     | f0 = 400 KHz                                        |

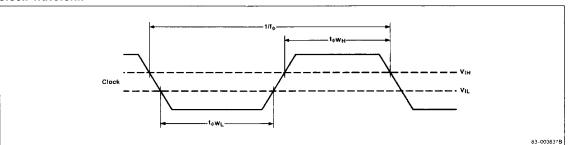

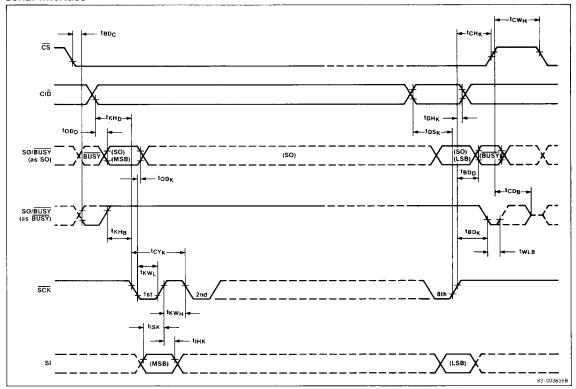

### **AC Characteristics**

$T_A = -10^{\circ}C \text{ to } +70^{\circ}C, V_{DD} = +5.0V \pm 10\%$

| ·                                    |                    | Lim  | its  |      | Test                         |

|--------------------------------------|--------------------|------|------|------|------------------------------|

| Parameter                            | Symbol             | Min  | Max  | Unit | l est<br>Conditions          |

| Clock frequency                      | fφ                 | 100  | 1000 | KHz  |                              |

| Clock pulse<br>width high            | t <sub>¢WH</sub>   | 400  |      | ns   | -                            |

| Clock pulse width low                | <sup>t</sup> ∳WL   | 400  |      | ns   |                              |

| SCK cycle                            | t <sub>CYK</sub>   | 0.9  |      | μS   |                              |

| SCK pulse<br>width high              | t <sub>KWH</sub>   | 400  |      | ns   |                              |

| SCK pulse width low                  | t <sub>KWL</sub>   | 400  |      | ns   |                              |

| SCK hold time<br>after BUSYt         | t <sub>KHB</sub>   | 0    |      | ns   |                              |

| SI setup time to SCK1                | <sup>t</sup> ISK   | 100  |      | ns   |                              |

| SI hold time after SCK†              | t <sub>IHK</sub>   | 250  |      | ns   |                              |

| SO delay time<br>after SCK↓          | todk               |      | 320  | ns   | C <sub>LOAD</sub> = 50 pF    |

| SO delay time after C/D↓             | todd               |      | 2    | μS   |                              |

| SCK hold time<br>after C/D↓          | tkho               | 2    |      | μs   |                              |

| BUSY delay<br>time after 8th<br>SCKt | t <sub>BDK</sub>   |      | 3    | μS   | C <sub>LOAD</sub> = 50 pF    |

| BUSY delay<br>time after C/D†        | t <sub>BDD</sub>   |      | 2    | μS   |                              |

| BUSY delay<br>time after CS↓         | t <sub>BDC</sub>   |      | 2    | μS   |                              |

| C/D setup time<br>to 8th SCK†        | tosk               | 2    | -    | μS   |                              |

| C/D hold time after 8th SCK1         | t <sub>DHK</sub>   | 2    |      | μs   |                              |

| CS hold time<br>after 8th SCK†       | t <sub>CHK</sub>   | 2    |      | μS   |                              |

| CS pulse width high                  | tcwH               | 2/f¢ |      | μS   |                              |

| CS† delay time<br>to BUSY floating   | t <sub>CDB</sub>   | 2    |      | μS   | C <sub>LOAD</sub> =<br>50 pF |

| SYNC load capacitance                | C <sub>LOADS</sub> |      | 100  | pF   |                              |

| BUSY low<br>level width              | t <sub>WLB</sub>   | 18   | 64   | 1/fф | C <sub>LOAD</sub> =<br>50 pF |

## **Timing Waveforms**

### Clock Waveform

### Serial Interface

# **Command Summary**

|                           |                                                                                                                                                                                                  |                |                |                | Inst           | ruction Co     | ie             |                |                |        |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--------|

|                           |                                                                                                                                                                                                  |                |                |                |                | Binary         |                |                |                |        |

| Command                   | Description                                                                                                                                                                                      | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | HEX    |

| Mode Set                  | Initialize the µPD7227, including selection of 1. LCD drive configuration 2. Row driver port function 3. RAM bank 4. SYNC port function                                                          | 0              | Ō              | 0              | 1              | 1              | D <sub>2</sub> | D <b>1</b>     | D <sub>0</sub> | 18-1F  |

| Frame<br>Frequency<br>Set | Set LCD frame frequency                                                                                                                                                                          | 0              | 0              | 0              | 1              | 0              | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | 10 -14 |

| Load Data<br>Pointer      | Load data pointer with 7 bits of immediate data                                                                                                                                                  | 1              | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | 80-E7  |

| Write Mode                | Write display byte in serial<br>register to RAM location ad-<br>dressed by data pointer;<br>modify data pointer                                                                                  | 0              | 1              | 1              | 0              | 0              | 1              | D <sub>1</sub> | D <sub>0</sub> | 64-67  |

| Read Mode                 | Load RAM contents address-<br>ed by data pointer into serial<br>register for output; modify<br>data pointer                                                                                      | 0              | 1              | 1              | 0              | 0              | 0              | D <sub>1</sub> | D <sub>0</sub> | 60-63  |

| AND Mode                  | Perform a logical AND be-<br>tween the display byte in the<br>serial register and the RAM<br>contents addressed by data<br>pointer; write result to same<br>RAM location; modify data<br>pointer | 0              | 1              | 1              | 0              | 1              | 1              | D <sub>1</sub> | D <sub>0</sub> | 6C-6F  |

| OR Mode                   | Perform a logical OR be-<br>tween the display byte in the<br>serial register and the RAM<br>contents addressed by data<br>pointer; write result to same<br>RAM location; modify data<br>pointer  | 0              | 1              | 1              | 0              | 1              | 0              | D <sub>1</sub> | D <sub>0</sub> | 68-68  |

| Character Mode            | Decode display byte in serial register into 5 x 7 character with character generator; write character to RAM location addressed by data pointer; increment data pointer by 5                     | 0              | 1              | 1              | 1              | 0              | 0              | 1              | 0              | 72     |

| Set Bit                   | Set single bit of RAM loca-<br>tion addressed by data<br>pointer; modify data pointer                                                                                                            | 0              | 1              | 0              | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | 40-5F  |

| Reset Bit                 | Reset single bit of RAM loca-<br>tion addressed by data<br>pointer; modify data pointer                                                                                                          | 0              | 0              | 1              | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | 20-3F  |

| Enable Display            | Turn on the LCD                                                                                                                                                                                  | 0              | 0              | 0              | 0              | 1              | 0              | 0              | 1              | 09     |

| Disable Display           | Turn off the ICD                                                                                                                                                                                 | 0              | 0              | 0              | 0              | 1              | 0              | 0              | 0              | 08     |

Further details of operation can be found in the  $\mu PD7227$  intelligent dot-matrix LCD controller/driver technical manual.

## $5 \times 7$ Character Set as Generated in $\mu$ PD7227

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |       |       | Display Byte |                |                |       |                |                |                |                | Display Byte   |  |      |      |   |          |                |                |                |                |                |                |                |       |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-------|--------------|----------------|----------------|-------|----------------|----------------|----------------|----------------|----------------|--|------|------|---|----------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-------|--|

| D7   D6   D5   D4   D3   D2   D1   D0   D0   D0   D0   D0   D0   D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1 1 | 0     |       |              |                |                |       |                |                |                |                |                |  | 1    | 1    | 0 | 0        |                |                |                |                |                |                |                |       |  |

| D7      D6      D5      D4      D3      D2      D1      D0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0      0 | 0 0 | 1     |       |              |                |                |       |                |                |                |                |                |  | 0    | 0    | 1 | 1        |                |                |                |                |                |                |                |       |  |

| 0 0 0 0 1 1 0 1 0 1 0 1 1 1 0 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0 1 | 1     | )     |              |                |                |       |                |                |                | l              |                |  | 1    | 0    | 1 | 0        |                |                |                |                |                |                |                |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |       |       |              | D <sub>0</sub> | D <sub>1</sub> | $D_2$ | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> |  |      |      |   |          | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> | $D_7$ |  |

| 0 0 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | :     |       |              | 0              | 0              | 0     | 1              |                |                |                |                |  | :::: | :::: |   |          | 0              | 0              | 0              | 0              |                |                |                |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | •     | :     | ļ            | 1              | 0              | 0     | 1              |                |                |                |                |  |      |      |   | :        | 1              | 0              | 0              | 0              |                |                |                |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | ::    | ::    | :            | 0              | 1              | 0     | 1              |                |                |                |                |  |      |      | : | ::       | 0              | 1              | 0              | 0              |                |                |                |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | ::    |       |              | 1              | 1              | 0     | 1              |                |                |                |                |  |      |      |   |          | 1              | 1              | 0              | 0              |                |                |                |       |  |

| 0 1 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |       | •     | - 1 -        | 0              | 0              | 1     | 1              |                |                |                |                |  |      |      | 1 | <u> </u> | 0              | 0              | 1              | 0              |                |                |                |       |  |

| 0 1 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | 00000 | • • • |              | 1              | 0              | 1     | 1              |                |                |                |                |  |      |      |   | 1        | 1              | 0              | 1              | 0              |                |                |                |       |  |

| 0 1 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |       |       | -            | 0              | 1              | 1     | 1              |                |                |                |                |  |      |      |   |          | 0              | 1              | 1              | 0              |                |                |                |       |  |

| 0 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |       |       |              | 1              | 1              | 1     | 1              |                |                |                |                |  |      |      |   |          | 1              | 1              | 1              | 0              |                |                |                |       |  |