# Description

The  $\mu$ PD77C25 and  $\mu$ PD77P25 Digital Signal Processors (DSP) are significant upgrades to the  $\mu$ PD7720—the original member of NEC's DSP family.  $\mu$ PD77C25 is the mask ROM version;  $\mu$ PD77P25 has an OTP ROM or a UVEPROM. All versions are CMOS and identical in function. Unless contextually excluded, references in this data sheet to 77C25 include 77P25

The 77C25 executes instructions twice as fast as the 77C20A/7720A. Additional instructions allow the 77C25 to execute common digital filter routines more efficiently and at more than twice the speed of a 7720 implementation.

In addition to doubled execution speed, the 77C25 has four times the instruction ROM space and twice the data ROM and RAM space of the 7720. Real savings are now possible, especially where one 77C25 can do the work of and replace two or more 7720s.

The external clock frequency (8.3 MHz maximum) remains the same as for 77C20A/7720A while the internal instruction execution speed is doubled. For most applications, the 77C25 is plug-in compatible with the 77C20A/7720A/77P20.

The feature that distinguishes digital signal processing chips from general-purpose microcomputers is the onchip multiplier necessary for high-speed signal processing algorithms. The 77C25 multiplier is very sophisticated, especially for a low-cost DSP chip; both multiplier inputs can be loaded simultaneously from two separate memory areas. These loading operations are only two of nine operations that can occur during one 122-ns instruction cycle.

For a typical DSP filter application involving many successive multiplications, the 77C25 provides a new multiplication product for addition to a sum of products every 122 nanoseconds. Additionally, during the same instruction, memory data pointers are manipulated, and even a return from subroutine may be executed. Table 1 compares 77C25 with 77C20A.

### **Features**

- Low-power CMOS: 25 mA typical current use (77C25)

- □ Fast instruction execution: 122 ns with 8.192-MHz clock

- □ All instructions execute in one instruction cycle

- □ Drop-in compatible with 77C20A/7720A/77P20

- 16-bit data word

- Multioperation instructions for fast program execution: any part, any combination, or all of the following operations may constitute one instruction that executes in 122 ns.

- Load one multiplier input

- Load the other multiplier input

- Multiply (automatic)

- Load product to output registers (automatic)

- Add product to accumulator

- Move RAM column data pointer

- Move RAM row pointer

- Move data ROM pointer

- Return from subroutine

- Modified Harvard architecture with three separate memory areas

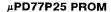

- Instruction ROM (2048 x 24 bits)

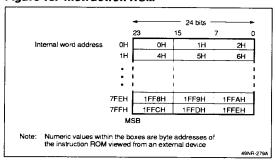

- Data ROM (1024 x 16 bits)

- Data RAM (256 x 16 bits)

- 16 x 16-bit multiplier; 31-bit product with every instruction

- Dual 16-bit accumulators

- External maskable interrupt

- □ Four-level stack for subroutines and/or interrupt

- □ Multiple I/O capabilities

- Serial: 8 or 16-bit (244 ns/bit)

- Parallel: 8 or 16-bit

- -- DMA

- Compatible with most microprocessors, including:

- $-\mu$ PD8080

- $-\mu PD8085$

- $-\mu$ PD8086/88

- -- μPD780 (Z80®)

- $-\mu$ PD78xx family

- Packages: 28-pin DIP, 32-pin SOP, 44-pin PLCC

- Single + 5-volt power supply

Z80 is a registered trademark of Zilog Corporation.

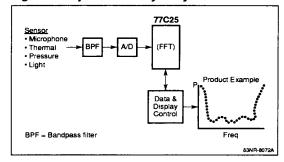

## **Applications**

- Portable telecommunications equipment

- Digital filtering

- High-speed data modems

- □ Fast Fourier transforms (FFT)

50014-1

- Speech synthesis and analysis

- Dual-tone multifrequency (DTMF) transmitters/ receivers

- Equalizers

- Adaptive control

- Numerical processing

## Performance Benchmarks

- $\Box$  Second-order digital filter (biquad): 1.1  $\mu$ s

- □ Sin/cos of angles: 2.58 µs

- $\Box$   $\mu$ -law or A-law to linear conversion: 0.24  $\mu$ s

- □ FFT

- 32-point complex: 0.35 ms64-point complex: 0.8 ms

# Ordering Information

| Package            | ROM                                                                                        | Operating<br>Temperature<br>Range<br>-40 to +85°C                                                      |  |

|--------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| 28-pin plastic DIP | Mask                                                                                       |                                                                                                        |  |

| 32-pin SOP         |                                                                                            |                                                                                                        |  |

| 44-pin PLCC        |                                                                                            |                                                                                                        |  |

| 28-pin plastic DIP | OTP                                                                                        | -10 to +70 °C                                                                                          |  |

| 28-pin ceramic DIP | UVEPROM                                                                                    | _                                                                                                      |  |

| 32-pin SOP         | OTP                                                                                        |                                                                                                        |  |

| 44-pin PLCC        | ОТР                                                                                        |                                                                                                        |  |

|                    | 28-pin plastic DIP 32-pin SOP 44-pin PLCC 28-pin plastic DIP 28-pin ceramic DIP 32-pin SOP | 28-pin plastic DIP 32-pin SOP 44-pin PLCC 28-pin plastic DIP 28-pin ceramic DIP UVEPROM 32-pin SOP OTP |  |

Table 1. Comparison of 77C25 With 77C20A

|                           | 77C25/77P25                 | 77C20A/77P20                |  |  |

|---------------------------|-----------------------------|-----------------------------|--|--|

| Technology                | CMOS/CMOS                   | CMOS/NMOS                   |  |  |

| Instruction cycle         | 122 ns                      | 244 ns                      |  |  |

| Instruction ROM           | 2048 x 24 bits              | 512 x 23 bits               |  |  |

| Data ROM                  | 1024 x 16 bits              | 510 x 13 bits               |  |  |

| Data RAM                  | 256 x 16 bits               | 128 x 16 bits               |  |  |

| Fixed-point<br>multiplier | 16 bits x 16 bits → 31 bits | 16 bits x 16 bits → 31 bits |  |  |

| ALU                       | 16-bit fixed-point          | 16-bit fixed-point          |  |  |

| Accumulator               | 2 x 16 bits                 | 2 x 16 bits                 |  |  |

| Host CPU interface        | 8-bit bus                   | 8-bit bus                   |  |  |

| Serial interface          | One input and one output    | One input and one output    |  |  |

|                           | 4 MHz                       | 2 MHz                       |  |  |

| Temporary registers       | Two                         | One                         |  |  |

Table 1. Comparison of 77C25 With 77C20A (cont)

|                               | 77C25/77P25                                   | 77C20A/77P20               |

|-------------------------------|-----------------------------------------------|----------------------------|

| Additional                    | JDPLN0                                        | _                          |

| instructions                  | JDPLNF                                        |                            |

|                               | Modification of RAM column data pointer M8-MF |                            |

| DMA mode                      | Fully implemented                             | Partially<br>implemented   |

| Package                       | 28-pin DIP                                    | 28-pin DIP                 |

|                               | 44-pin PLCC                                   | 44-pin PLCC                |

|                               | 32-pin SOP                                    | <del>_</del>               |

| Power supply                  | 5 V                                           | 5 V                        |

| Power consumption             | 50 mA (max) @ 8.192<br>MHz                    | 40 mA (max) @ 8.192<br>MHz |

| Power saving mode (when idle) | Yes                                           | No                         |

Since the 77C25 executes an instruction in one external clock cycle (versus two cycles of the same 8.192-MHz clock for 77C20A), the 77C25 may be substituted for a 77C20A (or 7720A or 77P20) in a circuit without modification of that circuit. Hardware/software that implements data transfers—both serial and parallel—between the 77C25 and other devices in an existing 7720 design should use the handshake protocol described in the 77C25 User's Manual.

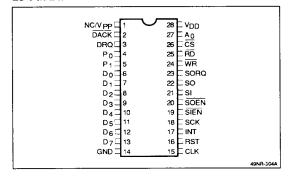

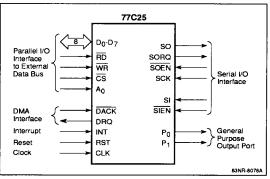

## Pin Configurations

## 28-Pin DIP

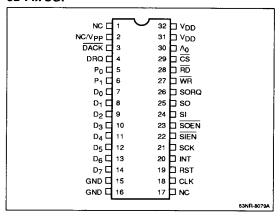

# Pin Configurations (cont)

# 32-Pin SOP

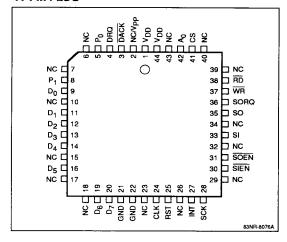

#### 44-Pin PLCC

#### Pin Identification

| Symbol                          | Function                                                                               |  |  |  |

|---------------------------------|----------------------------------------------------------------------------------------|--|--|--|

| A <sub>0</sub>                  | Status/data register select input                                                      |  |  |  |

| CLK                             | Single-phase master clock input                                                        |  |  |  |

| CS                              | Chip select input                                                                      |  |  |  |

| D <sub>0</sub> -D <sub>7</sub>  | Three-state I/O data bus                                                               |  |  |  |

| DACK                            | DMA request acknowledge input                                                          |  |  |  |

| DRQ                             | DMA request output                                                                     |  |  |  |

| INT                             | Interrupt input                                                                        |  |  |  |

| P <sub>0</sub> , P <sub>1</sub> | General-purpose output control lines                                                   |  |  |  |

| RD                              | Read control signal input                                                              |  |  |  |

| RST                             | Reset input                                                                            |  |  |  |

| SCK                             | Serial data I/O clock input                                                            |  |  |  |

| SI                              | Serial data input                                                                      |  |  |  |

| SIEN                            | Serial input enable input                                                              |  |  |  |

| so                              | Three-state serial data output                                                         |  |  |  |

| SOEN                            | Serial output enable input                                                             |  |  |  |

| SORQ                            | Serial data output request                                                             |  |  |  |

| WR                              | Write control signal input                                                             |  |  |  |

| GND                             | Ground                                                                                 |  |  |  |

| V <sub>DD</sub>                 | +5 V power supply                                                                      |  |  |  |

| NC/V <sub>PP</sub>              | 77C25: no connection<br>77P25: +12.5 V programming<br>77P25: +5 V for normal operation |  |  |  |

## **PIN FUNCTIONS**

## A<sub>0</sub> (Status Data Register Select)

This input selects data register for read/write (low) or status register for read (high).

#### CLK

This is the single-phase master clock input.

## CS (Chip Select)

This input enables data transfer through the data port with  $\overline{\text{RD}}$  or  $\overline{\text{WR}}$ .

## D<sub>0</sub>-D<sub>7</sub> (Data Bus)

This three-state I/O data bus transfers data between the data register or status register and the external data bus.

## DACK (DMA Request Acknowledge)

This input indicates to the 77C25 that the data bus is ready for a DMA transfer ( $\overline{DACK} = CS$  and  $A_0 = 0$ ).

## DRQ (DMA Request)

This output signals that the 77C25 is requesting a data transfer on the data bus.

# INT (Interrupt)

A low-to-high transition on this pin executes a call instruction to location 100H if interrupts were previously enabled.

## P<sub>0</sub>, P<sub>1</sub>

These pins are general-purpose output control lines.

# RD (Read Control Signal)

This input latches data from the data or status register to the data port where it is read by an external device.

## RST (Reset)

This input initializes the 77C25 internal logic and sets the PC to 0.

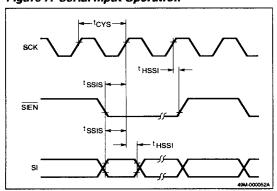

## SCK (Serial Data I/O Clock)

When this input is high, a serial data bit is transferred.

# SI (Serial Data Input)

This pin inputs 8- or 16-bit serial data words from an external device such as an A/D converter.

## SIEN (Serial Input Enable)

This input enables the shift clock to the serial input register.

## SO (Serial Data Output)

This three-state port outputs 8- or 16-bit data words to an external device such as a D/A converter.

## SOEN (Serial Output Enable)

This input enables the shift clock to the serial output register.

# SORQ (Serial Data Output Request)

This output specifies to an external device that the serial data register has been loaded and is ready for output. SORQ is reset when the entire 8- or 16-bit word has been transferred.

## WR (Write Control Signal)

This input writes data from the data port into the data register.

#### GND

This is the connection to ground.

## V<sub>DD</sub> (Power Supply)

This pin is the +5-volt power supply.

## NC/Vpp

This pin is not internally connected in the 77C25. In the 77P25, this pin inputs the programming voltage (V<sub>PP</sub>) when the part is being programmed.

This pin must be connected to  $V_{\text{DD}}$  for normal 77P25 operation.

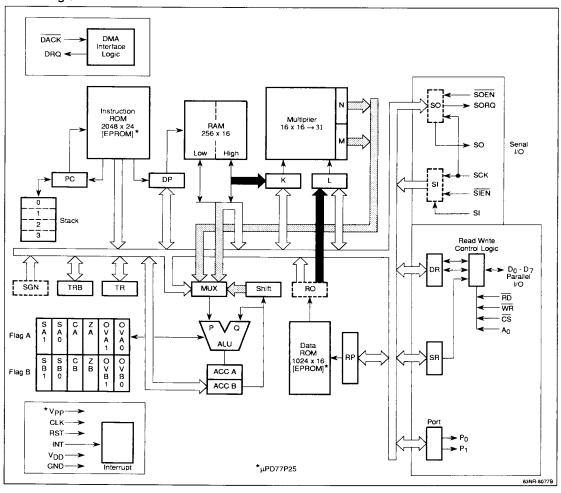

## **Block Diagram**

## **DATA BUSES**

The primary bus (unshaded in the block diagram) makes a data path between all of the registers (including I/O), memory, and the processing sections. This bus is referred to as the IDB (internal data bus). The multiplier input registers K and L can be loaded not only from the IDB but alternatively via buses (darkened in the block diagram) directly from RAM to the K register and directly from data ROM to the L register. Output from the multiplier in the M and N registers is

typically added via buses (shaded in the block diagram) to either accumulator A or B as part of a multioperation instruction.

## **MEMORY**

Memory is divided into three types: instruction ROM, data ROM, and data RAM. The 2048 x 24-bit words of instruction ROM are addressed by an 11-bit program counter that can be modified by an external reset, interrupt, call, jump, or return instruction.

The data ROM is organized in 1024 x 16-bit words that are addressed through a 10-bit ROM pointer (RP register). The RP may be modified simultaneously with arithmetic instructions so that the next value is available for the next instruction. The data ROM is ideal for storing the necessary coefficients, conversion tables, and other constants for signal and math processing.

The data RAM is 256 x 16-bit words and is addressed through an 8-bit data pointer (DP register). The DP has extensive addressing features that operate simultaneously with arithmetic instructions, eliminating additional time for addressing or address modification.

## **ARITHMETIC CAPABILITIES**

One of the unique features of the 77C25 architecture is its arithmetic facilities. With a separate multiplier, ALU, and multiple internal data paths, the 77C25 is capable of carrying out a multiply, an add or other arithmetic operation, and a data move between internal registers in a single instruction cycle.

#### ALU

The ALU is a 16-bit two's complement unit capable of executing 16 distinct operations on data routed via the P and Q ALU inputs.

## Accumulators (ACCA/ACCB)

Associated with the ALU are two 16-bit accumulators, each with its own set of flags, which are updated at the end of each arithmetic instruction. Table 2 shows the ACC A/B flag registers. In addition to zero result, sign, carry, and overflow flags, the 77C25 incorporates auxiliary overflow and sign flags (SA1, SB1, OVA1, OVB1). These flags enable the detection of an overflow condition and maintain the correct sign after as many as three successive additions or subtractions.

Table 2. ACC A/B Flag Registers

| Flag A | SA1 | SA0 | CA | ZA | OVA1 | OVA0 |

|--------|-----|-----|----|----|------|------|

| Flag B | SB1 | SB0 | СВ | ZB | OVB1 | OVB0 |

# Sign Register (SGN)

When OVA1 is set, the SA1 bit will hold the corrected sign of the overflow. The SGN register will use SA1 to automatically generate saturation constants 7FFH(+) or 8000H(-) to permit efficient limiting of a calculated value. The SGN register is not affected by arithmetic operations on accumulator B, but flags SB1, SB0, CB, ZB, OVB1, and OVB0 are affected.

## Multiplier

Thirty-one bit results are developed by a 16 x 16-bit two's complement multiplier in 122 ns. The result is automatically latched to two 16-bit registers, M and N, at the end of each instruction cycle. The sign bit and 15 higher bits are in M and the 15 lower bits are in N; the LSB in N is zero. A new product is available for use after every instruction cycle, providing significant advantages in maximizing processing speed for real-time signal processing.

#### Stack

The 77C25 contains a four-level program stack for efficient program usage and interrupt handling.

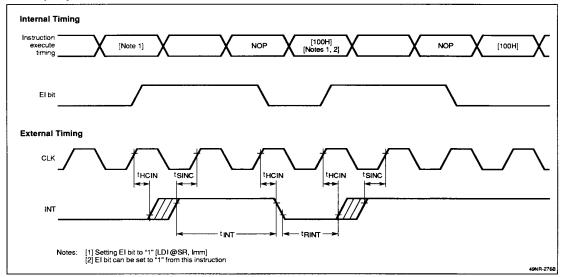

#### Interrupt

The 77C25 supports a single-level interrupt. Upon sensing a high level on the INT terminal, a subroutine call to location 100H is executed. The El bit of the status register automatically resets to 0, disabling the interrupt facility until it is reenabled under program control.

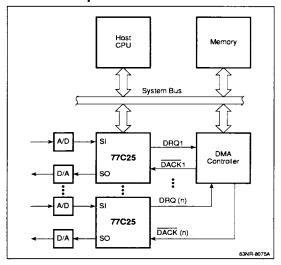

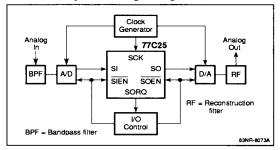

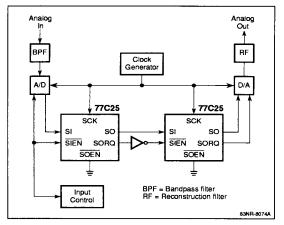

## INPUT/OUTPUT

The 77C25 has three communication ports as shown in figure 1: two serial and one 8-bit parallel, each with its own control lines for interface handshaking. Parallel port operation is software-configurable to be in either polled mode or DMA mode. A general-purpose, two-line output port rounds out a full complement of interface capability.

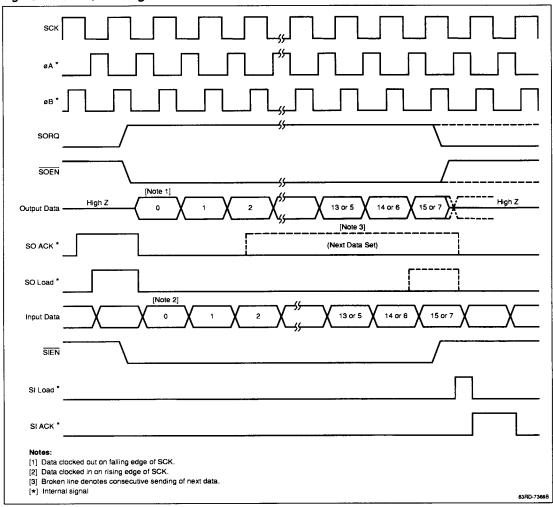

## Serial I/O

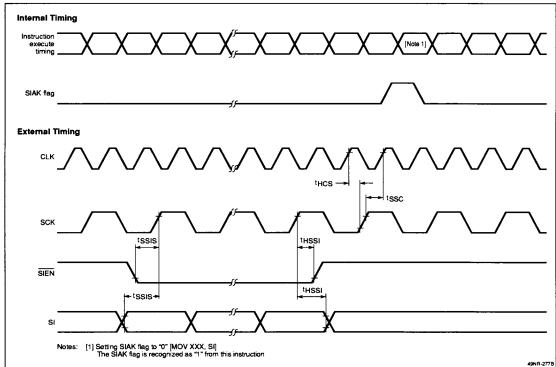

The two shift registers (SI, SO) are software-configurable to single- or double-byte transfers. The shift registers are externally clocked (SCK) to provide a simple interface between the 77C25 and serial peripherals such as A/D and D/A converters, codecs, or other 77C25's. Figure 2 shows serial I/O timing

3b-6

Figure 1. 77C25 Communication Ports

## Parallel I/O

The 8-bit parallel I/O port may be used for transferring data or reading the 77C25 status as shown in table 3. Data transfer is handled through a 16-bit data register (DR) that is software-configurable for double- or single-byte data transfers. The port is ideally suited for operating with 8080, 8085, and 8086 processor buses and may be used with other processors and computer systems.

## **DMA Mode Option**

Parallel data transfers may be controlled (optionally) via DMA control lines DRQ and DACK. DMA mode allows high-speed transfers and reduced processor overhead. When in DMA mode, DACK input resets DRQ output when data transfer is completed.

Note: The RQM bit of the status register is affected by read/write operations in DMA mode the same as non-DMA mode. (In 7720 operation, RQM is not affected when in DMA mode.)

Table 3. Parallel R/W Operation

| CS | $A_0$ | WR | RD | Operation                                                            |

|----|-------|----|----|----------------------------------------------------------------------|

| 1  | Х     | Х  | Х  | No effect on internal operation; D <sub>0</sub> -D <sub>7</sub> are  |

| X  | X     | 1  | 1  | at high impedance levels.                                            |

| 0  | 0     | 0  | 1  | Data from D <sub>0</sub> -D <sub>7</sub> is latched to DR (Note 1)   |

| 0  | 0     | 1  | 0  | Contents of DR are output to D <sub>0</sub> -D <sub>7</sub> (Note 1) |

| 0  | 1     | 0  | 1  | Illegal (SR is read only)                                            |

| 0  | 1     | 1  | 0  | Eight MSBs of SR are output to D <sub>0</sub> -D <sub>7</sub>        |

| 0  | Х     | 0  | 0  | Illegal (may not read and write simultaneously)                      |

#### Notes:

Eight MSBs or LSBs of data register (<u>DR</u>) are used, depending on DR status bit (<u>DRS</u>). The condition of <u>DACK</u> = 0 is equivalent to A<sub>0</sub> = CS = 0.

## Status Register

The status register, (figure 3, table 4) is a 16-bit register in which the 8 most significant bits may be read by the system's microprocessor for the latest parallel data I/O status. The RQM and DRS bits can only be affected by parallel data moves. The other bits can be written to (or read) by the 77C25 load immediate (LD) or move (MOV) instruction. The El bit is automatically reset when an interrupt is serviced.

3b-8

Figure 3. Status Register

| 15  | 14   | 13   | 12  | 11  | 10  | 9   | 8   |

|-----|------|------|-----|-----|-----|-----|-----|

| RQM | USF1 | USF0 | DRS | DMA | DRC | soc | SIC |

| MSB | •    |      |     | •   | •   |     |     |

| 7   | 6    | 5    | 4   | 3   | 2   | 1   | 0   |

| EI  | 0    | 0    | 0   | 0   | 0   | P1  | P0  |

|     | •    |      |     |     |     |     | LSB |

Table 4. Status Register Flags

| Flag                                                                                                                | Description                                                                                                                               |  |

|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| RQM (Request for master)                                                                                            | A read or write from DR to IDB sets RQM = 1. An external read (write) resets RQM = 0.                                                     |  |

| USF1 and USF0 General-purpose flags that may be rea<br>(User flags 1 external processor for user-defined signand 0) |                                                                                                                                           |  |

| DRS (DR<br>status)                                                                                                  | For 16-bit DR transfers (DRC = 0), DRS = 1 after the first 8 bits have been transferred. DRS = 0 after all 16 bits have been transferred. |  |

| DMA (DMA<br>enable)                                                                                                 | DMA = 0 (Non-DMA transfer mode) DMA = 1 (DMA transfer mode)                                                                               |  |

| DRC (DR control)                                                                                                    | DRC = 0 (16-bit mode) DRC = 1 (8-bit mode)                                                                                                |  |

| SOC (SO control)                                                                                                    | SOC = 0 (16-bit mode)<br>SOC = 1 (8-bit mode)                                                                                             |  |

| SIC (SI control)                                                                                                    | SIC = 0 (16-bit mode)<br>SIC = 1 (8-bit mode)                                                                                             |  |

| El (Enable interrupt)                                                                                               | El = 0 (interrupts disabled)<br>El = 1 (interrupts enabled)                                                                               |  |

| P1, P0 (Ports 0 and 1)                                                                                              | P0 and P1 directly control the state of output pins $\rm P_0$ and $\rm P_1$                                                               |  |

## **Temporary Registers**

The 77C25 has two 16-bit temporary registers.

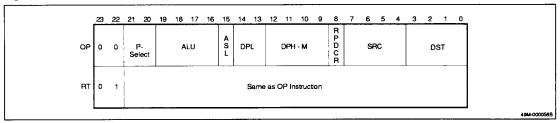

## INSTRUCTIONS

The 77C25 has three types of instructions: OP/RT (operation/return), JP (jump), and LD (load immediate). Each type takes the form of a 24-bit word and executes in 122 ns.

## Instruction Timing

To control the execution of instructions, the external 8-MHz clock is divided into phases for internal execution. The various elements of the 24-bit instruction word are executed in a set order. Multiplication automatically begins first. Also, data moves from source to destination before other elements of the instruction.

Data being moved on the internal data bus (IDB) is available for use in ALU operations (if P-select field of

the instruction specifies IDB). However, if the accumulator specified in the ASL field is also specified as the destination of the data move, the ALU operation becomes a NOP, as the data move supersedes the ALU operation.

Pointer modifications occur at the end of the instruction cycle after their values have been used for data moves. The result of multiplication is available at the end of the instruction cycle for possible use in the next instruction. If a return is specified as part of an OP instruction, it is executed last.

An assembly language OP instruction may consist of what looks like one to six lines of assembly code, but all of these lines are assembled together into one 24-bit instruction word. Therefore, the order of the six lines makes no difference in the order of execution described above. However, for understanding 77C25 operation and to eliminate confusion, assembly code should be written in the order described; that is: data move, ALU operations, data pointer modifications, and then return.

## **OP/RT Instructions**

Figure 4 illustrates the OP/RT (operation/return) instruction field specification. This is really one instruction type capable of executing all ALU functions listed in table 6.

The ALU functions operate on the value specified by the P-select field (table 5).

The RT indicates an option in bit  $D_{22}$  that causes a return from subroutine or interrupt service.

Besides the arithmetic functions, this instruction can also (1) modify the RAM data pointer DP, (2) modify the data ROM pointer RP, and (3) move data along the on-chip data bus from a source register to a destination register. Tables 7, 8, 9, and 10 show the ASL, DPL, DPH, and RPDCR fields, respectively. The possible source and destination registers are listed in tables 11 and 12.

Table 5. P-Select Field

| Mnemonic | D <sub>21</sub> | D <sub>20</sub> | ALU Input           |

|----------|-----------------|-----------------|---------------------|

| RAM      | 0               | 0               | RAM                 |

| IDB      | 0               | 1               | * Internal data bus |

| M        | 1               | 0               | M register          |

| N        | 1               | 1               | N register          |

<sup>\*</sup> Any value on the on-chip data bus. Value may be selected from any of the source registers listed in table 11.

Figure 4. OP/RT Instruction Field

Table 6. ALU Field

| Mnemonic | D <sub>19</sub> | D <sub>18</sub> | D <sub>17</sub> | D <sub>16</sub> | ALU Function                      | SA1, SB1 | SAO, SBO | CA, CB | ZA, ZB | OVA1, OVB1 | OVA0, OVB0 |

|----------|-----------------|-----------------|-----------------|-----------------|-----------------------------------|----------|----------|--------|--------|------------|------------|

| NOP      | 0               | 0               | 0               | 0               | No operation                      |          | _        | _      | _      | _          |            |

| OR       | 0               | 0               | 0               | 1               | OR                                | ×        | Δ        | 0      | Δ      | 0          | 0          |

| AND      | 0               | 0               | 1               | 0               | AND                               | ×        | Δ        | 0      | Δ      | 0          | 0          |

| XOR      | 0               | 0               | 1               | 1               | Exclusive OR                      | ×        | Δ        | 0      | Δ      | 0          | 0          |

| SUB      | 0               | 1               | 0               | 0               | Subtract                          | Δ        | Δ        | Δ      | Δ      | Δ          | Δ          |

| ADD      | 0               | 1               | 0               | 1               | Add                               | Δ        | Δ        | Δ      | Δ      | Δ          | Δ          |

| SBB      | 0               | 1               | 1               | 0               | Subtract with borrow              | Δ        | Δ        | Δ      | Δ      | Δ          | Δ          |

| ADC      | 0               | 1               | 1               | 1               | Add with carry                    | Δ        | Δ        | Δ      | Δ      | Δ          | Δ          |

| DEC      | 1               | 0               | 0               | 0               | Decrement ACC                     | Δ        | Δ        | Δ      | Δ      | Δ          | Δ          |

| INC      | 1               | 0               | 0               | 1               | Increment ACC                     | Δ        | Δ        | Δ      | Δ      | Δ          | Δ          |

| CMP      | 1               | 0               | 1               | 0               | Complement ACC (one's complement) | x        | Δ        | 0      | Δ      | 0          | 0          |

| SHR1     | 1               | 0               | 1               | 1               | 1-bit right shift                 | ×        | Δ        | Δ      | Δ      | 0          | 0          |

| SHL1     | 1               | 1               | 0               | 0               | 1-bit left shift                  | x        | Δ        | Δ      | Δ      | 0          | 0          |

| SHL2     | 1               | 1               | 0               | 1               | 2-bit left shift                  | ×        | Δ        | 0      | Δ      | 0          | 0          |

| SHL4     | 1               | 1               | 1               | 0               | 4-bit left shift                  | х        | Δ        | 0      | Δ      | 0          | 0          |

| XCHG     | 1               | 1               | 1               | 1               | 8-bit exchange                    | х        | Δ        | 0      | Δ      | 0          | 0          |

#### Symbols

- $\triangle$  May be affected, depending on the results

- Previous status can be held

- 0 Reset

- x Indefinite

Table 7. ASL Field

| Mnemonic | D <sub>15</sub> | ACC Selection |

|----------|-----------------|---------------|

| ACCA     | 0               | ACCA          |

| ACCB     | 1               | ACCB          |

#### Table 8. DPL Field

| Mnemonic | D <sub>14</sub> | D <sub>13</sub> | Low DP Modify (DP <sub>3</sub> -DP <sub>0</sub> ) |

|----------|-----------------|-----------------|---------------------------------------------------|

| DPNOP    |                 | 213             |                                                   |

|          |                 | <u>U</u>        | No operation                                      |

| DPINC    | 0               | 1               | Increment DPL                                     |

| DPDEC    | 1               | 0               | Decrement DPL                                     |

| DPCLR    | 1               | 1               | Clear DPL                                         |

#### Table 9. DPH Field

| Mnemonic | D <sub>12</sub> | D <sub>11</sub> | D <sub>10</sub> | D <sub>9</sub> | High DP Modify                                                             |

|----------|-----------------|-----------------|-----------------|----------------|----------------------------------------------------------------------------|

| МО       | 0               | 0               | 0               | 0              | Exclusive OR of DPH                                                        |

| M1       | 0               | 0               | 0               | 1              | (DP <sub>7</sub> -DP <sub>4</sub> ) with the mask<br>defined by the 4 bits |

| M2       | 0               | 0               | 1               | 0              | (D <sub>12</sub> -D <sub>9</sub> ) of the DPH field                        |

| МЗ       | 0               | 0               | 1               | 1              | •                                                                          |

| M4       | 0               | 1               | 0               | 0              | •                                                                          |

| M5       | 0               | 1               | 0               | 1              | •                                                                          |

| M6       | 0               | 1               | 1               | 0              | •                                                                          |

| M7       | 0               | 1               | 1               | 1              | •                                                                          |

| M8       | 1               | 0               | 0               | 0              | •                                                                          |

| M9       | 1               | 0               | 0               | 1              |                                                                            |

| MA       | 1               | 0               | 1               | 0              | •                                                                          |

| MB       | 1               | 0               | 1               | 1              | •                                                                          |

| MC       | 1               | 1               | 0               | 0              |                                                                            |

| MD       | 1               | 1               | 0               | 1              |                                                                            |

| ME       | 1               | 1               | 1               | 0              | -                                                                          |

| MF       | 1               | 1               | 1               | 1              | -                                                                          |

#### Table 10. RPDCR Field

| Mnemonic | D <sub>8</sub> | RP operation |

|----------|----------------|--------------|

| RPNOP    | 0              | No operation |

| RPDEC    | 1              | Decrement RP |

#### Table 11. SRC Field

| Mnemonic | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | Source Register       |

|----------|----------------|----------------|----------------|----------------|-----------------------|

| NON/TRB  | 0              | 0              | 0              | 0              | TRB (Note 1)          |

| Α        | 0              | 0              | 0              | 1              | ACCA (Accumulator A)  |

| В        | 0              | 0              | 1              | 0              | ACCB (Accumulator B)  |

| TR       | 0              | 0              | 1              | 1              | TR temporary register |

| DP       | 0              | 1              | 0              | 0              | DP data pointer       |

| RP       | 0              | 1              | 0              | 1              | RP ROM pointer        |

| RO       | 0              | 1              | 1              | 0              | RO ROM output data    |

| SGN      | 0              | 1              | 1              | 1              | SGN sign register     |

| DR       | 1              | 0              | 0              | 0              | DR data register      |

| DRNF     | 1              | 0              | 0              | 1              | DR no flag (Note 2)   |

| SR       | 1              | 0              | 1              | 0              | SR status register    |

Table 11. SRC Field (cont)

| Mnemonic | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | Source Register           |  |

|----------|----------------|----------------|----------------|----------------|---------------------------|--|

| SIM      | 1              | 0              | 1              | 1              | SI serial in MSB (Note 3) |  |

| SIL      | 1              | 1              | 0              | 0              | SI serial in LSB (Note 4) |  |

| К        | 1              | 1              | 0              | 1              | K register                |  |

| L        | 1              | 1              | 1              | 0              | L register                |  |

| MEM      | 1              | 1              | 1              | 1              | RAM                       |  |

#### Notes:

- (1) Contents of TRB register are also output if NON is specified.

- (2) DR to IDB, RQM not set. in DMA, DRQ not set.

- (3) First bit in goes to MSB, last bit to LSB.

- (4) First bit goes to LSB, last bit to MSB (bit reversed).

# Jump Instructions

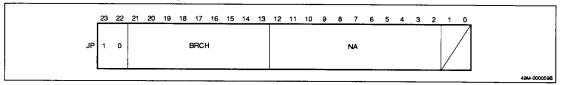

Figure 5 shows the JP instruction field specification. Bits  $D_{21}$ ,  $D_{20}$ , and  $D_{19}$  of the BRCH field identify the three types of instructions: unconditional jump (100), subroutine call (101), and conditional jump (010). Table 13 lists the instruction mnemonics for the complete BRCH field, bits  $D_{21}$ - $D_{13}$ .

All the instructions in table 13—if unconditional or if the specified condition is true—take their next program execution address from the next address field (NA) in figure 5. Otherwise, PC = PC + 1.

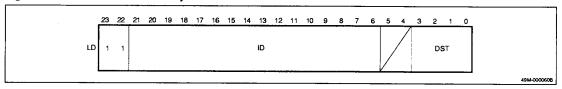

## Load Data (LD) Instructions

Figure 6 shows the LD instruction field specification.

The load data instruction will take the 16-bit value contained in the immediate data field (ID) and place it in the register specified by the destination field (DST). This is the same as the DST field (table 12) in the OP/RT instruction.

Table 12. DST Field

| Mnemonic | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | Do | Destination Register    |  |

|----------|----------------|----------------|----------------|----|-------------------------|--|

| @NON     | 0              | 0              | 0              | 0  | No register             |  |

| @A       | 0              | 0              | 0              | 1  | ACCA (Accumulator A)    |  |

| @B       | 0              | 0              | 1              | 0  | ACCB (Accumulator B)    |  |

| @TR      | 0              | 0              | 1              | 1  | TR temporary register   |  |

| @DP      | 0              | 1              | 0              | 0  | DP data pointer         |  |

| @ RP     | 0              | 1              | 0              | 1  | RP ROM pointer          |  |

| @DR      | 0              | 1              | 1              | 0  | DR data register        |  |

| @SR      | 0              | 1              | 1              | 1  | SR status register      |  |

| @SOL     | 1              | 0              | 0              | 0  | SO serial out LSB (Note |  |

Table 12. DST Field (cont)

| Mnemonic | $D_3$ | $D_2$ | $D_1$ | $D_0$ | Destination Register            |

|----------|-------|-------|-------|-------|---------------------------------|

| @SOM     | 1     | 0     | 0 0   |       | SO serial out MSB<br>(Note 2)   |

| @K       | 1     | 0     | 1     | 0     | K (Mult)                        |

| @KLR     | 1     | 0     | 1     | 1     | IDB → K, ROM → L<br>(Note 3)    |

| @KLM     | 1     | 1     | 0     | 0     | Hi RAM → K, IDB → L<br>(Note 4) |

| @L       | 1     | 1     | 0     | 1     | L register                      |

| @TRB     | 1     | 1     | 1     | 0     | TRB register                    |

| Mnemonic | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | Destination Register |

|----------|----------------|----------------|----------------|----------------|----------------------|

| @МЕМ     | 1              | 1              | 1              | 1              | RAM                  |

#### Notes:

- (1) LSB is first bit out.

- (2) MSB is first bit out.

- (3) Internal data bus to K, and ROM to L register.

- (4) Contents of RAM address specified by DP<sub>6</sub> = 1 is placed in K register, IDB is placed in L (that is: 1, DP<sub>5</sub>, DP<sub>4</sub>, DP<sub>3</sub>-DP<sub>0</sub>).

Figure 5. JP Instruction Field Specification

Figure 6. LD Instruction Field Specification

Table 13. BRCH Field

| Mnemonic | D <sub>21</sub> -D <sub>19</sub> | D <sub>18</sub> -D <sub>16</sub> | D <sub>15</sub> -D <sub>13</sub> | Conditions   |

|----------|----------------------------------|----------------------------------|----------------------------------|--------------|

| JMP      | 1 0 0                            | 0 0 0                            | 000                              | No condition |

| CALL     | 1 0 1                            | 0 0 0                            | 0 0 0                            | No condition |

| JNCA     | 0 1 0                            | 0 0 0                            | 000                              | CA = 0       |

| JCA      | 0 1 0                            | 0 0 0                            | 0 1 0                            | CA = 1       |

| JNCB     | 0 1 0                            | 0 0 0                            | 1 0 0                            | CB = 0       |

| JCB      | 0 1 0                            | 000                              | 1 1 0                            | CB = 1       |

| JNZA     | 0 1 0                            | 0 0 1                            | 000                              | ZA = 0       |

| JZA      | 0 1 0                            | 0 0 1                            | 010                              | ZA = 1       |

| JNZB     | 0 1 0                            | 0 0 1                            | 1 0 0                            | ZB = 0       |

| JZB      | 0 1 0                            | 0 0 1                            | 1 1 0                            | ZB = 1       |

| JNOVAO   | 0 1 0                            | 0.1 0                            | 000                              | OVA0 = 0     |

| JOVA0    | 0 1 0                            | 0 1 0                            | 0 1 0                            | OVA0 = 1     |

| JNOVB0   | 0 1 0                            | 0 1 0                            | 100                              | OVB0 = 0     |

| JOVB0    | 0 1 0                            | 0 1 0                            | 1 1 0                            | OVB0 = 1     |

| JNOVA1   | 0 1 0                            | 0 1 1                            | 0 0 0                            | OVA1 = 0     |

| JOVA1    | 0 1 0                            | 0 1 1                            | 0 1 0                            | OVA1 = 1     |

| Mnemonic | D <sub>21</sub> -D <sub>19</sub> | D <sub>18</sub> -D <sub>16</sub> | D <sub>15</sub> -D <sub>13</sub> | Conditions |

|----------|----------------------------------|----------------------------------|----------------------------------|------------|

| JNOVB1   | 0 1 0                            | 0 1 1                            | 1 0 0                            | OVB1 = 0   |

| JOVB1    | 0 1 0                            | 0 1 1                            | 1 1 0                            | OVB1 = 1   |

| JNSA0    | 0 1 0                            | 1 0 0                            | 0 0 0                            | SA0 = 0    |

| JSA0     | 0 1 0                            | 1 0 0                            | 0 1 0                            | SA0 = 1    |

| JNSB0    | 0 1 0                            | 1 0 0                            | 1 0 0                            | SB0 = 0    |

| JSB0     | 0 1 0                            | 1 0 0                            | 1 1 0                            | SB0 = 1    |

| JNSA1    | 0 1 0                            | 1 0 1                            | 000                              | SA1 = 0    |

| JSA1     | 0 1 0                            | 1 0 1                            | 0 1 0                            | SA1 = 1    |

| JNSB1    | 0 1 0                            | 1 0 1                            | 1 0 0                            | SB1 = 0    |

| JSB1     | 0 1 0                            | 1 0 1                            | 1 1 0                            | SB1 = 1    |

| JDPL0    | 0 1 0                            | 1 1 0                            | 0 0 0                            | DPL = 0    |

| JDPLN0   | 0 1 0                            | 1 1 0                            | 0 0 1                            | DPL ≠ 0    |

| JDPLF    | 0 1 0                            | 1 1 0                            | 0 1 0                            | DPL = FH   |

| JDPLNF   | 0 1 0                            | 1 1 0                            | 0 1 1                            | DPL ≠ FH   |

| JNSIAK   | 0 1 0                            | 1 1 0                            | 1 0 0                            | SI ACK = 0 |

| JSIAK    | 0 1 0                            | 1 1 0                            | 1 1 0                            | SI ACK = 1 |

# Table 13. BRCH Field (cont)

| Mnemonic | D <sub>21</sub> -D <sub>19</sub> | D <sub>18</sub> -D <sub>16</sub> | D <sub>15</sub> -D <sub>13</sub> | Conditions |

|----------|----------------------------------|----------------------------------|----------------------------------|------------|

| JNSOAK   | 010                              | 1 1 1                            | 0 0 0                            | SO ACK = 0 |

| JSOAK    | 0 1 0                            | 1 1 1                            | 0 1 0                            | SO ACK = 1 |

| JNRQM    | 0 1 0                            | 1 1 1                            | 1 0 0                            | RQM = 0    |

| JRQM     | 010                              | 1 1 1                            | 1 1 0                            | RQM = 1    |

## **ELECTRICAL SPECIFICATIONS**

# **Absolute Maximum Ratings**

T<sub>A</sub> = 25°C unless otherwise specified

| A = 25 C unless otherwise specified                                                                        |                                              |  |  |  |  |

|------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|--|--|--|

| Supply voitage, V <sub>DD</sub>                                                                            | -0.5 to +7.0 V                               |  |  |  |  |

| V <sub>PP</sub> (77P25)                                                                                    | -0.5 to +13.5 V                              |  |  |  |  |

| Input voltage, V <sub>I</sub>                                                                              | - 0.5 to V <sub>DD</sub> + 0.5 V             |  |  |  |  |

| V <sub>RST</sub> (77P25)                                                                                   | -0.5 to + 13 V                               |  |  |  |  |

| Output voltage, V <sub>O</sub>                                                                             | - 0.5 to V <sub>DD</sub> + 0.5 V             |  |  |  |  |

| Storage temperature, T <sub>STG</sub>                                                                      | -65 to 150°C                                 |  |  |  |  |

| Operating temperature, T <sub>OPT</sub><br>77C25/77C25-10<br>77P25 (Normal operation)<br>77P25 (PROM mode) | -40 to +80°C<br>-10 to +70°C<br>+20 to +30°C |  |  |  |  |

|                                                                                                            |                                              |  |  |  |  |

Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage.

# **Recommended Operating Conditions**

| Parameter                           | Symbol             | Min  | Тур  | Max                   | Unit | Conditions                   |

|-------------------------------------|--------------------|------|------|-----------------------|------|------------------------------|

| Supply voltage                      | V <sub>DD</sub>    | 4.5  | 5.0  | 5.5                   | ٧    | Normal operation             |

|                                     |                    | 5.7  | 6.0  | 6.25                  | ٧    | Programming*                 |

|                                     | V <sub>PP</sub> *  | 4.5  | 5.0  | 5.5                   | ٧    | Reading and normal operation |

|                                     |                    | 12   | 12.5 | 12.8                  | V    | Programming                  |

| Input voltage, low                  | V <sub>IL</sub>    | -0.3 |      | 0.8                   | ν    |                              |

| Input voltage, high                 | V <sub>IH</sub>    | 2.2  |      | V <sub>DD</sub> + 0.3 | ٧    | •                            |

| CLK input voltage, low              | V <sub>ILC</sub>   | -0.3 |      | 0.5                   | V    | •                            |

| CLK input voltage, high             | VIHC               | 3.5  |      | V <sub>DD</sub> + 0.3 | ٧    | •                            |

| Input voltage for setting PROM mode | V <sub>RST</sub> * | 11.5 | 12.0 | 12.5                  | ٧    | Reading and writing          |

| Operating temperature               | Торт               | -40  | + 25 | + 85                  | °C   | 77C25/77C25-10               |

|                                     |                    | -10  | + 25 | +70                   | °C   | Normal operation*            |

|                                     |                    | +20  | + 25 | + 30                  | °C   | PROM mode*                   |

<sup>\*</sup> For μPD77P25

# DC Characteristics, Normal

$T_A = -40 \text{ to } + 85^{\circ}\text{C} (77C25/77C25-10), -10 \text{ to } 70^{\circ}\text{C} (77P25); V_{DD} = 4.5 \text{ to } 5.5 \text{ V}$

| Parameter                    | Symbol           | Min                 | Тур | Max  | Unit | Conditions                            |

|------------------------------|------------------|---------------------|-----|------|------|---------------------------------------|

| Output voltage, low          | V <sub>OL</sub>  |                     |     | 0.45 | ٧    | I <sub>OL</sub> = 2.0 mA              |

| Output voltage, high         | V <sub>OH</sub>  | 0.7 V <sub>DD</sub> |     |      | V    | I <sub>OH</sub> = 400 μA              |

| Input leakage current, low   | ILIL             |                     |     | -10  | μΑ   | V <sub>IN</sub> = 0 V                 |

| Input leakage current, high  | l <sub>LiH</sub> |                     |     | 10   | μΑ   | $V_{IN} = V_{DD}$                     |

| Output leakage current, low  | l <sub>LOL</sub> |                     |     | -10  | μΑ   | V <sub>OUT</sub> = 0.47 V             |

| Output leakage current, high | l <sub>LOH</sub> |                     |     | 10   | μΑ   | $V_{OUT} = V_{DD}$                    |

| Supply current (77C25)       | IDD              |                     | 25  | 50   | mA   | f <sub>CLK</sub> = 8.192 MHz          |

|                              |                  |                     | 15  | 25   | mA   | f <sub>CLK</sub> = 8.192 MHz; RST = 1 |

| Supply current (77P25)       | IDD              |                     | 35  | 60   | mA   | f <sub>CLK</sub> = 8.192 MHz          |

|                              |                  |                     | 20  | 35   | mA   | f <sub>CLK</sub> = 8.192 MHz; RST = 1 |

|                              | lpp              |                     |     | 1    | mA   |                                       |

# DC Characteristics, PROM Mode

$T_A = +20 \text{ to } +30^{\circ}\text{C}; V_{DD} = 5.75 \text{ to } 6.25 \text{ V}$

| Parameter                | Symbol           | Min | Тур | Max | Unit | Conditions                         |

|--------------------------|------------------|-----|-----|-----|------|------------------------------------|

| Input leakage<br>current | I <sub>RST</sub> |     |     | 30  | μΑ   | V <sub>RST</sub> = 12.0<br>± 0.5 V |

| Supply current           | lcc              |     |     | 60  | mA   |                                    |

|                          | lpp              |     |     | 30  | mA   | •                                  |

# Capacitance

$T_A = 25^{\circ}C; V_{DD} = 0 \text{ V}$

| Parameter            | Symbol           | Тур | Max | Unit | Conditions |

|----------------------|------------------|-----|-----|------|------------|

| CLK, SCK capacitance | Сф               |     | 20  | pF   | fc = 1 MHz |

| Input capacitance    | CIN              |     | 20  | рF   |            |

| Output capacitance   | C <sub>OUT</sub> |     | 20  | pF   | •          |

## **AC Characteristics**

$T_A = -40$  to  $85^{\circ}$ C (77C25/77C25-10), -10 to  $+70^{\circ}$ C (77P25);  $V_{DD} = 4.5$  to 5.5 V

| Parameter                             | Symbol            | Min                 | Тур | Max  | Unit     | Conditions                              |

|---------------------------------------|-------------------|---------------------|-----|------|----------|-----------------------------------------|

| Clock                                 |                   |                     |     |      |          |                                         |

| CLK cycle time                        | tcyc              |                     |     |      |          | Measuring at 2 V                        |

| 77C25/77P25                           |                   | 120                 | 122 | 2000 | ns       |                                         |

| 77C25-10                              |                   | 100                 | 100 | 2000 | ns       | _                                       |

| CLK pulse width                       | tcc               |                     |     |      |          |                                         |

| 77C25<br>77P25                        |                   | 55<br>60            |     |      | ns       |                                         |

| 77C25-10                              |                   | 45                  |     |      | ns<br>ns |                                         |

| CLK rise time                         | t <sub>CR</sub>   |                     |     | 10   | ns       | Measuring at 1 and 3 V                  |

| CLK fall time                         | tor               |                     |     | 10   | ns       |                                         |

| SCK cycle time                        |                   |                     |     |      |          | , ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

| 77C25/77P25                           | t <sub>CYS</sub>  | 240                 | 244 |      | ns       |                                         |

| 77C25-10                              |                   | 200                 | 200 |      | ns       |                                         |

| SCK high pulse with                   | tssH              |                     |     |      |          | _                                       |

| 77C25/77P25                           | .99Ц              | 100                 |     |      | ns       |                                         |

| 77C25-10                              |                   | 80                  |     |      | ns       |                                         |

| SCK low pulse width                   | tssl              |                     |     |      |          | _                                       |

| 77C25/77P25                           |                   | 100                 |     |      | ns       |                                         |

| 77C25-10                              |                   | 80                  |     |      | ns       | _                                       |

| SCK rise time                         | tsR               |                     |     | 20   | ns       | _                                       |

| SCK fall time                         | t <sub>SF</sub>   |                     |     | 20   | ns       |                                         |

| Host Interface Timing                 |                   |                     |     |      |          |                                         |

| A0, CS, DACK setup time for RD        | tsan              | 0                   |     |      | ns       |                                         |

| A0, CS, DACK hold time for RD         | tHRA              | 0                   |     |      | ns       | _                                       |

| RD pulse width                        | twrp              |                     |     |      |          | _                                       |

| 77C25/77P25                           |                   | 120                 |     |      | ns       |                                         |

| 77C25-10                              |                   | 100                 |     |      | ns       |                                         |

| A0, CS, DACK setup time for WR        | t <sub>SAW</sub>  | 0                   |     |      | ns       |                                         |

| A0, CS, DACK hold time for WR         | t <sub>HWA</sub>  | 0                   |     |      | ns       |                                         |

| WR pulse width                        | twwn              |                     |     |      |          | _                                       |

| 77C25/77P25                           |                   | 120                 |     |      | ns       |                                         |

| 77C25-10                              |                   | 100                 |     |      | ns       | _                                       |

| Data setup time for WR                | t <sub>SDW</sub>  |                     |     |      |          |                                         |

| 77C25/77P25                           |                   | 100                 |     |      | ns       |                                         |

| 77C25-10                              |                   | 80                  |     |      | ns       |                                         |

| Data hold time for WR                 | thwp              | 0                   |     |      | ns       | _                                       |

| RD, WR recovery time<br>77C25/77P25   | <sup>t</sup> RV   | 100                 |     |      |          |                                         |

| 77C25/77P25<br>77C25-10               |                   | 100<br>80           |     |      | ns<br>ns |                                         |

| DACK hold time for DRQ                | t <sub>HRQA</sub> | 0.5t <sub>CYC</sub> |     |      | ns       | _                                       |

| RD, WR setup time for CLK             | tsrwc             | 50                  |     |      | ns       | Note 1                                  |

| RD, WR hold time for CLK              | tHCRW             | 50                  |     |      | ns       | Note 1                                  |

| Host Interface Switching              | TIONW             |                     |     |      |          |                                         |

|                                       | •                 |                     |     |      |          |                                         |

| RD ↓ → data delay time<br>77C25/77P25 | t <sub>DRD</sub>  |                     |     | 100  | ns       |                                         |

| 77C25/77725                           |                   |                     |     | 80   | ns       |                                         |

| AC | Characteristics | (cont) | ١ |

|----|-----------------|--------|---|

|----|-----------------|--------|---|

| Parameter                                       | Symbol            | Min               | Тур         | Max      | Unit     | Conditions               |

|-------------------------------------------------|-------------------|-------------------|-------------|----------|----------|--------------------------|

| RD ↑ → data float time                          | t <sub>FRD</sub>  |                   |             |          |          |                          |

| 77C25/77P25                                     |                   | 10                |             | 65       | ns       |                          |

| 77C25-10                                        |                   | 10                | <del></del> | 50       | ns       | _                        |

| CLK f → DRQ delay time                          | <sup>t</sup> DCRQ |                   |             | 00       |          |                          |

| 77C25/77P25<br>77C25-10                         |                   |                   |             | 80<br>65 | ns<br>ns |                          |

|                                                 |                   |                   |             |          |          | _                        |

| DACK ↓ → DRQ delay time<br>77C25/77P25          | t <sub>DARQ</sub> |                   |             | 110      | ns       |                          |

| 77C25-10                                        |                   |                   |             | 90       | ns       |                          |

| CLK↑→P <sub>0</sub> , P <sub>1</sub> delay time | t <sub>DCP</sub>  |                   |             |          |          | _                        |

| 77C25/77P25                                     | vocr              |                   |             | 100      | ns       |                          |

| 77C25-10                                        |                   |                   |             | 80       | ns       |                          |

| Interrupt Reset Timing                          |                   |                   |             |          |          |                          |

| RST setup time for CLK                          | tsrsc             |                   |             |          |          | Note 1                   |

| 77C25/77P25                                     |                   | 50                |             |          | ns       |                          |

| 77C25-10                                        |                   | 40                |             |          | ns       |                          |

| RST hold time for CLK                           | tHCRS             | 50                |             |          |          | Note 1                   |

| 77C25/77P25<br>77C25-10                         |                   | 50<br>40          |             |          | ns<br>ns |                          |

|                                                 |                   |                   |             |          | -        | 0                        |

| RST pulse width                                 | <sup>t</sup> RST  | 2t <sub>CYC</sub> |             |          | ns       | System reset             |

|                                                 |                   | 3t <sub>CYC</sub> |             |          | ns       | Enter power saving state |

| INT setup time for CLK<br>77C25/77P25           | tsinc             | 50                |             |          | ns       | Note 1                   |

| 77C25/77F25                                     |                   | 40                |             |          | ns       |                          |

| INT hold time for CLK                           | tHCIN             |                   |             |          |          | Note 1                   |

| 77C25/77P25                                     | 110111            | 50                |             |          | ns       |                          |

| 77C25-10                                        |                   | 40                |             |          | ns       |                          |

| INT pulse width                                 | t <sub>INT</sub>  | 3t CYC            |             |          | ns       | _                        |

| INT recovery time                               | t <sub>RINT</sub> | 2t CYC            |             |          | ns       |                          |

| Interrupt Reset Switching                       |                   |                   |             |          |          |                          |

| CLK↑ → reset state delay time                   | tDCRS             |                   |             |          |          |                          |

| 77C25/77P25                                     |                   |                   |             | 100      | ns       |                          |

| 77C25-10                                        |                   |                   |             | 80       | ns       |                          |

| Serial Interface Timing                         |                   |                   |             |          |          |                          |

| SIEN, SI setup time for SCK                     | tss is            |                   |             |          |          |                          |

| 77C25/77P25<br>77C25-10                         |                   | 50<br>40          |             |          | ns<br>ns |                          |

|                                                 |                   |                   |             |          |          | _                        |

| SIEN, SI hold time for SCK<br>77C25/77P25       | <sup>t</sup> HSSI | 30                |             |          | ns       |                          |

| 77C25,777 25                                    |                   | 20                |             |          | ns       |                          |

| SOEN setup time for SCK                         | tsses             |                   |             |          |          | <del></del>              |

| 77C25/77P25                                     | -03L3             | 50                |             |          | ns       |                          |

| 77C25-10                                        |                   | 40                |             |          | ns       |                          |

| SOEN hold time for SCK                          | t <sub>HSSE</sub> |                   |             |          |          |                          |

| 77C25/77P25                                     |                   | 30                |             |          | ns       |                          |

| 77C25-10 <b>•</b>                               |                   | 25                |             |          | ns       |                          |

| CLK setup time for SCK                          | tscs              |                   |             |          |          | Note 1                   |

| 77C25/77P25<br>77C25-10                         |                   | 50<br>40          |             |          | ns<br>ns |                          |

| 11020-10                                        |                   | 40                |             |          | 110      | ··                       |

| AC Characteristics (cor | nt | CO | ics ( | ist | acter | )ha | C | AC |

|-------------------------|----|----|-------|-----|-------|-----|---|----|

|-------------------------|----|----|-------|-----|-------|-----|---|----|

| Parameter                                          | Symbol              | Min      | Тур | Max        | Unit     | Conditions |

|----------------------------------------------------|---------------------|----------|-----|------------|----------|------------|

| CLK hold time for SCK<br>77C25/77P25<br>77C25-10   | tHSC                | 50<br>40 |     |            | ns<br>ns | Note 1     |

| SCK setup time for CLK<br>77C25/77P25<br>77C25-10  | tssc                | 50<br>40 | -   |            | ns<br>ns | Note 1     |

| SCK hold time for CLK<br>77C25/77P25<br>77C25-10   | thes                | 50<br>40 |     |            | ns<br>ns | Note 1     |

| Serial Interface Switching                         |                     |          |     |            |          |            |

| SCK † → SORQ delay time<br>77C25/77P25<br>77C25-10 | t <sub>DSSQ</sub>   | 30<br>20 |     | 150<br>120 | ns<br>ns |            |

| SCK ↓ → SO delay time<br>77C25/77P25<br>77C25-10   | t <sub>DSLS</sub> O |          |     | 60<br>50   | ns<br>ns | _          |

| SCK ↓ → SO hold time<br>77C25/77P25<br>77C25-10    | <sup>t</sup> HSLSO  | 0        |     |            | ns<br>ns | _          |

| SCK ↓ → SO float time<br>77C25/77P25<br>77C25-10   | t <sub>FSSO</sub>   |          |     | 60<br>50   | ns<br>ns | _          |

#### Notes:

(1) Setup and hold requirement for asynchronous signal only guarantees recognition at next CLK.

# **PROM Program Timing**

$T_A = 25 \pm 5^{\circ}C; V_{IHR} = 12.0 \pm 0.5 V$

| Parameter                         | Symbol             | Min | Тур      | Max | Unit | Conditions                               |  |

|-----------------------------------|--------------------|-----|----------|-----|------|------------------------------------------|--|

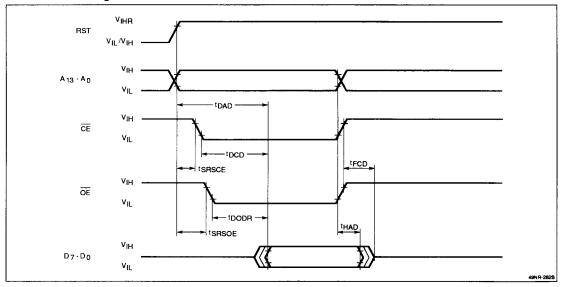

| Data Read                         |                    |     |          |     |      |                                          |  |

| CE setup time for RST             | t <sub>SRSCE</sub> | 2   |          |     | μs   | $V_{DD} = 5.0 \pm 0.5 V$                 |  |

| OE setup time for RST             | <sup>t</sup> SRSOE | 2   |          |     | μs   | $V_{PP} = V_{DD}$                        |  |

| Data Read Switching               |                    |     |          |     |      |                                          |  |

| Address to output delay           | t <sub>DAD</sub>   |     |          | 200 | ns   | $V_{DD} = 5.0 \pm 0.5 \text{ V}$         |  |

| CE to output delay                | † <sub>DCD</sub>   |     |          | 200 | ns   | — V <sub>PP</sub> = V <sub>DD</sub><br>— |  |

| OE to output delay                | †DODR              |     |          | 75  | ns   |                                          |  |

| OE high to output float           | t <sub>FCD</sub>   | 0   |          | 60  | ns   |                                          |  |

| Address to output hold            | t <sub>HAD</sub>   | 0   |          |     | ns   |                                          |  |

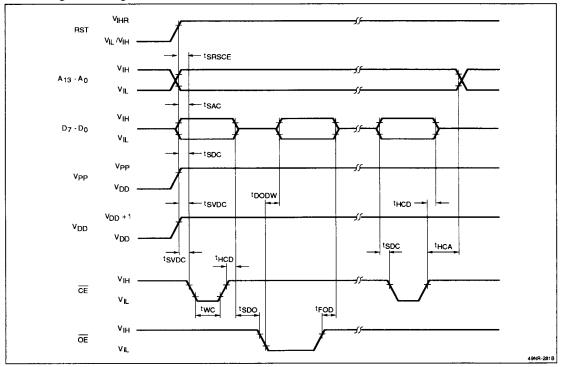

| Data Write                        |                    |     | <u> </u> |     |      |                                          |  |

| CE setup time for RST             | t <sub>SRSCE</sub> | 2   |          |     | μs   | $V_{DD} = 6.0 \pm 0.25 \text{ V}$        |  |

| CE setup time for address         | tsac               | 2   |          |     | μs   | $V_{PP} = 12.5 \pm 0.3 \text{ V}$        |  |

| CE setup time for data            | tspc               | 2   |          |     | μs   | _                                        |  |

| CE setup time for V <sub>PP</sub> | tsvpc_             | 2   |          |     | μs   |                                          |  |

| CE setup time for V <sub>DD</sub> | <sup>t</sup> svDC  | 2   |          |     | μs   |                                          |  |

| OE setup time for data            | tspo               | 2   |          |     | με   |                                          |  |

# **PROM Program Timing (cont)**

| Parameter                   | Symbol            | Min  | Тур | Max   | Unit | Conditions                        |  |

|-----------------------------|-------------------|------|-----|-------|------|-----------------------------------|--|

| Address hold time           | tHCA              | 2    |     |       | μs   |                                   |  |

| Data hold time              | tHCD              | 2    |     |       | μs   | A-4                               |  |

| Initial program pulse width | twco              | 0.95 | 1.0 | 1.05  | ms   | <del>_</del>                      |  |

| Overprogram pulse width     | twc1*             | 2.85 |     | 78.75 | ms   |                                   |  |

| Data Write Switching        |                   |      |     |       |      |                                   |  |

| OE to output float time     | t <sub>FOD</sub>  | 0    |     | 130   | ns   | $V_{DD} = 6.0 \pm 0.25 \text{ V}$ |  |

| OE to output delay          | t <sub>DODW</sub> |      |     | 150   | ns   | $V_{PP} = 12.5 \pm 0.3 \text{ V}$ |  |

twc1 = 3ntwc0 assuming initial program pulse is applied n times.

# **Timing Waveforms**

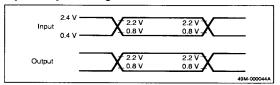

# Input/Output Voltage Reference Levels

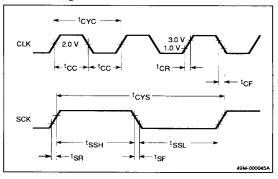

# **Clock Timing**

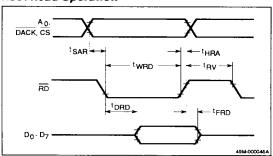

# **Host Read Operation**

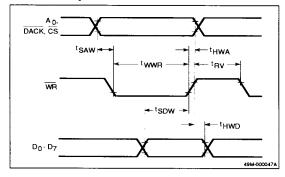

# Host Write Operation

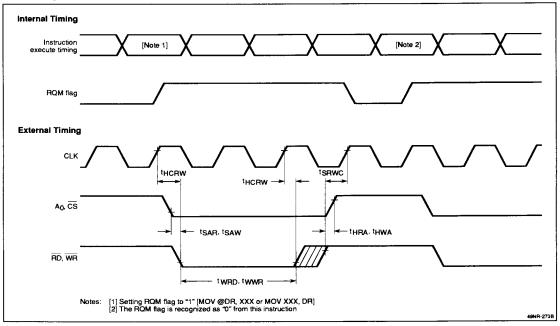

# Normal Operation, 8-Bit Mode

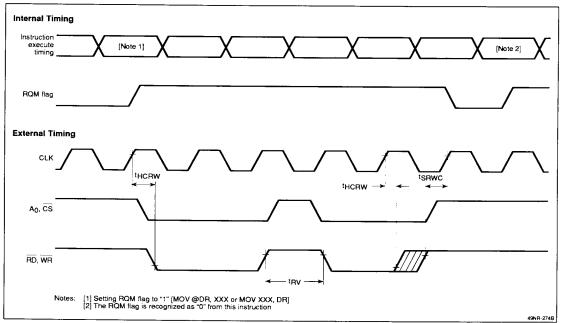

# Normal Operation, 16-Bit Mode

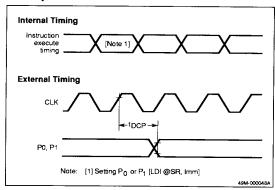

# **Port Operation**

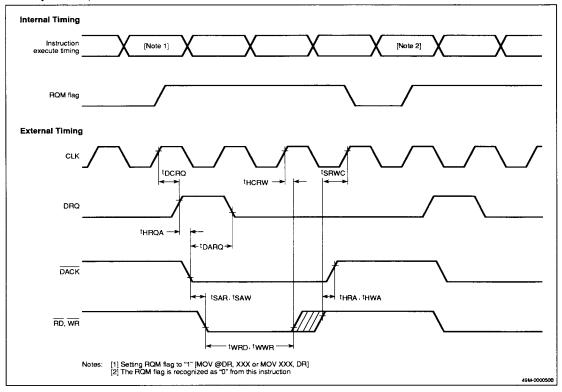

# DMA Operation, 8-Bit Mode

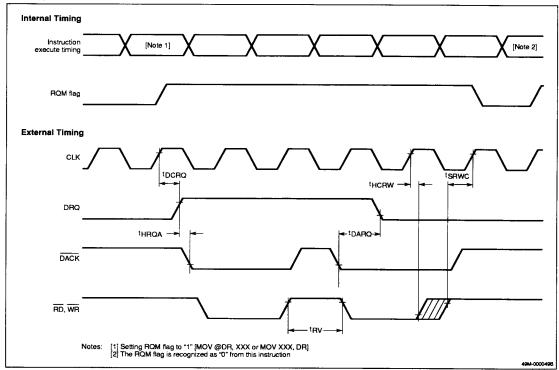

# DMA Operation, 16-Bit Mode

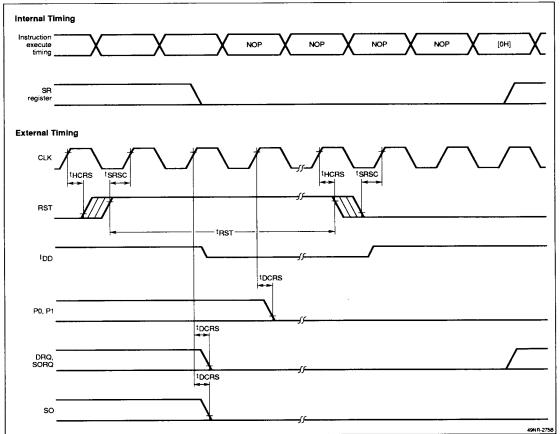

## Interrupt Operation

# **PROM Read Timing**

## **PROM Program Timing**

Figure 7. Serial Input Operation

## SERIAL TIMING

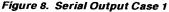

# Serial Output Case 1: SOEN Asserted in Response to SORQ

Figure 8 shows timing for serial output when  $\overline{\text{SOEN}}$  is asserted in response to SORQ. If  $\overline{\text{SOEN}}$  is held inactive until after SORQ is asserted, and then  $\overline{\text{SOEN}}$  is asserted at least t<sub>SSES</sub> before the falling edge of SCK, SO will become valid t<sub>DSLSO</sub> after the falling edge of SCK for use by an external device at the subsequent rising edge of SCK.

Note that, although figure 8 shows  $\overline{\text{SOEN}}$  being asserted during a different SCK pulse than the one in which SORQ is asserted, it is permissible for these to occur during the same pulse of SCK as long as  $\overline{\text{SOEN}}$  is still asserted t<sub>SSES</sub> before the falling edge of SCK.

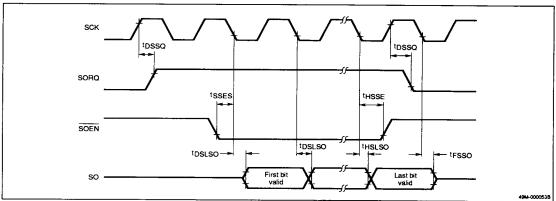

# Serial Output Case 2: SOEN Active Before SORQ Is High

Figure 9 shows output timing when  $\overline{SOEN}$  is active before SORQ is high. If  $\overline{SOEN}$  is held active before SORQ is high, data will be shifted out whenever it becomes available in the serial output register (assuming previous data is already shifted out). In this case, SORQ will rise  $t_{DSSQ}$  after a rising edge of SCK. The first SO bit occurs  $t_{DSLSO}$  after the next falling edge of SCK for use by an external device at the subsequent rising edge of SCK.

Subsequent bits will be shifted out  $t_{\rm DSLSO}$  after subsequent falling edges of SCK for use at subsequent rising edges of SCK. The last bit to be shifted out will also follow this pattern, and will be held valid  $t_{\rm FSSO}$  after the