# Spread Spectrum Desktop/Notebook System Frequency Generator

#### **Features**

- Maximized EMI suppression using Cypress's Spread Spectrum technology

- Reduces measured EMI by as much as 10 dB

- I<sup>2</sup>C programmable to 153 MHz (16 selectable frequencies)

- Two skew-controlled copies of CPU output

- SEL100/66# selects CPU frequency (100 or 66.8 MHz)

- Seven copies of PCi output (synchronous w/CPU output)

- · One copy of 14.31818-MHz IOAPIC output

- · One copy of 48-MHz USB output

- Selectable 24-/48-MHz output is determined by resistor straps on power-up

- One high-drive output buffer that produces a copy of the 14.318-MHz reference

- · Isolated core VDD pin for noise reduction

#### **Key Specifications**

| Supply Voltages:                                                        | $V_{DDQ3} = 3.3V \pm 5\%$<br>$V_{DDQ2} = 2.5V \pm 5\%$ |

|-------------------------------------------------------------------------|--------------------------------------------------------|

| CPU Cycle to Cycle Jitter:                                              | 200 ps                                                 |

| CPU, PCI Output Edge Rate:                                              | ≥1 V/ns                                                |

| CPU0:1 Output Skew:                                                     | 175 ps                                                 |

| PCI_F, PCI1:6 Output Skew:                                              | 500 ps                                                 |

| CPU to PCI Skew:1                                                       | to 4 ns (CPU Leads)                                    |

| REF2X/SEL48#, SCLOCK, SDATA                                             | 250-kΩ pull-up                                         |

| <b>Note:</b> Internal pull-up resistors should r setting I/O pins HIGH. | not be relied upon for                                 |

Table 1. Pin Selectable Frequency

| SEL100/66# | CPU(0:1) | PCI      |

|------------|----------|----------|

| 1          | 100 MHz  | 33.3 MHz |

| 0          | 66.8 MHz | 33.4 MHz |

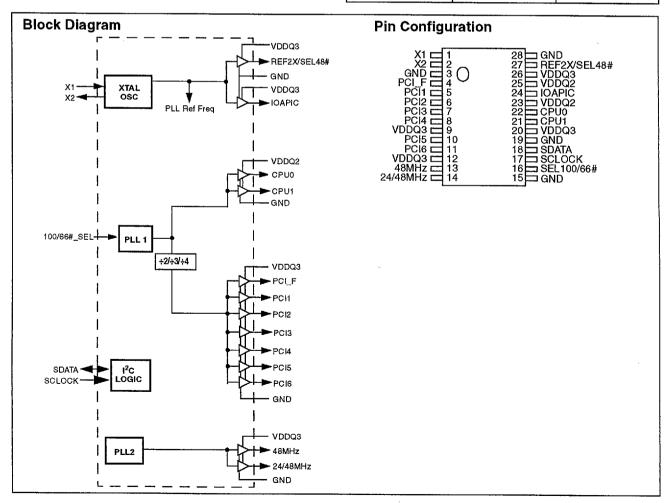

#### Pin Definitions

| Pin Name        | Pin<br>No.               | Pin<br>Type | Pin Description                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|--------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU0:1          | 22, 21                   | 0           | CPU Clock Outputs 0 through 1: These two CPU clocks run at a frequency set by SEL100/66#. Output voltage swing is set by the voltage applied to VDDQ2.                                                                                                                                                                                                                     |

| PCI1:6<br>PCI_F | 5, 6, 7, 8, 10,<br>11, 4 | 0           | PCI Clock Outputs 1 through 6 and PCI_F: These seven PCI clock outputs run synchronously to the CPU clock. Voltage swing is set by the power connection to VDDQ3.                                                                                                                                                                                                          |

| IOAPIC          | 24                       | 0           | I/O APIC Clock Output: Provides 14.318-MHz fixed frequency. The output voltage swing is set by the power connection to VDDQ2.                                                                                                                                                                                                                                              |

| 48MHz           | 13                       | 0           | 48-MHz Output: Fixed 48-MHz USB clock. Output voltage swing is controlled by voltage applied to VDDQ3.                                                                                                                                                                                                                                                                     |

| 24/48MHz        | 14                       | .0          | 24-MHz or 48-MHz Output: Frequency is set by the state of pin 27 on power-up.                                                                                                                                                                                                                                                                                              |

| REF2X/SEL48#    | 27                       | I/O         | I/O Dual-Function REF2X and SEL48# pin: Upon power-up, the state of SEL48# is latched. The initial state is set by either a 10K resistor to GND or to $V_{DD}$ . A 10K resistor to GND causes pin 14 to output 48 MHz. If the pin is strapped to $V_{DD}$ , pin 14 will output 24 MHz. After 2 ms, the pin becomes a high-drive output that produces a copy of 14.318 MHz. |

| SEL100/66#      | 16                       | ı           | Frequency Selection Input: Selects CPU clock frequency as shown in Table 1 on page 1.                                                                                                                                                                                                                                                                                      |

| SDATA           | 18                       | I/O         | $I^2C$ Data Pin: Data should be presented to this input as described in the $I^2C$ section of this data sheet. Internal 250-k $\Omega$ pull-up resistor.                                                                                                                                                                                                                   |

| SCLOCK          | 17                       | ı           | $I^2C$ Clock Pin: The $I^2C$ data clock should be presented to this input as described in the $I^2C$ section of this data sheet.                                                                                                                                                                                                                                           |

| X1              | 1                        | I           | Crystal Connection or External Reference Frequency Input: Connect to either a 14.318-MHz crystal or other reference signal.                                                                                                                                                                                                                                                |

| X2              | 2                        | ı           | Crystal Connection: An input connection for an external 14.318-MHz crystal. If using an external reference, this pin must be left unconnected.                                                                                                                                                                                                                             |

| VDDQ3           | 9, 12, 20, 26            | Р           | <b>Power Connection:</b> Power supply for core logic and PLL circuitry, PCI, 48-/24-MHz, and Reference output buffers. Connect to 3.3V supply.                                                                                                                                                                                                                             |

| VDDQ2           | 23, 25                   | Р           | <b>Power Connection:</b> Power supply for IOAPIC and CPU output buffers. Connect to 2.5V supply.                                                                                                                                                                                                                                                                           |

| GND             | 3, 15, 19, 28            | G           | <b>Ground Connections:</b> Connect all ground pins to the common system ground plane.                                                                                                                                                                                                                                                                                      |

#### **Functional Description**

#### I/O Pin Operation

Pin 27 is a dual-purpose I/O pin. Upon power-up this pin acts as a logic input, allowing the determination of assigned device functions. A short time after power-up, the logic state of the pin is latched and the pin becomes a clock output. This feature reduces device pin count by combining clock outputs with input select pins.

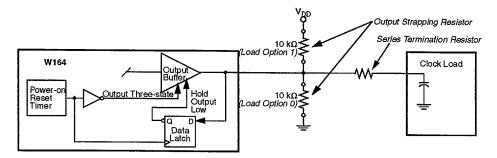

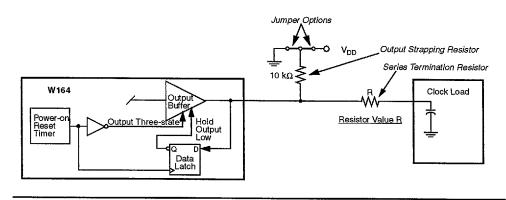

An external 10-k $\Omega$  "strapping" resistor is connected between the I/O pin and ground or V<sub>DD</sub>. Connection to ground sets a latch to "0," connection to V<sub>DD</sub> sets a latch to "1." *Figure 1* and *Figure 2* show two suggested methods for strapping resistor connections.

Upon W164 power-up, the first 2 ms of operation is used for input logic selection. During this period, the Reference clock output buffer is three-stated, allowing the output strapping resistor on the I/O pin to pull the pin and its associated capacitive clock load to either a logic HIGH or LOW state. At the end of the 2-ms period, the established logic "0" or "1" condition of the

I/O pin is then latched. Next the output buffer is enabled which converts the I/O pin into an operating clock output. The 2-ms timer is started when  $V_{DD}$  reaches 2.0V. The input bit can only be reset by turning  $V_{DD}$  off and then back on again.

It should be noted that the strapping resistor has no significant effect on clock output signal integrity. The drive impedance of clock output is  $25\Omega$  (nominal) which is minimally affected by the 10-k $\Omega$  strap to ground or  $V_{DD}.$  As with the series termination resistor, the output strapping resistor should be placed as close to the I/O pin as possible in order to keep the interconnecting trace short. The trace from the resistor to ground or  $V_{DD}$  should be kept less than two inches in length to prevent system noise coupling during input logic sampling.

When the clock output is enabled following the 2-ms input period, a 14.318-MHz output frequency is delivered on the pin, assuming that  $V_{DD}$  has stabilized. If  $V_{DD}$  has not yet reached full value, output frequency initially may be below target but will increase to target once  $V_{DD}$  voltage has stabilized. In either case, a short output clock cycle may be produced from the CPU clock outputs when the outputs are enabled.

Figure 1. Input Logic Selection Through Resistor Load Option

Figure 2. Input Logic Selection Through Jumper Option

#### Serial Data Interface

The W164 features a two-pin, serial data interface that can be used to configure internal register settings that control particular device functions. Upon power-up, the W164 initializes with default register settings. Therefore, the use of this serial data interface is optional. The serial interface is write-only (to the clock chip) and is the dedicated function of device pins SDATA and SCLOCK. In motherboard applications, SDATA and SCLOCK are typically driven by two logic outputs of the

chipset. Clock device register changes are normally made upon system initialization, if required. The interface can also be used during system operation for power management functions. *Table 2* summarizes the control functions of the serial data interface.

#### Operation

Data is written to the W164 in ten bytes of eight bits each. Bytes are written in the order shown in  $Table\ 3$ .

Table 2. Serial Data Interface Control Functions Summary

| Control Function                 | Description                                                                                                                                                                     | Common Application                                                                                                                                 |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock Output Disable             | Any individual clock output(s) can be disabled. Disabled outputs are actively held LOW.                                                                                         | Unused outputs are disabled to reduce EMI and system power. Examples are clock outputs to unused PCI slots.                                        |

| CPU Clock Frequency<br>Selection | Provides CPU/PCI frequency selections beyond the 100- and 66.6-MHz selections that are provided by the SEL100/66# pin. Frequency is changed in a smooth and controlled fashion. | For alternate microprocessors and power management options. Smooth frequency transition allows CPU frequency change under normal system operation. |

| Output Three-state               | Puts all clock outputs into a high-impedance state.                                                                                                                             | Production PCB testing.                                                                                                                            |

| Test Mode                        | All clock outputs toggle in relation to X1 input, internal PLL is bypassed. Refer to <i>Table 4</i> .                                                                           | Production PCB testing.                                                                                                                            |

| (Reserved)                       | Reserved function for future device revision or production device testing.                                                                                                      | No user application. Register bit must be written as 0.                                                                                            |

Table 3. Byte Writing Sequence

| Byte<br>Sequence | Byte Name       | Bit Sequence     | Byte Description                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|-----------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | Slave Address   | 11010010         | Commands the W164 to accept the bits in Data Bytes 3–6 for internal register configuration. Since other devices may exist on the same common serial data bus, it is necessary to have a specific slave address for each potential receiver. The slave receiver address for the W164 is 11010010. Register setting will not be made if the Slave Address is not correct (or is for an alternate slave receiver). |

| 2                | Command<br>Code | Don't Care       | Unused by the W164, therefore bit values are ignored ("don't care"). This byte must be included in the data write sequence to maintain proper byte allocation. The Command Code Byte is part of the standard serial communication protocol and may be used when writing to another addressed slave receiver on the serial data bus.                                                                             |

| 3                | Byte Count      | Don't Care       | Unused by the W164, therefore bit values are ignored ("don't care"). This byte must be included in the data write sequence to maintain proper byte allocation. The Byte Count Byte is part of the standard serial communication protocol and may be used when writing to another addressed slave receiver on the serial data bus.                                                                               |

| 4                | Data Byte 0     | Don't Care       | Refer to Cypress SDRAM drivers.                                                                                                                                                                                                                                                                                                                                                                                 |

| 5                | Data Byte 1     | 1                |                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6                | Data Byte 2     | 1                |                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7                | Data Byte 3     | Refer to Table 4 | The data bits in these bytes set internal W164 registers that control device                                                                                                                                                                                                                                                                                                                                    |

| 8                | Data Byte 4     |                  | operation. The data bits are only accepted when the Address Byte bit sequence is 11010010, as noted above. For description of bit control                                                                                                                                                                                                                                                                       |

| 9                | Data Byte 5     | 1                | functions, refer to <i>Table 4</i> , Data Byte Serial Configuration Map.                                                                                                                                                                                                                                                                                                                                        |

| 10               | Data Byte 6     |                  |                                                                                                                                                                                                                                                                                                                                                                                                                 |

### **Writing Data Bytes**

Each bit in the data bytes controls a particular device function except for the "reserved" bits, which must be written as a logic 0. Bits are written MSB (most significant bit) first, which is bit 7. *Table 4* gives the bit formats for registers located in Data Bytes 3–6.

Table 5 details additional frequency selections that are available through the serial data interface.

Table 6 details the select functions for Byte 3, bits 1 and 0.

Table 4. Data Bytes 3-6 Serial Configuration Map

|          | Affe                    | cted Pin                              |                                        | Bit C                                                           | ontrol                                               |      |  |  |

|----------|-------------------------|---------------------------------------|----------------------------------------|-----------------------------------------------------------------|------------------------------------------------------|------|--|--|

| Bit(s)   | Bit(s) Pin No. Pin Name |                                       | Control Function                       | 0                                                               | Default                                              |      |  |  |

| Data Byt | e 3                     |                                       | I                                      |                                                                 |                                                      |      |  |  |

| 7        |                         |                                       | SEL_3                                  |                                                                 | T                                                    | 0    |  |  |

| 6        |                         |                                       | SEL_2                                  | Refer to                                                        | Table 5                                              | 0    |  |  |

| 5        |                         |                                       | SEL_1                                  | Refer to                                                        | Table 5                                              | 0    |  |  |

| 4        |                         |                                       | SEL_0                                  | Refer to                                                        | Table 5                                              | 0    |  |  |

| 3        |                         |                                       | Frequency Table<br>Selection           | Frequency Controlled<br>by external SEL100/<br>66# pin Table 1  | Frequency Controlled<br>by BYT3 SEL_(3:0)<br>Table 5 | 0    |  |  |

| 2        |                         |                                       | (Reserved)                             | -                                                               |                                                      | 0    |  |  |

| 1–0      |                         | <del></del>                           | 0 0 Norma<br>0 1 Test Mo<br>1 0 Spread | 0 0 Normal Operation<br>0 1 Test Mode<br>1 0 Spread Spectrum on |                                                      |      |  |  |

| Data Byt | e 4                     | · · · · · · · · · · · · · · · · · · · |                                        |                                                                 |                                                      |      |  |  |

| 7        |                         |                                       | (Reserved)                             | -                                                               |                                                      | 0    |  |  |

| 6        | 14                      | 24/48MHz                              | Clock output Disable                   | Low                                                             | Active                                               | 1    |  |  |

| 5        |                         |                                       | (Reserved)                             |                                                                 |                                                      | 0    |  |  |

| 4        |                         |                                       | (Reserved)                             |                                                                 |                                                      | 0    |  |  |

| 3        |                         |                                       | (Reserved)                             |                                                                 |                                                      | 0    |  |  |

| 2        | 21                      | CPU1                                  | Clock Output Disable                   | Low                                                             | Active                                               | 1    |  |  |

| 1        |                         |                                       | (Reserved)                             |                                                                 |                                                      | 0    |  |  |

| 0        | 22                      | CPU0                                  | Clock Output Disable                   | Low                                                             | Active                                               | 1    |  |  |

| Data Byt | e 5                     |                                       |                                        | L                                                               | <u> </u>                                             |      |  |  |

| 7        | 4                       | PCI_F                                 | Clock Output Disable                   | Low                                                             | Active                                               | 1    |  |  |

| 6        | 11                      | PCI6                                  | Clock Output Disable                   | Low                                                             | Active                                               | 1    |  |  |

| 5        | 10                      | PCI5                                  | Clock Output Disable                   | Low                                                             | Active                                               | 1    |  |  |

| 4        | -                       |                                       | (Reserved)                             |                                                                 |                                                      | 0    |  |  |

| 3        | 8                       | PCI4                                  | Clock Output Disable                   | Low                                                             | Active                                               | 1    |  |  |

| 2        | 7                       | PCI3                                  | Clock Output Disable                   | Low                                                             | Active                                               | 1    |  |  |

| 1        | 6                       | PCI2                                  | Clock Output Disable                   | Low                                                             | Active                                               | 1    |  |  |

| 0        | 5                       | PCI1                                  | Clock Output Disable                   | Low                                                             | Active                                               | 1    |  |  |

| Data Byt | e 6                     |                                       |                                        |                                                                 |                                                      |      |  |  |

| 7        |                         |                                       | (Reserved)                             | -                                                               |                                                      | 0    |  |  |

| 6        |                         |                                       | (Reserved)                             | _                                                               | a                                                    | 0    |  |  |

| 5        | 24                      | IOAPIC                                | Clock Output Disable                   | Low                                                             | Active                                               | 1    |  |  |

| 4        |                         |                                       | (Reserved)                             |                                                                 |                                                      | 0    |  |  |

| 3        |                         |                                       | (Reserved)                             | ***                                                             |                                                      | 0    |  |  |

| 2        |                         |                                       | (Reserved)                             |                                                                 |                                                      | 0    |  |  |

| 1        | 27                      | REF2X                                 | Clock Output Disable                   | Low                                                             | Active                                               | 1[7] |  |  |

| 0        | 27                      | REF2X                                 | Clock Output Disable                   | Low                                                             | Active                                               | 1[1] |  |  |

<sup>1.</sup> Both Bits 0 and 1 of Byte 6 in Table 4 must be programmed as the same value.

Table 5. Additional Frequency Selections through Serial Data Interface Data Bytes

|                | Input Conditions |                | Output Fr      | equency                    | If Spread is On     |                   |  |

|----------------|------------------|----------------|----------------|----------------------------|---------------------|-------------------|--|

|                | Data Byte        | 3, Bit 3 = 1   |                |                            |                     |                   |  |

| Bit 7<br>SEL_3 | Bit 6<br>SEL_2   | Bit 5<br>SEL_1 | Bit 4<br>SEL_0 | CPU, SDRAM<br>Clocks (MHz) | PCI Clocks<br>(MHz) | Spread Percentage |  |

| 0              | 0                | 0              | 0              | 68.5                       | 34.25               | ±0.5% Center      |  |

| 0              | 0                | 0              | 1              | 75                         | 37.5                | ±0.5% Center      |  |

| 0              | 0                | 1              | 0              | 83.3                       | 41.6                | ±0.5% Center      |  |

| 0              | 0                | 1              | 1              | 66.8                       | 33.4                | ±0.5% Center      |  |

| 0              | 1                | 0              | 0              | 103                        | 34.25               | ±0.5% Center      |  |

| 0              | 1                | 0              | 1              | 112                        | 37.3                | ±0.5% Center      |  |

| 0              | 1                | . 1            | 0              | 133.3                      | 33.3                | ±0.5% Center      |  |

| 0              | . 1              | 1              | 1              | 100                        | 33,3                | ±0.5% Center      |  |

| 1              | 0                | 0              | 0              | 117                        | 39.0                | ±0.5% Center      |  |

| 1              | 0                | 0              | 1              | 117                        | 29.25               | ±0,5% Center      |  |

| 1              | 0                | 1              | 0              | 124                        | 31.0                | ±0.5% Center      |  |

| 1              | 0                | 1              | 1              | 129                        | 32.25               | ±0.5% Center      |  |

| 1              | 1                | 0              | 0              | 138                        | 34.5                | ±0.5% Center      |  |

| 1              | 1                | 0              | 1              | 143                        | 35.75               | ±0.5% Center      |  |

| 1              | 1                | 1              | 0              | 148                        | 37.0                | ±0.5% Center      |  |

| 1              | 1                | 1              | 1              | 153                        | 38.25               | ±0.5% Center      |  |

Table 6. Select Function for Data Byte 3, Bits 0:1

|                  | Input Co    | onditions | Output Conditions |                |            |        |        |  |  |

|------------------|-------------|-----------|-------------------|----------------|------------|--------|--------|--|--|

|                  | Data Byte 3 |           |                   |                | REF2X,     |        |        |  |  |

| <b>Function</b>  | Bit 1       | Bit 0     | CPU0:1            | PCI_F, PCI1:6  |            | 48MHZ  | 24MHZ  |  |  |

| Normal Operation | 0           | 0         | Note 2            | Note 2         | 14.318 MHz | 48 MHz | 24 MHz |  |  |

| Test Mode        | 0           | 1         | X1/2              | CPU/2, 3, or 4 | X1         | X1/2   | X1/4   |  |  |

| Spread Spectrum  | 1           | 0         | ±0.5%             | ±0.5%          | 14.318 MHz | 48 MHz | 24 MHz |  |  |

| Three-state      | 1           | 1         | Hi-Z              | Hi-Z           | Hi-Z       | Hi-Z   | Hi-Z   |  |  |

Note:

<sup>2.</sup> CPU and PCI frequency selections are listed in Table 1 and Table 5.

## **Absolute Maximum Ratings**

Stresses greater than those listed in this table may cause permanent damage to the device. These represent a stress rating only. Operation of the device at these or any other conditions

above those specified in the operating sections of this specification is not implied. Maximum conditions for extended periods may affect reliability.

| Parameter           | Description                            | Rating       | Unit |

|---------------------|----------------------------------------|--------------|------|

| $V_{DD}$ , $V_{IN}$ | Voltage on any pin with respect to GND | -0.5 to +7.0 | V    |

| T <sub>STG</sub>    | Storage Temperature                    | -65 to +150  | °C   |

| T <sub>A</sub>      | Operating Temperature                  | 0 to +70     | °C   |

| T <sub>B</sub>      | Ambient Temperature under Bias         | -55 to +125  | °C   |

| ESD <sub>PROT</sub> | Input ESD Protection                   | 2 (min.)     | kV   |

## DC Electrical Characteristics: $T_A = 0$ °C to +70°C, $V_{DDO3} = 3.3V \pm 5\%$ , $V_{DDO2} = 2.5V \pm 5\%$

| Parameter         | Descrip                           | tion          | Test Condition                                   | Min.         | Тур. | Max.                     | Unit     |

|-------------------|-----------------------------------|---------------|--------------------------------------------------|--------------|------|--------------------------|----------|

| Supply Curr       | ent                               |               |                                                  |              |      | 1                        | <u> </u> |

| I <sub>DDQ3</sub> | Combined 3.3V Suppl               | y Current     | CPU0:1 =100 MHz<br>Outputs Loaded <sup>[3]</sup> |              | 85   |                          | mA       |

| I <sub>DDQ3</sub> | Combined 2.5V Suppl               | y Current     | CPU0:1 =100 MHz<br>Outputs Loaded <sup>[3]</sup> |              | 30   |                          | mA       |

| Logic Inputs      | 8                                 |               |                                                  |              |      |                          |          |

| V <sub>IL</sub>   | Input Low Voltage                 |               |                                                  | GND -<br>0.3 | :    | 0.8                      | ٧        |

| V <sub>IH</sub>   | Input High Voltage                |               |                                                  | 2.0          |      | V <sub>DD</sub> +<br>0.3 | V        |

| ال                | Input Low Current <sup>[4]</sup>  |               |                                                  |              |      | -25                      | μA       |

| I <sub>IH</sub>   | Input High Current <sup>[4]</sup> |               |                                                  |              |      | 10                       | μA       |

| l <sub>և</sub>    | Input Low Current (SE             | L100/66#)     |                                                  |              |      | <b>–</b> 5               | μA       |

| l <sub>IH</sub>   | Input High Current (SI            | EL100/66#)    |                                                  |              |      | 5                        | μA       |

| Clock Outpu       | uts                               |               |                                                  |              |      |                          |          |

| $V_{OL}$          | Output Low Voltage                |               | I <sub>OL</sub> = 1 mA                           |              |      | 50                       | mV       |

| V <sub>OH</sub>   | Output High Voltage               |               | I <sub>OH</sub> = -1 mA                          | 3.1          |      |                          | ٧        |

| V <sub>OH</sub>   | Output High Voltage               | CPU0:1/IOAPIC | I <sub>OH</sub> = -1 mA                          | 2.2          |      |                          | ٧        |

| loL               | Output Low Current                | CPU0:1        | V <sub>OL</sub> = 1.25V                          | 50           | 70   | 100                      | mA       |

|                   |                                   | PCI_F, PCI1:6 | V <sub>OL</sub> = 1.5V                           | 60           | 80   | 120                      | mA       |

|                   |                                   | IOAPIC        | V <sub>OL</sub> = 1.25V                          | 40           | 85   | 140                      | mA       |

|                   |                                   | REF2X         | V <sub>OL</sub> = 1.5V                           | 100          | 130  | 152                      | mA       |

|                   |                                   | 48MHz, 24MHz  | V <sub>OL</sub> = 1.5V                           | 40           | 50   | 76                       | mA       |

| ЮН                | Output High Current               | CPU0:1        | V <sub>OH</sub> = 1.25V                          | 50           | 70   | 100                      | mA       |

|                   |                                   | PCI_F, PCI1:6 | V <sub>OH</sub> = 1.5V                           | 60           | 70   | 120                      | mA       |

|                   |                                   | IOAPIC        | V <sub>OH</sub> = 1.25V                          | 40           | 87   | 155                      | mA       |

|                   |                                   | REF2X         | V <sub>OH</sub> = 1.5V                           | 100          | 130  | 150                      | mA       |

|                   |                                   | 48MHz, 24MHz  | V <sub>OH</sub> = 1.5V                           | 40           | 50   | 94                       | mA       |

#### Notes:

All clock outputs loaded with maximum lump capacitance test load specified in the AC Electrical Characteristics section. W164 logic inputs have internal pull-up resistors, except SEL100/66# (pull-ups not full CMOS level).

## DC Electrical Characteristics: $T_A = 0$ °C to +70°C, $V_{DDQ3} = 3.3V \pm 5\%$ , $V_{DDQ2} = 2.5V \pm 5\%$ (continued)

| Parameter          | Description                                                  | Test Condition           | Min. | Тур. | Max. | Unit |

|--------------------|--------------------------------------------------------------|--------------------------|------|------|------|------|

| Crystal Osc        | illator                                                      |                          | -    | •    | •    |      |

| V <sub>TH</sub>    | X1 Input Threshold Voltage <sup>[5]</sup>                    | V <sub>DDQ3</sub> = 3.3V |      | 1.65 |      | V    |

| C <sub>LOAD</sub>  | Load Capacitance, as seen by External Crystal <sup>[6]</sup> |                          |      | 13   |      | pF   |

| C <sub>IN,X1</sub> | X1 Input Capacitance <sup>[7]</sup>                          | Pin X2 unconnected       |      | 26   |      | pF   |

| Pin Capacit        | ance/Inductance                                              |                          |      | •    |      |      |

| C <sub>IN</sub>    | Input Pin Capacitance                                        | Except X1 and X2         |      |      |      | pF   |

| C <sub>OUT</sub>   | Output Pin Capacitance                                       |                          |      |      |      | pF   |

| L <sub>IN</sub>    | Input Pin Inductance                                         |                          |      |      | 7    | nH   |

#### **AC Electrical Characteristics**

#### $T_A = 0$ °C to +70°C, $V_{DDQ3} = 3.3V \pm 5\%$ , $V_{DDQ2} = 2.5V \pm 5\%$ , $f_{XTL} = 14.31818$ MHz

AC clock parameters are tested and guaranteed over stated operating conditions using the stated lump capacitive load at the clock output; Spread Spectrum clocking is disabled.

#### CPU Clock Outputs, CPU0:1 (Lump Capacitance Test Load = 20 pF)

|                 |                                                            |                                                                                                                     | CPU  | = 66.8 | MHz  | CPU = 100 MHz |      |      |      |

|-----------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------|--------|------|---------------|------|------|------|

| Parameter       | Description                                                | Test Condition/Comments                                                                                             | Min. | Тур.   | Max. | Min.          | Тур. | Max. | Unit |

| tp              | Period                                                     | Measured on rising edge at 1.25V                                                                                    | 15   |        | 15.5 | 10            |      | 10.5 | ns   |

| t <sub>H</sub>  | High Time                                                  | Duration of clock cycle above 2.0V                                                                                  | 5.2  |        |      | 3.0           |      |      | ns   |

| tլ              | Low Time                                                   | Duration of clock cycle below 0.4V                                                                                  | 5.0  |        |      | 2.8           |      |      | ns   |

| t <sub>R</sub>  | Output Rise Edge Rate                                      | Measured from 0.4V to 2.0V                                                                                          | 1    |        | 4    | 1             |      | 4    | V/ns |

| t <sub>F</sub>  | Output Fall Edge Rate                                      | Measured from 2.0V to 0.4V                                                                                          | 1    |        | 4    | 1             |      | 4    | V/ns |

| t <sub>D</sub>  | Duty Cycle                                                 | Measured on rising and falling edge at 1.25V                                                                        | 45   |        | 55   | 45            |      | 55   | %    |

| tic             | Jitter, Cycle-to-Cycle                                     | Measured on rising edge at 1.25V. Max-<br>imum difference of cycle time between<br>two adjacent cycles.             |      |        | 200  |               | -    | 250  | ps   |

| t <sub>SK</sub> | Output Skew                                                | Measured on rising edge at 1.25V                                                                                    |      |        | 175  |               |      | 175  | ps   |

| f <sub>ST</sub> | Frequency Stabiliza-<br>tion from Power-up<br>(cold start) | Assumes full supply voltage reached within 1 ms from power-up. Short cycles exist prior to frequency stabilization. |      |        | 3    |               |      | 3    | ms   |

| Z <sub>o</sub>  | AC Output Impedance                                        | Average value during switching transition. Used for determining series termination value.                           |      | 20     |      |               | 20   |      | Ω    |

5. X1 input threshold voltage (typical) is V<sub>DD</sub>/2.

The W164 contains an internal crystal load capacitor between pin X1 and ground and another between pin X2 and ground. Total load placed on crystal is 14 pF; this includes typical stray capacitance of short PCB traces to crystal.

X1 input capacitance is applicable when driving X1 with an external clock source (X2 is left unconnected).

## PCI Clock Outputs, PCI1:6 and PCI\_F (Lump Capacitance Test Load = 30 pF

| Parameter       | Description                                        |                                                                                                                     |      | CPU = 66.8/100 MHz |      |      |

|-----------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------|--------------------|------|------|

|                 |                                                    | Test Condition/Comments                                                                                             | Min. | Тур.               | Max. | Unit |

| t <sub>P</sub>  | Period                                             | Measured on rising edge at 1.5V                                                                                     | 30   |                    |      | ns   |

| t <sub>H</sub>  | High Time                                          | Duration of clock cycle above 2.4V                                                                                  | 12   |                    |      | ns   |

| tլ              | Low Time                                           | Duration of clock cycle below 0.4V                                                                                  | 12   |                    |      | ns   |

| t <sub>R</sub>  | Output Rise Edge Rate                              | Measured from 0.4V to 2.4V                                                                                          | 1    | <del></del>        | 4    | V/ns |

| t <sub>F</sub>  | Output Fall Edge Rate                              | Measured from 2.4V to 0.4V                                                                                          | 1    |                    | 4    | V/ns |

| t <sub>D</sub>  | Duty Cycle                                         | Measured on rising and falling edge at 1.5V                                                                         | 45   |                    | 55   | %    |

| tuc             | Jitter, Cycle-to-Cycle                             | Measured on rising edge at 1.5V. Maximum difference of cycle time between two adjacent cycles.                      |      | ,                  | 250  | ps   |

| t <sub>SK</sub> | Output Skew                                        | Measured on rising edge at 1.5V                                                                                     |      |                    | 500  | ps   |

| t <sub>o</sub>  | CPU to PCI Clock Skew                              | Covers all CPU/PCI outputs. Measured on rising edge at 1.5V. CPU leads PCI output.                                  | 1    |                    | 4    | ns   |

| f <sub>ST</sub> | Frequency Stabilization from Power-up (cold start) | Assumes full supply voltage reached within 1 ms from power-up. Short cycles exist prior to frequency stabilization. |      |                    | 3    | ms   |

| Z <sub>o</sub>  | AC Output Impedance                                | Average value during switching transition. Used for determining series termination value.                           |      | 20                 |      | Ω    |

## IOAPIC Clock Output (Lump Capacitance Test Load = 20 pF)

|                 |                                                    |                                                                                                                     | CPU:     |             |      |      |  |

|-----------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------|-------------|------|------|--|

| Parameter       | Description                                        | Test Condition/Comments                                                                                             | Min.     | Тур.        | Max. | Unit |  |

| f               | Frequency, Actual                                  | Frequency generated by crystal oscillator                                                                           | 14.31818 |             |      | MHz  |  |

| t <sub>R</sub>  | Output Rise Edge Rate                              | Measured from 0.4V to 2.0V                                                                                          | 1 4      |             |      | V/ns |  |

| t <sub>F</sub>  | Output Fall Edge Rate                              | Measured from 2.0V to 0.4V                                                                                          |          | 4           | V/ns |      |  |

| t <sub>D</sub>  | Duty Cycle                                         | Measured on rising and falling edge at 1.25V                                                                        | 45       | <del></del> | 55   | %    |  |

| f <sub>ST</sub> | Frequency Stabilization from Power-up (cold start) | Assumes full supply voltage reached within 1 ms from power-up. Short cycles exist prior to frequency stabilization. |          |             | 1.5  | ms   |  |

| Z <sub>o</sub>  | AC Output Impedance                                | Average value during switching transition. Used for determining series termination value.                           |          | 15          |      | Ω    |  |

## REF2X Clock Output (Lump Capacitance Test Load = 20 pF)

| Parameter       |                                                    |                                                                                                                     | CPU    |      |      |      |

|-----------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------|------|------|------|

|                 | Description                                        | Test Condition/Comments                                                                                             | Min.   | Тур. | Max. | Unit |

| f               | Frequency, Actual                                  | Frequency generated by crystal oscillator                                                                           | 14.318 |      |      | MHz  |

| t <sub>R</sub>  | Output Rise Edge Rate                              | Measured from 0.4V to 2.4V                                                                                          | 0.5    |      | 2    | V/ns |

| t <sub>F</sub>  | Output Fall Edge Rate                              | Measured from 2.4V to 0.4V                                                                                          |        |      | 2    | V/ns |

| t <sub>D</sub>  | Duty Cycle                                         | Measured on rising and falling edge at 1.5V                                                                         | 45     |      | 55   | %    |

| f <sub>ST</sub> | Frequency Stabilization from Power-up (cold start) | Assumes full supply voltage reached within 1 ms from power-up. Short cycles exist prior to frequency stabilization. |        |      | 3    | ms   |

| Z <sub>o</sub>  | AC Output Impedance                                | Average value during switching transition. Used for determining series termination value.                           |        | 15   |      | Ω    |

### 48-MHz and 24-MHz Clock Output (Lump Capacitance Test Load = 20 pF)

| Parameter       |                                                    |                                                                                                                     | С                | -iz  |      |      |

|-----------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------|------|------|------|

|                 | Description                                        | Test Condition/Comments                                                                                             | Min.             | Тур. | Max. | Unit |

| f               | Frequency, Actual                                  | Determined by PLL divider ratio (see m/n below)                                                                     | 48.008<br>24.004 |      |      | MHz  |

| f <sub>D</sub>  | Deviation from 48 MHz                              | (48.008 – 48)/48                                                                                                    | +167             |      |      | ppm  |

| m/n             | PLL Ratio                                          | (14.31818 MHz x 57/17 = 48.008 MHz)                                                                                 | 57/17, 57/34     |      |      |      |

| t <sub>R</sub>  | Output Rise Edge Rate                              | Measured from 0.4V to 2.4V                                                                                          | 0.5              |      | 2    | V/ns |

| t <sub>F</sub>  | Output Fall Edge Rate                              | Measured from 2.4V to 0.4V                                                                                          | 0.5              |      | 2    | V/ns |

| t <sub>D</sub>  | Duty Cycle                                         | Measured on rising and falling edge at 1.5V                                                                         | 45               |      | 55   | %    |

| f <sub>ST</sub> | Frequency Stabilization from Power-up (cold start) | Assumes full supply voltage reached within 1 ms from power-up. Short cycles exist prior to frequency stabilization. | 3                |      |      | ms   |

| Z <sub>o</sub>  | AC Output Impedance                                | Average value during switching transition. Used for determining series termination value.                           |                  | 25   |      | Ω    |

## **Ordering Information**

| Ordering Code | Package<br>Name | Package Type           |

|---------------|-----------------|------------------------|

| W164          | G               | 28-pin SOIC (300 mils) |

Document #: 38-00841

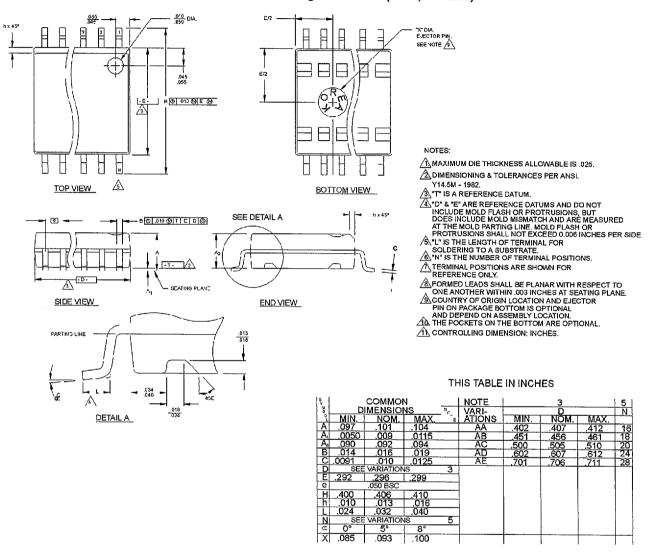

#### **Package Diagram**

#### 28-Pin Small Outline Integrated Circuit (SOIC, 300 mils)

#### THIS TABLE IN MILLIMETERS

| S              | COMMON           |          |       | NOTE |        | 5     |       |       |          |

|----------------|------------------|----------|-------|------|--------|-------|-------|-------|----------|

| y B            | DIMENSIONS       |          |       | "C_  | VARI-  | D     |       |       | N        |

|                | MIN.             | NOM.     | MAX.  | F    | ATIONS | MIN.  | NŌM.  | MAX.  | 1 . [    |

| Α              | 2.46             | 2.56     | 2.64  |      | AA     | 10.21 | 10.34 | 10.46 | 16       |

| A <sub>1</sub> | 0.127            | 0.22     | 0.29  |      | AB     | 11.46 | 11.58 | 11.71 | 16<br>18 |

| A <sub>2</sub> | 2.29             | 2.34     | 2.39  |      | AC     | 12.70 | 12,83 | 12.95 | 20       |

| В              | 0.35             | 0.41     | 0.48  |      | AD     | 15.29 | 15.42 | 15.54 | 24       |

| С              | 0.23             | 0.25     | 0.32  |      | ΑĒ     | 17.81 | 17.93 | 18.06 | 28       |

|                | D SEE VARIATIONS |          |       | 3    |        |       |       |       |          |

| E              | 7.42             | 7.52     | 7.59  |      |        |       |       |       | 1        |

| e              |                  | 1.27 BSC |       |      |        |       |       |       | i        |

| $\Box$ H       | 10.16            | 10.31    | 10.41 |      |        | l     |       |       | i i      |

| h              | 0.25             | 0,33     | 0.41  |      |        |       |       |       |          |

| 7              | 0.61             | 0.81     | 1.02  |      |        |       |       |       |          |

| N              |                  |          |       | 5    |        |       |       |       |          |

| ≈              | 0°               | 5°       | 8°    |      |        |       |       |       |          |

| X              | 2.16             | 2.36     | 2.54  |      |        |       |       |       |          |

<sup>©</sup> Cypress Semiconductor Corporation, 1999. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.