### зос D 🔳 6427525 0027007 4 🔳

### μPD70330/70332 (V35) **16-Bit Microcomputers:** Advanced, Single-Chip, CMOS

### T-49-19-16

T-49-19-59

### Description

The µPD70330/70332 (V35™) is a high-performance, 16-bit single-chip microcomputer with a 16-bit external data bus. The µPD70330/70332 is fully software compatible with µPD8086/8088 and µPD70108/70116 (V20®/30®) instruction set.

The µPD70330 is a ROMless part. The µPD70332 has 16K ROM, while the µPD70P322 has 16K EPROM and can be used as a  $\mu$ PD70330 (V35) or a  $\mu$ PD70320 (V25™).

### **Features**

- $\Box$  Functionally compatible with  $\mu$ PD70320/322 (V25)

- □ Internal 16-bit architecture and external 16-bit

- data bus  $\Box$  Software compatible with  $\mu$ PD8086/8088.

- µPD70108/70116 (V20/30) in the native mode New and enhanced instructions

- Six-byte prefetch queue

- □ Minimum instruction cycle: 500 ns at 8 MHz □ Internal memory

- - ROM: 16K bytes (µPD70332 only)

- RAM: 256 bytes

- □ Memory space: 1M bytes

- □ Input port with comparator (port T): eight bits Bus interface optimized for use with dynamic

- RAMs

- Multiplexed address

50006-1 (NECEL-870)

- On-board refresh controller

V20 and V30 are registered trademarks of NEC Corporation. V25 and V35 are trademarks of NEC Corporation.

- 24 parallel I/O lines

- Serial interface: two channels

- Dedicated baud rate generator

- Asynchronous mode, I/O interface mode Interrupt controller

- - Programmable priority (eight levels) - Three interrupt service functions

- Vectored interrupt, register bank switching, macro service

- DRAM, pseudo SRAM refresh function

- Two DMA channels

- Two 16-bit timers

- One 20-bit time base counter

- Clock generator

- Programmable wait function

- □ Low power modes

- HALT

- STOP

- □ 1.2-micron CMOS

#### **Ordering Information**

| Part- Number    | Clock (MHz) | Package            | Internal ROM               |

|-----------------|-------------|--------------------|----------------------------|

| µPD70330L-8     | 8           | 84-pin PLCC        | ROMIess                    |

| GJ-8            | 8           | 94-pin plastic QFP |                            |

| µPD70332L-8-xxx | 8           | 84-pin PLCC        | 16K mask ROM               |

| GJ-8-xxx        | 8           | 94-pin plastic QFP |                            |

| µPD70P322KE-8   | 8           | 84-pin LCC         | 16K EPROM<br>(UV erasable) |

30E D 🖿 6427525 0027008 6

7

T-49-19-16 T-49-19-59

### μ**PD7**0330/332 (V35)

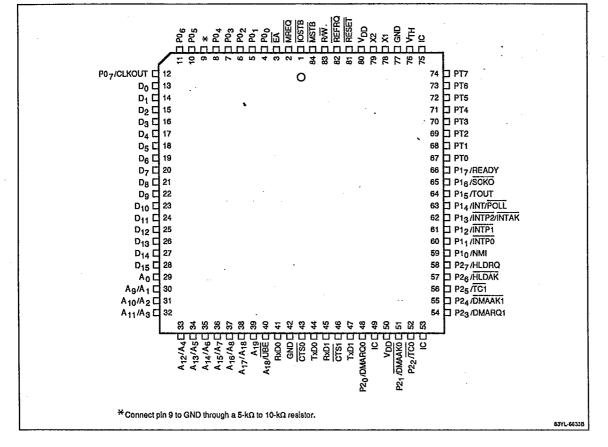

### **Pin Configuration**

84-Pin PLCC and 84-Pin LCC

2

:

### μ**PD70330/332 (V35)**

T-49-19-16 **T-49-19-59**

3

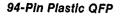

### **Pin Configuration (cont)**

30E D 🖿 6427525 0027010 4 1

### μ**PD70330/332 (V35)**

### **Pin Identification**

| Symbol                          | Function                                                                      |

|---------------------------------|-------------------------------------------------------------------------------|

| A19-A0                          | Address bus outputs                                                           |

| CLKOUT                          | System clock output                                                           |

| CTS0                            | Clear-to-send input, serial channel 0                                         |

| CTS1                            | Clear-to-send input, serial channel 1                                         |

| D <sub>15</sub> -D <sub>0</sub> | Bidirectional data bus                                                        |

| DMAAK0                          | DMA acknowledge output, DMA controller<br>channel 0                           |

| DMAAK1                          | DMA acknowledge output, DMA<br>controller channel 1                           |

| DMARQ0                          | DMA request input, DMA controller<br>channel 0                                |

| DMARQ1                          | DMA request input, DMA controller<br>channel 1                                |

| ĒĀ                              | External access; clamped low or high according to program access requirements |

| HLDAK                           | Hold acknowledge output                                                       |

| HLDRQ                           | Hold request input                                                            |

| INT                             | Interrupt request input                                                       |

| INTAK                           | Interrupt acknowledge output                                                  |

| INTPO                           | Interrupt request 0 input                                                     |

| INTP1                           | Interrupt request 1 input                                                     |

| INTP2                           | Interrupt request 2 input                                                     |

| IOSTB                           | I/O read or write strobe output                                               |

| MREQ                            | Memory request output                                                         |

| MSTB                            | Memory strobe output                                                          |

| NMI                             | Nonmaskable interrupt request                                                 |

| POLL                            | Input on POLL synchronizes the CPU and<br>external devices                    |

| P07-P00                         | I/O port 0                                                                    |

| P17-P10                         | I/O port 1                                                                    |

| P27-P20                         | 1/0 port 2                                                                    |

| PTO-PT7                         | Comparator port input lines                                                   |

| READY                           | Ready signal input controls insertion of wait states                          |

| REFRO                           | DRAM refresh request output                                                   |

| RESET                           | Reset signal input                                                            |

| R/W                             | Read/write strobe output                                                      |

| RxD0                            | Receive data input, serial channel 0                                          |

|                                 |                                                                               |

|        | T-49-19-59                                                                                |

|--------|-------------------------------------------------------------------------------------------|

| Symbol | Function                                                                                  |

| RxD1   | Receive data input, serial channel 1                                                      |

| SCKO   | Serial clock output                                                                       |

| TCO    | Terminal count output; DMA completion, channel 0                                          |

| TC1    | Terminal count output; DMA completion, channel 1                                          |

| TOUT   | Timer output                                                                              |

| TxD0   | Transmit data output, serial channel 0                                                    |

| TxD1   | Transmit data output, serial channel 1                                                    |

| UBE    | Upper byte enable                                                                         |

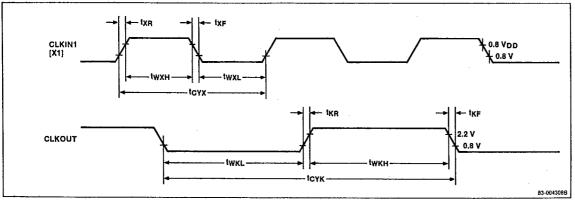

| X1, X2 | Connections to external frequency control source (crystal, ceramic resonator, or clock)   |

| VDD    | +5-volt power source input (two pins)                                                     |

| VTH    | Threshold voltage input to comparator circuits                                            |

| GND    | Ground reference (two pins)                                                               |

| IC     | Internal connection; must be tied to V <sub>DD</sub> externally through a pullup resistor |

NEC

T-49-19-16

ĥ

### μ**PD70330/332 (V35)**

### **Pin Functions**

#### A<sub>19</sub>-A<sub>0</sub>; Address Bus

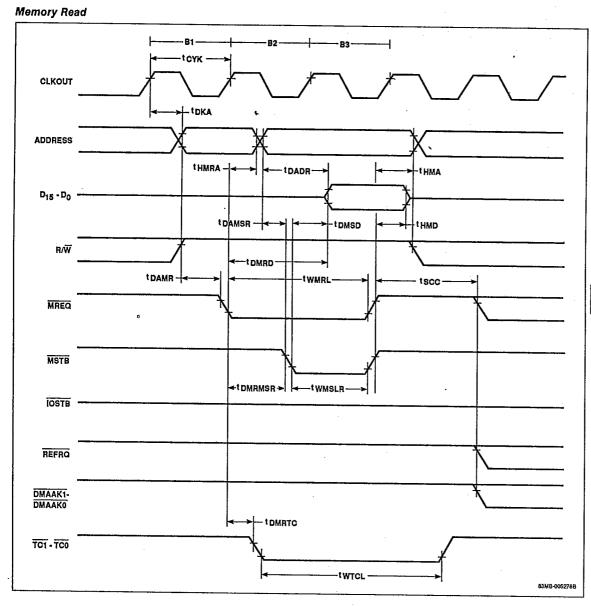

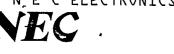

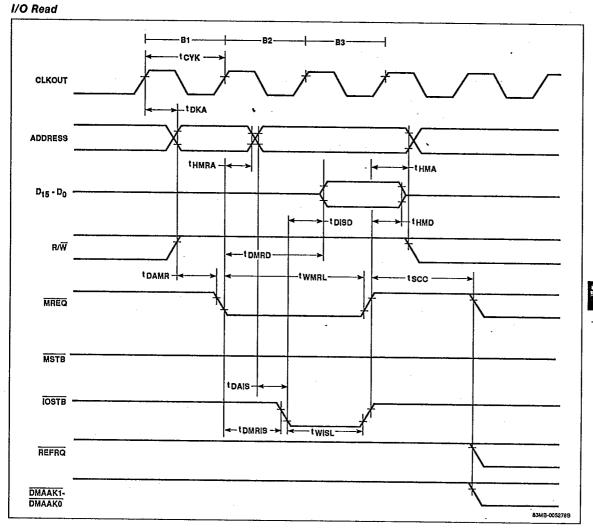

To support dynamic RAMs, the 20-bit address is multiplexed on 11 lines. When  $\overline{\text{MREQ}}$  is asserted,  $A_{17}$ - $A_9$  are valid. When  $\overline{\text{MSTB}}$  or  $\overline{\text{IOSTB}}$  are asserted,  $A_8$ - $A_1$  and  $A_{18}$  are valid.  $A_{18}$  is also multiplexed with  $\overline{\text{UBE}}$  and is valid when  $\overline{\text{MREQ}}$  is asserted. Therefore  $A_{18}$  is active throughout the bus cycle.  $A_{19}$  and  $A_0$  are not multiplexed but have dedicated pins and are valid throughout the bus cycle.

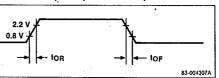

### **CLKOUT; Clock Out**

The system clock (CLK) is distributed from the internal clock generator to the CPU and output to peripheral hardware at the CLKOUT pin.

### CTS0; Clear-to-Send 0

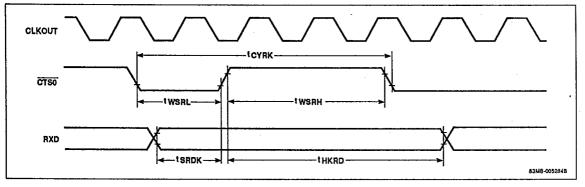

This is the CTS pin of the channel 0 serial interface. In asynchronous mode, a low-level input on CTS0 enables transmit operation. In I/O interface mode, CTS0 is the receive clock pin.

### CTS1; Clear-to-Send 1

This is the CTS pin of the channel 1 serial interface. In asynchronous mode, a low-level input on CTS1 enables transmit operation.

### D<sub>15</sub>-D<sub>0</sub>; Data Bus

D<sub>15</sub>-D<sub>0</sub> is the 16-bit data bus.

### DMAAK0 and DMAAK1; DMA Acknowledge

These are the DMA acknowledge outputs of the DMA controller, channels 0 and 1. Signals are not output during DMA memory-to-memory transfer operations (burst mode, single-step mode).

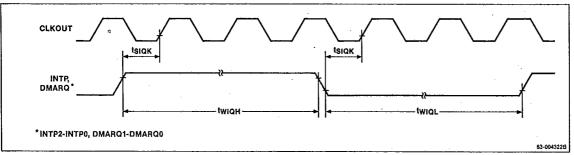

### DMARQ0 and DMARQ1; DMA Request

These are the DMA request inputs of the DMA controller, channels 0 and 1.

### EA; External Access

T-49-19-59

T-49-19-16

For the ROM-less  $\mu$ PD70330, connect this pin to ground. For the  $\mu$ PD70332, connect EAto ground if program code is in external memory; connect EA to +5 volts if program code is in the internal ROM.

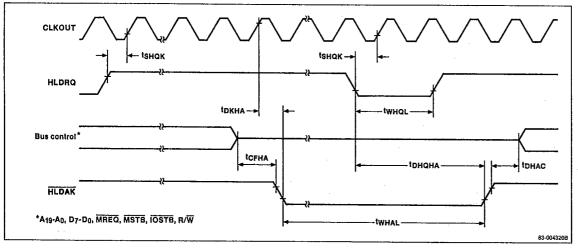

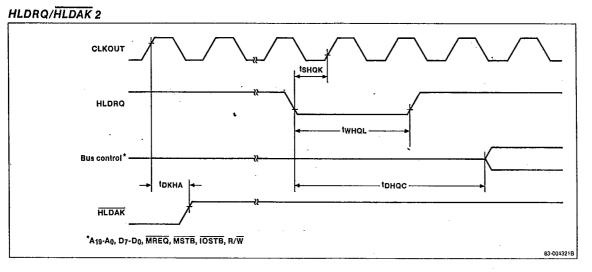

### HLDAK; Hold Acknowledge

The HLDAK output signal indicates that the hold request (HLDRQ) has been accepted. When HLDAK is active (low), the following lines go to the high-impedance state with internal 4700-ohm pullup resistors:  $A_{19}$ - $A_0$ ,  $D_7$ - $D_0$ , IOSTB, MREQ, MSTB, REFRQ, and R/W.

#### HLDRQ; Hold Request

The HLDRQ input from an external device requests that the  $\mu$ PD70330/332 relinquish the address, data, and control buses to an external bus master.

#### INT; Interrupt

The INT input is a vectored interrupt request from an external device that can be masked by software. The active high level is detected in the last clock cycle of an instruction. The external device confirms that the INT interrupt request has been accepted by the INTAK signal output from the CPU.

The INT signal must be held high until the first INTAK signal is output. Together with INTAK, INT is used for operation with an interrupt controller such as  $\mu$ PD71059.

### **INTAK;** Interrupt Acknowledge

The INTAK output is the acknowledge signal for the software-maskable interrupt request INT. The INTAK signal goes low when the CPU accepts INT. The external device inputs the interrupt vector to the CPU via data bus  $D_7$ - $D_0$  in synchronization with INTAK.

### μ**PD7**0330/332 (V35)

### INTP0, INTP1, INTP2; Interrupt from Peripheral 0, 1, 2

The  $\overline{INTPn}$  inputs (n = 0, 1, 2) are external interrupt requests that can be masked by software. The  $\overline{INTPn}$  input is detected at the effective edge specified by external interrupt mode register INTM.

The INTPn input is also used to release the HALT mode.

#### IOSTB; I/O Strobe

A low-level output on  $\overline{IOSTB}$  indicates that the I/O bus cycle has been initiated and that the I/O address output on  $A_{15}$ - $A_0$  is valid.

#### MREQ; Memory Request

A low-level output on  $\overline{\text{MREQ}}$  indicates that the memory or I/O bus cycle has started and that address bits A<sub>0</sub>, A<sub>17</sub>-A<sub>9</sub>, A<sub>19</sub> and A<sub>18</sub> are valid.

#### MSTB; Memory Strobe

Together with  $\overline{\text{MREQ}}$  and  $\overline{\text{R/W}}$ ,  $\overline{\text{MSTB}}$  controls memory accessing operations.  $\overline{\text{MSTB}}$  should be used either to enable data buffers or as a data strobe. During memory write, a low-level output on  $\overline{\text{MSTB}}$  indicates that data on the data bus is valid. A low-level output on  $\overline{\text{MSTB}}$ indicates that multiplexed address bits  $A_8$ - $A_1$ ,  $A_{18}$ , and  $\overline{\text{UBE}}$  are valid.

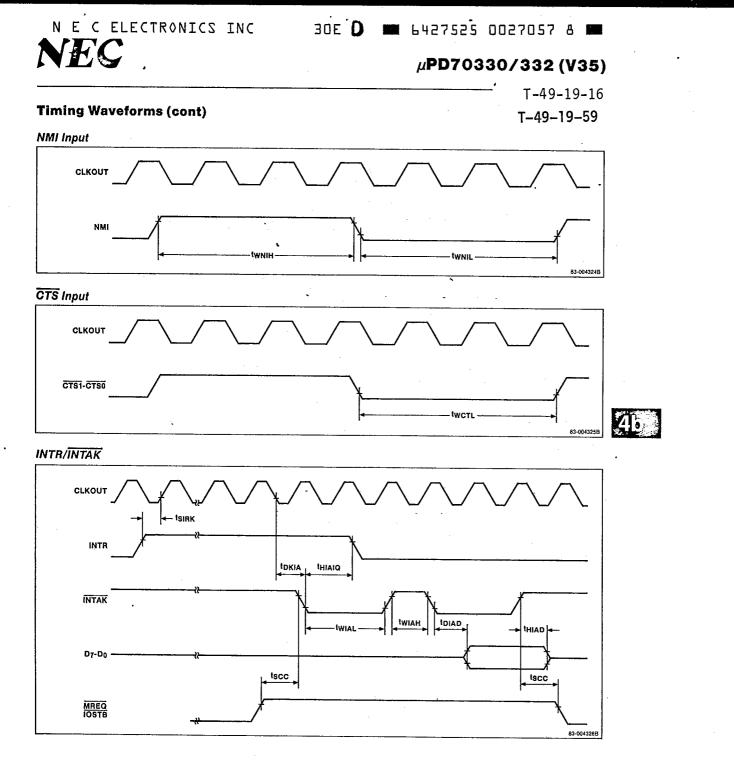

#### NMI; Nonmaskable Interrupt

The NMI input is an interrupt request that cannot be masked by software. The NMI is always accepted by the CPU; therefore, it has priority over any other interrupt.

The NMI input is detected at the effective edge specified by external interrupt mode register INTM. Sampled in each clock cycle, NMI is accepted when the active level lasts for some clock cycles. When the NMI is accepted, a number 2 vector interrupt is generated after completion of the instruction currently being executed.

The NMI input is also used to release the CPU standby mode.

### P07-P00; Port 0

Port 0 is an 8-bit bidirectional I/O port.

#### P17-P10; Port 1

30E **D**

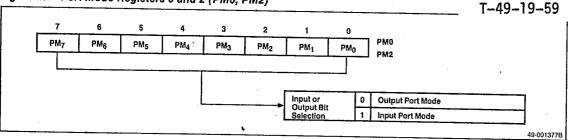

Lines P1<sub>7</sub>-P1<sub>4</sub> are individually programmable as an input, output, or control function. The status of P1<sub>3</sub>-P1<sub>0</sub> can be read but these lines are always control functions.

### P27-P20; Port 2

P27-P20 are the lines of port 2, an 8-bit bidirectional I/O port. These lines can also be used as control signals for the on-chip DMA controllers. See table 2-3.

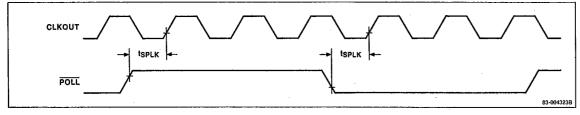

### POLL; Poll

The POLL input is checked by the POLL instruction. If the level is low, execution of the next instruction is initiated. If the level is high, the POLL input is checked every five clock cycles until the level becomes low.

The POLL functions are used to synchronize the CPU program and the operation of external devices.

Note: POLL is effective when P14 is specified for the input port mode; otherwise, POLL is assumed to be at low level when the POLL instruction is executed.

#### PT0-PT7; Port with Comparator

The PT input is compared with a threshold voltage that is programmable to one of 16 voltage steps individually for each of the eight lines.

#### READY

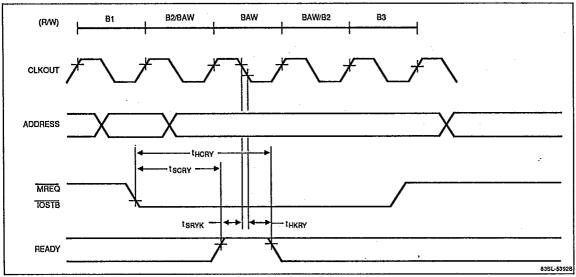

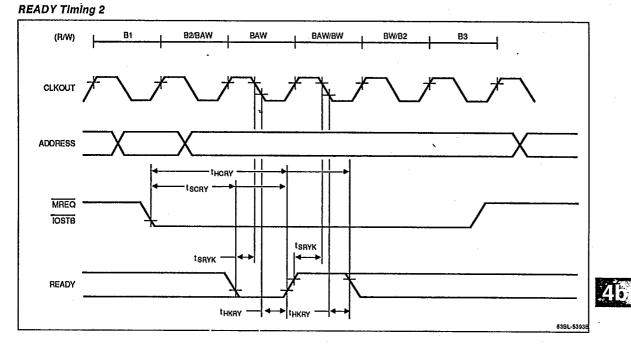

After READY is de-asserted low, the CPU will synchronize and insert at least two wait states into a read or write cycle to memory or I/O. This allows the processor to accommodate devices whose access times are longer than normal execution allows.

#### **REFRQ;** Refresh Request

This output pulse can refresh nonstatic RAM. It can be programmed to meet system specifications and is internally synchronized so that refresh cycles do not interfere with normal CPU operation.

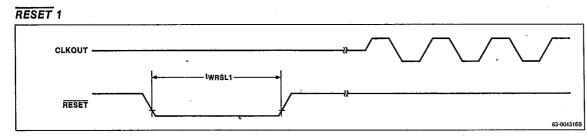

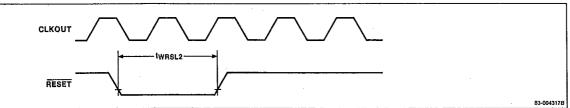

### RESET

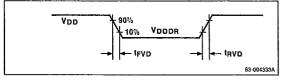

This input signal is asynchronous. A low on RESET for a certain duration resets the CPU and all on-chip peripherals regardless of clock operation. The reset operation has priority over all other operations.

The reset signal is used for normal initialization/startup and also for releasing the STOP or HALT mode. After the reset signal returns high, program execution begins from address FFFF0H.

6

### н 6427525°0027012 8 н NEC т-49-19-16

T-49-19-59

### R/W; Read/Write Strobe

When the memory bus cycle is initiated, the  $R/\overline{W}$  signal output to external hardware indicates a read (high level) or write (low level) cycle. It can also control the direction of bidirectional buffers.

### RxD0, RxD1; Receive Data 0, 1

These pins input data from serial channels 0 and 1.

In the asynchronous mode, when receive operation is enabled, a low level on the RxD0 or RxD1 input pin is recognized as the start bit and receive operation is initiated.

In the I/O interface mode (channel 0 only), receive data is input to the serial register at the rising edge of the receive clock.

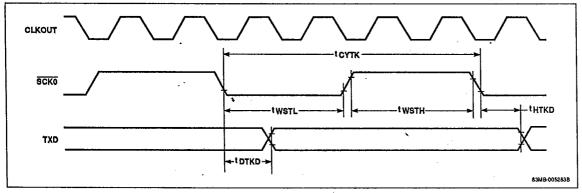

### SCKO; Serial Clock

The SCKO output is the transmit clock of serial channel 0.

### TC0, TC1; Terminal Count 0, 1

The  $\overline{TC0}$  and  $\overline{TC1}$  outputs go low when the terminal count of DMA service channels 0 and 1, respectively, reach zero, indicating DMA completion.

#### **TOUT;** Timer Output

The TOUT signal is a square-wave output from the internal timer.

#### TxD0, TxD1; Transmit Data 0, 1

These pins output data from serial channels 0 and 1.

In the asynchronous mode, the transmit signal is in a frame format that consists of a start bit, 7 or 8 data bits (least significant bit first), parity bit, and stop bit. The TxD0 and TxD1 pins become mark state (high level) when transmit operation is disabled or when the serial register has no transmit data.

In the I/O interface mode (channel 0 only), the frame has 8 data bits and the most significant bit is transmitted first.

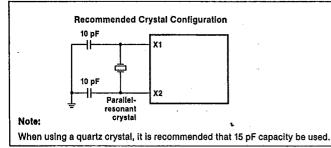

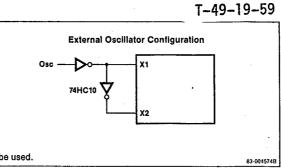

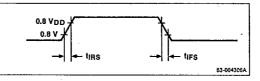

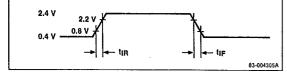

## X1, X2; Clock Control

### T-49-19-59

T-49-19-16

The frequency of the internal clock generator is controlled by an external crystal or ceramic resonator connected across pins X1 and X2. The crystal frequency is the same as the clock generator frequency  $f_X$ . By programming the PRC register, the system clock frequency  $f_{CLK}$  is selected as  $f_X$  divided by 2, 4, or 8.

μPD70330/332 (V35)

As an alternative to the crystal or ceramic resonator, the positive and negative phases of an external clock (with frequency  $f_X$ ) can be connected to pins X1 and X2.

### VDD

+5-volt power source (two pins).

#### VTH

Comparator port PT0-PT7 uses threshold voltage  $V_{TH}$  to determine the analog reference points. The actual threshold to each comparator line is programmable to  $V_{TH} \times n/16$  where n = 1 to 16.

#### GND

Ground reference (two pins).

### IC

Internal connection; must be tied to  $V_{DD}$  externally through a 10-k $\Omega$  to 20-k $\Omega$  resistor.

### UBE, Upper Byte Enable

UBE is a high-order memory bank selection signal output. UBE and  $A_0$  are used to decide which bytes of the data bus will be used. UBE is used along with  $A_0$  to select the even/odd banks as follows.

| UBE | Ao                           | Number of bus cycles                                                                           |

|-----|------------------------------|------------------------------------------------------------------------------------------------|

| 0   | 0                            | 1                                                                                              |

| 0   | 1                            | 2                                                                                              |

| 1   | 0                            |                                                                                                |

| 1   | 0                            | 1                                                                                              |

| Ø   | 1                            | 1                                                                                              |

|     | UBE<br>0<br>0<br>1<br>1<br>0 | UBE     A0       0     0       1     0       1     0       0     1       0     1       0     1 |

7

### ЗОЕ 🕽' 🖿 6427525 0027013 Т 🔳

# 30E D ■ 6427525 0027014 1 ■

### μ**PD70330/332 (V35)**

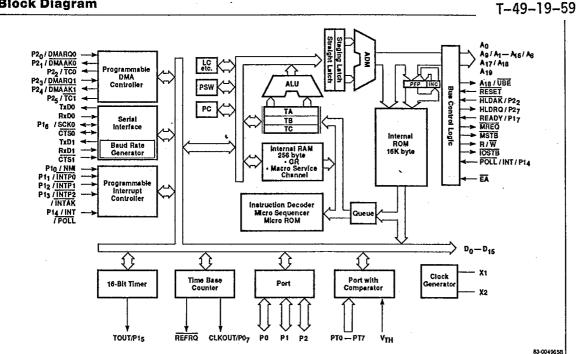

#### **Block Diagram**

### **Functional Description**

#### **Architectural Enhancements**

The following features enable the  $\mu$ PD70330/332 to perform high-speed execution of instructions:

- Dual data bus .

- 16-/32-bit temporary registers/shifters (TA, TB, . TA + TB

- 16-bit loop counter (LC)

- Program counter (PC) and prefetch pointer (PFP) .

- Internal ROM pass bus (µPD70332 only) •

Dual Data Bus. The µPD70330/332 has two internal 16-bit data buses: the main data bus and a subdata bus. This reduces the processing time required for addition/ subtraction and logical comparison instructions by one-third over single-bus systems. The dual data bus method allows two operands to be fetched simultaneously from the general-purpose registers and transferred to the ALU.

16-/32-Bit Temporary Registers/Shifters. The 16-bit temporary registers/shifters (TA, TB) allow high-speed execution of multiplication/division and shift/rotation instructions. By using the temporary registers/shifters.

the µPD70330/332 can execute multiplication/division instructions about four times faster than with the microprogramming method.

T-49-19-16

Loop Counter [LC]. The dedicated hardware loop counter counts the number of loops for string operations and the number of shifts performed for multiple bit shift/ rotation instructions. The loop counter works with internal dedicated shifters to speed the processing of multiplication/division instructions.

Program Counter and Prefetch Pointer [PC and PFP]. The hardware PC addresses the memory location of the instruction to be executed next. The hardware PFP addresses the program memory location to be accessed next. Several clocks are saved for branch, call, return, and break instructions compared with processors having only one instruction pointer.

Internal ROM Pass Bus. The uPD70332 features a dedicated data bus between the internal ROM and the instruction pre-fetch queue. This allows internal ROM opcode fetches to be performed in a single clock cycle (200 ns at 5 MHz); it also makes it possible for opcode fetches to be performed while the external data bus is busy. This feature gives the V35 a 10-20% performance increase when executing from the internal ROM.

30E 🕽 🖿 6427525 0027015 3 🖿

N E C ELECTRONICS INC

μ**PD70330/332 (V35)** T-49-19-16 T-49-19-59

### **Register Set**

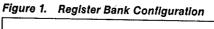

The  $\mu$ PD70330/70332 CPUs have general purpose register sets compatible with the  $\mu$ PD70108/70116 and the  $\mu$ PD70320/70322 microprocessors. Like the  $\mu$ PD70320/70322, they also have a set of special function registers for controlling the onboard peripherals. All registers reside in the CPU's memory space. They are grouped in a 4K byte block called the internal data area (IDA). The 256 byte internal RAM is also in the IDA. The addresses of the register are given as offsets into the IDA. The start address of the IDA is set by the Internal Data Area Base register (IDB), and may be programmed to any 4K boundary in the memory address space.

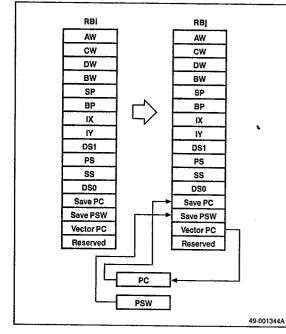

**Register Banks.** Because the general purpose register set is in internal RAM, it is possible to have multiple banks of registers. The  $\mu$ PD70330/70332 CPU supports up to 8 register banks. A bit field in the PSW selects which bank is currently being used. Each bank contains the entire CPU register set plus additional information needed for context switching. Register banks may be switched using special instructions (TSKSW, BRKCS, MOVSPA, MOVSPB), or may switch in response to an interrupt. This provides fast context switching and fast interrupt handling. During and after RESET, register bank 7 is selected.

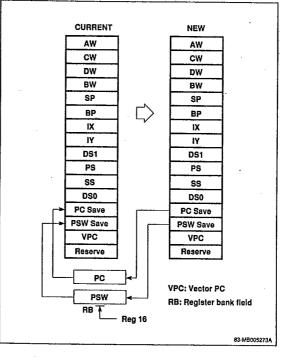

Figure 1 shows the configuration of a register bank and how the banks are mapped to internal RAM. The Vector PC field contains the value that will be loaded into the PC when a register bank switch occurs. The PC Save and PSW Save fields contain the values of the PC and the PSW just before the banks are switched. The PSW is left unmodified after a bank switch; the PSW Save field is used to restore the PSW to its previous state is required.

General-Purpose Registers [AW, BW, CW, DW]. These four 16-bit general-purpose registers can also serve as independent 8-bit registers (AH, AL, BH, BL, CH, CL, DH, DL). The instructions below use general-purpose registers for default;

- AW Word multiplication/division, word I/O, data conversion

- AL Byte multiplication/division, byte I/O, BCD rotation, data conversion, translation

- AH Byte multiplication/division

- BW Translation

- CW Loop control branch, repeat prefix

- CL Shift instructions, rotation instructions, BCD operations

- DW Word multiplication/division, indirect addressing I/O

### 6427525 0027016 5 🛚

T-49-19-59

### N E C ELECTRONICS INC

Pointers [SP, BP] and index Registers [IX, IY]. These registers are used as 16-bit base pointers or index registers in based addressing, indexed addressing, and based indexed addressing. The registers are used as default registers under the following conditions:

30E

SP Stack operations

μ**PD7**0330/332 (V35)

- IX Block transfer (source), BCD string operations

- IY Block transfer (destination), BCD string operations

Segment Registers. The segment registers divide the 1M-byte address space into 64K-byte blocks. Each segment register functions as a base address to a block; the effective address is an offset from that base. Physical addresses are generated by shifting the associated segment register left four binary digits and then adding the effective address. The segment registers are:

| Segment Register     | Default Offset        |

|----------------------|-----------------------|

| PS (Program segment) | PC                    |

| SS (Stack segment)   | SP, Effective address |

| DS0 (Data segment-0) | IX, Effective address |

| DS1 (Data segment-1) | IY, Effective address |

During RESET, PS is set to FFFFH; DS0, DS1 and SS are set to 0000H.

**Program Counter [PC].** The PC is a 16-bit binary counter that contains the offset address from the program segment of the next instruction to be executed. It is incremented every time an instruction is received from the queue. It is loaded with a new location whenever a branch, call, return, break, or interrupt is executed. During RESET, PC is set to 0000H.

Program Status Word [PSW]. The PSW contains the following status and control flags.

T-49-19-16

| 15   |          |          | PS  | SW    |        |                    | 8                      |

|------|----------|----------|-----|-------|--------|--------------------|------------------------|

| 1    | RB2      | RB1      | RB0 | V     | DIR    | IE                 | BRK                    |

| 7    |          |          |     |       |        |                    | 0                      |

| S    | Z        | F1       | AC  | FO    | P      | BRKI               | CY                     |

| Stat | us Flags |          |     | Contr | ol Fla | gs                 |                        |

| V    | Overflo  | w bit    |     | DIR   |        |                    | f string               |

| s    | Sign     |          |     |       | •      | essing             |                        |

| z    | Zero     |          |     | IE    | Inter  | rupt er            | nable                  |

| AC   | Auxilia  | ry carry | /   | BRK   |        | k (afte<br>uction) | r every                |

| Р    | Parity   |          |     | RBn   | Curr   | ent reg            | jister                 |

| CY   | Carry    |          |     |       | bank   | flags              |                        |

|      |          |          |     | BRKI  |        | •                  | able (see<br>terrupts) |

F0, F1 General-purpose user flags

The eight low-order bits of the PSW can be stored in the A4 register and restored by a MOV instruction execution. The only way to alter the RBn bits via software is to execute an RETRBI or RETI instruction. During RESET, PSW is set to F002H. The F0 and F1 flags may be accessed as bits in the FLAG special functioning register.

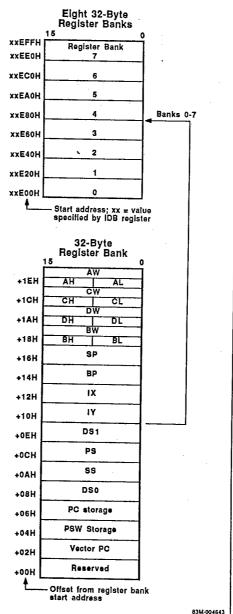

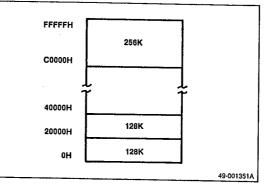

#### Memory Map

The  $\mu$ PD70330/332 has a 20-bit address bus that can directly access 1M bytes of memory. Figure 2 shows that the 16K bytes of internal ROM ( $\mu$ PD70332 only) are located at the top of the address space from FC000H to FFFFFH.

30E **D E** 6427525 0027017 7 **E**

μ**PD70330/332 (V35)**

T-49-19-16

Figure 2. Memory Map

.

N E C ELECTRONICS INC

46

### μ**PD70330/332 (V35)**

Figure 2 shows the internal data area (IDA) is a 256byte internal RAM area followed consecutively by a 256-byte special function register (SFR) area. All the data and control registers for on-chip peripherals and I/O are mapped into the SFR area and accessed as RAM. For a description of these functions, see table 6. The IDA is dynamically relocatable in 4K-byte increments by changing the value in the internal data base (IDB) register. Whatever value is in this register will be assigned as the uppermost eight bits of the IDA address. The IDB register can be accessed from two different memory locations, FFFFFH and XXFFFH, where XX is the value in the IDB register.

On reset, the internal data base register is set to FFH which maps the IDA into the internal ROM space. However, since the  $\mu$ PD70332 has a separate bus to internal ROM, this does not present a problem. When these address spaces overlap, program code cannot be executed from the IDA and internal ROM locations cannot be accessed as data.

Figure 2 shows that the internal data area is divided into 2 parts: the 256 byte internal RAM and the special function register area.

The internal RAM area serves various purposes. When the RAMEN bit in the Processor Control Register is set, this area may be accessed as RAM and code may be executed from it. Note that the processor may run slower when the RAMEN bit is set. See the Instruction Clock Count table. In addition, whether the RAMEN bit is on or off, each of the 8 macroservice channels has an 8 byte control block that is assigned to a fixed location in the low 64 bytes of the internal RAM. Similarly, the two 8 byte DMA control blocks are assigned to the low 16 bytes of the RAM. The 8 CPU register banks use 32 bytes each. Since the RAM can't be used for more than one purpose, there are restrictions on how V35 features can be combined. For example, if register bank 0 is used, then macroservice channels 0-3 and both DMA channels cannot be used. If DMA channel 1 is used. then macroservice channel 1 cannot be used.

The special function register area contains the registers used to control the onboard peripheral functions. Table 6 shows the SFRs. The address shown in the table is an offset from the IDB register. Most SFRs can be both read and written, but some are read-only; others are write-only. Some SFRs may be accessed one bit at a time; others only 8 bits at a time, and some SFRs are 16 bits wide.

#### Instructions

30E D

### T-49-19-59

T-49-19-16

The  $\mu$ PD70330/332 instruction set is fully compatible with the V20 native mode instruction set. The V20 instruction set is a superset of the  $\mu$ PD8086/8088 instruction set with different execution times and mnemonics.

🖬 6427525 0027018 9 📰

The  $\mu$ PD70330/332 does not support the V20 8080 emulation mode. All of the instructions pertaining to this have been deleted from the  $\mu$ PD70330/332 instruction set.

#### **Enhanced Instructions**

Implusion

In addition to the  $\mu$ PD8086/88 instructions, the  $\mu$ PD70330/332 has the following enhanced instructions.

| Instruction                                                                         | Function                                                                     |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| PUSH imm                                                                            | Pushes immediate data onto stack                                             |

| PUSH R                                                                              | Pushes eight general registers onto stack                                    |

| POP R                                                                               | Pops eight general registers from stack                                      |

| MUL imm                                                                             | Executes 16-bit multiply of register or<br>memory contents by immediate data |

| SHL imm8<br>SHR imm8<br>SHRA imm8<br>ROL imm8<br>ROR imm8<br>ROLC imm8<br>RORC imm8 | Shifts/rotates register or memory by immediate value                         |

| CHKIND                                                                              | Checks array index against designated boundaries                             |

| INM                                                                                 | Moves a string from an I/O port to<br>memory                                 |

| OUTM                                                                                | Moves a string from memory to an I/O port                                    |

| PREPARE                                                                             | Allocates an area for a stack frame and copies previous frame pointers       |

| DISPOSE                                                                             | Frees the current stack frame on a                                           |

procedure exit

30Ė **D**

### 🖬 6427525 0027019 O 🛤

### μ**PD70330/332 (V35)**

Т-49-19-16 Т-49-19-59

### **Unique Instructions**

The  $\mu$ PD70330/332 has the following unique instructions.

| Instruction                                                                                                    | Function |

|----------------------------------------------------------------------------------------------------------------|----------|

| the second s |          |

| INS   | Inserts bit field                      |

|-------|----------------------------------------|

| EXT   | Extracts bit field                     |

| ADD4S | Performs packed BCD string addition    |

| SUB4S | Performs packed BCD string subtraction |

| CMP4S | Performs packed BCD string comparison  |

| ROL4  | Rotates BCD digit left                 |

| ROR4  | Rotates BCD digit right                |

| TEST1 | Tests bit                              |

| SET1  | Sets bit                               |

| CLR1  | Clears bit                             |

| NOT1  | Complements bit                        |

| BTCLR | Tests bit; if true, clear and branch   |

| REPC  | Repeat while carry set                 |

| REPNC | Repeat while carry cleared             |

### Variable Length Bit Field Operation Instructions

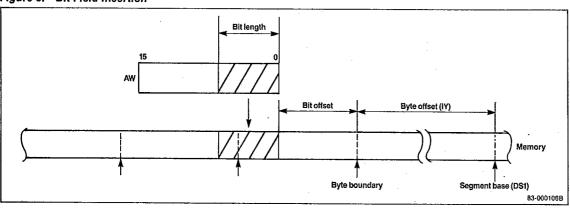

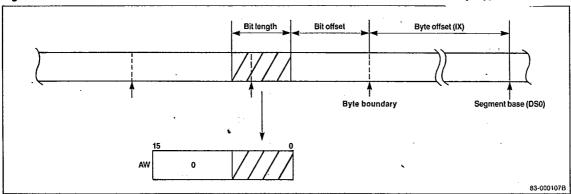

Bit fields are a variable length data structure that can range in length from 1 to 16 bits. The  $\mu$ PD70330/332 supports two separate operations on bit fields: insertion (INS) and extraction (EXT). There are no restrictions on the position of the bit field in memory. Separate segment, byte offset, and bit offset registers are used for insertion and extraction. Following the execution of these instructions, both the byte offset and bit offset

#### Figure 3. Bit Field Insertion

are left pointing to the start of the next bit field, ready for the next operation. Bit field operation instructions are powerful and flexible and are therefore highly effective for graphics, high-level languages, and packing/ unpacking applications.

Bit field insertion copies the bit field of specified length from the AW register to the bit field addressed by DS1:IY:reg8 (8-bit general-purpose register). The bit field length can be located in any byte register or supplied as immediate data. Following execution, both the IY and reg8 are updated to point to the start of the next bit field.

Bit field extraction copies the bit field of specified length from the bit field addressed by DS0:IX:reg8 to the AW register. If the length of the bit field is less than 16 bits, the bit field is right justified with a zero fill. The bit field length can be located in any byte register or supplied as immediate data. Following execution, both IX and reg8 are updated to point to the start of the next bit field.

Figures 3 and 4 show bit field insertion and bit field extraction.

#### **Packed BCD Instructions**

Packed BCD instructions process packed BCD data either as strings (ADD4S, SUB4S, CMP4S) or byte format operands (ROR4, ROL4). Packed BCD strings may be 1 to 254 digits in length. The two BCD rotation instructions perform rotation of a single BCD digit in the lower half of the AL register through the register or the memory operand.

μ**PD70330/332 (V35)**

### Figure 4. Bit Field Extraction

30E **D**

#### **Bit Manipulation Instructions**

The  $\mu$ PD70330/332 has five unique bit manipulation instructions. The ability to test, set, clear, or complement a single bit in a register or memory operand increases code readability as well as performance over the logical operations traditionally used to manipulate bit data. This feature further enhances control over on-chip peripherals.

#### **Additional Instructions**

Besides the V20 instruction set, the  $\mu$ PD70330/0332 has the eight additional instructions described in table 1.

#### Table 1. Additional Instructions Instruction Function BTCLR var, imm8, Bit test and if true, clear and branch; short label otherwise, no operation STOP (no operand) Power down instruction, stops oscillator **RETRBI** (no operand). Return from register bank context switch interruot FINT (no operand) Finished interrupt. After completion of a hardware interrupt request, this instruction must be used to reset the current priority bit in the in-service priority register (ISPR).\*

\*Do not use with NMI or INTR Interrupt service routines.

#### **Repeat Prefixes**

Two new repeat prefixes (REPC, REPNC) allow conditional block transfer instructions to use the state of the CY flag as the termination condition. This allows inequalities to be used when working on ordered data, thus increasing performance when searching and sorting algorithms.

### **Bank Switch Instructions**

The V35 has four new instructions that allow the effective use of the register banks for software interrupts and multitasking. These instructions are shown in table 2. Also, see figures 8 and 10.

🛛 🖬 6427525 0027020 7 1

T-49-19-16

T-49-19-59

#### Table 2. Bank Switch Instructions

| Instruction  | Function                                                                                                                                                                                                                                                                                |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| BRKCS reg 16 | Performs a high-speed software interrupt with<br>context switch to the register bank indicated<br>by the lower 3-bits of reg 16. This operation is<br>identical to the interrupt operation shown in<br>figure 9.                                                                        |  |  |

| TSKSW reg 16 | Performs a high-speed task switch to the<br>register bank indicated by the lower 3-bits of<br>reg 16. The PC and PSW are saved in the old<br>banks. PC and PSW save registers and the new<br>PC and PSW values are retrieved from the new<br>register bank's save areas. See figure 10. |  |  |

| MOVSPA       | Transfers both the SS and SP of the old<br>register bank to the new register bank after<br>the bank has been switched by an interrupt or<br>BRKCS instruction.                                                                                                                          |  |  |

| MOVSPB       | Transfers the SS and the SP of the current<br>register bank before the switch to the SS and<br>SP of the new register bank indicated by the<br>lower 3-bits of reg 16.                                                                                                                  |  |  |

#### **Interrupt Structure**

The  $\mu$ PD70330/332 can service interrupts generated both by hardware and by software. Software interrupts are serviced through vectored interrupt processing. See table 3 for the various types of software interrupts.

μPD70330/332 (V35)

#### Table 3. Software Interrupts

| Interrupt                 | Description                                                                                                                                                                                                                                         |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Divide error              | The CPU will trap if a divide error occurs as the result of a DIV or DIVU instruction.                                                                                                                                                              |

| Single step               | The Interrupt is generated after every instruction<br>if the BRK bit in the PSW is set.                                                                                                                                                             |

| Overflow                  | By using the BRKV instruction, an interrupt can be generated as the result of an overflow.                                                                                                                                                          |

| Interrupt<br>Instructions | The BRK 3 and BRK imm8 instructions can generate interrupts.                                                                                                                                                                                        |

| Array bounds              | The CHKIND instruction will generate an interrupt if specified array bounds have been exceeded.                                                                                                                                                     |

| Escape trap               | The CPU will trap on an FP01,2 instruction to allow software to emulate the floating point processor.                                                                                                                                               |

| I/O trap                  | If the I/O trap bit in the PSW is cleared, a trap will<br>be generated on every IN or OUT instruction.<br>Software can then provide an updated peripheral<br>address. This feature allows software<br>interchangeability between different systems. |

When executing software written for another system, it is better to implement I/O with on-chip peripherals to reduce external hardware requirements. However, since µPD70330/332 internal peripherals are memory mapped, software conversion could be difficult. The I/O trap feature allows easy conversion from external peripherals to on-chip peripherals.

### **Interrupt Vectors**

The starting address of the interrupt processing routines may be obtained from table 4. The table begins at physical address 00H, which is outside the internal ROM space. Therefore, external memory is required to service these routines. By servicing Interrupts via the macro service function or context switching, this requirement can be eliminated.

Each interrupt vector is four bytes wide. To service a vectored interrupt, the lower addressed word is transferred to the PC and the upper word to the PS. See figure 5.

### T-49-19-16 T-49-19-59 Figure 5. Interrupt Vector 0

Vector 0

000H

002H

PS ← (003H, 002H) PC ← (001H, 000H)

ЗÓЕ

## 001H 003H 83-000112A

#### Table 4. Interrupt Vectors

| Address | Vector No. | Assigned Use                                  |

|---------|------------|-----------------------------------------------|

| 00      | 0          | Divide error                                  |

| 04      | 1          | Break flag                                    |

| 08      | 2          | NMI                                           |

| 00      | 3          | BRK3 instruction                              |

| 10      | 4          | BRKV instruction                              |

| 14      | 5          | CHKIND instruction                            |

| 18      | 6          | General purpose                               |

| 10      | 7          | FPO instructions                              |

| 20-2C   | 8-11       | General purpose                               |

| 30      | 12         | INTSER0 (Interrupt serial error, channel 0)   |

| 34      | 13         | INTSR0 (Interrupt serial receive, channel 0)  |

| 38      | 14         | INTSTO (Interrupt serial transmit, channel 0) |

| 30      | 15         | General purpose                               |

| 40      | 16         | INTSER1 (Interrupt serial error, channel 1)   |

| 44      | 17         | INTSR1 (Interrupt serial receive, channel 1)  |

| 48      | 18         | INTST1 (Interrupt serial transmit, channel 1) |

| 4C      | 19         | I/O trap                                      |

| 50      | 20         | INTDO (Interrupt from DMA, channel 0)         |

| 54      | 21         | INTD1 (Interrupt from DMA, channel 1)         |

| 58      | 22         | General purpose                               |

| 5C      | 23         | General purpose                               |

| 60      | 24         | INTPO (Interrupt from peripheral 0)           |

| 64      | 25         | INTP1 (Interrupt from peripheral 1)           |

| 68      | 26         | INTP2 (interrupt from peripheral 2)           |

| 6C      | 27         | General purpose                               |

| 70      | 28         | INTTUO (Interrupt from timer unit 0)          |

| 74      | 29         | INTTU1 (Interrupt from timer unit 1)          |

| 78      | 30         | INTTU2 (Interrupt from timer unit 2)          |

| 70      | 31         | INTTB (Interrupt from time base counter)      |

| 080-3FF | 32-255     | General purpose                               |

| ·       |            |                                               |

μ**PD70330/332 (V35)**

T-49-19-16 T-49-19-59

Execution of a vectored interrupt occurs as follows:

$(SP-1, SP-2) \leftarrow PSW$  $(SP-3, SP-4) \leftarrow PS$  $(SP-5, SP-6) \leftarrow PC$  $SP \leftarrow SP-6$  $IE \leftarrow 0, BRK \leftarrow 0$  $PS \leftarrow$  vector high bytes  $PC \leftarrow$  vector low bytes

#### Hardware Interrupt Configuration

The V35 features a high-performance on-bhip controller capable of controlling multiple processing for interrupts from up to 17 different sources (5 external, 12 internal). The interrupt configuration includes system interrupts that are functionally compatible with those of the V20/V30 and unique high-performance microcontroller interrupts.

### Interrupt Sources

The 17 interrupt sources (table 5) are divided into groups for management by the interrupt controller. Using software, each of the groups can be assigned a priority from 0 (highest) to 7 (lowest). The priority of individual interrupts within a group is fixed in hardware. If interrupts from different groups occur simultaneously and the groups have the same assigned priority level, the priority followed will be as shown in the Default Priority column of table 5.

30E n 🖬 6427525 0027022 O I

The ISPR is an 8-bit SFR; bits  $PR_0$ - $PR_7$  correspond to the eight possible interrupt request priorities. The ISPR keeps track of the priority of the interrupt currently being serviced by setting the appropriate bit. The address of the ISPR is XXFFCH. The ISPR format is shown below.

| PR <sub>7</sub> | PR <sub>6</sub> | PR5     | PR4 | PR <sub>3</sub> | PR <sub>2</sub> | PR <sub>1</sub> | PRo |

|-----------------|-----------------|---------|-----|-----------------|-----------------|-----------------|-----|

| ليجنب ك         |                 | - · · · |     |                 | -               |                 |     |

NMI and INT are system-type external vectored interrupts. NMI is not maskable via software. INTR is maskable (IE bit in PSW) and requires that an external device provide the interrupt vector number. It allows expansion by the addition of an external interrupt controller ( $\mu$ PD71059).

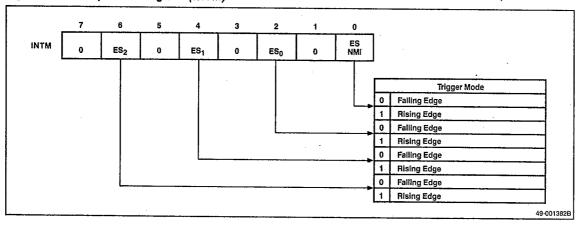

NMI, INTP0, and INTP1 are edge-sensitive interrupt inputs. By selecting the appropriate bits in the interrupt mode register, these inputs can be programmed to be either rising or falling edge triggered.  $ES_0-ES_2$  correspond to INTP0-INTP2, respectively. See figure 6.

Figure 6. Interrupt Mode Register (INTM)

30E D 💻 6427525 0027023 2 🔳

### μ**PD70330/332 (V35)**

T-49-19-16

T-49-19-59

### Table 5. Interrupt Sources

NEC

|                                                           |                       |               |                  |                   |                     | Priority Order    |                  | Multi-te                          |            |

|-----------------------------------------------------------|-----------------------|---------------|------------------|-------------------|---------------------|-------------------|------------------|-----------------------------------|------------|

| Interrupt Source                                          | External/<br>Internal | Vector        | Macro<br>Service | Bank<br>Switching | Setting<br>Possible | Between<br>Groups | Within<br>Groups | Multiple<br>Processing<br>Control |            |

| NMI<br>Nonmaskable interrupt                              | External              | 2             | No               | No                | No                  | 0                 |                  | Not                               | -          |

| INTTUO<br>Interrupt from timer<br>unit O                  | Internal              | _ 28          | Yes              | Yes               | Yes                 | 1                 | 1 .              | Accepted                          | <b>-</b> . |

| NTTU1<br>nterrupt from timer<br>unit 1                    | Internal              | 29            | Yes              | Yes               | Yes                 | 1                 | 2                |                                   |            |

| NTTU2<br>Interrupt from timer<br>unit 2                   | Internal              | 30            | Yes              | Yes               | Yes                 | 1                 | 3                |                                   |            |

| NTDO<br>Interrupt from DMA<br>channel O                   | Internal              | 20            | No               | Yes               | Yes                 | 2                 | 1                | Accepted                          | <b>_</b>   |

| INTD1<br>Interrupt from DMA<br>channel 1                  | Internal              | 21            | No               | Yes               | Yes                 | 2                 | 2                |                                   |            |

| INTPO<br>Interrupt from<br>peripheral O                   | External              | 24            | Yes              | Yes               | Yes                 | 3                 | 1                | Accepted                          |            |

| NTP1<br>Interrupt from<br>peripheral 1                    | External              | 25            | Yes              | Yes               | Yes                 | 3                 | 2                |                                   |            |

| NTP2<br>nterrupt from<br>peripheral 2                     | External              | 26            | Yes              | Yes               | Yes                 | 3                 | 3                |                                   | 46         |

| NTSER0<br>nterrupt from serial<br>error on channel 0      | Internal              | 12            | No               | Yes               | Yes                 | 4                 | 1                | Accepted                          |            |

| NTSRO<br>Interrupt from serial<br>receiver of channel O   | Internal              | 13            | Yes              | Yes               | Yes                 | 4                 | 2                |                                   |            |

| NTSTO<br>nterrupt from serial<br>transmitter of channel O | Internal              | 14            | Yes              | Yes               | Yes                 | 4                 | 3                |                                   |            |

| NTSER1<br>nterrupt from serial<br>prror on channel 1      | Internal              | 16            | No               | Yes               | Yes                 | 5                 | 1                | Accepted                          | -          |

| NTSR1<br>nterrupt from serial<br>eceiver of channel 1     | Internal              | 17            | Yes              | Yes               | Yes                 | 5                 | 2                |                                   |            |

| NTST1<br>nterrupt from serial<br>ransmitter of channel 1  | Internal              | 18            | Yes              | Yes               | Yes                 | 5                 | 3                |                                   |            |

| NTTB<br>nterrupt from time<br>pase counter                | Internal              | 31            | No               | No                | No<br>(Preset to 7) | 6                 |                  | Accepted                          | -          |

| NT<br>nterrupt                                            | External              | Ext.<br>input | No               | No                | No                  | 7                 | _                | Not<br>accepted                   | -          |

μ**PD70330/332 (V35)**

### Interrupt Processing Modes

Interrupts, with the exception of NMI, INT, and INTTB, have high-performance capability and can be processed in any of three modes: standard vectored interrupt, register bank context switching, or macro service function. The processing mode for a given interrupt can be chosen by enabling the appropriate bits in the corresponding interrupt request control register. As shown in table 6, each individual interrupt, with the exception of INTR and NMI, has its own associated IRC register. The format for all IRC registers is shown in figure 7. There is an IRC for every interrupt source except NHI and INT.

All interrupt processing routines other than those for NMI and INT must end with the execution of an FINT instruction. Otherwise, subsequently, only interrupts of a higher priority will be accepted. FINT allows the internal interrupt controller to begin looking for new interrupts.

In the vectored interrupt mode, the CPU traps to the vector location in the interrupt vector table.

#### **Register Bank Switching**

ЗОЕ **О 🖿** 6427525 0027024 4 I

Register bank context switching allows interrupts to be processed rapidly by switching register banks. After an interrupt, the new register bank selected is that which has the same register bank number (0-7) as the priority of the interrupt to be serviced. The PC and PSW are automatically stored in the save areas of the new register bank and the address of the interrupt routine is loaded from the vector PC storage location in the new register bank. As in the vectored mode, the IE and BRK bits in the PSW are cleared to zero. After interrupt processing, execution of the RETRBI (return from register bank interrupt) returns control to the former register bank and restores the former PC and PSW. Figures 8 and 9 show register bank context switching and register bank return.

T-49-19-16 T-49-19-59

Specific IRC registers include the following.

Symbol **IRC Register** DIC0, DIC1 EXIC0-EXIC2 SEICO, SEIC1 SRICO, SRIC1 STICO, STIC1 TMIC0-TMIC2

DMA External Serial error Serial receive Serial transmit Timer

Figure 7. Interrupt Request Control Registers (IRC)

5 6 3 2 0 IRC MS/ FLAG MASK ENCS 0 PR<sub>2</sub> PR<sub>1</sub> PR<sub>0</sub> 1 0 Priority 0 0 Highest 1 Lowes ENCS Context Switch Vectored Interrupt Mode 0 Bank Switching 1 MS/INT Macro Service or Interrupt 0 Interrupt 1 Macro Service xxMKn Interrupt Mask 0 Mask Open; Interrupts Enabled Mask Closed: Interrupts Disabled 1 xxFn Interrupt Request Flag 0 No Request Interrupt Requested 49-001383E

FC

### μ**PD**70330/332 (V35)

### Figure 8. Register Bank Context Switching

### Macro Service Function

T-49-19-16 T-49-19-59

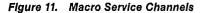

The macro service function (MSF) is a special microprogram that acts as an internal DMA controller between on-chip peripherals (special function registers, SFR) and memory. The MSF greatly reduces the software overhead and CPU time that other processors would require for register save processing, register returns, and other handling associated with interrupt processing.

If the MSF is selected for a particular interrupt, each time the request is received, a byte or word of data will be transferred between the SFR and memory without interrupting the CPU. Each time a request occurs, the macro service counter is decremented. When the counter reaches zero, an interrupt to the CPU is generated. The MSF also has a character search option. When selected, every byte transferred will be compared to an 8-bit search character and an interrupt will be generated if a match occurs or if the macro service counter counts out.

Like the NMI, INT and INTTB, the two DMA controller interrupts (INTD0, INTD1) do not have MSF capability.

Figure 10. Task Switching

### μPD70330/332 (V35)

There are eight 8-byte macro service channels mapped into internal RAM from XXE00H to XXE3FH. Figure 11 shows the components of each channel.

30E

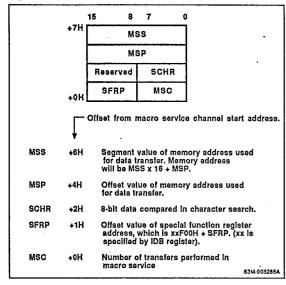

Setting the macro service mode for a given interrupt requires programming the corresponding macro service control register. Each individual interrupt, excluding INTR, NMI and TBC, has its own associated MSC register. See table 6. Format for all MSC registers is shown in figure 12.

#### **On-Chip Peripherals**

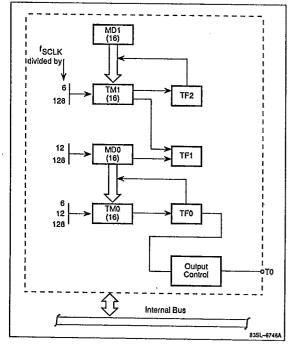

#### **Timer Unit**

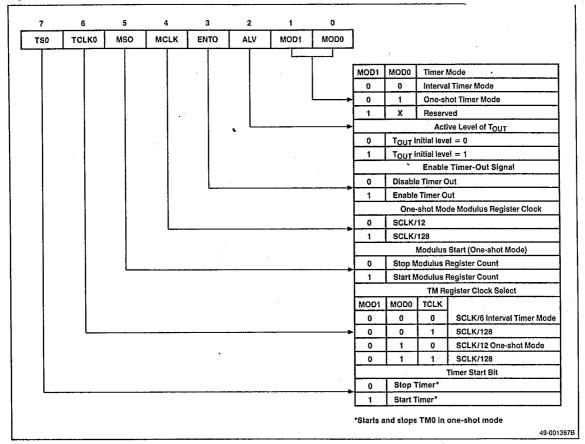

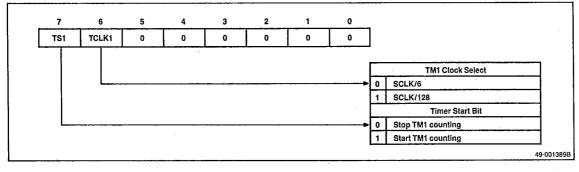

The  $\mu$ PD70330/332 (figure 13) has two programmable 16-bit interval timers (TM0, TM1) on-chip, each with variable input clock frequencies. Each of the two 16-bit timer registers has an associated 16-bit modulus register (MD0, MD1). Timer 0 operates in the interval timer mode or one-shot mode; timer 1 has only the interval timer mode. **Interval Timer Mode.** In this mode, TM0/TM1 are decremented by the selected input clock and, after counting out, the registers are automatically reloaded from the modulus registers and counting continues. Each time TM1 counts out, interrupts are generated through TF1 and TF2 (Timer Flags 1, 2). When TM0 counts out, an interrupt is generated through TF0. The timer-out signal can be used as a square-wave output whose half-cycle is equal to the count time. There are two selectable input clocks (SCLK: system clock =  $f_{OSC}/2$ ;  $f_{OSC} = 10$  MHz).

T-49-19-59

📕 6427525 0027026 8

T-49-19-16

| Clock    | <b>Timer Resolution</b> | Full Count |

|----------|-------------------------|------------|

| SCLK/6   | `1.2 μs                 | 78.643 ms  |

| SCLK/128 | 25.6 <i>µ</i> s         | 1.678 s    |

**One-Shot Mode.** In the one-shot mode, TM0 and MD0 operate as independent one-shot timers. Starting with a preset value, each is decremented to zero. At zero, counting ceases and an interrupt is generated by TF0 (from TM0) or TF1 (from MD0). One-shot mode allows two selectable input clocks ( $f_{OSC} = 10 \text{ MHz}$ ).

| Clock    | Timer Resolution | Full Count |

|----------|------------------|------------|

| SCLK/12  | 2.4 μs           | 157.283 ms |

| SCLK/128 | 25.6 μs          | 1.678 s    |

Setting the desired timer mode requires programming the timer control register. See figures 14 and 15 for format.

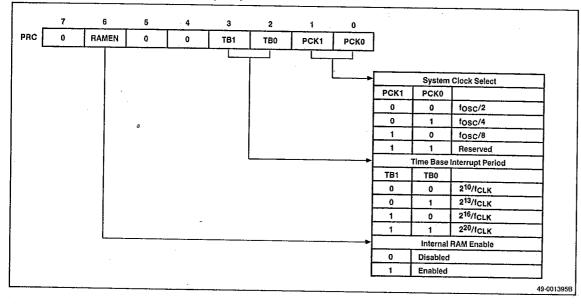

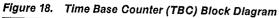

#### Time Base Counter/Processor Control Register

The 20-bit free-running time base counter controls internal timing sequences and is available to the user as the source of periodic interrupts at lengthy intervals. One of four interrupt periods can be selected by programming the TB0 and TB1 bits in the processor control register (PRC). The TBC interrupt is unlike the others in that it is fixed as a level 7 vectored interrupt. Macro service and register bank switching cannot be used to service this interrupt. See figures 16 and 17.

The RAMEN bit in the PRC register allows the internal RAM to be removed from the memory address space to implement faster instruction execution.

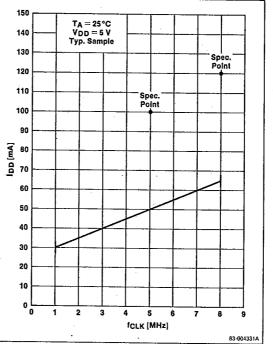

The TBC (figure 18) uses the system clock as the input frequency. The system clock can be changed by programming the PCK0 and PCK1 bits in the processor control register (PRC). Reset initializes the system clock to  $f_{OSC}/8$  ( $f_{OSC}$  = external oscillator frequency).

### ЗОЕ **D** 🖿 6427525 0027027 Т 🔳

### N E C ELECTRONICS INC

### μPD70330/332 (V35)

T-49-19-16

Figure 12. Macro Service Control Registers (MSC)

### Figure 13. Timer Unit Block Diagram

### N E C ELECTRONICS INC 30E D 🖬 6427525 0027028 1 🖿

T-49-19-16

T-49-19-59

Figure 14. Timer Control Register 0

### μ**PD70330/332 (V35)**

#### Figure 16. Time Base Interrupt Request Control Register T-49-19-59 7 6 5 4 3 2 1 Ò TBF твмк 0 0 0 1 t 1 , Time Base Interrupt Mask Bit σ Unmasked Masked 1 Time Base Interrupt Flag 0 No Interrupt Generated 1 Interrupt Generated 49-001393B

• •

30E D

### Figure 17. Processor Control Register (PRC)

🖿 6427525 0027030 T 🛲 30E N

### µPD70330/332 (V35)

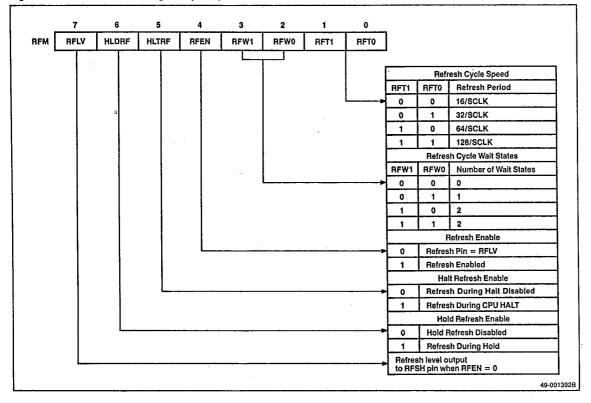

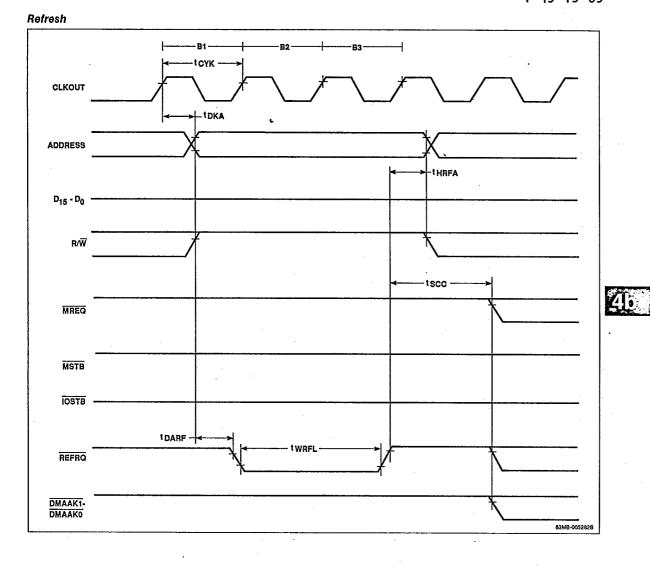

#### **Refresh Controller**

The µPD70330/332 has an on-chip refresh controller for dynamic and pseudostatic RAM mass storage memories. The refresh controller generates refresh addresses and refresh pulses. It inserts refresh cycles between the normal CPU bus cycles according to refresh specifications.

The refresh controller outputs a 9-bit refresh address on address bits A<sub>0</sub>-A<sub>8</sub> during the refresh bus cycle. Address bits A9-A19 are all 1's. The 9-bit refresh address is automatically incremented at every refresh timing for 512 row addresses. The 8-bit refresh mode (RFM) register (figure 19) specifies the refresh operation and allows refresh during both CPU HALT and

Figure 19. Refresh Mode Register (RFM)

T-49-19-59 HOLD modes. Refresh cycles are automatically timed

T-49-19-16

to REFRQ following read/write cycles to minimize the effect on system thoughput.

The following shows the REFRQ pin level in relation to bits 4 (RFEN) and 7 (RFLV) of the refresh mode reaister.

| RFEN | RFLV    | <b>REFRQ</b> Level   |

|------|---------|----------------------|

| 0    | 0       | 0                    |

| 0    | 1       | 1                    |

| 1    | 0       | . 0                  |

| 1    | 1       | Refresh pulse output |

|      | · · · · |                      |

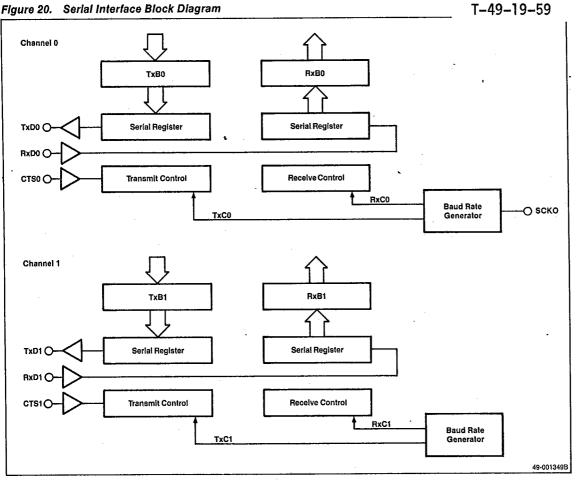

### Serial Interface

The µPD70330/332 has two full-duplex UARTs, channel 0 and channel 1. Each serial port channel has a transmit line (TxDn), a receive line (RxDn), and a clear to send (CTSn) input line for handshaking. Communication is synchronized by a start bit, and you can program the ports for even, odd, or no parity, character lengths of 7 or 8 bits, and 1 or 2 stop bits.

The µPD70330/332 has dedicated baud rate generators for each serial channel. This eliminates the need to obligate the on-chip timers. The baud rate generator allows a wide range of data transfer rates (up to 1.25 Mb/s). This includes all of the standard baud rates without being restricted by the value of the particular external crystal.

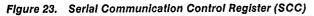

Each baud rate generator has an 8-bit baud rate generator (BRGn) data register, which functions as a prescaler to a programmable input clock selected by the serial communication control (SCCn) register. Together these must be set to generate a frequency equivalent to the desired baud rate.

The baud rate generator can be set to obtain the desired transmission rate according to the following formula:

$$B \times G = \frac{SCLK \times 10^6}{2^{n+1}}$$

where B = baud rate

- G = baud rate generator register (BRGn) value

- n = input clock specifications (n between 0 and 8). This is the value that is loaded into the SCCn register. See figure 23. SCLK = system clock frequency (MHz)

Based on the above expression, the following table shows the baud rate generator values used to obtain standard transmission rates when SCLK = 5 MHz.

### μPD70330/332 (V35) T-49-19-16

T-49-19-59

| Baud Rate | n | BRGn Value | Error (%) |

|-----------|---|------------|-----------|

| 110       | 7 | 178        | 0.25      |

| 150       | 7 | 130        | 0.16      |

| 300       | 6 | 130        | 0.16      |

| 600       | 5 | 130        | 0.16      |

| 1200      | 4 | 130        | 0.16      |

| 2400      | 3 | 130        | 0.16      |

| 4800      | 2 | 130        | 0.16      |

| 9600      | 1 | 130        | 0.16      |

| 19,200    | 0 | , 130      | 0.16      |

| 38,400    | 0 | 65         | 0.16      |

| 1.25M     | 0 | 2          | 0         |

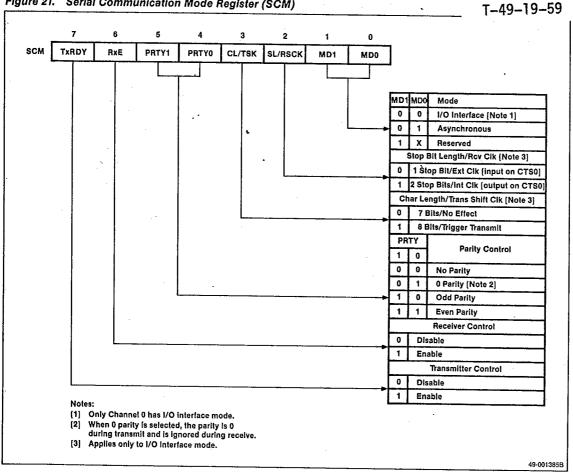

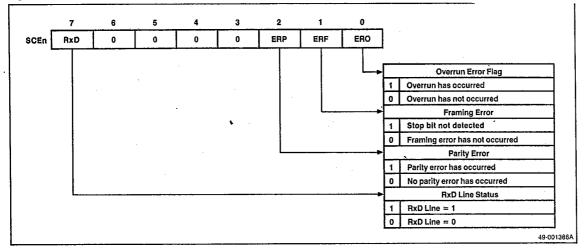

In addition to the asynchronous mode, channel 0 has a synchronous I/O interface mode. In this mode, each bit of data tranferred is synchronized to a serial clock (SCKO). This is the same as the NEC  $\mu$ COM75 and µCOM87 series, and allows easy interfacing to these devices. Figure 20 is the serial interface block diagram; figures 21, 22, and 23 show the three serial communication registers.

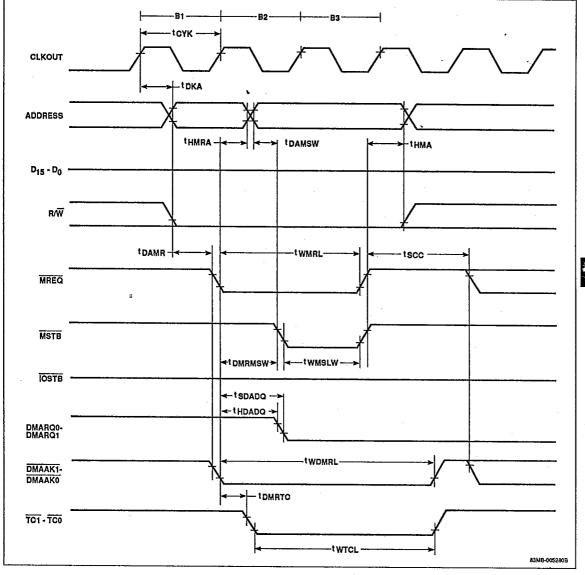

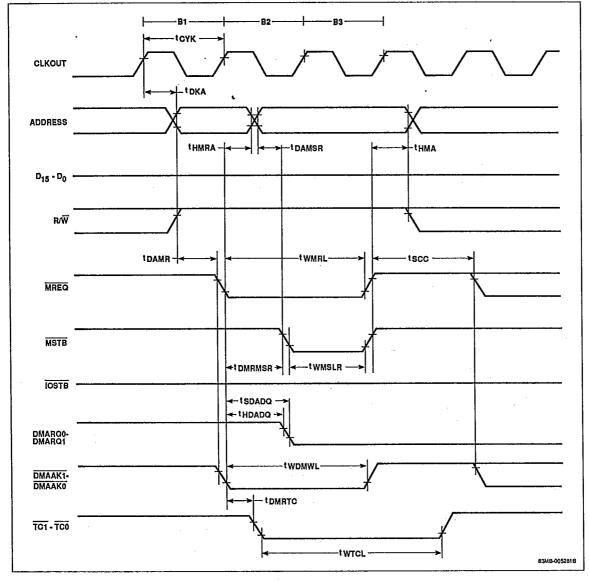

#### **DMA Controller**

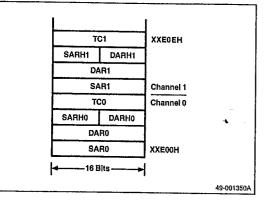

The µPD70330/332 has a two-channel, on-chip DMA controller. This allows rapid data transfer between memory and auxiliary storage devices. The DMA controller supports four modes of operation, two for memory-to-memory transfers and two for transfers between I/O and memory. See figures 24, 25, and 26 for a graphic representation of the DMA registers.

30É Ď 🛲 6427525 0027032 3 🛲

IEC

T-49-19-16

1

### μ**PD70330/332 (V35)**

Figure 20. Serial Interface Block Diagram

### μ**PD70330/332 (V35)**

T-49-19-16

Figure 21. Serial Communication Mode Register (SCM)

μ**PD7**0330/332 (V35)

Figure 22. Serial Communication Error Registers (SCE)

30E D = 6427525 0027034 7 =

T-49-19-16 T-49-19-59

зов Ď 🖿 6427525 оо27035 9 🖿

# NEC

### μ**PD70330/332 (V35)**

T-49-19-16 T-49-19-59

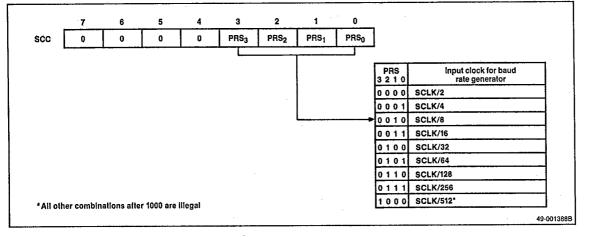

### Figure 24. DMA Channels

### Figure 25. DMA Mode Registers (DMAM)

4b

μ**PD70330/332 (V35)**

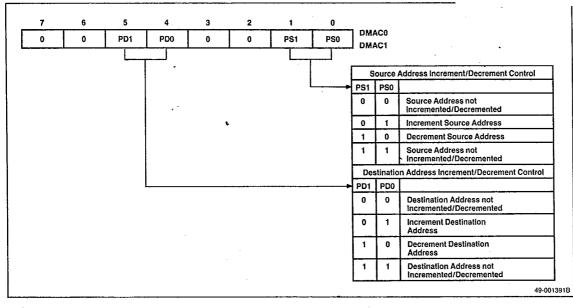

#### Figure 26. DMA Control Registers (DMAC)

30E N

Memory-to-Memory Transfers. In the single-step mode, when one DMA request is made, execution of one instruction and one DMA transfer are repeated alternately until the prescribed number of DMA transfers has occurred. Interrupts can be accepted while in this mode. In burst mode, a DMA request causes DMA transfer cycles to continue until the DMA terminal counter decrements to zero. Software can also initiate memory-to-memory transfers.

Transfers Between I/O and Memory. In single-transfer mode, one DMA transfer occurs after each rising edge of DMARQ. After the transfer, the bus is returned to the CPU. In demand release mode, the rising edge of DMARQ enables DMA cycles, which continue as long as DMARQ is high.

In all modes, the  $\overline{TC}$  (terminal count) output pin will pulse low and a DMA completion I/O request will be generated after the predetermined number of DMA cycles has been completed.

The bottom of internal RAM contains all the necessary address information for the designated DMA channels. The DMA channel mnemonics are as follows:

| тс   | Terminal counter                  |

|------|-----------------------------------|

| SAR  | Source address register           |

| SARH | Source address register high      |

| DAR  | Destination address register      |

| DARH | Destination address register high |

|      |                                   |

The DMA controller generates physical source addresses by offsetting SARH 12 bits to the left and then adding the SAR. The same procedure is also used to generate physical destination addresses. You can program the controller to increment or decrement source and/or destination addresses independently during DMA transfers.

🛛 🛲 6427525 0027036 0 📖

T-49-19-16

T-49-19-59

When the EDMA bit is set, the internal DMARQ flag is cleared. Therefore, DMARQs are only recognized after the EDMA bit has been set.

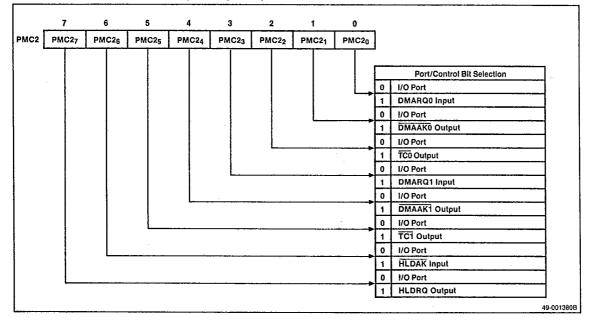

#### Parallel Ports

The  $\mu$ PD70330/332 has three 8-bit parallel I/O ports: P0, P1, and P2. Refer to figures 27 through 31. Special function register (SFR) locations can access these ports. The port lines are individually programmable as inputs or outputs. Many of the port lines have dual functions as port or control lines.

Use the associated port mode and port mode control registers to select the mode for a given I/O line.

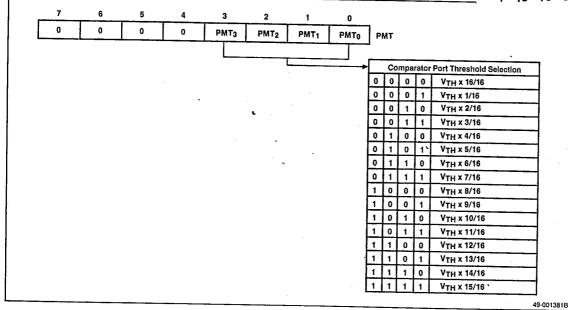

The analog comparator port (PT) compares each input line to a reference voltage. The reference voltage is programmable to be the  $V_{TH}$  input x n/16, where n = 1 to 16. See figure 32.

зое 🔘 🗰 6427525 оо27037 2 🖿

T-49-19-16

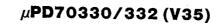

### Figure 27. Port Mode Registers 0 and 2 (PM0, PM2)

### Figure 28. Port Mode Register 1 (PM1)

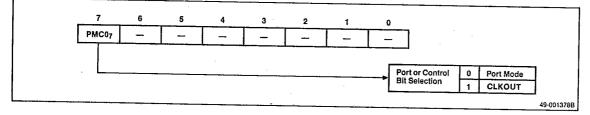

Figure 29. Port Mode Control Register 0 (PMC0)

30E D = 6427525 0027038 4 =

T-49-19-16

T-49-19-59

μ**PD7**0330/332 (V35)

Figure 30. Port Mode Control Register 1 (PMC1)

|   | 7    | 6     | 5     | 4     | 3     | 2     | 1     | 0     |   |                            |

|---|------|-------|-------|-------|-------|-------|-------|-------|---|----------------------------|

| F | MC17 | PMC16 | PMC15 | PMC14 | PMC13 | PMC12 | PMC11 | PMC10 |   |                            |

|   |      |       |       |       |       |       |       |       |   |                            |

|   |      |       |       |       |       |       |       |       |   | Port/Control Bit Selection |

|   |      |       |       |       |       |       |       | └→    | X | NMI/P10 Input              |

|   |      |       | 1     |       |       |       | ·     | >     | X | INTP0/P11 Input            |

|   |      |       |       |       |       | L     |       |       | X | INTP1/P12 Input            |

|   |      |       |       |       | •     |       |       |       | 0 | INTP2/P13 Input            |

|   |      |       |       |       |       |       |       |       | 1 | INTAK Output               |

|   |      |       |       |       |       |       |       |       | 0 | P14 I/O or POLL Input      |

|   |      |       |       |       |       |       |       |       | 1 | INT Input                  |

|   |      |       |       |       |       |       |       |       | 0 | P151/O                     |

|   |      |       |       |       |       |       | •     |       | 1 | TOUT Output                |

|   |      |       |       |       |       |       |       |       | 0 | P1 <sub>6</sub> I/O        |

|   |      |       |       |       |       |       |       |       | 1 | SCKO Output                |

|   |      |       |       |       |       |       |       |       | 0 | P17 I/O                    |

|   |      |       |       |       |       |       |       |       | 1 | READY Input                |

|   |      |       |       |       |       |       |       |       |   | 49.0                       |

### Figure 31. Port Mode Control Register 2 (PMC2)

### μ**PD70330/332 (V35**)

T-49-19-16

Figure 32. Port Mode Register T (PMT)

T-49-19-59

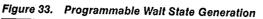

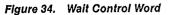

### Programmable Wait State Generation

You can generate wait states internally to further reduce the necessity for external hardware. Insertion of these wait states allows direct interface to devices whose access times cannot meet the CPU read/write timing requirements.

When using this function, the entire 1M-byte memory address space is divided into 128K-blocks. Each block can be programmed for zero, one, or two wait states, or two plus those added by the extenal READY signal. The top two blocks are programmed together as one unit.

The appropriate bits in the wait control word (WTC) control wait state generation. Programming the upper two bits in the wait control word will set the wait state conditions for the entire I/O address space. Figure 33 shows the memory map for programmable wait state generation; see figure 34 for a graphic representation of the wait control word.

30E D 🖬 6427525 0027040 2 1

.

### μ**PD7**0330/332 (V35)

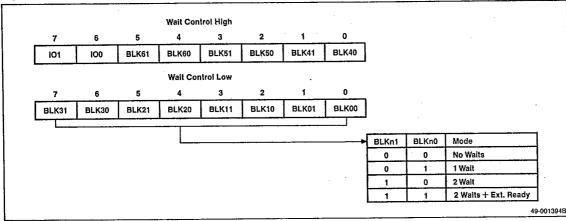

### Standby Modes

The two low-power standby modes are HALT and STOP. Software causes the processor to enter either mode.

### HALT Mode.

In the HALT mode, the processor is inactive and the chip consumes much less power than when operational. The external oscillator remains functional and all peripherals are active. Internal status and output port line conditions are maintained. Any unmasked interrupt can release this mode. In the El state, interrupts subsequently will be processed in vector mode. In the DI state, program execution is restarted with the instruction following the HALT instruction.

#### STOP Mode.

The STOP mode allows the largest power reduction while maintaining RAM. The oscillator is stopped,

T-49-19-16 T-49-19-59

halting all internal peripherals. Internal status is maintained. Only a reset or NMI can release this mode.

A standby flag in the SFR area is reset by rises in the supply voltage. Its status is maintained during normal operation and standby. The STBC register (figure 35) is not initialized by RESET. Use the standby flag to determine whether program execution is returning from standby or from a cold start by setting this flag before entering the STOP mode.

### **Special Function Registers**

Table 6 shows the special function register mnemonic, type, address, reset value, and function. The 8 highorder bits of each address (xx) are specified by the IDB register.

SFR area addresses not listed in table 6 are reserved. If read, the contents of these addresses are undefined, and any write operation will be meaningless.

Figure 35. Standby Register

### μ**PD70330/332 (V35)**

### Table 6. Special-Function Registers

### T-49-19-16

T-49-19-59

| Table 6. | Special-Function Registers                  |        | -   |                    | [-49-19-     | 59 |

|----------|---------------------------------------------|--------|-----|--------------------|--------------|----|

| Address  | Register Function                           | Symbol | R/W | Manipulation (Bit) | When RESET   | •  |

| xxF00H   | Port 0                                      | PO     | B/W | 8/1                | Undefined    |    |

| xxF01H   | Port mode 0                                 | PMO    | W   | . 8                | FFH          |    |

| xxF02H   | Port mode control 0                         | PMCO   | W   | 8                  | 00H          |    |

| XXF08H   | Port 1                                      | P1     | R/W | 8/1                | Undefined    |    |

| xxF09H   | Port mode 1                                 | PM1    | W   | 8                  | FFH          |    |

| xxF0AH   | Port mode control 1                         | PMC1   | W   |                    | 00H          |    |

| xxF10H   | Port 2                                      | P2     | R/W | 8/1                | Undefined    |    |

| xxF11H   | Port mode 2                                 | PM2    | W   | 8                  | FFH          |    |

| xxF12H   | Port mode control 2                         | PMC2   | W   | × 8                |              |    |

| xxF38H   | Port T                                      | PT     | R   | 8                  | Undefined    |    |

| xxF3BH   | Port mode T                                 | РМТ    | R/W | 8/1                | 00H          |    |

| XXF40H   | External interrupt mode                     | INTM   | R/W | 8/1                | 00H          |    |

| xxF44H   | External interrupt macro service control 0  | EMS0   | R/W | 8/1                | Undefined    |    |

| xxF45H   | External interrupt macro service control 1  | EMS1   | R/W | 8/1                | -            |    |

| xxF46    | External interrupt macro service control 2  | EMS2   | R/W | 8/1                | -            |    |

| xxF4CH   | External interrupt request control 0        | EXIC0  | R/W | 8/1                | 47H          |    |

| XXF4DH   | External interrupt request control 1        | EXIC1  | R/W | 8/1                | -            | _  |

| xxF4EH   | External interrupt request control 2        | EXIC2  | R/W | 8/1                | -            | 14 |