# CDP68HC05C4B, CDP68HC05C8B, CDP68HCL05C4B, CDP68HCL05C8B, CDP68HSC05C4B, CDP68HSC05C8B

March 1998

# 8-Bit Enhanced Microcontroller Series

### Features

#### **HARDWARE**

- 8-Bit HCMOS Microcontroller

- Extended Version of MC68HC05C4A/C8A Family

- Pin for Pin Compatible

- Power-Saving Stop, Wait and Data Retention Modes

- STOP Instruction can be Disabled via Mask Option

- · Fully Static Operation

- · On-Chip Memory

- CDP68HC05C4B, 68HCL05C4B, 68HSC05C4B

- 176 Bytes RAM, 4160 Bytes ROM

- CDP68HC05C8B, 68HCL05C8B, 68HSC05C8B

- 176 Bytes RAM, 7744 Bytes ROM

- · Keyboard Scanning Logic

- Watchdog Timer (COP)

- · 24 Bidirectional I/O Lines and 7 Input-Only Lines

- 1 High Current Output for LED drive (PC7)

- · Internal 16-Bit Timer

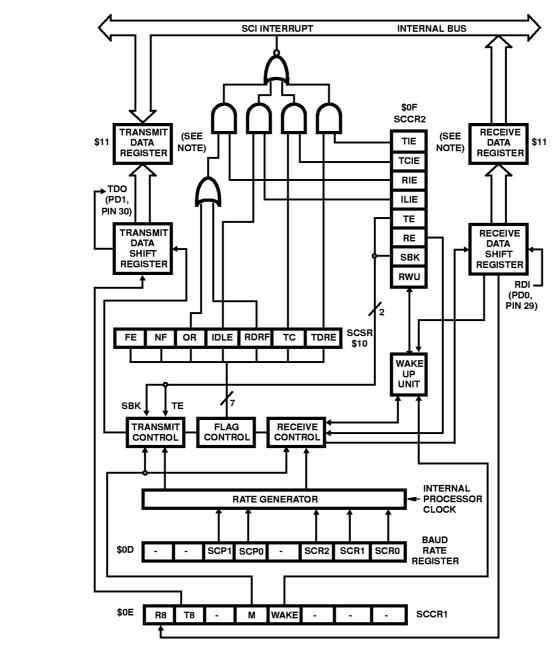

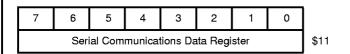

- · Serial Communications Interface (SCI) System

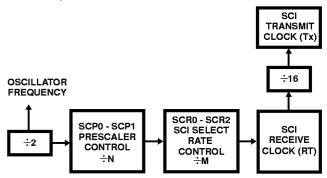

- · Serial Peripheral Interface (SPI) System

- Fixed Frequency Tone/Simple PWM Outputs (Mask Programmable)

- Self-Check Mode

- · External, Timer, SCI, and SPI Interrupts

- · Master Reset and Power-On Reset

- · On-Chip Oscillator with RC or Crystal Mask Options

- CDP68HC05C4B, CDP68HC05C8B

- 4.2MHz Oscillator (2.1MHz Internal Bus Frequency) at 5V; 2.0MHz (1.0MHz Internal Bus) at 3.0V

- Single 3.0V to 6.0V Supply (1.2V Data Retention Mode)

- CDP68HCL05C4B, CDP68HCL05C8B

- Lower Supply Current, I<sub>DD</sub> in RUN, WAIT and STOP Modes at 5.5V, 2.5V and 1.8V

- Single 1.8V to 6.0V Supply (1.2V Data Retention Mode)

- CDP68HSC05C4B, CDP68HSC05C8B

- 8.0MHz Oscillator (4.0MHz Internal Bus Frequency)

- Single 2.4V to 6.0V Supply (1.2V Data Retention Mode)

#### **SOFTWARE**

- · Complete 68HC05 Instruction Set

- · Efficient Use of Program Space

- Memory Mapped I/O

- · Versatile Interrupt Handling

- · True Bit Manipulation

- Addressing Modes with Indexed Addressing for Accessing Tables

# Description

The CDP68HC05C4B HCMOS Microcomputer is a new member of the CDP68HC05 family of low-cost single chip microcomputers. It is an enhanced version of the CDP68HC05C4. The enhancements include keyboard scanning logic, a high current output pin, a watchdog timer, fixed tone outputs, and a maskable STOP instruction. This 8-bit microcomputer unit (MCU) also contains an on-chip oscillator, CPU, 176 bytes of RAM, 4160 bytes of user ROM in the CDP68HC05C4B and 7744 bytes of user ROM in the CDP68HC05C8B, I/O, two serial interface systems, and timer. The fully static design allows operation at frequencies down to DC, further reducing its already low-power consumption. All information pertaining CDP68HC05C4B MCU applies to the CDP68HC05C8B with the exception of the memory description.

The CDP68HCL05C4B and CDP68HCL05C8B MCU devices are low-power versions of the CDP68HC05C4B and CDP68HC05C4B, respectively. They contain all the features of the CDP68HC05C4B and CDP68HC05C8B with additional features of lower power consumption in the RUN, WAIT and STOP modes; and low voltage operation down to 2.4V. The CDP68HSC05C4B and CDP68HSC05C8B MCU devices are high-speed versions of the CDP68HC05C4B and CDP68HC05C4B and CDP68HC05C4B, respectively. They also contain all the features of the CDP68HC05C4B and CDP68HC05C8B with the and have a higher frequency operation (up to 8.0MHz).

#### Table of Contents

| Ordering Information                               | 2  |

|----------------------------------------------------|----|

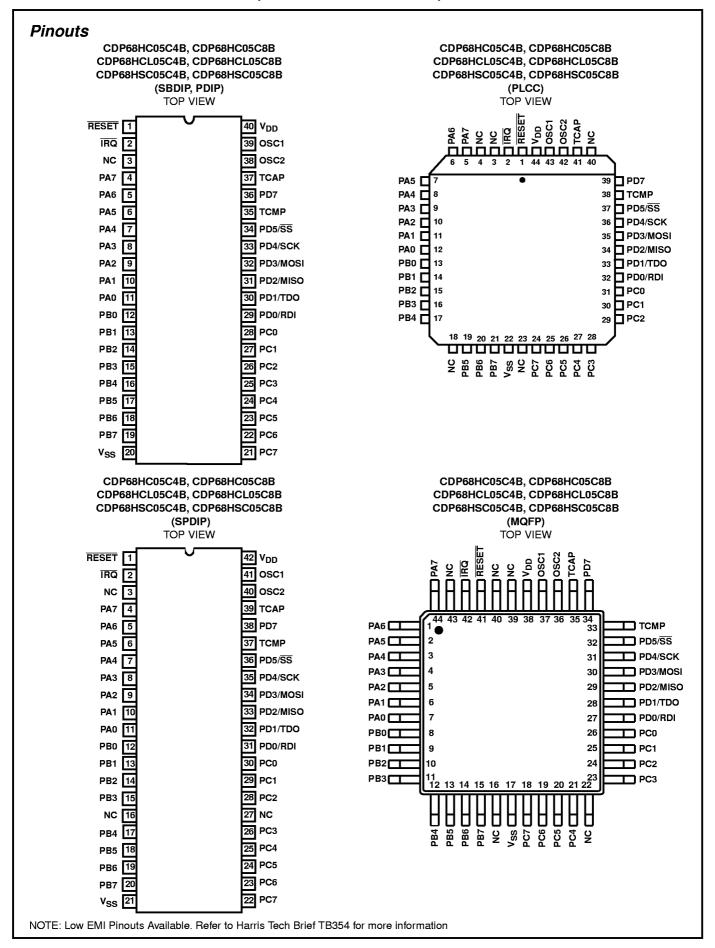

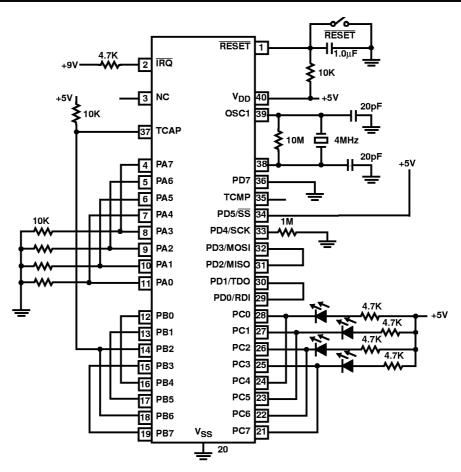

| Pinouts                                            | 3  |

| MCU Block Diagram                                  | 4  |

| Characterization Curves                            | 5  |

| Electrical and Timing Specifications               | 6  |

| Functional Pin Description                         | 23 |

| Input/Output Programming                           |    |

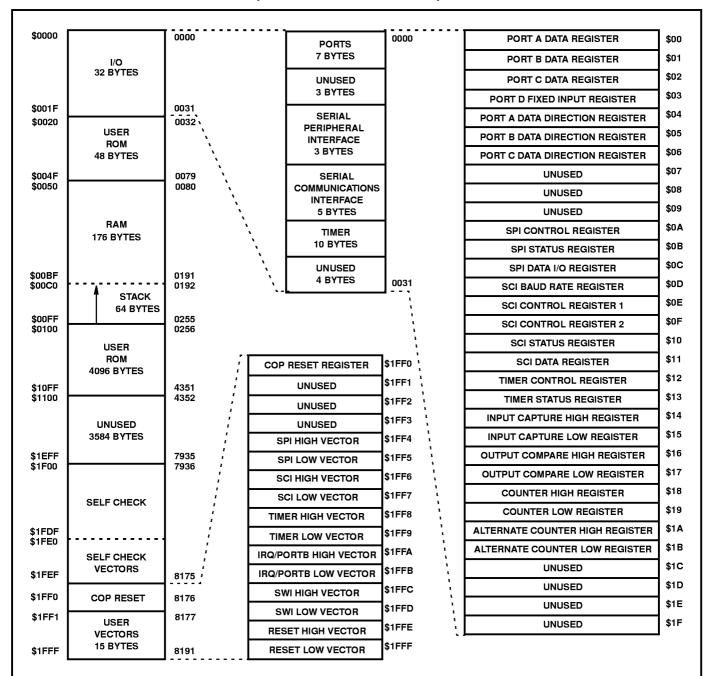

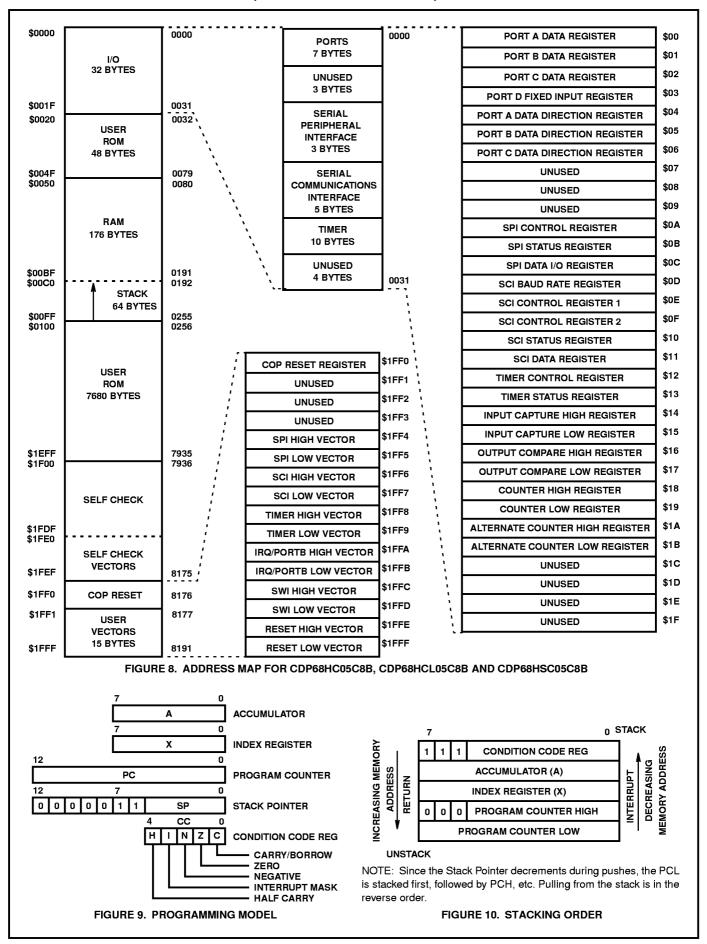

| Memory Maps                                        | 27 |

| Memory                                             | 27 |

| Self Check Mode                                    |    |

| Resets, Interrupts and Low Power Modes             | 30 |

| Hardware/Power-On Resets                           | 30 |

| COP Watchdog System                                | 30 |

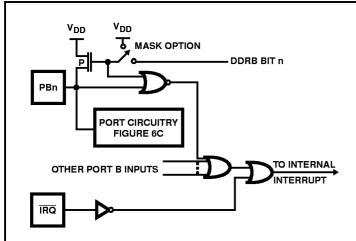

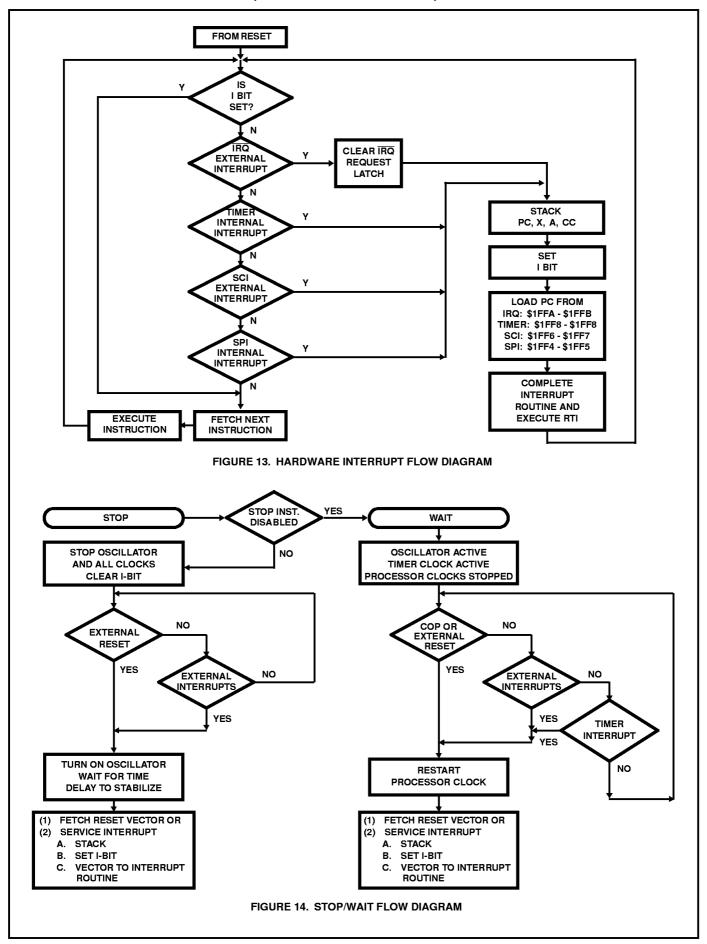

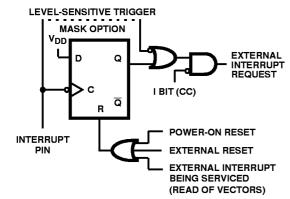

| Interrupts                                         | 31 |

| Low Power Modes                                    | 34 |

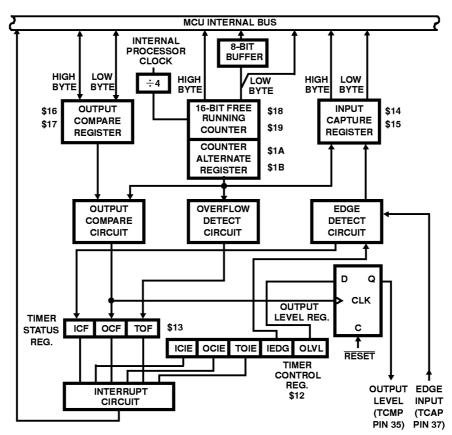

| Programmable Timer                                 | 35 |

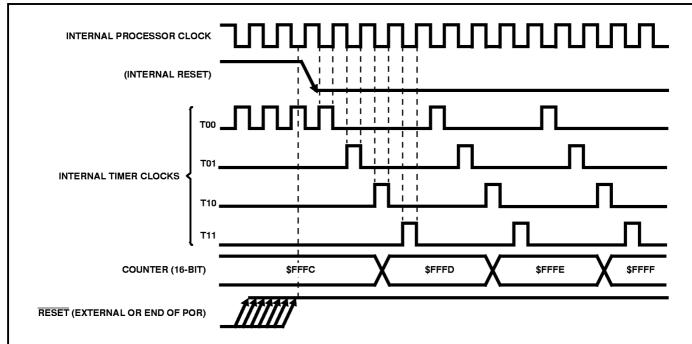

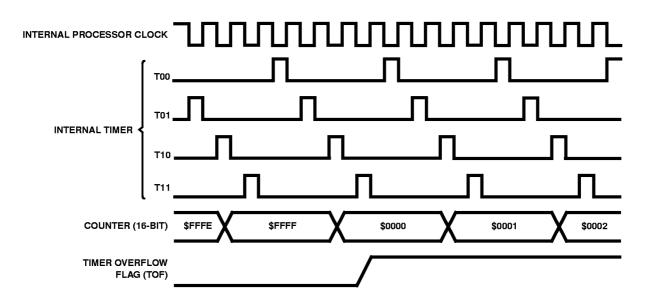

| Counter                                            | 38 |

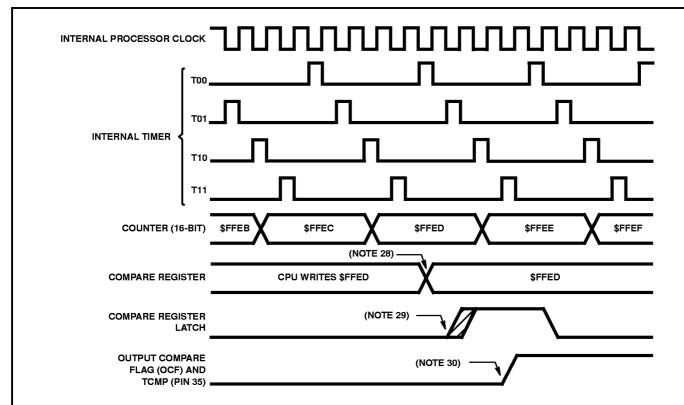

| Output Compare                                     | 38 |

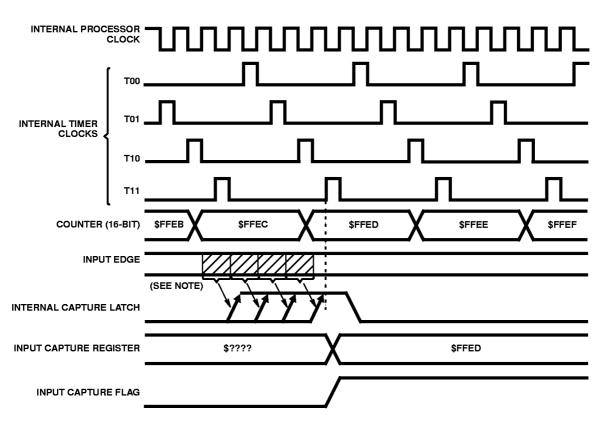

| Input Capture                                      | 38 |

| Serial Communications Interface (SCI)              | 40 |

| Serial Peripheral Interface (SPI)                  |    |

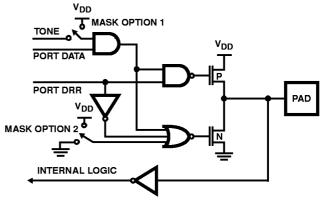

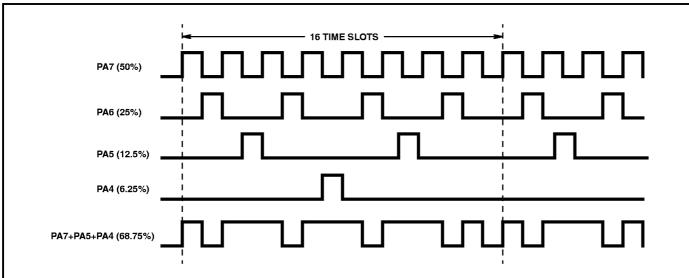

| Port A Tone and Simple PWM Circuitry               | 52 |

| Effects of STOP and WAIT modes                     | 53 |

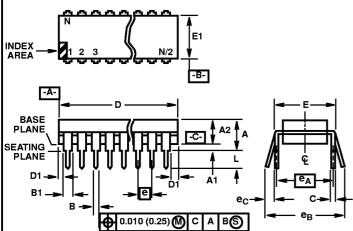

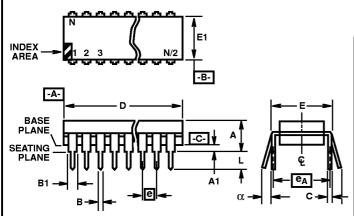

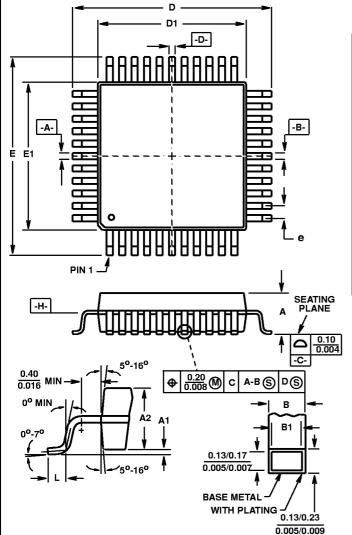

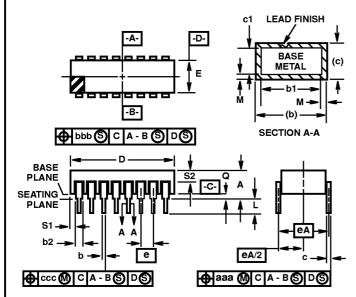

| Package Outline Dimensions                         | 54 |

| Opcode Map                                         |    |

| I/O, Control, Status and Data Register Definitions | 61 |

| Ordering Information Sheet                         | 62 |

|                                                    |    |

# Ordering Information

| PART NUMBER     | PACKAGE     | PKG. NO.  |

|-----------------|-------------|-----------|

| CDP68HC05C4BE   | 40 Ld PDIP  | E40.6     |

| CDP68HC05C4BN   | 44 Ld PLCC  | N44.65    |

| CDP68HC05C4BQ   | 44 Ld MQFP  | Q44.10x10 |

| CDP68HC05C4BSE  | 42 Ld SPDIP | E42.6C    |

| CDP68HC05C4BD   | 40 Ld SBDIP | D40.6     |

| CDP68HC05C4BH   | Chip        |           |

| CDP68HCL05C4BE  | 40 Ld PDIP  | E40.6     |

| CDP68HCL05C4BN  | 44 Ld PLCC  | N44.65    |

| CDP68HCL05C4BQ  | 44 Ld MQFP  | Q44.10x10 |

| CDP68HCL05C4BSE | 42 Ld SPDIP | E42.6C    |

| CDP68HCL05C4BD  | 40 Ld SBDIP | D40.6     |

| CDP68HCL05C4BH  | Chip        |           |

| CDP68HSC05C4BE  | 40 Ld PDIP  | E40.6     |

| CDP68HSC05C4BN  | 44 Ld PLCC  | N44.65    |

| CDP68HSC05C4BQ  | 44 Ld MQFP  | Q44.10x10 |

| CDP68HSC05C4BSE | 42 Ld SPDIP | E42.6C    |

| CDP68HSC05C4BD  | 40 Ld SBDIP | D40.6     |

| CDP68HSC05C4BH  | Chip        |           |

NOTE: Pin number references throughout this specification refer to the 40 lead DIP. See pinouts for cross reference.

# **ROM Ordering Information**

The CDP68HC05C4B and CDP68HC05C8B families of microcontrollers contain mask programmed ROMs. The contents of these ROMs are personalized to meet a customer's code requirements during manufacturing of the ICs. The code is programmed via photomasking techniques. Semiconductor manufacturing is a batch process, and all microcontrollers manufactured in a given lot (a batch) will contain identical ROM code.

Harris generates a customer's ROM mask from an ASCII representation of the desired ROM contents together with other specific information. The end of this document contains a sheet which can be used to provide the required information when ordering a masked ROM microcontroller.

#### **Data Format Options**

The ROM data can be submitted in various formats. The following list summarizes the principal formats which Harris will accept. The list is in order of preference, with S-Record formatted data files being the preferred format.

- S-Record Formatted Hex Data File via modem upload

- · S-Record Formatted Hex Data File via e-mail

- · S-Record Formatted Hex Data File on floppy disk

- 6805 Assembly Language Source File on floppy disk

- Contents of a 27XX type EPROM/EEPROM

Regardless of the medium used to transfer the data, contents of all of the User ROM regions of the memory map of the particular microcontroller should be specified. This includes any Page 0 User ROM and User Reset/Interrupt Vectors. Data should not be specified for the Self Check ROM space of a device. All unused locations should either not be specified (S-Record and source files) or specified as \$00 (EPROM/EEPROM). Any unspecified locations will be filled with \$00 by Harris.

### **Procedure for Submitting Data**

When submitting data via a physical medium such as a floppy disk or EPROM, the "Ordering Information Sheet" at the end of this document must be completed and submitted with the data.

When utilizing the Harris Customer Pattern Retrieval System (modem upload) the customer will be prompted for the same information as that specified on the "Ordering Information Sheet"

If the data is submitted via e-mail, the message should include the same information as that specified on the "Ordering Information Sheet".

### Harris Customer Pattern Retrieval System

To access the Harris Customer Pattern Retrieval System, you must first obtain an account ID and password from your Harris sales representative. The system is accessed by dialing 1-908-685-6541. It is presently set to run with baud rates up to 2400 baud, with 8 data bits, 1 stop bit, and no parity bit. The data transfer is done using text mode Kermit transfers.

Check the Harris Corporate internet site, www.harris.com, for the latest information on the Harris Customer Pattern Retrieval System.

#### Microcomputer Block Diagram OSC1 OSC2 39 **†** 38 **OSCILLATOR** 16 BIT WATCHDOG 37 TIMER SYSTEM ÷2 INTERNAL 1 RESET PROCESSOR TONE GEN CLOCK 2 IRQ **BAUD RATE** PORT A DIRECTION PORT A DATA REG A TONE OPT GENERATOR **ACCUMULATOR** - PD7 PORT D PORT A CPU 29 CONTROL I/O INDEX - RDI (PD0) **SCI SYSTEM** 30 31 → TDO (PD1) LINES REGISTER PORT → MISO (PD2) **CONDITION CODE** 32 33 MOSI (PD3) REGISTER **SPI SYSTEM** CPU 33 34 SCK (PD4) STACK - SS (PD5) PB0 ◀ POINTER 13 INTERRUPT B DATA REG B DIRECTION PROGRAM COUNTER 14 27 PC0 PB2 ◀ HIGH ALU PORT B ► PC1 16 **PROGRAM →** PC2 LINES 17 PCI **COUNTER LOW** 25 PORT C DATA **PORT** 18 늍 24 I/O DIR С LINES 19 REG REG 23 22 PC5 4160 x 8 ROM 176 x 8 (NOTE) ► PC6 21 STATIC RAM 240 x 8 SELF-CHECK ROM

NOTE: 7744 Bytes of ROM for: CDP68HC05C8B, CDP68HCL05C8B, CDP68HSC05C8B

### **Power Considerations**

The average chip-junction temperature,  $T_{J}$ , in  ${}^{o}C$  can be obtained from:

$$T_{J} = T_{A} + (P_{D} \cdot \theta_{JA}) \tag{EQ. 1}$$

Where: T<sub>A</sub> = Ambient Temperature, <sup>o</sup>C

$\theta_{JA}$  = Package Thermal Resistance, Junction-to-Ambient,  ${}^{o}C/W$

$P_D = P_{INT} + P_{I/O}$

$P_{INT} = I_{CC} \times V_{CC}$ , Watts - Chip Internal Power

$P_{I/O}$  = Power Dissipation on Input and Output

Pins - User Determined

For most applications  $P_{I/O} << P_{INT}$  and can be neglected.

An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:

$$P_D = K \div (T_{.1} + 273^{\circ}C)$$

(EQ. 2)

Solving Equation 1 and Equation 2 for K gives:

$$K = P_D \cdot (T_A + 273^{\circ}C) + \theta_{JA} \cdot P_D 2$$

(EQ. 3)

Where K is a constant pertaining to the particular part. K can be determined from Equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K the values of  $P_D$  and  $T_J$  can be obtained by solving Equation 1 and Equation 2 iteratively for any value of  $T_A$ .

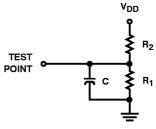

| PINS                     | R1      | R2     | С     |

|--------------------------|---------|--------|-------|

| V <sub>DD</sub> = 4.5V   |         |        |       |

| PA0-7, PB0-7, PC0-7, PD6 | 3.26kΩ  | 2.38kΩ | 50pF  |

| PD1-4                    | 1.9kΩ   | 2.26kΩ | 200pF |

| V <sub>DD</sub> = 3.0V   |         |        |       |

| PA0-7, PB0-7, PC0-7, PD6 | 10.19kΩ | 6.32kΩ | 50pF  |

| PD1-4                    | 6kΩ     | 6kΩ    | 200pF |

**EQUIVALENT TEST LOAD**

HIGH CURRENT OUTPUT N-CHANNEL 120.0  $V_{DD} = 5.0V$ 100.0  $V_{DD} = 4.5V$ **₹** 80.0 SINK CURRENT 60.0  $V_{DD} = 3.3V$ 40.0  $V_{DD} = 2.0V$ 20.0 ٩ 0 1.0 2.0 3.0 6.0 7.0 4.0 5.0 VO, OUTPUT VOLTAGE (V)

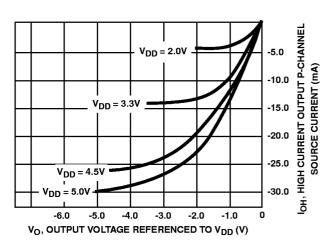

FIGURE 1A. TYPICAL PC7 PORT OUTPUT P-CHANNEL SOURCE CURRENT FOR  $\rm V_{DD}$  = 2V, 3.3V, 4.5V AND 5V AT 25°C

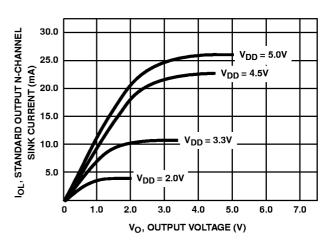

FIGURE 1B. TYPICAL PC7 PORT OUTPUT N-CHANNEL SINK CURRENT FOR  $V_{DD}$  = 2V, 3.3V, 4.5V AND 5V AT 25°C

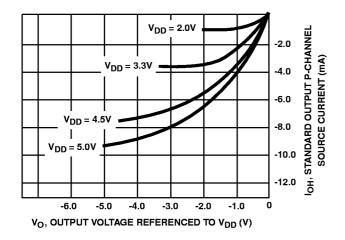

FIGURE 1C. TYPICAL PORT OUTPUT P-CHANNEL SOURCE CURRENT FOR  $V_{DD}$  = 2V, 3.3V, 4.5V AND 5V AT 25°C

FIGURE 1D. TYPICAL PORT OUTPUT N-CHANNEL SINK CURRENT FOR  $V_{DD}$  = 2V, 3.3V, 4.5V AND 5V AT 25°C

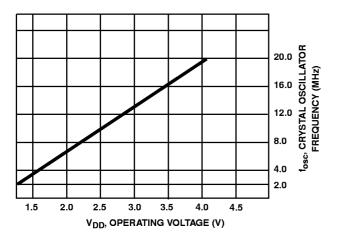

FIGURE 1E. TYPICAL CRYSTAL OSCILLATOR OPERATING FREQUENCIES vs OPERATING VOLTAGE,  $V_{DD}$  AT  $25^{\circ}\mathrm{C}$

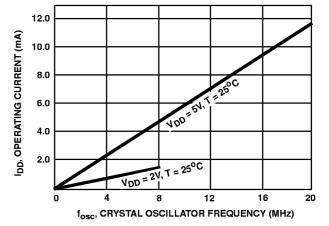

FIGURE 1F. TYPICAL SUPPLY CURRENT VS

OPERATING FREQUENCY AT 25°C

# **Absolute Maximum Ratings**

#

### **Operating Conditions**

| Operating Voltage Range     | +4.5V to +5.5V                               |

|-----------------------------|----------------------------------------------|

| Operating Temperature Range | 55 <sup>o</sup> C to 125 <sup>o</sup> C      |

| CDP68HC05C4B, CDP68HC05     | 5C8B40 <sup>o</sup> C to 85 <sup>o</sup> C   |

| CDP68HCL05C4B, CDP68HCL     | .05C8B                                       |

| CDP68HSC05C4B, CDP68HSC     | C05C8B40 <sup>o</sup> C to 85 <sup>o</sup> C |

| Input Low Voltage           |                                              |

|                             |                                              |

### **Thermal Information**

| Thermal Resistance (Typical, Note 1)                                 | θ <sub>JA</sub> ( <sup>o</sup> C/W) | θ <sub>JC</sub> (°C/W)  |

|----------------------------------------------------------------------|-------------------------------------|-------------------------|

| SPDIP Package                                                        | 55                                  | N/A                     |

| PDIP Package                                                         | 55                                  | N/A                     |

| PLCC Package                                                         | 45                                  | N/A                     |

| MQFP Package                                                         | 70                                  | N/A                     |

| SBDIP Package                                                        | 45                                  | 14                      |

| Maximum Junction Temperature (Hermetic I                             | Package)                            | 175 <sup>0</sup> C      |

| Maximum Junction Temperature (Plastic P                              | ackage)                             | 150 <sup>o</sup> C      |

| Maximum Storage Temperature Range                                    | 65                                  | o <sup>C</sup> to 150°C |

| Maximum Lead Temperature (Soldering 10 (PLCC, MQFP - Lead Tips Only) |                                     |                         |

|                                                                      |                                     |                         |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

# DC Electrical Specifications HC Product Type, V<sub>DD</sub> = 5.0V

| PARAMETER                                                                       | SYMBOL                 | CONDITIONS                                   | MIN                   | TYP | MAX                 | UNITS |

|---------------------------------------------------------------------------------|------------------------|----------------------------------------------|-----------------------|-----|---------------------|-------|

| CDP68HC05C4B/C8B V <sub>DD</sub> = 5V ±10%, V <sub>SS</sub> = 0                 | $V, T_A = -40^{\circ}$ | C to 85 <sup>o</sup> C (Note 2)              | •                     |     | 1                   |       |

| Output Voltage                                                                  | V <sub>OL</sub>        | I <sub>LOAD</sub> < 10μΑ                     | -                     | -   | 0.1                 | ٧     |

|                                                                                 | V <sub>OH</sub>        | 1                                            | V <sub>DD</sub> - 0.1 | -   | -                   | ٧     |

| Output High Voltage                                                             |                        |                                              |                       |     |                     |       |

| PA0-7, PB0-7, PC0-6, TCMP                                                       | V <sub>OH</sub>        | I <sub>LOAD</sub> = -0.8mA                   | V <sub>DD</sub> - 0.8 | -   | -                   | V     |

| PD1-4                                                                           | V <sub>OH</sub>        | $I_{LOAD} = -1.6mA$                          | V <sub>DD</sub> - 0.8 | -   | -                   | ٧     |

| PC7                                                                             | V <sub>OH</sub>        | I <sub>LOAD</sub> = -5.0mA                   | V <sub>DD</sub> - 0.8 | -   | -                   | ٧     |

| Output Low Voltage PA0-7, PB0-7, PC0-6, PD1-4, TCMP                             | V <sub>OL</sub>        | I <sub>LOAD</sub> = 1.6mA                    | _                     | _   | 0.4                 | V     |

| PC7                                                                             | V <sub>OL</sub>        | $I_{LOAD} = 10.0 \text{mA}$                  | _                     |     | 0.4                 | V .   |

| Input High Voltage                                                              | , OL                   | LOAD = 18.61X                                |                       |     |                     | ,     |

| PA0-7, PB0-7, PC0-7, PD0-5, PD7, TCAP, IRQ, RESET, OSC1                         | V <sub>IH</sub>        |                                              | 0.7•V <sub>DD</sub>   | -   | V <sub>DD</sub>     | ٧     |

| Input Low Voltage  PA0-7, PB0-7, PC0-7, PD0-5, PD7, TCAP, IRQ, RESET, OSC1      | V <sub>IL</sub>        |                                              | V <sub>SS</sub>       | -   | 0.2•V <sub>DD</sub> | ٧     |

| Data Retention Mode                                                             | $V_{RM}$               | $T_A = 0^{\circ}C$ to $70^{\circ}C$          | 1.2                   | -   | -                   | ٧     |

| Supply Current<br>RUN (Note 6)                                                  | I <sub>DD</sub>        | f <sub>OSC</sub> = 4.2MHz                    | -                     | 3.5 | 5.25                | mA    |

| WAIT (Notes 7, 9)                                                               | I <sub>DD</sub>        | External Square Wave                         | -                     | 1.0 | 3.25                | mA    |

| STOP (Note 8)                                                                   | I <sub>DD</sub>        | $T_A = 25^{\circ}C$                          | -                     | 1.0 | 20.0                | μA    |

| STOP (Note 8)                                                                   | I <sub>DD</sub>        | $T_A = -40^{\circ}C \text{ to } 85^{\circ}C$ | -                     | -   | 50                  | μА    |

| I/O Ports Hi-Z Leakage Current:<br>PA0-7, PB0-7 (without pullups), PC0-7, PD1-4 | l <sub>OZ</sub>        |                                              | -                     | -   | ±10                 | μΑ    |

| Input Current RESET, IRQ, TCAP, OSC1, PD0, PD5, PD7                             | l <sub>IN</sub>        |                                              | -                     | -   | ±1                  | μА    |

| Capacitance Ports (As Input or Output)                                          | C <sub>OUT</sub>       |                                              | =                     | -   | 12                  | pF    |

| RESET, IRQ, TCAP, OSC1, PD0-5, PD7                                              | C <sub>IN</sub>        |                                              | -                     |     | 8                   | pF    |

| Input Pullup Current (Note 10)                                                  | I <sub>IN</sub>        |                                              | 175                   | 385 | 750                 | μΑ    |

# DC Electrical Specifications HC Product Type , $V_{DD} = 5.0V$ (Continued)

| PARAMETER                                        | SYMBOL           | CONDITIONS | MIN                 | TYP | MAX                 | UNITS |

|--------------------------------------------------|------------------|------------|---------------------|-----|---------------------|-------|

| Input Hysteresis Voltage: PB0-7                  | V <sub>HYS</sub> |            | -                   | 0.5 | -                   | ٧     |

| Input Hysteresis Voltage: RESET, IRQ, OSC1, TCAP | V <sub>HYS</sub> |            | 0.1•V <sub>DD</sub> | 1.0 | 0.5•V <sub>DD</sub> | ٧     |

# Control Timing HC Product Type, $V_{DD} = 5.0V$

| PARAMETER                                                                                               | SYMBOL              | MIN       | MAX | UNITS            |

|---------------------------------------------------------------------------------------------------------|---------------------|-----------|-----|------------------|

| <b>CDP68HC05C4B/C8B</b> $V_{DD} = 5V \pm 10\%, V_{SS} = 0V, T_A = -40^{\circ}C \text{ to } 85^{\circ}C$ |                     |           |     |                  |

| Frequency Of Operation                                                                                  |                     |           |     |                  |

| Crystal Option                                                                                          | fosc                | -         | 4.2 | MHz              |

| External Clock Option                                                                                   | fosc                | DC        | 4.2 | MHz              |

| Internal Operating Frequency                                                                            |                     |           |     |                  |

| Crystal (f <sub>OSC</sub> ÷ 2)                                                                          | f <sub>OP</sub>     | -         | 2.1 | MHz              |

| External Clock (f <sub>OSC</sub> ÷ 2)                                                                   | fOP                 | DC        | 2.1 | MHz              |

| Cycle Time (See Figure 15)                                                                              | <sup>t</sup> CYC    | 476       | -   | ns               |

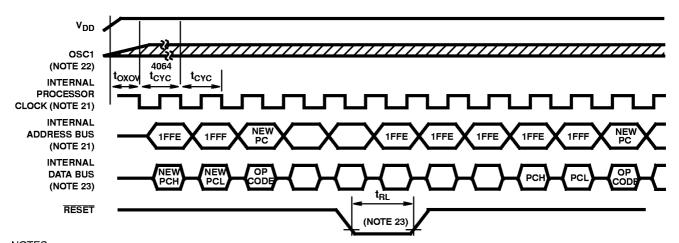

| Crystal Oscillator Start-up Time for AT-cut Crystal (See Figure 15)                                     | <sup>t</sup> OXOV   | -         | 100 | ms               |

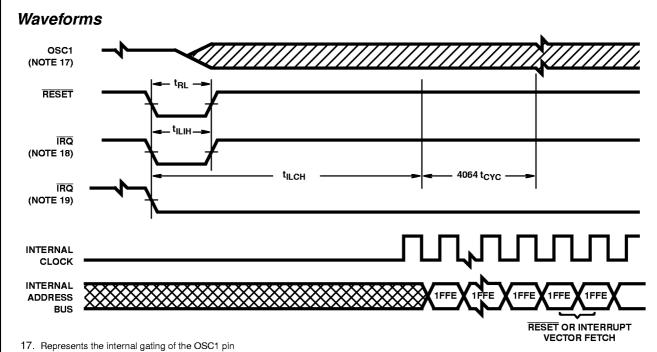

| Stop Recovery Start-up Time (AT-cut Crystal Oscillator) (See Figure 1)                                  | <sup>t</sup> ILCH   | -         | 100 | ms               |

| RESET Pulse Width (See Figure 15)                                                                       | t <sub>RL</sub>     | 1.5       | -   | tcyc             |

| Timer                                                                                                   |                     |           |     |                  |

| Resolution (Note 12)                                                                                    | t <sub>RES</sub>    | 4         | -   | t <sub>CYC</sub> |

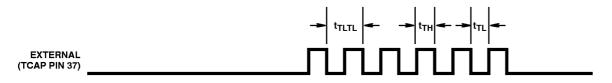

| Input Capture Pulse Width (See Figures 2, 23)                                                           | $t_{TH}$ , $t_{TL}$ | 125       | -   | ns               |

| Input Capture Pulse Period (See Figures 2, 23)                                                          | t <sub>TLTL</sub>   | (Note 13) | -   | tcyc             |

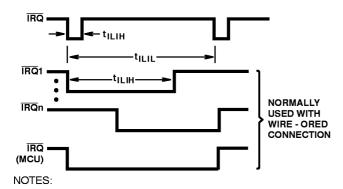

| Interrupt Pulse Width Low (Edge-Triggered) (See Figure 16B)                                             | t <sub>ILIH</sub>   | 125       | -   | ns               |

| Interrupt Pulse Period (See Figure 16B)                                                                 | t <sub>ILIH</sub>   | (Note11)  | -   | tcyc             |

| OSC1 Pulse Width                                                                                        | toH, toL            | 90        | -   | ns               |

# DC Electrical Specifications HC Product Type , $V_{DD} = 3.3V$

| PARAMETER                                                            | SYMBOL          | CONDITIONS                 | MIN                   | TYP | мах               | UNITS |

|----------------------------------------------------------------------|-----------------|----------------------------|-----------------------|-----|-------------------|-------|

| <b>CDP68HC05C4B/C8B</b> V <sub>DD</sub> = 3.3V ±10%, V <sub>SS</sub> |                 |                            |                       |     |                   |       |

| Output Voltage                                                       | V <sub>OL</sub> | I <sub>LOAD</sub> < 10μA   | -                     | -   | 0.1               | V     |

|                                                                      | V <sub>OH</sub> | 1                          | V <sub>DD</sub> - 0.1 | -   | -                 | ٧     |

| Output High Voltage                                                  |                 |                            |                       |     |                   |       |

| PA0-7, PB0-7, PC0-6, TCMP                                            | V <sub>OH</sub> | $I_{LOAD} = -0.2mA$        | V <sub>DD</sub> - 0.3 | -   | -                 | ٧     |

| PD1-4                                                                | V <sub>OH</sub> | $I_{LOAD} = -0.4mA$        | V <sub>DD</sub> - 0.3 | -   | -                 | ٧     |

| PC7                                                                  | V <sub>OH</sub> | I <sub>LOAD</sub> = -1.5mA | V <sub>DD</sub> - 0.3 | -   | -                 | ٧     |

| Output Low Voltage                                                   |                 |                            |                       |     |                   |       |

| PA0-7, PB0-7, PC0-6, PD1-4, TCMP                                     | V <sub>OL</sub> | $I_{LOAD} = 0.4mA$         | -                     | -   | 0.3               | V     |

| PC7                                                                  | V <sub>OL</sub> | I <sub>LOAD</sub> = 6.0mA  | -                     | -   | 0.3               | ٧     |

| Input High Voltage                                                   |                 |                            |                       |     |                   |       |

| PA0-7, PB0-7, PC0-7, PD0-5, PD7, TCAP, IRQ, RESET, OSC1              | V <sub>IH</sub> |                            | 0.7•V <sub>DD</sub>   | -   | $V_{\mathrm{DD}}$ | V     |

# DC Electrical Specifications HC Product Type , $V_{DD} = 3.3V$ (Continued)

| PARAMETER                                                                       | SYMBOL           | CONDITIONS                                           | MIN                 | TYP | MAX                 | UNITS |

|---------------------------------------------------------------------------------|------------------|------------------------------------------------------|---------------------|-----|---------------------|-------|

| Input Low Voltage PA0-7, PB0-7, PC0-7, PD0-5, PD7, TCAP, IRQ, RESET, OSC1       | V <sub>IL</sub>  |                                                      | V <sub>SS</sub>     | -   | 0.2•V <sub>DD</sub> | ٧     |

| Data Retention Mode                                                             | V <sub>RM</sub>  | $T_A = 0^{\circ}C$ to $70^{\circ}C$                  | 1.2                 | -   | -                   | V     |

| Supply Current<br>RUN (Note 6)                                                  | I <sub>DD</sub>  | f <sub>OSC</sub> = 2.1MHz                            | -                   | 1.0 | 1.6                 | mA    |

| WAIT (Notes 7, 9)                                                               | l <sub>DD</sub>  | External Square Wave                                 | -                   | 0.5 | 0.9                 | mA    |

| STOP (Note 8)                                                                   | I <sub>DD</sub>  | $T_A = 25^{\circ}C$                                  | -                   | 1.0 | 8.0                 | μА    |

| STOP (Note 8)                                                                   | l <sub>DD</sub>  | $T_A = -40^{\circ} \text{C to } 85^{\circ} \text{C}$ | -                   | -   | 20                  | μΑ    |

| I/O Ports Hi-Z Leakage Current:<br>PA0-7, PB0-7 (without pullups), PC0-7, PD1-4 | loz              |                                                      | -                   | -   | ±10                 | μА    |

| Input Current<br>RESET, IRQ, TCAP, OSC1, PD0, PD5, PD7                          | IN               |                                                      | -                   | -   | ±1                  | μА    |

| Capacitance Ports (As Input or Output)                                          | C <sub>OUT</sub> |                                                      | -                   |     | 12                  | pF    |

| RESET, IRQ, TCAP, OSC1, PD0-5, PD7                                              | C <sub>IN</sub>  |                                                      | -                   | -   | 8                   | pF    |

| Input Pullup Current (Note 10)                                                  | I <sub>IN</sub>  |                                                      | 75                  | 175 | 350                 | μΑ    |

| Input Hysteresis Voltage: PB0-7                                                 | V <sub>HYS</sub> |                                                      | -                   | 0.5 | -                   | ٧     |

| Input Hysteresis Voltage: RESET, IRQ, OSC1, TCAP                                | V <sub>HYS</sub> |                                                      | 0.1•V <sub>DD</sub> | 1.0 | 0.5•V <sub>DD</sub> | V     |

# Control Timing HC Product Type, $V_{DD}$ = 3.3V

| PARAMETER                                                                                                   | SYMBOL                            | MIN       | MAX  | UNITS            |

|-------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------|------|------------------|

| <b>CDP68HC05C4B/C8B</b> $V_{DD} = 3.3V \pm 10\%, V_{SS} = 0V, T_A = -40^{o}C \text{ to } 85^{o}C \text{ (}$ | (Note 2)                          |           |      |                  |

| Frequency Of Operation                                                                                      |                                   |           |      |                  |

| Crystal Option                                                                                              | fosc                              | -         | 2.1  | MHz              |

| External Clock Option                                                                                       | fosc                              | DC        | 2.1  | MHz              |

| Internal Operating Frequency                                                                                |                                   |           |      |                  |

| Crystal (f <sub>OSC</sub> ÷ 2)                                                                              | f <sub>OP</sub>                   | -         | 1.05 | MHz              |

| External Clock (f <sub>OSC</sub> ÷ 2)                                                                       | f <sub>OP</sub>                   | DC        | 1.05 | MHz              |

| Cycle Time (See Figure 15)                                                                                  | t <sub>CYC</sub>                  | 952       | -    | ns               |

| Crystal Oscillator Start-up Time for AT-cut Crystal (See Figure 15)                                         | toxov                             | -         | 100  | ms               |

| Stop Recovery Start-up Time (AT-cut Crystal Oscillator) (See Figure 1)                                      | <sup>†</sup> ILCH                 | -         | 100  | ms               |

| RESET Pulse Width (See Figure 15)                                                                           | t <sub>RL</sub>                   | 1.5       | -    | t <sub>CYC</sub> |

| Timer                                                                                                       |                                   |           |      |                  |

| Resolution (Note 12)                                                                                        | t <sub>RES</sub>                  | 4.0       | -    | tcyc             |

| Input Capture Pulse Width (See Figures 2, 23)                                                               | t <sub>TH</sub> , t <sub>TL</sub> | 250       | -    | ns               |

| Input Capture Pulse Period (See Figures 2, 23)                                                              | t <sub>TLTL</sub>                 | (Note 13) | -    | tcyc             |

| Interrupt Pulse Width Low (Edge-Triggered) (See Figure 16B)                                                 | t <sub>ILIH</sub>                 | 250       | -    | ns               |

| Interrupt Pulse Period (See Figure 16B)                                                                     | t <sub>ILIH</sub>                 | (Note 11) | -    | <sup>t</sup> cyc |

| OSC1 Pulse Width                                                                                            | toH, toL                          | 200       | -    | ns               |

# DC Electrical Specifications $\qquad$ HCL Product Type, $V_{DD}$ = 5.0V

| PARAMETER                                                                       | SYMBOL                                  | CONDITIONS                          | MIN                   | TYP | MAX                 | UNITS |

|---------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------|-----------------------|-----|---------------------|-------|

| <b>CDP68HCL05C4B/C8B</b> $V_{DD} = 5V \pm 10\%, V_{SS} = 10\%$                  | : 0V, T <sub>A</sub> = 0 <sup>0</sup> 0 | C to 70 <sup>o</sup> C (Note 2)     |                       |     |                     |       |

| Output Voltage                                                                  | V <sub>OL</sub>                         | I <sub>LOAD</sub> < 10μA            | -                     | -   | 0.1                 | V     |

|                                                                                 | V <sub>OH</sub>                         | 1                                   | V <sub>DD</sub> - 0.1 | -   | -                   | V     |

| Output High Voltage                                                             |                                         |                                     |                       |     |                     |       |

| PA0-7, PB0-7, PC0-6, TCMP                                                       | V <sub>OH</sub>                         | I <sub>LOAD</sub> = -0.8mA          | V <sub>DD</sub> - 0.8 | -   | -                   | V     |

| PD1-4                                                                           | V <sub>OH</sub>                         | I <sub>LOAD</sub> = -1.6mA          | V <sub>DD</sub> - 0.8 | -   | -                   | V     |

| PC7                                                                             | V <sub>OH</sub>                         | $I_{LOAD} = -5.0 \text{mA}$         | V <sub>DD</sub> - 0.8 | •   | -                   | V     |

| Output Low Voltage<br>PA0-7, PB0-7, PC0-6, PD1-4, TCMP                          | V <sub>OL</sub>                         | I <sub>LOAD</sub> = 1.6mA           | -                     | -   | 0.4                 | V     |

| PC7                                                                             | V <sub>OL</sub>                         | I <sub>LOAD</sub> = 10.0mA          | -                     | -   | 0.4                 | V     |

| Input High Voltage PA0-7, PB0-7, PC0-7, PD0-5, PD7, TCAP, IRQ, RESET, OSC1      | V <sub>IH</sub>                         |                                     | 0.7•V <sub>DD</sub>   | ı   | V <sub>DD</sub>     | V     |

| Input Low Voltage PA0-7, PB0-7, PC0-7, PD0-5, PD7, TCAP, IRQ, RESET, OSC1       | V <sub>IL</sub>                         |                                     | V <sub>SS</sub>       | -   | 0.2•V <sub>DD</sub> | ٧     |

| Data Retention Mode                                                             | $V_{RM}$                                | $T_A = 0^{\circ}C$ to $70^{\circ}C$ | 1.2                   | -   | -                   | V     |

| Supply Current<br>RUN (Note 6)                                                  | l <sub>DD</sub>                         | f <sub>OSC</sub> = 4.2MHz           | -                     | 3.5 | 4.25                | mA    |

| WAIT (Notes 7, 9)                                                               | I <sub>DD</sub>                         | External Square Wave                | -                     | 1.6 | 2.25                | mA    |

| STOP (Note 8)                                                                   | I <sub>DD</sub>                         | T <sub>A</sub> = 25 <sup>o</sup> C  | -                     | 1.0 | 15.0                | μΑ    |

| STOP (Note 8)                                                                   | l <sub>DD</sub>                         | $T_A = 0^{\circ}C$ to $70^{\circ}C$ | -                     | -   | 25                  | μΑ    |

| I/O Ports Hi-Z Leakage Current:<br>PA0-7, PB0-7 (without pullups), PC0-7, PD1-4 | loz                                     |                                     | -                     | -   | ±10                 | μА    |

| Input Current<br>RESET, IRQ, TCAP, OSC1, PD0, PD5, PD7                          | I <sub>IN</sub>                         |                                     | -                     | -   | ±1                  | μΑ    |

| Capacitance Ports (As Input or Output)                                          | C <sub>OUT</sub>                        |                                     | -                     | -   | 12                  | pF    |

| RESET, IRQ, TCAP, OSC1, PD0-5, PD7                                              | C <sub>IN</sub>                         |                                     | -                     | -   | 8                   | pF    |

| Input Pullup Current (Note 10)                                                  | I <sub>IN</sub>                         |                                     | 5                     |     | 250                 | μΑ    |

| Input Hysteresis Voltage: PB0-7                                                 | V <sub>HYS</sub>                        |                                     | -                     | 0.5 | -                   | ٧     |

| Input Hysteresis Voltage: RESET, IRQ, OSC1, TCAP                                | V <sub>HYS</sub>                        |                                     | 0.1•V <sub>DD</sub>   | 1.0 | 0.5•V <sub>DD</sub> | ٧     |

# Control Timing HCL Product Type, $V_{DD}$ = 5.0V

| PARAMETER                                                                                 | SYMBOL          | MIN | MAX | UNITS |  |  |  |  |  |

|-------------------------------------------------------------------------------------------|-----------------|-----|-----|-------|--|--|--|--|--|

| <b>CDP68HCL05C4B/C8B</b> $V_{DD} = 5V 10\%$ , $V_{SS} = 0V$ , $T_A = 0^{o}C$ to $70^{o}C$ |                 |     |     |       |  |  |  |  |  |

| Frequency Of Operation                                                                    |                 |     |     |       |  |  |  |  |  |

| Crystal Option                                                                            | fosc            | -   | 4.2 | MHz   |  |  |  |  |  |

| External Clock Option                                                                     | fosc            | DC  | 4.2 | MHz   |  |  |  |  |  |

| Internal Operating Frequency                                                              |                 |     |     |       |  |  |  |  |  |

| Crystal (f <sub>OSC</sub> ÷ 2)                                                            | f <sub>OP</sub> | -   | 2.1 | MHz   |  |  |  |  |  |

| External Clock (f <sub>OSC</sub> ÷ 2)                                                     | f <sub>OP</sub> | DC  | 2.1 | MHz   |  |  |  |  |  |

# Control Timing HCL Product Type, V<sub>DD</sub>= 5.0V (Continued)

| PARAMETER                                                              |                                   | MIN       | MAX | UNITS            |

|------------------------------------------------------------------------|-----------------------------------|-----------|-----|------------------|

| Cycle Time (See Figure 15)                                             | tcyc                              | 476       | -   | ns               |

| Crystal Oscillator Start-up Time for AT-cut Crystal (See Figure 15)    | toxov                             | -         | 100 | ms               |

| Stop Recovery Start-up Time (AT-cut Crystal Oscillator) (See Figure 1) | <sup>†</sup> ILCH                 | -         | 100 | ms               |

| RESET Pulse Width (See Figure 15)                                      | t <sub>RL</sub>                   | 1.5       | -   | <sup>t</sup> CYC |

| Timer                                                                  |                                   |           |     |                  |

| Resolution (Note 12)                                                   | t <sub>RES</sub>                  | 4         | -   | t <sub>CYC</sub> |

| Input Capture Pulse Width (See Figures 2, 23)                          | t <sub>TH</sub> , t <sub>TL</sub> | 125       | •   | ns               |

| Input Capture Pulse Period (See Figures 2, 23)                         | t <sub>TLTL</sub>                 | (Note 13) | -   | <sup>t</sup> CYC |

| Interrupt Pulse Width Low (Edge-Triggered) (See Figure 16B)            | t∣LIH                             | 125       | -   | ns               |

| Interrupt Pulse Period (See Figure 16B)                                | tILIH                             | (Note 11) | -   | tcyc             |

| OSC1 Pulse Width                                                       | t <sub>OH</sub> , t <sub>OL</sub> | 90        | -   | ns               |

# DC Electrical Specifications HCL Product Type, $V_{DD} = 2.5V - 3.6V$

| PARAMETER                                                                  | SYMBOL                   | CONDITIONS                                        | MIN                   | TYP | MAX                 | UNITS |

|----------------------------------------------------------------------------|--------------------------|---------------------------------------------------|-----------------------|-----|---------------------|-------|

| <b>CDP68HCL05C4B/C8B</b> V <sub>DD</sub> = 2.5V - 3.6V ±10                 | %, V <sub>SS</sub> = 0V, | $T_A = 0^{\circ}C$ to $70^{\circ}C$ (Note 2       | )                     |     | •                   |       |

| Output Voltage                                                             | V <sub>OL</sub>          | I <sub>LOAD</sub> < 10μΑ                          | -                     | -   | 0.1                 | V     |

|                                                                            | V <sub>OH</sub>          | ]                                                 | V <sub>DD</sub> - 0.1 | -   | -                   | V     |

| Output High Voltage                                                        |                          |                                                   |                       |     |                     |       |

| PA0-7, PB0-7, PC0-6, TCMP                                                  | V <sub>OH</sub>          | $I_{LOAD} = -0.2mA$                               | V <sub>DD</sub> - 0.3 | -   | -                   | V     |

| PD1-4                                                                      | V <sub>OH</sub>          | $I_{LOAD} = -0.4mA$                               | V <sub>DD</sub> - 0.3 | -   | -                   | V     |

| PC7                                                                        | V <sub>OH</sub>          | $I_{LOAD} = -1.5mA$                               | V <sub>DD</sub> - 0.3 | -   | -                   | V     |

| Output Low Voltage                                                         |                          |                                                   |                       |     |                     |       |

| PA0-7, PB0-7, PC0-6, PD1-4, TCMP                                           | V <sub>OL</sub>          | I <sub>LOAD</sub> = 0.4mA                         | -                     | -   | 0.3                 | V     |

| PC7                                                                        | V <sub>OL</sub>          | $I_{LOAD} = 6.0 \text{mA}$                        | -                     | -   | 0.3                 | V     |

| Input High Voltage PA0-7, PB0-7, PC0-7, PD0-5, PD7, TCAP, IRQ, RESET, OSC1 | V <sub>IH</sub>          |                                                   | 0.7•V <sub>DD</sub>   | -   | V <sub>DD</sub>     | ٧     |

| Input Low Voltage  PA0-7, PB0-7, PC0-7, PD0-5, PD7, TCAP, IRQ, RESET, OSC1 | V <sub>IL</sub>          |                                                   | V <sub>SS</sub>       | -   | 0.2•V <sub>DD</sub> | ٧     |

| Data Retention Mode                                                        | $V_{RM}$                 | $T_A = 0^{\circ}C$ to $70^{\circ}C$               | 1.2                   | -   | -                   | V     |

| Supply Current                                                             |                          |                                                   |                       |     |                     |       |

| RUN (Note 6)                                                               | I <sub>DD</sub>          | f <sub>OSC</sub> = 2.1MHz                         | -                     | 1.0 | 1.4                 | mA    |

| WAIT (Notes 7, 9)                                                          | I <sub>DD</sub>          | External Square Wave                              | -                     | 0.7 | 1.0                 | mA    |

| STOP (Note 8)                                                              | I <sub>DD</sub>          | T <sub>A</sub> = 25 <sup>o</sup> C                | -                     | 1.0 | 5.0                 | μΑ    |

| STOP (Note 8)                                                              | l <sub>DD</sub>          | $T_A = 0^{\circ}C$ to $70^{\circ}C$               | -                     | -   | 10                  | μΑ    |

| Supply Current                                                             |                          |                                                   |                       |     |                     |       |

| RUN (Note 6)                                                               | I <sub>DD</sub>          | f <sub>OSC</sub> = 1.0MHz<br>External Square Wave | -                     | 0.5 | 0.75                | mA    |

| WAIT (Notes 7, 9)                                                          | I <sub>DD</sub>          |                                                   | -                     | 0.3 | 0.5                 | mA    |

| STOP (Note 8)                                                              | I <sub>DD</sub>          | T <sub>A</sub> = 25 <sup>o</sup> C                | -                     | 1.0 | 5.0                 | μΑ    |

| STOP (Note 8)                                                              | I <sub>DD</sub>          | $T_A = 0^{\circ}C \text{ to } 70^{\circ}C$        | -                     | -   | 10                  | μΑ    |

# DC Electrical Specifications HCL Product Type, $V_{DD} = 2.5V - 3.6V$ (Continued)

| PARAMETER                                              | SYMBOL           | CONDITIONS | MIN                 | TYP | MAX                 | UNITS |

|--------------------------------------------------------|------------------|------------|---------------------|-----|---------------------|-------|

| I/O Ports Hi-Z Leakage Current:                        |                  |            |                     |     |                     |       |

| PA0-7, PB0-7 (without pullups), PC0-7, PD1-4           | loz              |            | -                   | -   | ±10                 | μΑ    |

| Input Current<br>RESET, IRQ, TCAP, OSC1, PD0, PD5, PD7 | I <sub>IN</sub>  |            | -                   | -   | ±1                  | μΑ    |

| Capacitance Ports (As Input or Output)                 | C <sub>OUT</sub> |            | -                   | -   | 12                  | pF    |

| RESET, IRQ, TCAP, OSC1, PD0-5, PD7                     | C <sub>IN</sub>  |            | -                   | -   | 8                   | pF    |

| Input Pullup Current (Note 10)                         | I <sub>IN</sub>  |            | 40                  | 160 | 300                 | μΑ    |

| Input Hysteresis Voltage: PB0-7                        | V <sub>HYS</sub> |            | -                   | 0.5 | -                   | ٧     |

| Input Hysteresis Voltage: RESET, IRQ, OSC1, TCAP       | V <sub>HYS</sub> |            | 0.1•V <sub>DD</sub> | 1.0 | 0.5•V <sub>DD</sub> | ٧     |

# Control Timing HCL Product Type, $V_{DD}$ = 2.4V - 3.6V

| PARAMETER                                                                                                              | SYMBOL                            | MIN       | MAX  | UNITS            |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------|------|------------------|

| <b>CDP68HCL05C4B/C8B</b> $V_{DD} = 2.4V \text{ to } 3.6V, V_{SS} = 0V, T_A = 0^{\circ}\text{C to } 70^{\circ}\text{C}$ | V <sub>DC</sub> = 3.6)            |           |      |                  |

| Frequency Of Operation                                                                                                 |                                   |           |      |                  |

| Crystal Option                                                                                                         | fosc                              | -         | 2.1  | MHz              |

| External Clock Option                                                                                                  | fosc                              | DC        | 2.1  | MHz              |

| Internal Operating Frequency                                                                                           |                                   |           |      |                  |

| Crystal (f <sub>OSC</sub> ÷ 2)                                                                                         | f <sub>OP</sub>                   | -         | 1.05 | MHz              |

| External Clock (f <sub>OSC</sub> ÷ 2)                                                                                  | fOP                               | DC        | 1.05 | MHz              |

| Cycle Time (See Figure 15)                                                                                             | <sup>t</sup> CYC                  | 952       | -    | ns               |

| Crystal Oscillator Start-up Time for AT-cut Crystal (See Figure 15)                                                    | toxov                             | -         | 100  | ms               |

| Stop Recovery Start-up Time (AT-cut Crystal Oscillator) (See Figure 1)                                                 | <sup>†</sup> ILCH                 | -         | 100  | ms               |

| RESET Pulse Width (See Figure 15)                                                                                      | t <sub>RL</sub>                   | 1.5       | -    | <sup>t</sup> CYC |

| Timer                                                                                                                  |                                   |           |      |                  |

| Resolution (Note 12)                                                                                                   | t <sub>RES</sub>                  | 4.0       | -    | tcyc             |

| Input Capture Pulse Width (See Figures 2, 23)                                                                          | t <sub>TH</sub> , t <sub>TL</sub> | 250       | -    | ns               |

| Input Capture Pulse Period (See Figures 2, 23)                                                                         | t <sub>TLTL</sub>                 | (Note 11) | -    | <sup>t</sup> CYC |

| Interrupt Pulse Width Low (Edge-Triggered) (See Figure 16B)                                                            | t <sub>ILIH</sub>                 | 250       | -    | ns               |

| Interrupt Pulse Period (See Figure 16B)                                                                                | t <sub>ILIH</sub>                 | (Note 13) | -    | tcyc             |

| OSC1 Pulse Width                                                                                                       | t <sub>OH</sub> , t <sub>OL</sub> | 200       | -    | ns               |

# DC Electrical Specifications HCL Product Type, $V_{DD} = 1.8V - 2.4V$

| PARAMETER                                                                                                                           | SYMBOL          | CONDITIONS                  | MIN                   | TYP | MAX | UNITS |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------|-----------------------|-----|-----|-------|--|--|

| <b>CDP68HCL05C4B/C8B</b> $V_{DD} = 1.8V - 2.4V$ , $V_{SS} = 0V$ , $T_A = 0^{\circ}$ C to $70^{\circ}$ C, Unless Otherwise Specified |                 |                             |                       |     |     |       |  |  |

| Output Voltage                                                                                                                      | V <sub>OL</sub> | I <sub>LOAD</sub> < 10μΑ    | -                     | -   | 0.1 | ٧     |  |  |

|                                                                                                                                     | V <sub>OH</sub> |                             | V <sub>DD</sub> - 0.1 | -   | -   | ٧     |  |  |

| Output High Voltage                                                                                                                 |                 |                             |                       |     |     |       |  |  |

| PA0-7, PB0-7, PC0-6, TCMP                                                                                                           | V <sub>OH</sub> | $I_{LOAD} = -0.1mA$         | V <sub>DD</sub> - 0.3 | -   | -   | ٧     |  |  |

| PD1-4                                                                                                                               | V <sub>OH</sub> | I <sub>LOAD</sub> = -0.2mA  | V <sub>DD</sub> - 0.3 | -   | -   | ٧     |  |  |

| PC7                                                                                                                                 | V <sub>OH</sub> | I <sub>LOAD</sub> = -0.75mA | V <sub>DD</sub> - 0.3 | -   | -   | ٧     |  |  |

DC Electrical Specifications HCL Product Type,  $V_{DD} = 1.8V - 2.4V$  (Continued)

| PARAMETER                                                                       | SYMBOL           | CONDITIONS                          | MIN                 | TYP | MAX                 | UNITS |

|---------------------------------------------------------------------------------|------------------|-------------------------------------|---------------------|-----|---------------------|-------|

| Output Low Voltage                                                              |                  |                                     |                     |     |                     |       |

| PA0-7, PB0-7, PC0-6, PD1-4, TCMP                                                | $V_{OL}$         | I <sub>LOAD</sub> = 0.2mA           | -                   | -   | 0.3                 | V     |

| PC7                                                                             | V <sub>OL</sub>  | I <sub>LOAD</sub> = 2.0mA           | -                   | -   | 0.3                 | V     |

| Input High Voltage PA0-7, PB0-7, PC0-7, PD0-5, PD7, TCAP, IRQ, RESET, OSC1      | V <sub>IH</sub>  |                                     | 0.7•V <sub>DD</sub> | -   | V <sub>DD</sub>     | V     |

| Input Low Voltage PA0-7, PB0-7, PC0-7, PD0-5, PD7, TCAP, IRQ, RESET, OSC1       | $V_IL$           |                                     | V <sub>SS</sub>     | -   | 0.2•V <sub>DD</sub> | V     |

| Data Retention Mode                                                             | $V_{RM}$         | $T_A = 0$ °C to $70$ °C             | 1.2                 | -   | -                   | ٧     |

| Supply Current<br>RUN (Note 6)                                                  | I <sub>DD</sub>  | f <sub>OSC</sub> = 1.0MHz           | -                   | 300 | 600                 | μΑ    |

| WAIT (Notes 7, 9)                                                               | I <sub>DD</sub>  | External Square Wave                | -                   | 250 | 400                 | μΑ    |

| STOP (Note 8)                                                                   | I <sub>DD</sub>  | $T_A = 25^{\circ}C$                 | -                   | 1.0 | 2.0                 | μΑ    |

| STOP (Note 8)                                                                   | I <sub>DD</sub>  | $T_A = 0^{\circ}C$ to $70^{\circ}C$ | -                   | -   | 5.0                 | μΑ    |

| I/O Ports Hi-Z Leakage Current:<br>PA0-7, PB0-7 (without pullups), PC0-7, PD1-4 | l <sub>OZ</sub>  |                                     | -                   | -   | ±10                 | μΑ    |

| Input Current<br>RESET, IRQ, TCAP, OSC1, PD0, PD5, PD7                          | I <sub>IN</sub>  |                                     | -                   | -   | ±1                  | μΑ    |

| Capacitance Ports (As Input or Output)                                          | C <sub>OUT</sub> |                                     | -                   | -   | 12                  | pF    |

| RESET, IRQ, TCAP, OSC1, PD0-5, PD7                                              | C <sub>IN</sub>  | IN                                  | -                   | -   | 8                   | pF    |

| Input Pullup Current (Note 10)                                                  | I <sub>IN</sub>  |                                     | 15                  | 110 | 200                 | μΑ    |

| Input Hysteresis Voltage: PB0-7                                                 | V <sub>HYS</sub> |                                     | -                   | 0.5 | -                   | ٧     |

| Input Hysteresis Voltage: RESET, IRQ, OSC1, TCAP                                | V <sub>HYS</sub> |                                     | 0.1•V <sub>DD</sub> | 1.0 | 0.5•V <sub>DD</sub> | V     |

# Control Timing HCL Product Type, $V_{DD} = 1.8V - 2.4V$

| PARAMETER                                                                                                                        | SYMBOL          | MIN  | MAX | UNITS            |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-----|------------------|--|--|--|--|--|

| <b>CDP68HCL05C4B/C8B</b> $V_{DD} = 1.8V \text{ to } 2.4V, V_{SS} = 0V, T_{A} = 0^{o}\text{C to } 70^{o}\text{C } (V_{DC} = 2.4)$ |                 |      |     |                  |  |  |  |  |  |

| Frequency Of Operation                                                                                                           |                 |      |     |                  |  |  |  |  |  |

| Crystal Option                                                                                                                   | fosc            | -    | 1.0 | MHz              |  |  |  |  |  |

| External Clock Option                                                                                                            | fosc            | DC   | 1.0 | MHz              |  |  |  |  |  |

| Internal Operating Frequency                                                                                                     |                 |      |     |                  |  |  |  |  |  |

| Crystal (f <sub>OSC</sub> ÷ 2)                                                                                                   | fOP             | -    | 0.5 | MHz              |  |  |  |  |  |

| External Clock (f <sub>OSC</sub> ÷ 2)                                                                                            | f <sub>OP</sub> | DC   | 0.5 | MHz              |  |  |  |  |  |

| Cycle Time (See Figure 15)                                                                                                       | tcyc            | 2000 | -   | ns               |  |  |  |  |  |

| Crystal Oscillator Start-up Time for AT-cut Crystal (See Figure 15)                                                              | toxov           | -    | 100 | ms               |  |  |  |  |  |

| Stop Recovery Start-up Time (AT-cut Crystal Oscillator) (See Figure 1)                                                           |                 | -    | 100 | ms               |  |  |  |  |  |

| RESET Pulse Width (See Figure 15)                                                                                                | t <sub>RL</sub> | 1.5  | -   | <sup>t</sup> CYC |  |  |  |  |  |

# Control Timing HCL Product Type, $V_{DD} = 1.8V - 2.4V$ (Continued)

| PARAMETER                                                   | SYMBOL                            | MIN       | MAX | UNITS            |

|-------------------------------------------------------------|-----------------------------------|-----------|-----|------------------|

| Timer                                                       |                                   |           |     |                  |

| Resolution (Note 12)                                        | t <sub>RES</sub>                  | 4.0       | -   | tcyc             |

| Input Capture Pulse Width (See Figures 2, 23)               | t <sub>TH</sub> , t <sub>TL</sub> | 500       | -   | ns               |

| Input Capture Pulse Period (See Figures 2, 23)              | t <sub>TLTL</sub>                 | (Note 13) | -   | <sup>t</sup> CYC |

| Interrupt Pulse Width Low (Edge-Triggered) (See Figure 16B) | tILIH                             | 500       | -   | ns               |

| Interrupt Pulse Period (See Figure 16B)                     | t <sub>ILIH</sub>                 | (Note 11) | -   | <sup>t</sup> CYC |

| OSC1 Pulse Width                                            | t <sub>OH</sub> , t <sub>OL</sub> | 400       | -   | ns               |

| PARAMETER                                                                       | SYMBOL                     | CONDITIONS                                           | MIN                   | TYP | MAX                 | UNITS |

|---------------------------------------------------------------------------------|----------------------------|------------------------------------------------------|-----------------------|-----|---------------------|-------|

| <b>CDP68HSC05C4B/C8B</b> $V_{DD} = 5V \pm 10\%, V_{SS} = 10\%$                  | = 0V, T <sub>A</sub> = -40 | <sup>o</sup> C to 85 <sup>o</sup> C (Note 2)         |                       |     | •                   |       |

| Output Voltage                                                                  | V <sub>OL</sub>            | I <sub>LOAD</sub> < 10μΑ                             | -                     | -   | 0.1                 | ٧     |

|                                                                                 | V <sub>OH</sub>            | ]                                                    | V <sub>DD</sub> - 0.1 | -   | -                   | ٧     |

| Output High Voltage                                                             |                            |                                                      |                       |     |                     |       |

| PA0-7, PB0-7, PC0-6, TCMP                                                       | V <sub>OH</sub>            | I <sub>LOAD</sub> = -0.8mA                           | V <sub>DD</sub> - 0.8 | -   | -                   | V     |

| PD1-4                                                                           | V <sub>OH</sub>            | I <sub>LOAD</sub> = -1.6mA                           | V <sub>DD</sub> - 0.8 | -   | -                   | V     |

| PC7                                                                             | V <sub>OH</sub>            | I <sub>LOAD</sub> = -5.0mA                           | V <sub>DD</sub> - 0.8 | -   | -                   | V     |

| Output Low Voltage<br>PA0-7, PB0-7, PC0-6, PD1-4, TCMP                          | V <sub>OL</sub>            | I <sub>LOAD</sub> = 1.6mA                            | -                     | -   | 0.4                 | V     |

| PC7                                                                             | V <sub>OL</sub>            | I <sub>LOAD</sub> = 10.0mA                           | -                     | -   | 0.4                 | ٧     |

| Input High Voltage PA0-7, PB0-7, PC0-7, PD0-5, PD7, TCAP, IRQ, RESET, OSC1      | V <sub>IH</sub>            |                                                      | 0.7•V <sub>DD</sub>   | -   | V <sub>DD</sub>     | ٧     |

| Input Low Voltage PA0-7, PB0-7, PC0-7, PD0-5, PD7, TCAP, IRQ, RESET, OSC1       | V <sub>IL</sub>            |                                                      | V <sub>SS</sub>       | ,   | 0.2•V <sub>DD</sub> | ٧     |

| Data Retention Mode                                                             | $V_{RM}$                   | $T_A = 0^{\circ}C$ to $70^{\circ}C$                  | 1.2                   | -   | -                   | ٧     |

| Supply Current<br>RUN (Note 6)                                                  | I <sub>DD</sub>            | f <sub>OSC</sub> = 8.0MHz                            | -                     | 7.0 | 11.0                | mA    |

| WAIT (Notes 7, 9)                                                               | l <sub>DD</sub>            | External Square Wave                                 | -                     | 2.0 | 6.5                 | mA    |

| STOP (Note 8)                                                                   | I <sub>DD</sub>            | T <sub>A</sub> = 25°C                                | -                     | 1.0 | 20.0                | μΑ    |

| STOP (Note 8)                                                                   | I <sub>DD</sub>            | $T_A = -40^{\circ} \text{C to } 85^{\circ} \text{C}$ | -                     | -   | 50                  | μΑ    |

| I/O Ports Hi-Z Leakage Current:<br>PA0-7, PB0-7 (without pullups), PC0-7, PD1-4 | l <sub>OZ</sub>            |                                                      | -                     | -   | ±10                 | μА    |

| Input Current RESET, IRQ, TCAP, OSC1, PD0, PD5, PD7                             | I <sub>IN</sub>            |                                                      | -                     | 1   | ±1                  | μА    |

| Capacitance Ports (As Input or Output)                                          | C <sub>OUT</sub>           |                                                      | -                     | 1   | 12                  | pF    |

| RESET, IRQ, TCAP, OSC1, PD0-5, PD7                                              | C <sub>IN</sub>            |                                                      | -                     | -   | 8                   | pF    |

| Input Pullup Current (Note 10)                                                  | I <sub>IN</sub>            |                                                      | 175                   | 385 | 750                 | μА    |

| Input Hysteresis Voltage: PB0-7                                                 | V <sub>HYS</sub>           |                                                      | -                     | 0.5 | -                   | ٧     |

| Input Hysteresis Voltage: RESET, IRQ, OSC1, TCAP                                | V <sub>HYS</sub>           |                                                      | 0.1•V <sub>DD</sub>   | 1.0 | 0.5•V <sub>DD</sub> | ٧     |

# Control Timing HSC Product Type, $V_{DD} = 5.0V$

| PARAMETER                                                                                                        | SYMBOL          | MIN | MAX | UNITS |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|-------|--|--|--|--|

| <b>CDP68HSC05C4B/C8B</b> $V_{DD} = 5V \pm 10\%$ , $V_{SS} = 0V$ , $T_A = -40^{\circ}C$ to $85^{\circ}C$ (Note 2) |                 |     |     |       |  |  |  |  |

| Frequency Of Operation                                                                                           |                 |     |     |       |  |  |  |  |

| Crystal Option                                                                                                   | fosc            | -   | 8.2 | MHz   |  |  |  |  |

| External Clock Option                                                                                            | fosc            | DC  | 8.2 | MHz   |  |  |  |  |

| Internal Operating Frequency                                                                                     |                 |     |     |       |  |  |  |  |

| Crystal (f <sub>OSC</sub> ÷ 2)                                                                                   | f <sub>OP</sub> | -   | 4.1 | MHz   |  |  |  |  |

| External Clock (f <sub>OSC</sub> ÷ 2)                                                                            | f <sub>OP</sub> | DC  | 4.1 | MHz   |  |  |  |  |

# Control Timing HSC Product Type, $V_{DD} = 5.0V$ (Continued)

| PARAMETER                                                              | SYMBOL                            | MIN       | MAX | UNITS |

|------------------------------------------------------------------------|-----------------------------------|-----------|-----|-------|

| Cycle Time (See Figure 15)                                             | tcyc                              | 244       | -   | ns    |

| Crystal Oscillator Start-up Time for AT-cut Crystal (See Figure 15)    | toxov                             | -         | 100 | ms    |

| Stop Recovery Start-up Time (AT-cut Crystal Oscillator) (See Figure 1) | <sup>t</sup> ILCH                 | -         | 100 | ms    |

| RESET Pulse Width (See Figure 15)                                      | t <sub>RL</sub>                   | 1.5       |     | tcyc  |

| Timer                                                                  |                                   |           |     |       |

| Resolution (Note 12)                                                   | t <sub>RES</sub>                  | 4         | -   | tcyc  |

| Input Capture Pulse Width (See Figures 2, 23)                          | t <sub>TH</sub> , t <sub>TL</sub> | 64        | -   | ns    |

| Input Capture Pulse Period (See Figures 2, 23)                         | t <sub>TLTL</sub>                 | (Note 13) | -   | tcyc  |

| Interrupt Pulse Width Low (Edge-Triggered) (See Figure 16B)            | tILIH                             | 64        | -   | ns    |

| Interrupt Pulse Period (See Figure 16B)                                | <sup>t</sup> ILIH                 | (Note 11) | -   | tcyc  |

| OSC1 Pulse Width                                                       | t <sub>OH</sub> , t <sub>OL</sub> | 50        | -   | ns    |

# DC Electrical Specifications HSC Product Type, $V_{DD} = 2.6V - 3.6V$

| PARAMETER                                                                       | SYMBOL                                  | CONDITIONS                                           | MIN                   | TYP | MAX                 | UNITS |

|---------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------|-----------------------|-----|---------------------|-------|

| <b>CDP68HSC05C4B/C8B</b> V <sub>DD</sub> = 2.4V - 3.6V, V <sub>SS</sub>         | = 0V, T <sub>A</sub> = -4               | 40 <sup>o</sup> C to 85 <sup>o</sup> C (Note 2)      | •                     |     |                     |       |

| Output Voltage                                                                  | V <sub>OL</sub> I <sub>LOAD</sub> ≤10μA |                                                      | -                     | -   | 0.1                 | ٧     |

|                                                                                 | V <sub>OH</sub>                         |                                                      | V <sub>DD</sub> - 0.1 | -   | -                   | ٧     |

| Output High Voltage                                                             |                                         |                                                      |                       |     |                     |       |

| PA0-7, PB0-7, PC0-6, TCMP                                                       | V <sub>OH</sub>                         | $I_{LOAD} = -0.2mA$                                  | V <sub>DD</sub> - 0.3 | -   | -                   | V     |

| PD1-4                                                                           | V <sub>OH</sub>                         | $I_{LOAD} = -0.4mA$                                  | V <sub>DD</sub> - 0.3 | -   | -                   | ٧     |

| PC7                                                                             | V <sub>OH</sub>                         | I <sub>LOAD</sub> = -1.5mA                           | V <sub>DD</sub> - 0.3 | -   | -                   | V     |

| Output Low Voltage                                                              |                                         |                                                      |                       |     |                     |       |

| PA0-7, PB0-7, PC0-6, PD1-4, TCMP                                                | $V_{OL}$                                | I <sub>LOAD</sub> = 0.4mA                            | -                     | -   | 0.3                 | V     |

| PC7                                                                             | $V_{OL}$                                | $I_{LOAD} = 6.0 \text{mA}$                           | -                     | -   | 0.3                 | V     |

| Input High Voltage PA0-7, PB0-7, PC0-7, PD0-5, PD7, TCAP, IRQ, RESET, OSC1      | V <sub>IH</sub>                         |                                                      | 0.7•V <sub>DD</sub>   | -   | V <sub>DD</sub>     | ٧     |

| Input Low Voltage PA0-7, PB0-7, PC0-7, PD0-5, PD7, TCAP, IRQ, RESET, OSC1       | V <sub>IL</sub>                         |                                                      | V <sub>SS</sub>       | -   | 0.2•V <sub>DD</sub> | ٧     |

| Data Retention Mode                                                             | $V_{RM}$                                | $T_A = 0^{\circ}C$ to $70^{\circ}C$                  | 1.2                   | -   | -                   | ٧     |

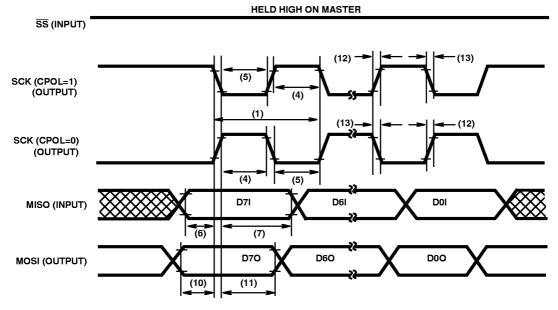

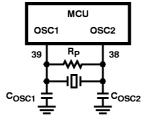

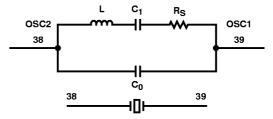

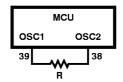

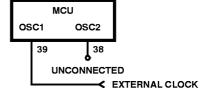

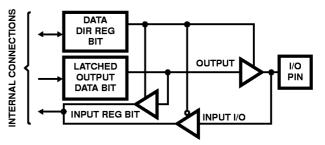

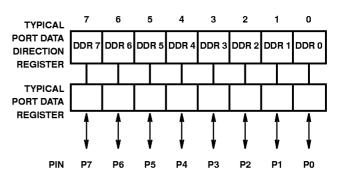

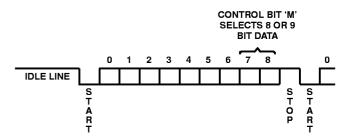

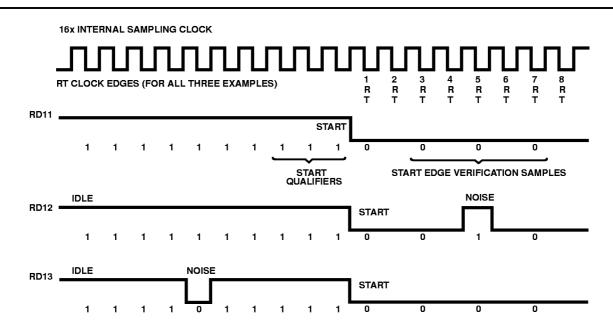

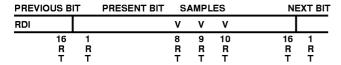

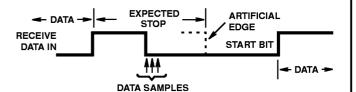

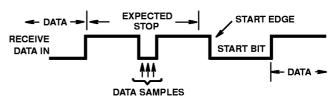

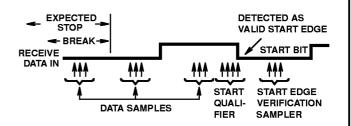

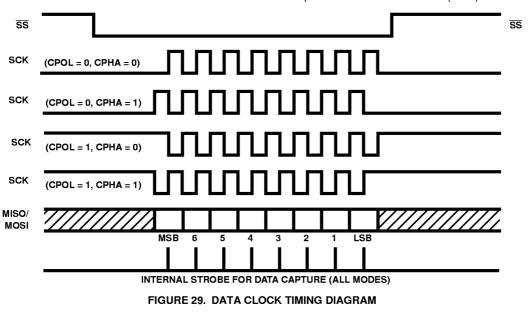

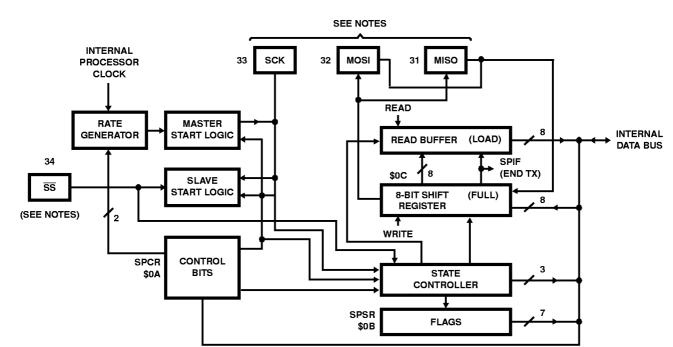

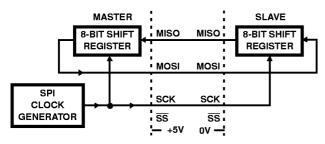

| Supply Current<br>RUN (Note 6)                                                  | I <sub>DD</sub>                         | f <sub>OSC</sub> = 4.2MHz                            | -                     | 2.5 | 4.0                 | mA    |