# PDH ATM UNI Processor Product Overview

#### **FEATURES**

- Operates at rates up to 140 Mbps.

- Complies with the ATM Forum UNI specification 3.0, ITU specification G.804, ITU specification G.832, and Bellcore specification TR-TSV-000773.

- Provides integrated framers for DS3 (44.736 Mbps), E3 G.804 (34.368 Mbps), and E4 G.804 (139.264 Mbps).

- Provides ATM cells for DS1 (1.544 Mbps) or E1 (2.048 Mbps).

- Transfers ATM data through an 8-bit UTOPIA interface.

- Transfers DS3- and E3-formatted data through a synchronous, serial, Non-Return to Zero (NRZ) interface, and E3/E4-formatted data through a synchronous 8-bit interface.

- Provides access to the full DS3 PLCP, E3, and E4 data stream via a synchronous 8-bit interface.

- Provides built-in performance and alarm monitoring.

- Inserts and monitors Generic Flow Control (GFC) bits.

- Provides built-in error generation and loopback.

- Compatible with CMOS and TTL signals.

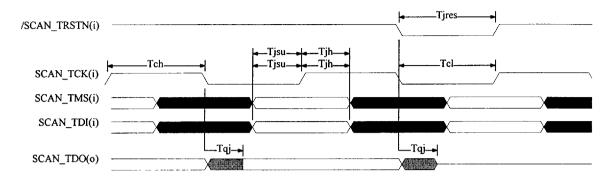

- Provides boundary scan capability and tristatable outputs for ATE testing.

- Available in 144-pin QFP.

### DESCRIPTION

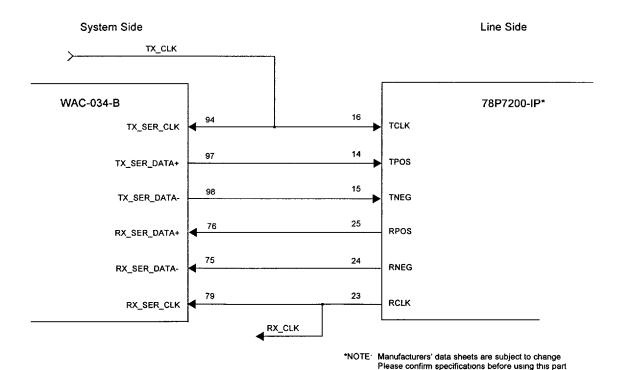

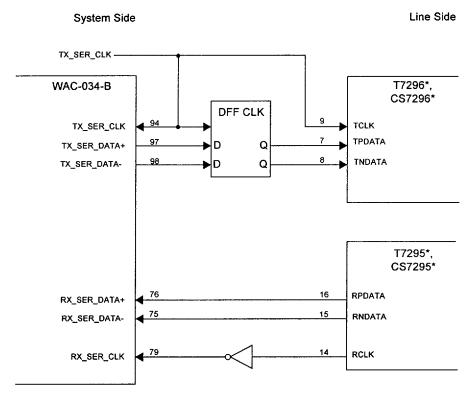

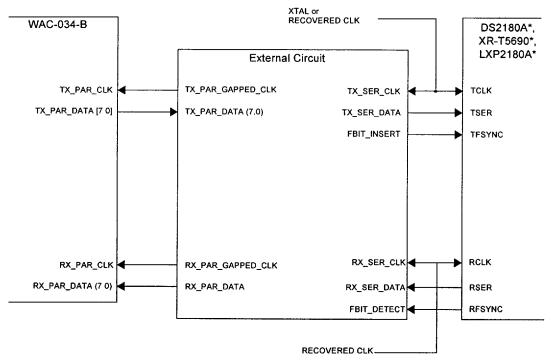

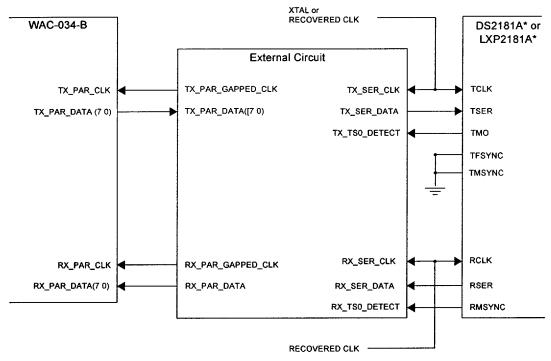

The WAC-034-B PDH ATM UNI Processor maps 53-byte ATM cells into a synchronous DS3, E3, or E4 payload. It is ideally suited for equipment in the wide area network, such as ATM switches, hubs, bridges, routers, workstations, and test equipment. This device can also be used with external circuitry in any application requiring a DS1 or E1 interface. Figure 1 shows a simple data flow diagram for DS3 applications.

#### ATM (UTOPIA) Interface RA\_DATA Cells TA\_DATA Celis TA\_FIFO RA FIFO TM\_CELL RM CELL RM OCD Processor Processor TO\_EXT\_IN RO\_EXT\_OUT PLCP Overhead PLCP Overhead TO\_ALARMS ➤ RO\_ALARMS Processor Processor TX\_DLINK\_DATA RX\_DLINK\_DATA DS3 Overhead **DS3 Overhead** TX\_ALARMS RX\_ALARMS Processor Processor TX DATA RX\_DATA (To LIU) DS3 Interface

Figure 1. Simple Data Flow Diagram of the WAC-034-B for DS3 Applications

Figure 2 shows a simple data flow diagram for E3/E4 applications.

#### ATM (UTOPIA) Interface RA\_DATA Cells TA\_DATA Cells RA\_FIFO TA\_FIFO TM\_CELL RM\_CELL RM\_OCD Processor Processor TO\_EXT\_IN ▶ RO\_EXT\_OUT E3/E4 Overhead E3/E4 Overhead TO\_ALARMS RO\_ALARMS Processor Processor TX\_DATA (To LIU) (From LIU)

Figure 2. Simple Data Flow Diagram of the WAC-034-B for E3/E4 Applications

E3/E4 Interface

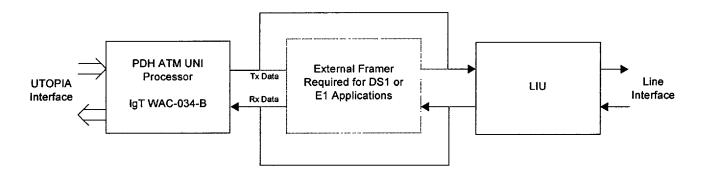

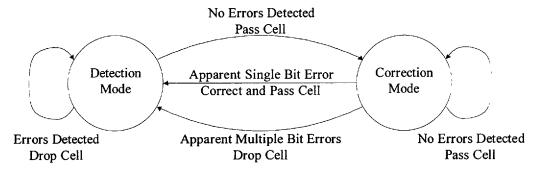

Figure 3 shows connection to a generic physical medium dependent layer.

Figure 3. Generic Physical Medium Connection

# **DS3 APPLICATION**

## 1. SYSTEM FEATURES

### 1. 1. Rates

DS3 (44.736 Mbps).

## 1. 2. Setup

Transmitter and receiver can be set up and accessed independently.

## 1. 3. Loopback

Local: TX\_SER\_DATA and TX\_SER\_CLK is fed back to RX\_SER\_DATA and RX\_SER\_CLK.

# 1. 4. Testability

- All outputs are tristatable.

- Boundary scan (JTAG) on all pins except the serial data and clock signals.

## 1. 5. Framing Format

#### 1. 5. 1. DS3 Format

The DS3 frame is composed of seven subframes. Table 1 and Table 2 show the overhead bits for the M13 and C-bit parity modes. Each subframe consists of eight blocks containing 85 bits each. The first bit in each block is a DS3 overhead bit.

X [84]  $C_{12}$ [84]  $C_{13}$ [84] [84] [84] [84] [84] [84]  $F_1$ X [84]  $F_1$ [84]  $C_{21}$ [84]  $F_0$ [84]  $C_{22}$ [84]  $F_0$ [84]  $C_{23}$ [84]  $F_1$ [84] [84]  $C_{32}$ [84] P [84] [84] [84] [84] [84] [84]  $F_1$  $C_{31}$  $F_0$  $F_0$  $C_{33}$  $F_1$ P  $F_0$  $C_{42}$  $C_{43}$ [84]  $F_1$ [84] [84] [84] [84]  $\mathbf{F}_{\mathbf{0}}$ [84] [84] [84]  $C_{41}$ [84] [84]  $M_0$ [84]  $F_1$ [84] [84]  $F_0$ [84] [84]  $F_0$  $C_{53}$ [84]  $F_1$  $C_{51}$  $C_{52}$ [84] [84] [84] [84]  $C_{62}$ [84] [84]  $C_{63}$ [84]  $\mathbf{F}_{1}$ [84]  $M_1$  $C_{61}$  $F_0$  $\mathbf{F_0}$  $F_0$ [84]  $F_1$ [84] C<sub>71</sub> [84] [84] C<sub>72</sub> [84]  $F_0$ [84]  $C_{73}$ [84]  $F_1$ [84]  $M_0$

Table 1. M13 DS3 Overhead Bits

#### NOTES:

- · Each row represents a subframe.

- $F_1F_0F_0F_1$  is the frame alignment signal.  $F_0 = 0$  and  $F_1 = 1$ .

- $M_0M_1M_0$  is the multiframe alignment signal.  $M_0 = 0$  and  $M_1 = 1$ .

- P is the parity information calculated over all information bits in the preceding DS3 frame. Both P-bits equal 1 if the digital sum of all information bits is 1. Both P-bits equal 0 if the sum is 0.

- The X-bits may be used to transmit in-service messages. In any one DS3 frame the two X-bits must be identical and may not change more than once per second.

- $C_{11}C_{12}C_{13}$  = stuffing indicators for DS2 input 1.

- $C_{21}C_{22}C_{23}$  = stuffing indicators for DS2 input 2.

- $C_{31}C_{32}C_{33}$  = stuffing indicators for DS2 input 3.

- $C_{41}C_{42}C_{43}$  = stuffing indicators for DS2 input 4.

- $C_{51}C_{52}C_{53}$  = stuffing indicators for DS2 input 5.

- $C_{61}C_{62}C_{63}$  = stuffing indicators for DS2 input 6.

- $C_{71}C_{72}C_{73}$  = stuffing indicators for DS2 input 7.

- [84] represents 84 information bits between every DS3 overhead bit.

AIC [84] X [84]  $\mathbf{F}_1$ [84] [84]  $F_0$ [84]  $N_a$ [84]  $F_0$ **FEAC** [84]  $F_1$ [84] X [84]  $\mathbf{F}_{1}$ [84] User DL [84]  $F_0$ [84] User DL [84]  $F_0$ [84] User DL [84]  $F_1$ [84] P [84]  $F_1$ [84] CP [84] [84] CP  $F_0$ [84]  $F_0$ [84] CP [84]  $F_1$ [84] P  $F_1$ [84] **FEBE** [84]  $F_1$ [84]  $F_0$ [84] **FEBE** [84]  $\mathbf{F}_{0}$ [84] **FEBE** [84] [84] DL [84] [84]  $\mathbf{F}_{\mathbf{I}}$ [84]  $F_0$ [84] DL[84] [84] DL $M_0$ [84]  $F_1$ [84]  $F_0$  $M_1$ [84]  $\mathbf{F_1}$ [84] User DL [84]  $F_0$ [84] User DL [84] [84] User DL [84]  $F_1$ [84]  $F_0$ [84] User DL [84]  $M_0$ [84]  $F_1$  $F_0$ [84] User DL [84] [84] User DL [84]  $F_0$  $\mathbf{F}_{\mathbf{1}}$ [84]

Table 2. C-bit Parity DS3 Overhead Bits

#### NOTES:

- Each row represents a subframe.

- $F_1F_0F_0F_1$  is the frame alignment signal.  $F_0 = 0$  and  $F_1 = 1$ .

- $M_0M_1M_0$  is the multiframe alignment signal.  $M_0 = 0$  and  $M_1 = 1$ .

- P is the parity information calculated over all information bits in the preceding DS3 frame. Both P-bits equal 1 if the digital sum of all information bits is 1. Both P-bits equal 0 if the sum is 0.

- The X-bits are used to transmit a Yellow Alarm. In any one DS3 frame the two X-bits must be identical and may not change more than once per second.

- C-bit definitions:

- AIC = Application Identification Channel = 1.

- $N_a$  = Reserved Network Application Bit = 1.

- FEAC = Far-End Alarm and Control Channel.

- DL = Data Link.

- User DL = User Defined Data Link = 1.

- CP = C-bit Parity.

- FEBE = Far-End Block Error.

- [84] represents 84 information bits between every DS3 overhead bit.

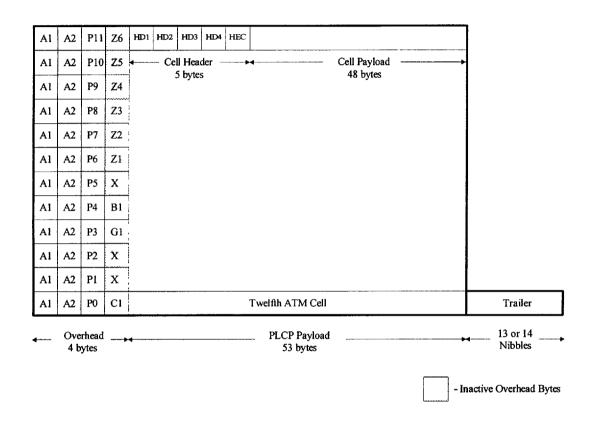

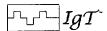

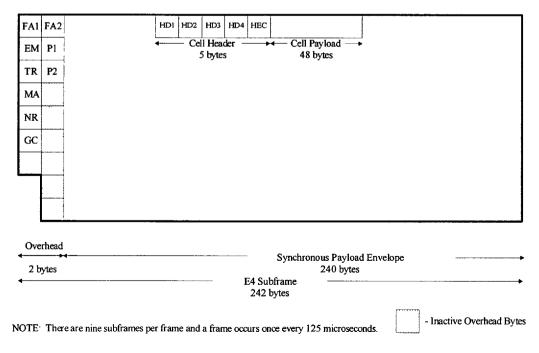

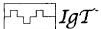

### 1. 5. 2. PLCP Format

The Physical Layer Convergence Protocol (PLCP) for DS3 is shown in Figure 4. *Inactive* overhead bytes (bytes not processed by the WAC-034-B) are shown in the shaded squares. These bytes are transmitted as  $00_h$  and are ignored by the receiver. *Active* overhead bytes (bytes processed by the WAC-034-B) are summarized in Table 3. The trailer may be 13 or 14 nibbles in length and is used to frequency justify the 125  $\mu$ s PLCP frame. The contents of each trailer nibble is 1100. Descriptions of the processing performed on each one of the active bytes is given in section "2. Transmitter Features" on page 10 and in section "3. Receiver Features" on page 12.

Figure 4. DS3 PLCP Format

Table 3 describes the values used for coding the DS3 overhead bytes. Bits are shown in parentheses; bit 7 is the most significant bit and is the first bit to be transmitted in the data stream, and bit 0 is the least significant bit and is the last bit to be transmitted in the data stream. For example, the first four bits of the G1 byte are indicated as G1(7:4). This numbering scheme maintains consistency between the pin descriptions and the microprocessor port register descriptions. Default values used by the transmitter are indicated by (def).

Table 3. Values for the DS3 Overhead Bytes

| Overhead Byte Location | Function                                                                                                                         | Value                                                                    |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Al                     | Frame alignment                                                                                                                  | F6 <sub>h</sub>                                                          |

| A2                     | Frame alignment                                                                                                                  | 28 <sub>h</sub>                                                          |

| P11                    | Path Overhead Identifier                                                                                                         | 2C <sub>h</sub>                                                          |

| P10                    | Path Overhead Identifier                                                                                                         | 29 <sub>h</sub>                                                          |

| Р9                     | Path Overhead Identifier                                                                                                         | 25 <sub>h</sub>                                                          |

| P8                     | Path Overhead Identifier                                                                                                         | 20 <sub>h</sub>                                                          |

| P7                     | Path Overhead Identifier                                                                                                         | 1C <sub>h</sub>                                                          |

| P6                     | Path Overhead Identifier                                                                                                         | 19 <sub>h</sub>                                                          |

| P5                     | Path Overhead Identifier                                                                                                         | 15 <sub>h</sub>                                                          |

| P4                     | Path Overhead Identifier                                                                                                         | 10 <sub>h</sub>                                                          |

| P3                     | Path Overhead Identifier                                                                                                         | 0D <sub>h</sub>                                                          |

| P2                     | Path Overhead Identifier                                                                                                         | 08 <sub>h</sub>                                                          |

| P1                     | Path Overhead Identifier                                                                                                         | 04 <sub>h</sub>                                                          |

| P0                     | Path Overhead Identifier                                                                                                         | 01 <sub>b</sub>                                                          |

| B1                     | Error monitoring                                                                                                                 | BIP-8                                                                    |

| G1(7:4)                | FEBE                                                                                                                             | B1 error count                                                           |

| G1(3)                  | No alarm Failure condition                                                                                                       | 0 (def)<br>1                                                             |

| G1(2:0)                | Inactive bits                                                                                                                    | 000                                                                      |

| C1                     | Identify first frame phase Identify second frame phase Identify third frame phase, no stuffing Identify third frame phase, stuff | FF <sub>h</sub><br>00 <sub>h</sub><br>66 <sub>h</sub><br>99 <sub>h</sub> |

### 2. TRANSMITTER FEATURES

#### 2. 1. General

#### 2. 1. 1. Data Insertion

The default values for all PLCP data, including the overhead, can be overwritten with a synchronous 8bit interface.

#### 2. 1. 2. Error Insertion

• Single and continuous error insertion capabilities are valid for all bytes specified as having a general error insertion feature.

#### 2. 1. 3. Automatic Alarm Generation

- Dedicated internal circuitry or an external signal will generate the appropriate alarm signal upon detection of an alarm condition (for example, a Far-End Block Error FEBE).

- · Software can force alarm signal generation.

#### 2. 2. ATM

- Provides a three cell deep, cell-by-cell FIFO to decouple system and line side clocks.

- Generates null cells with programmable headers and programmable one-byte payload patterns.

- Optionally generates Header Error Check (HEC) with error insertion on any bits.

- Optionally generates the HEC without the coset pattern.

- Optionally scrambles the cell payload.

- Counts the number of message cells transmitted.

- Detects transmit FIFO empty and begins sending a null cell immediately.

#### 2. 3. PLCP Overhead Processing

- Optionally disables PLCP overhead processing.

- Generates A1 and A2 with continuous error insertion on the most significant bit (bit 7) of the A1 and A2 bytes.

- Generates B1 (BIP-8) with error insertion on all 8 bits simultaneously.

- Generates Path Overhead Indentifier (POI) coding to index the adjacent Path Overhead (POH) bytes.

- Automatically generates G1 FEBE on reception of B1 byte errors.

- Generates G1 Remote Alarm Indication (RAI) when the G1\_RAI signal is asserted.

- Generates C1 code to indicate nibble stuffing cycle.

- Optionally generates external or looped nibble stuffing.

- Generates a frame pulse to indicate start-of-frame (TO\_FRAME).

- Synchronizes the frame format to an external frame sync signal (TO\_FRAME\_IN).

### 2. 4. DS3 Frame Overhead Processing

- Optionally generates C-bit parity or M13 framing.

- Generates frame bits (F-bits and M-bits) with single error insertion per frame (F-bits only).

- Generates X-bits with microprocessor control.

- Generates parity bits (P-bits) with single error insertion.

- Generates programmable FEAC codes.

- Generates C-bit Parity bits (CP-bits) with single error insertion.

- Automatically generates FEBEs when F-bit, M-bit, or CP-bit errors are received.

- Generates the Alarm Indication Signal (AIS) pattern. An AIS signal is defined as a signal with all of the following conditions:

- all C-bits are set to 0,

- both X-bits are set to 1, and

- the information bits are set to 1010 and synchronized to the framing bits.

- Generates the Idle signal pattern. An Idle signal is defined as a signal with all of the following conditions:

- all three C-bits in the subframe three are set to 0,

- both X-bits are set to 1, and

- the information bits are set to 1100 and synchronized to the framing bits.

- Generates a frame pulse to indicate start-of-frame (TX FRAME).

- Synchronizes the frame format to an external frame sync signal (TO FRAME IN).

## 2. 5. Line Interface Processing

- Generates Loss Of Signal (LOS), which forces the transmit data stream to 0.

- · Generates B3ZS coding.

- Optionally generates single Bipolar Violations (BPVs).

### 3. RECEIVER FEATURES

#### 3. 1. General

### 3. 1. 1. Plesiochronous Digital Hierarchy (PDH) Data Monitoring

Monitors the full descrambled PLCP data stream, including all the overhead bytes, through a synchronous 8-bit interface.

#### 3. 1. 2. Counters

- Counter length is 16 bits.

- Counters are latched synchronously and cleared when latched.

### 3. 1. 3. Alarms

- One hardware pin is associated with each alarm.

- One interrupt is generated with each alarm. Each interrupt has three microprocessor bits: mask, interrupt, and status.

#### 3. 2. ATM

- Provides a three cell deep, cell-by-cell FIFO to decouple system and line side clocks.

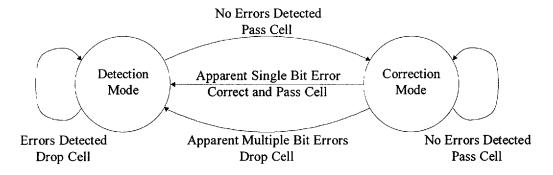

- Performs cell delineation by checking for HEC matches.

- Detects out-of-cell delineation (RM\_OCD) in accordance to ITU Recommendation I.432 (refer to "Appendix B. References" on page 123), where delta is 6 and alpha is 7.

- Detects FIFO overflow with RM\_FIFO\_OVERFLOW\_INTR.

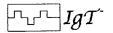

- Optionally corrects the first header containing a single apparent bit error (Correction Mode for ATM cell header processing).

- Optionally disables coset function in HEC calculation.

- · Optionally passes cells with invalid HECs.

- Optionally passes unassigned cells. (Unassigned cells have the following five header bytes, X000000XXX<sub>h</sub>, where X is any hexadecimal digit).

- Optionally passes data during receive out-of-cell delineation.

- · Optionally descrambles the cell payload.

- Counts complete cells written to the receive FIFO.

- Counts all cells with invalid HECs in Detection Mode for ATM cell header processing, and counts all

cells with uncorrectable HECs in Correction Mode.

### 3. 3. PLCP Overhead Processing

- · Optionally disables PLCP overhead processing.

- Detects Out-Of-Frame (RO OOF).

RO OOF is set if:

- An error is detected in both A1 and A2 bytes, or

- Two consecutive, invalid, and nonsequential POI bytes are detected.

RO\_OOF is reset if two consecutive valid A1 and A2 bytes with two consecutive, valid, and sequential POI bytes are detected.

Detects Loss-Of-Frame (RO\_LOF).

RO\_LOF is set if 1 ms of OOF is accumulated with fewer than 1 ms of in-frame between OOFs. RO LOF is reset if 12 consecutive ms of in-frame are detected.

- Counts A1, A2, and POI errors.

- Optionally counts B1 (BIP-8) errors individually or as a block.

- Detects G1 RAI.

- G1\_RAI is set if 10 consecutive G1 bytes are set to XXXX1XXX G1\_RAI is reset if 10 consecutive G1 bytes are set to XXXX0XXX

- Counts G1 FEBEs.

#### 3. 4. DS3 Frame Overhead Processing

- Detects Out\_Of\_Frame (RX\_OOF) with optional criteria.

- RX\_OOF is set if:

- Three out of 15 F-bits are in error, or

- Six out of 15 F-bits are in error, or

- · Two out of three M-bits are in error.

RX\_OOF is reset if two consecutive frames with correct 010 M-bit sequences are detected. Search for the M-bit sequences begins after detection of 15 consecutive error-free F-bits.

- Counts frame (F-bit and M-bit) errors.

- · Counts parity (P-bit) errors.

- Counts C-bit parity (CP-bit) errors.

- Counts FEBEs.

- Provides microprocessor access to X-bit status.

- Detects changes in Far-End Alarm and Control (FEAC) code and provides microprocessor access to FEAC code.

- Detects Yellow Alarm when both X-bits are 0.

- Detects the AIS 1010 signal condition. An AIS 1010 signal is defined as a signal with the following conditions:

- both X-bits are set to 1, and

- the information bits are set to 1010 and synchronized to the framing bits.

- Detects the AIS Stuck C-bit condition. An AIS Stuck C-bit condition is defined as a signal with the following conditions:

- all C-bits are set to 0, and

- both X-bits are set to 1.

- Detects the Idle signal pattern. An Idle signal is defined as a signal with the following conditions:

- all three C-bits in subframe three are set to 0,

- both X-bits are set to 1, and

- the information bits are set to 1100 and synchronized to the framing bits.

### 3. 5. Line Interface Processing

- Detects Loss-Of-Signal (RX\_LOS).

- RX\_LOS is valid if incoming data is stuck at all 0s or all 1s for a period of  $175 \pm 75$  contiguous bit positions.

- RX\_LOS is reset on the detection of an average pulse density of at least 33 percent over a period of 175  $\pm$  75 contiguous bit positions.

- Provides B3ZS decoding.

- · Counts BPVs as line code violations.

- Optionally counts excess 0s as line code violations.

# 4. PIN DESCRIPTIONS

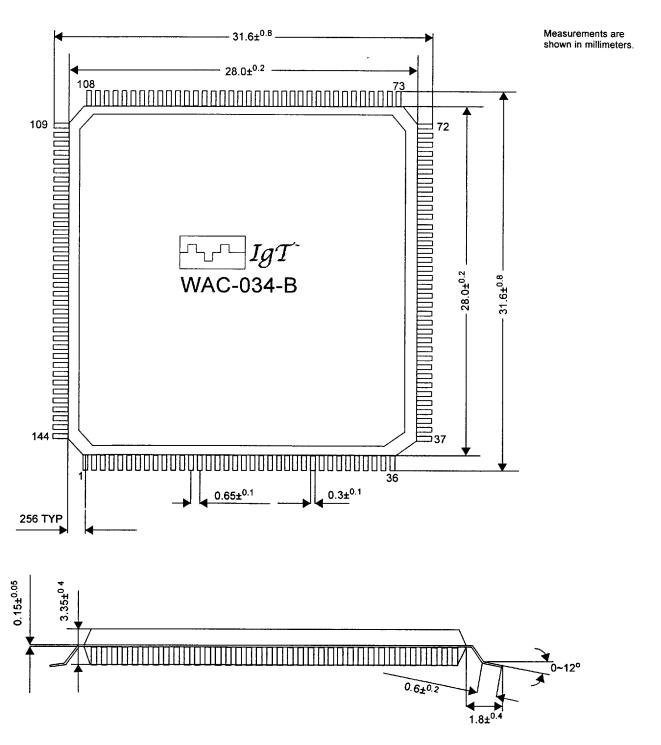

## 4. 1. Package Diagram

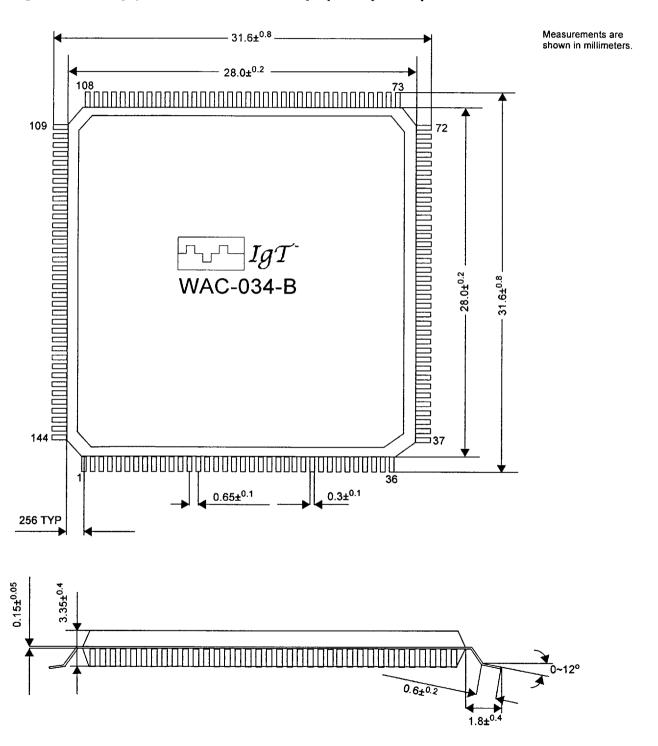

Figure 5 shows the physical dimensions for the 144-pin plastic quad flat pack used for the WAC-034-B.

Figure 5. WAC-034-B Package (PQFP-144)

# 4. 2. Pin Locations

Refer to Table A-1 on page 121 for prefix name explanations.

Table 4. Pin Locations

| Pin | Name          | Pin | Name           | Pin | Name         | Pin | Name           |

|-----|---------------|-----|----------------|-----|--------------|-----|----------------|

| 1   | /CS           | 37  | VCC            | 73  | VCC          | 109 | VCC            |

| 2   | /RD           | 38  | RPHY_SOC       | 74  | SER_IO_EN    | 110 | E3 OUT         |

| 3   | /WR           | 39  | RPHY_CLAV      | 75  | RX_SER_DATA- | 111 | E3 OUT         |

| 4   | A0            | 40  | /RPHY_AEMPTY   | 76  | RX_SER_DATA+ | 112 | TX_PAR_CLK_OUT |

| 5   | A1            | 41  | RO_TR_EN       | 77  | GND          | 113 | TO_FRAME       |

| 6   | A2            | 42  | SCAN_TCK       | 78  | N/C          | 114 | TO_FRAME_IN    |

| 7   | A3            | 43  | SCAN_TMS       | 79  | RX_SER_CLK   | 115 | TO_INSERT      |

| 8   | A4            | 44  | SCAN_TDI       | 80  | GND          | 116 | TO_EXT_IN0     |

| 9   | A5            | 45  | SCAN_TDO       | 81  | N/C          | 117 | TO_EXT_IN1     |

| 10  | N/C           | 46  | RO_EXT_OUT0    | 82  | E3 IN        | 118 | TO_EXT_IN2     |

| 11  | N/C           | 47  | RO_EXT_OUT1    | 83  | E3 IN        | 119 | TO_EXT_IN3     |

| 12  | D0            | 48  | RO_EXT_OUT2    | 84  | E3 IN        | 120 | TO_EXT_IN4     |

| 13  | D1            | 49  | RO_EXT_OUT3    | 85  | E3 IN        | 121 | TO_EXT_IN5     |

| 14  | D2            | 50  | RO_EXT_OUT4    | 86  | E3 IN        | 122 | TO_EXT_IN6     |

| 15  | D3            | 51  | RO_EXT_OUT5    | 87  | E3 IN        | 123 | TO_EXT_IN7     |

| 16  | D4            | 52  | RO_EXT_OUT6    | 88  | E3 IN        | 124 | TX_DLINK_DATA  |

| 17  | D5            | 53  | RO_EXT_OUT7    | 89  | E3 IN        | 125 | TX_DLINK_CLK   |

| 18  | GND           | 54  | GND            | 90  | E3 IN 126    | 126 | GND            |

| 19  | VCC           | 55  | VCC            | 91  | N/C          | 127 | VCC            |

| 20  | D6            | 56  | RM_OCD         | 92  | GND          | 128 | TO_RAI         |

| 21  | D7            | 57  | RX_DLINK_DATA  | 93  | TX_AIS       | 129 | ADDR_LAT_EN    |

| 22  | INTR          | 58  | /TPHY_AEMPTY   | 94  | TX_SER_CLK   | 130 | TX_FRAME       |

| 23  | /RESET        | 59  | RX_DLINK_CLK   | 95  | VCC          | 131 | /TPHY_WRITE_EN |

| 24  | OUTPUT_EN     | 60  | RX_OOF         | 96  | GND          | 132 | TPHY_SOC       |

| 25  | RPHY_DATA0    | 61  | RO_EN          | 97  | TX_SER_DATA+ | 133 | TPHY_CLK       |

| 26  | RPHY_DATA1    | 62  | RX_FRAME       | 98  | TX_SER_DATA- | 134 | TPHY_DATA0     |

| 27  | RPHY_DATA2    | 63  | RO_RAI         | 99  | GND          | 135 | TPHY_DATA1     |

| 28  | RPHY_DATA3    | 64  | RX_AIS         | 100 | VCC          | 136 | TPHY_DATA2     |

| 29  | GND           | 65  | GND            | 101 | E3 IN        | 137 | TPHY_DATA3     |

| 30  | RPHY_DATA4    | 66  | RX_LOS         | 102 | E3 OUT       | 138 | TPHY_DATA4     |

| 31  | RPHY_DATA5    | 67  | RO_OOF         | 103 | E3 OUT       | 139 | TPHY_DATA5     |

| 32  | RPHY_DATA6    | 68  | RO_LOF         | 104 | E3 OUT       | 140 | TPHY_DATA6     |

| 33  | RPHY_DATA7    | 69  | RO_FRAME       | 105 | E3 OUT       | 141 | TPHY_DATA7     |

| 34  | /RPHY_READ_EN | 70  | RX_PAR_CLK_OUT | 106 | E3 OUT       | 142 | TO_EXT_STUFF   |

| 35  | RPHY_CLK      | 71  | /SCAN_TRSTN    | 107 | E3 OUT       | 143 | TPHY_CLAV      |

| 36  | GND           | 72  | N/C            | 108 | GND          | 144 | GND            |

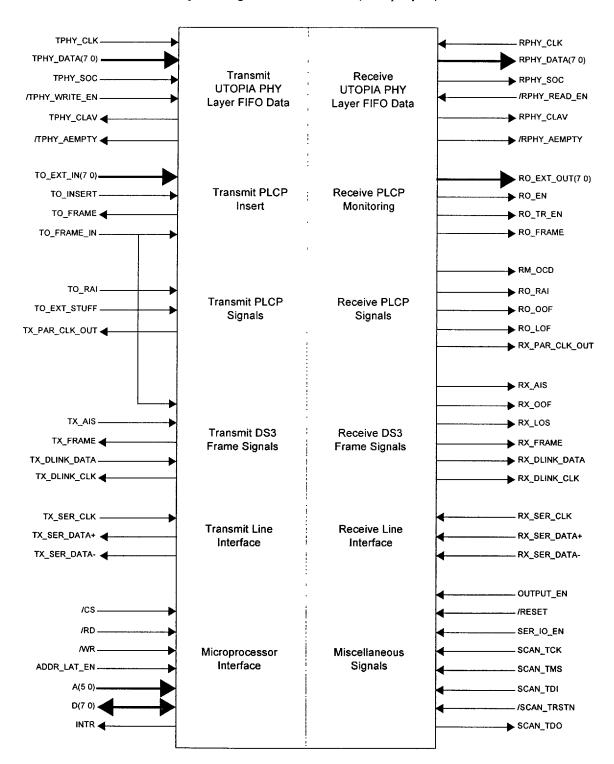

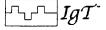

Figure 6 displays the pins of the WAC-034-B grouped by logical functions. Arrows heading toward the device are input pins, those heading away from the device are output pins, and those heading both toward and away from the device are bidirectional pins. Larger arrows are buses (multiple pins).

Figure 6. WAC-034-B Logical Pin Diagram for DS3 Applications

# 4. 3. Pin Descriptions

Refer to Table A-1 on page 121 for pin name prefix explanations.

# 4. 3. 1. UTOPIA PHY Layer FIFO Data Signals

# 4. 3. 1. 1. Transmit UTOPIA PHY Layer FIFO Data Signals

Table 5. Transmit UTOPIA PHY Layer FIFO Data Signals

| Signal Name    | Pin #     | Туре | Description                                                                                                                                                                                                                                                               |

|----------------|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPHY_CLK       | 133       | In   | Transmit UTOPIA PHY Layer Clock is used to write data from the ATM layer into the transmit ATM FIFO.                                                                                                                                                                      |

| TPHY_DATA(7:0) | 141 - 134 | In   | Transmit UTOPIA PHY Layer Data Bits 7 to 0 are part of the 8-bit ATM data byte being written into the transmit ATM FIFO. Bit 7 is the first bit transmitted once the parallel byte is serialized. Bit 0 is the last bit transmitted once the parallel byte is serialized. |

| TPHY_SOC       | 132       | In   | Transmit UTOPIA PHY Layer Start-Of-Cell indicates that the data being written into the transmit ATM FIFO is the first byte of the 53-byte ATM cell.                                                                                                                       |

| /TPHY_WRITE_EN | 131       | In   | Transmit UTOPIA PHY Layer Write Enable is an active low signal used to enable writing data into the transmit ATM FIFO.                                                                                                                                                    |

| TPHY_CLAV      | 143       | Out  | Transmit UTOPIA PHY Layer Cell Available is an active high signal used to indicate that the transmit ATM FIFO can accept a complete cell. When this signal is low, the transmit ATM FIFO is able to accept at most four more bytes of data before it becomes full.        |

| /TPHY_AEMPTY   | 58        | Out  | Transmit UTOPIA PHY Layer FIFO Almost Empty is an active low signal used to indicate that the transmit ATM FIFO has fewer than 51 bytes of data left. Note that this signal is synchronous to TX_PAR_CLK and not to TPHY_CLK.                                             |

# 4. 3. 1. 2. Receive UTOPIA PHY Layer FIFO Data Signals

Table 6. Receive UTOPIA PHY Layer FIFO Data Signals

| Signal Name                      | Pin #              | Туре | Description                                                                                                                                                                                                                                                    |

|----------------------------------|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RPHY_CLK                         | 35                 | In   | Receive UTOPIA PHY Layer Clock is used by the ATM layer to read data from the receive ATM FIFO.                                                                                                                                                                |

| RPHY_DATA(7:4)<br>RPHY_DATA(3:0) | 33 - 30<br>28 - 25 | Out  | Receive UTOPIA PHY Layer Data Bits 7 to 0 are part of the 8-bit ATM data byte being read from the receive ATM FIFO. Bit 7 is the first bit received once the parallel byte is serialized. Bit 0 is the last bit received once the parallel byte is serialized. |

| RPHY_SOC                         | 38                 | Out  | Receive UTOPIA PHY Layer Start-of-Cell indicates that the data being read from the receive ATM FIFO is the first byte of the 53-byte ATM cell.                                                                                                                 |

| /RPHY_READ_EN                    | 34                 | In   | Receive UTOPIA PHY Layer Read Enable is an active low signal used to indicate that the ATM layer is reading data from the receive ATM FIFO.                                                                                                                    |

| RPHY_CLAV                        | 39                 | Out  | Receive UTOPIA PHY Layer Cell Available is an active high signal used to indicate that the receive ATM FIFO contains a full cell (53 or more bytes).                                                                                                           |

| /RPHY_AEMPTY                     | 40                 | Out  | Receive UTOPIA PHY Layer Almost Empty is an active low signal used to indicate that the receive ATM FIFO contains fewer than 50 bytes.                                                                                                                         |

# 4. 3. 2. PLCP Signals

# 4. 3. 2. 1. Transmit PLCP Insert Signals

Table 7. Transmit PLCP Insert Signals

| Signal Name | Pin# | Туре | Description                                                                                                                                                                                                                                                                                                                                         |

|-------------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TO_EXT_IN7  | 123  | In   | Transmit Overhead External In Bit 7 is bit 7 of the 8-bit parallel data that can overwrite the default PLCP data stream. This pin can also be used to overwrite GFC3 of each cell when GFC_EN (A=00 <sub>h</sub> ,D5) is a 1 and GFC_MASK3 (A=0A <sub>h</sub> , D7) is a 1. This is the first bit transmitted once the parallel byte is serialized. |

| TO_EXT_IN6  | 122  | In   | Transmit Overhead External In Bit 6 is bit 6 of the 8-bit parallel data that can overwrite the default PLCP data stream. This pin can also be used to overwrite GFC2 of each cell when GFC_EN (A=00 <sub>h</sub> , D5) is a 1 and GFC_MASK2 (A=0A <sub>h</sub> , D6) is a 1.                                                                        |

| TO_EXT_IN5  | 121  | In   | Transmit Overhead External In Bit 5 is bit 5 of the 8-bit parallel data that can overwrite the default PLCP data stream. This pin can also be used to overwrite GFC1 of each cell when GFC_EN (A=00 <sub>h</sub> , D5) is a 1 and GFC_MASK1 (A=0A <sub>h</sub> , D5) is a 1.                                                                        |

| TO_EXT_IN4  | 120  | In   | Transmit Overhead External In Bit 4 is bit 4 of the 8-bit parallel data that can overwrite the default PLCP data stream. This pin can also be used to overwrite GFC0 of each cell when GFC_EN (A=00 <sub>h</sub> , D5) is a 1 and GFC_MASK0 (A=0A <sub>h</sub> , D4) is a 1.                                                                        |

Table 7. Transmit PLCP Insert Signals (Continued)

| Signal Name    | Pin #     | Туре | Description                                                                                                                                                                                                   |

|----------------|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TO_EXT_IN(3:0) | 119 - 116 | In   | Transmit Overhead External In Bits 3 to 0 are bits 3 to 0 of the 8-bit parallel data that can overwrite the default PLCP data stream. Bit 0 is the last bit transmitted once the parallel byte is serialized. |

| TO_INSERT      | 115       | In   | Transmit Overhead Insert indicates that the current Transmit Overhead External In (TO_EXT_IN) byte should overwrite the default PLCP data stream.                                                             |

| TO_FRAME       | 113       | Out  | Transmit Overhead Frame is an active high signal which indicates that a PLCP frame has been transmitted.                                                                                                      |

| TO_FRAME_IN    | 114       | In   | Transmit Overhead Frame Input is an active high signal which can be asserted to synchronize the PLCP and DS3 frame generators to an external event.                                                           |

# 4. 3. 2. 2. Transmit PLCP Signals

Table 8. Transmit PLCP Signals

| Signal Name    | Pin # | Type | Description                                                                                                                                                       |

|----------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TO_RAI         | 128   | In   | Transmit Overhead Remote Alarm Indication inserts RAI into the transmit data stream.                                                                              |

| TO_EXT_STUFF   | 142   | In   | Transmit Overhead External Stuff indicates that stuffing should occur in the third frame of the PLCP when the TO_STUFF_LOOP (A=0B <sub>b</sub> , D3) is disabled. |

| TX_PAR_CLK_OUT | 112   | Out  | Transmit Parallel Clock Out is equivalent to Transmit Serial Clock (TX_SER_CLK) divided by eight.                                                                 |

# 4. 3. 2. 3. Receive PLCP Monitoring Signals

Table 9. Receive PLCP Monitoring Signals

| Signal Name | Pin # | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RO_EXT_OUT7 | 53    | Out  | Receive Overhead External Out Bit 7 is bit 7 of the 8-bit PLCP data when GFC_EN (Addr=00h, D5) is a 0. This pin is used to report GFC3 of each valid cell when GFC_EN is a 1. This bit is the first bit received once the parallel byte is serialized. If GFC_EN is a 0, then the Receive Overhead External Out signals, in conjunction with Receive Overhead Frame (RO_FRAME), Receive Overhead Enable (RO_EN), and Receive Overhead Trailer Enable (RO_TR_EN), can be used to monitor the PLCP overhead data. |

| RO_EXT_OUT6 | 52    | Out  | Receive Overhead External Out Bit 6 is bit 6 of the 8-bit PLCP data when GFC_EN (Addr=00 <sub>h</sub> , D5) is a 0. This pin is used to report GFC2 of each valid cell when GFC_EN is a 1.                                                                                                                                                                                                                                                                                                                      |

| RO_EXT_OUT5 | 51    | Out  | Receive Overhead External Out Bit 5 is bit 5 of the 8-bit PLCP data when GFC_EN (Addr=00 <sub>h</sub> , D5) is a 0. This pin is used to report GFC1 of each valid cell when GFC_EN is a 1.                                                                                                                                                                                                                                                                                                                      |

Table 9. Receive PLCP Monitoring Signals (Continued)

| Signal Name     | Pin#    | Туре | Description                                                                                                                                                                                                                                   |

|-----------------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RO_EXT_OUT4     | 50      | Out  | Receive Overhead External Out Bit 4 is bit 4 of the 8-bit PLCP data when GFC_EN (Addr=00 <sub>h</sub> , D5) is a 0. This pin is used to report GFC0 of each valid cell when GFC_EN is a 1.                                                    |

| RO_EXT_OUT(3:0) | 49 - 46 | Out  | Receive Overhead External Out Bits 3 to 0 are bits 3 to 0 of the 8-bit PLCP data. Bit 0 is the last bit received once the parallel byte is serialized.                                                                                        |

| RO_EN           | 61      | Out  | Receive Overhead Enable indicates that the current Receive Overhead External Out (RO_EXT_OUT) is a PLCP overhead byte.                                                                                                                        |

| RO_TR_EN        | 41      | Out  | Receive Overhead Trailer Enable indicates that the current Receive Overhead External Out (RO_EXT_OUT) contains the trailer nibbles.                                                                                                           |

| RO_FRAME        | 69      | Out  | Receive Overhead Frame is an active high signal asserted to indicate that a PLCP framing pattern was detected. This frame pulse is asserted three clock cycles after the frame byte A2 appears at Receive Overhead External Out (RO_EXT_OUT). |

# 4. 3. 2. 4. Receive PLCP Signals

Table 10. Receive PLCP Signals

| Signal Name    | Pin # | Туре | Description                                                                                                              |

|----------------|-------|------|--------------------------------------------------------------------------------------------------------------------------|

| RM_OCD         | 56    | Out  | Receive Mapper Out-of-Cell Delineation indicates that the receiver has lost ATM cell delineation.                        |

| RO_RAI         | 63    | Out  | Receive Overhead Remote Alarm Indication indicates that the receiver is detecting RAI.                                   |

| RO_OOF         | 67    | Out  | Receive Overhead Out-Of-Frame indicates that the receiver for the PLCP layer is out-of-frame.                            |

| RO_LOF         | 68    | Out  | Receive Overhead Loss-Of-Frame indicates that the receiver for the PLCP layer has entered the loss-of-frame alarm state. |

| RX_PAR_CLK_OUT | 70    | Out  | Receive Parallel Clock Out is equivalent to Receive Serial Clock (RX_SER_CLK) divided by eight.                          |

# 4. 3. 3. DS3 Frame Signals

# 4. 3. 3. 1. Transmit DS3 Frame Signals

Table 11. Transmit DS3 Frame Signals

| Signal Name   | Pin# | Туре | Description                                                                                                                                       |

|---------------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| TX_AIS        | 93   | In   | Transmit Alarm Indication Signal inserts the AIS into the transmit data stream.                                                                   |

| TX_FRAME      | 130  | Out  | Transmit Frame is an active high signal which indicates that a DS3 frame has been transmitted.                                                    |

| TX_DLINK_DATA | 124  | In   | Transmit Data Link Data is data inserted from an external source for transmission on the DS3 data link (the C-bits in subframe 5).                |

| TX_DLINK_CLK  | 125  | Out  | Transmit Data Link Clock is a 28.2 kHz clock used by external circuitry to generate LAP-D formatted packets for data link channel communications. |

# 4. 3. 3. 2. Receive DS3 Frame Signals

Table 12. Receive DS3 Frame Signals

| Signal Name   | Pin # | Туре | Description                                                                                                                                              |

|---------------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX_AIS        | 64    | Out  | Receive Alarm Indication Signal indicates that the receiver is detecting AIS.                                                                            |

| RX_OOF        | 60    | Out  | Receive Out-of-Frame indicates that the DS3 framer is out-of-frame.                                                                                      |

| RX_LOS        | 66    | Out  | Receive Loss-of-Signal indicates that the receiver is detecting loss-of-signal (the incoming data is stuck at 1 or 0).                                   |

| RX_FRAME      | 62    | Out  | Receive Frame is an active high signal that marks the location of the first bit of the DS3 frame within the Receive PHY Layer Serial Data (RX_SER_DATA). |

| RX_DLINK_DATA | 57    | Out  | Receive Data Link Data is the C-bits which have been extracted from subframe 5 of each incoming DS3 frame.                                               |

| RX_DLINK_CLK  | 59    | Out  | Receive Data Link Clock is a 28.2 kHz clock which clocks out the Receive Data-Link Data (RX_DLINK_DATA).                                                 |

# 4. 3. 4. Line Interface Signals

# 4. 3. 4. 1. Transmit Line Interface Signals

Table 13. Transmit Line Interface Signals

| Signal Name  | Pin # | Туре | Description                                                                                                                                                    |

|--------------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX_SER_CLK   | 94    | In   | Transmit Serial Clock is the serial clock used to generate Transmit Serial Data (TX_SER_DATA). This clock's frequency is 44.736 MHz for DS3.                   |

| TX_SER_DATA+ | 97    | Out  | Transmit Serial Data Plus is the Non-Return to Zero (NRZ) data when Bipolar is disabled, and represents a positive B3ZS-encoded pulse when Bipolar is enabled. |

| TX_SER_DATA- | 98    | Out  | Transmit Serial Data Minus is the inverted NRZ data when bipolar is disabled, and represents a negative B3ZS-encoded pulse when bipolar is enabled.            |

# 4. 3. 4. 2. Receive Line Interface Signals

Table 14. Receive Line Interface Signals

| Signal Name  | Pin # | Type Description |                                                                                                                                                                                                                             |

|--------------|-------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX_SER_CLK   | 79    | In               | Receive Serial Clock is the serial clock used to write serial data into the receiver. This clock's frequency is 44.736 MHz for DS3.                                                                                         |

| RX_SER_DATA+ | 76    | In               | Receive Serial Data Plus is the serial data stream that is written into the receiver. This signal is NRZ data when bipolar is disabled, and represents the positive half of the B3ZS encoded pulse when Bipolar is enabled. |

| RX_SER_DATA- | 75    | In               | Receive Serial Data Minus is the negative half of the B3ZS encoded signal that is written into the receiver when Bipolar is enabled.                                                                                        |

# 4. 3. 5. Microprocessor Interface Signals

Table 15. Microprocessor Interface Signals

| Signal Name      | Pin#               | Туре | Description                                                                                                                                                                                                                                                              |

|------------------|--------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /CS              | 1                  | In   | Chip Select is an active low signal used to select the device.                                                                                                                                                                                                           |

| /RD              | 2                  | In   | Read is an active low read signal from the external microprocessor.                                                                                                                                                                                                      |

| /WR              | 3                  | In   | Write is an active low write signal from the external microprocessor.                                                                                                                                                                                                    |

| ADDR_LAT_EN      | 129                | In   | Address Latch Enable is used to latch the value of the bus. A high value enables the internal transparent latches on the address bus. The value on the address bus is latched on the falling edge of address latch enable. If not used, this signal should be tied high. |

| A(5:0)           | 9 - 4              | In   | Address Bits 5 to 0 are bits 5 to 0 of the 6-bit microprocessor address bus.                                                                                                                                                                                             |

| D(7:6)<br>D(5:0) | 21 - 20<br>17 - 12 | Bi   | Data Bits 7 to 0 are bits 7 to 0 of the 8-bit microprocessor data bus.                                                                                                                                                                                                   |

| INTR             | 22                 | Out  | Interrupt goes high when an alarm condition is detected. Each condition is independently maskable. Interrupt goes low after all INTR read ports are read.                                                                                                                |

# 4. 3. 6. Miscellaneous Signals

Table 16. Miscellaneous Signals

| Signal Name | Pin # | Type | Description                                                                                                                                                                                                                                                                                                                                    |

|-------------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUTPUT_EN   | 24    | In   | Output Enable is an active high signal used to enable all output signals. A low on this signal forces all output pins into a high impedance state.                                                                                                                                                                                             |

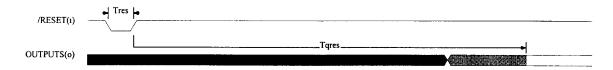

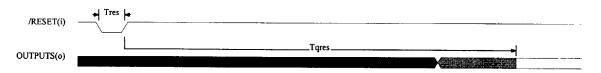

| /RESET      | 23    | In   | Reset is an active low signal used to force all microprocessor write ports to the default setting, and to reset both the transmitter and the receiver.                                                                                                                                                                                         |

| SER_IO_EN   | 74    | In   | Serial Input/Output Enable is used to enable the serial PDH section input/output streams. When Serial Input/Output Enable is high, the PDH interface is configured to handle serial I/O. When Serial Input/Output Enable is low, the PDH interface is configured to handle parallel I/O. For DS3, Serial Input/Output Enable must be set high. |

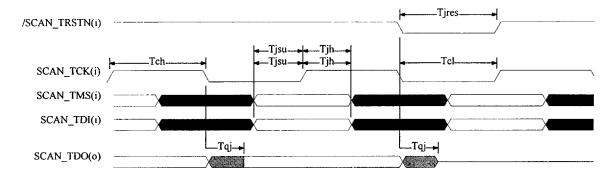

| SCAN_TCK    | 42    | In   | Scan Test Clock is an independent clock used to drive the internal boundary scan test logic. This signal should be connected to +5 volts through a pull-up resistor.                                                                                                                                                                           |

| SCAN_TMS    | 43    | In   | Scan Test Mode Select controls the operation of the internal boundary scan test logic. This signal should be connected to +5 volts through a pull-up resistor.                                                                                                                                                                                 |

| SCAN_TDI    | 44    | In   | Scan Test Data Input is the serial input for boundary scan test data and instruction bits. This signal should be connected to +5 volts through a pull-up resistor.                                                                                                                                                                             |

| /SCAN_TRSTN | 71    | In   | Scan Test Reset is an active low signal used to reset the internal boundary scan test logic. When not using boundary scan, this signal should be connected to ground through a pull-down resistor.                                                                                                                                             |

| SCAN_TDO    | 45    | Out  | Scan Test Data Output is the serial output for boundary scan test data.                                                                                                                                                                                                                                                                        |

Table 16. Miscellaneous Signals (Continued)

| Signal Name | Pin #                                                             | Туре | Description                                                                                                                                      |

|-------------|-------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC         | 19, 37, 55,<br>73, 95,<br>100, 109,<br>127                        | In   | Supply voltage 5 ± 0.25 volts.                                                                                                                   |

| GND         | 18, 29, 36,<br>54, 65, 77,<br>80, 92, 96,<br>99, 108,<br>126, 144 | In   | Ground.                                                                                                                                          |

| N/C         | 10, 11, 72,<br>78, 81, 91                                         |      | No connection. All no-connection pins should be connected to ground through a resistor to maintain compatibility with future hardware revisions. |

| E3 IN       | 82, 83, 84,<br>85, 86, 87,<br>88, 89, 90,<br>101                  | In   | E3 inputs are input signals used for different applications. All E3 input pins should be connected to ground through a resistor.                 |

| E3 OUT      | 102, 103,<br>104, 105,<br>106, 107,<br>110, 111                   | Out  | E3 outputs are output signals used for different applications. Leave all E3 outputs unconnected.                                                 |

# 5. PHYSICAL CHARACTERISTICS

Table 17. Absolute Maximum Ratings

| Symbol           | Parameter                  | Conditions                        | Min  | Max | Unit |

|------------------|----------------------------|-----------------------------------|------|-----|------|

| V <sub>cc</sub>  | Supply voltage             | With respect to GND               | -0.3 | 6.5 | V    |

| I <sub>out</sub> | DC output current, per pin | All outputs except TX_SER_DATA+/- | -12  | 12  | mA   |

| Iout             | DC output current, per pin | TX_SER_DATA+/-                    | -25  | 50  | mA   |

| T <sub>stg</sub> | Storage temperature        |                                   | -65  | 150 | °C   |

**Table 18. Recommended Operating Conditions**

| Symbol          | Parameter             | Conditions | Min  | Max             | Unit |

|-----------------|-----------------------|------------|------|-----------------|------|

| V <sub>cc</sub> | Supply voltage        |            | 4.75 | 5.25            | V    |

| V <sub>t</sub>  | Input voltage         |            | 0    | V <sub>cc</sub> | V    |

| V <sub>o</sub>  | Output voltage        |            | 0    | $V_{cc}$        | V    |

| T <sub>A</sub>  | Operating temperature |            | -40  | 85              | °C   |

| t <sub>R</sub>  | Input rise time       | •          |      | 10              | ns   |

| t <sub>F</sub>  | Input fall time       |            |      | 10              | ns   |

Table 19. DC Operating Conditions

| Symbol            | Parameter                                         | Conditions                                   | Min                  | Тур        | Max | Unit     |

|-------------------|---------------------------------------------------|----------------------------------------------|----------------------|------------|-----|----------|

| V <sub>ITH</sub>  | High-level TTL input voltage                      | All TTL inputs except clocks                 | 2.0                  |            |     | V        |

| V <sub>ITL</sub>  | Low-level TTL input voltage                       | All TTL inputs except clocks                 |                      |            | 0.8 | V        |

| V <sub>ISH</sub>  | High-level Schmitt-triggered<br>TTL input voltage | All TTL clock inputs                         |                      |            | 2.4 | V        |

| V <sub>ISL</sub>  | Low-level Schmitt-triggered<br>TTL input voltage  | All TTL clock inputs                         | 0.6                  |            |     | V        |

| V <sub>IHys</sub> | Hysteresis Schmitt-triggered TTL input voltage    | All TTL clock inputs                         | 0.1                  |            |     |          |

| V <sub>осні</sub> | CMOS high-level output voltage                    | I <sub>OL</sub> = -1 mA DC                   | V <sub>cc</sub> =0.4 |            |     |          |

| Vocli             | CMOS low-level output voltage                     | I <sub>OL</sub> = 2 mA DC                    |                      |            | 0.4 |          |

| V <sub>OCH4</sub> | CMOS high-level output voltage                    | I <sub>OH</sub> = -8 mA DC<br>TX_SER_DATA+/- | V <sub>cc</sub> =0.4 |            |     | V        |

| V <sub>ocl4</sub> | CMOS low-level output voltage                     | I <sub>OL</sub> = 24 mA DC<br>TX_SER_DATA+/- |                      |            | 0.4 | V        |

| I <sub>TYP</sub>  | Typical operating current                         | 139.264 MHz, parallel<br>44.736 MHz, serial  |                      | 215<br>180 |     | mA<br>mA |

NOTES: •  $V_{cc}$ = 5 V ± 5%,  $T_A$  = -40° C to 85° C for industrial use • Typical values are  $T_A$  = 25° C and  $V_{cc}$  = 5 V.

Table 20. Capacitance

| Symbol           | Parameter          | Conditions | Min | Max | Unit |

|------------------|--------------------|------------|-----|-----|------|

| C <sub>IN</sub>  | Input capacitance  |            |     | 10  | pF   |

| C <sub>out</sub> | Output capacitance |            |     | 6   | pF   |

## 6. TIMING DIAGRAMS

All pin names are described in section "4. 3. Pin Descriptions" starting on page 18. Refer to Table A-1 on page 121 for PDH pin name prefix explanations. Unless otherwise indicated, all output timing delays assume a capacitive loading of 30 pF.

### 6. 1. Transmitter Timing

## 6. 1. 1. UTOPIA PHY Layer FIFO Input

The transmit UTOPIA PHY layer FIFO timing signals are compatible with the UTOPIA cell-by-cell specification (refer to "Appendix B. References" on page 123). Table 21 indicates the transmit FIFO signal names and their corresponding UTOPIA designations.

| Signal Name    | UTOPIA Name    |

|----------------|----------------|

| TPHY_DATA      | TxData         |

| TPHY_SOC       | TxSOC          |

| /TPHY_WRITE_EN | TxEnb*         |

| TPHY_CLAV      | TxFull*/TxClav |

| TPHY_CLK       | TxClk          |

| TO_FRAME       | TxRef*         |

| /TPHY_AEMPTY   | Not Available  |

| Not Available  | TxPrty         |

Table 21. Transmit Signal Names and Corresponding UTOPIA Designations

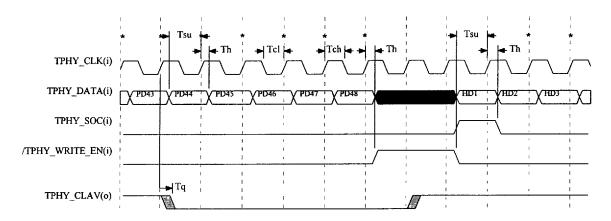

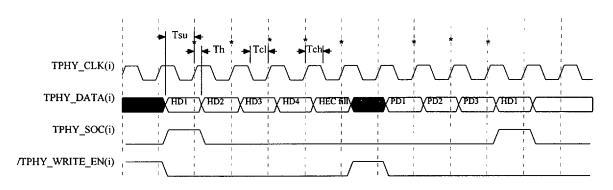

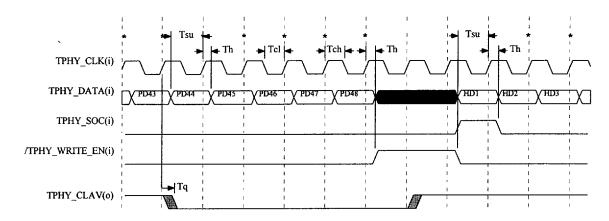

Figure 7 and Figure 8 display the data input format for the internal transmit UTOPIA PHY layer FIFO. The parameter symbols used in Figure 7 and Figure 8 are defined in the table that follows Figure 8. Table 22 defines the contents of the TPHY\_DATA bytes. The transmitter accepts data from the TPHY\_DATA pins on the rising edge of TPHY\_CLK only when /TPHY\_WRITE\_EN is asserted (low). The transmit ATM FIFO indicates that it has room to accept a full cell by asserting TPHY\_CLAV. TPHY\_CLAV will be deasserted (low) when the FIFO has accepted the 43rd payload data byte of the third cell. The clock cycles on which data is accepted are marked by an asterisk.

The start-of-cell marker, TPHY\_SOC, is asserted when the first byte of the header is written into the FIFO. Under normal circumstances, the TPHY\_SOC should be asserted once for every 53 bytes written into the FIFO. If more than 53 bytes are written into the FIFO before the next TPHY\_SOC is asserted, the transmitter will ignore all bytes after the 53rd byte until the next TPHY\_SOC. If a cell with fewer than 53 bytes (a runt cell) is written into the FIFO before the next TPHY\_SOC is asserted, the transmitter will assume that the next TPHY\_SOC is the start of a new cell, and discard the runt cell data.

The HEC fill byte is a dummy byte written into the FIFO and replaced by the transmitter with a HEC calculated for the first four header bytes. TPHY\_DATA7 is the first bit transmitted in the serial data stream. TPHY\_DATA0 is the last bit transmitted in the serial data stream.

Figure 7. Transmit UTOPIA PHY Layer FIFO Timing

Figure 8. Transmit UTOPIA PHY Layer FIFO Timing with HEC Fill

| Symbol | Parameter                | Signals                             | Min | Max | Unit |

|--------|--------------------------|-------------------------------------|-----|-----|------|

| Fc     | TPHY_CLK frequency       |                                     |     | 25  | MHz  |

| Tch    | TPHY_CLK high            |                                     | 18  |     | ns   |

| Tel    | TPHY_CLK low             |                                     | .18 |     | ns   |

| Th     | TPHY_CLK hold time       | TPHY_DATA, /TPHY_WRITE_EN, TPHY_SOC | 1   |     | ns   |

| Tsu    | TPHY_CLK setup time      | TPHY_DATA, /TPHY_WRITE_EN, TPHY_SOC | 8   |     | ns   |

| Tq     | TPHY_CLK-to-output delay | TPHY_CLAV                           |     | 19  | ns   |

Table 22. Definitions of TPHY\_DATA Byte Contents

| Symbol | Definition      | Symbol   | Definition        |

|--------|-----------------|----------|-------------------|

| HD1    | 1st header byte | HEC fill | HEC filler byte   |

| HD2    | 2nd header byte | PD1      | 1st payload byte  |

| HD3    | 3rd header byte | PD2      | 2nd payload byte  |

| HD4    | 4th header byte | PD48     | 48th payload byte |

## 6. 1. 2. Transmit Serial Timing

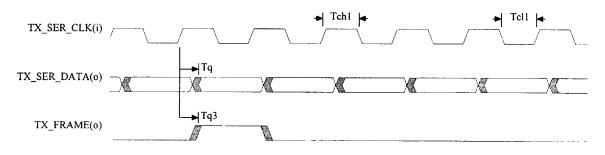

For DS3 operation, the SER\_IO\_EN signal must be set high. Figure 9 shows the relationship for TX\_SER\_CLK, TX\_SER\_DATA, and TX\_FRAME. The frame pulse, TX\_FRAME, indicates the start of a DS3 frame and occurs once per DS3 frame (once every 4760 clock cycles).

Figure 9. Transmit Serial Timing

Figure 10 reveals that TX\_AIS is sampled on the rising edge of TX\_SER\_CLK. The AIS condition is transmitted while TX\_AIS is held high. The example in Figure 10 displays the assertion of TX\_AIS for four clock cycles.

Figure 10. Transmit AIS

| Symbol | Parameter                  | Signals                    | Min | Max | Unit |

|--------|----------------------------|----------------------------|-----|-----|------|

| Fc     | TX_SER_CLK frequency       |                            |     | 45  | MHz  |

| Tch1   | TX_SER_CLK high            |                            | 9   |     | ns   |

| Tcl1   | TX_SER_CLK low             |                            | 9   |     | ns   |

| Th     | TX_SER_CLK hold time       | TX_AIS                     | 1   |     | ns   |

| Tsu    | TX_SER_CLK setup time      | TX_AIS                     | 8   |     | ns   |

| Tq     | TX_SER_CLK-to-output delay | TX_SER_DATA+, TX_SER_DATA- |     | 16  | ns   |

| Tq3    | TX_SER_CLK-to-output delay | TX_FRAME                   |     | 18  | ns   |

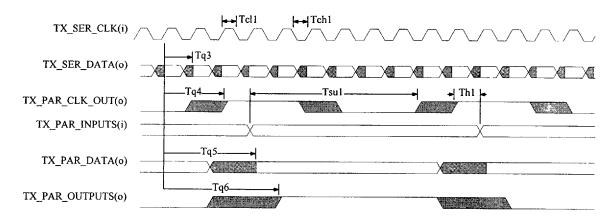

# 6. 1. 3. Transmit Parallel Timing

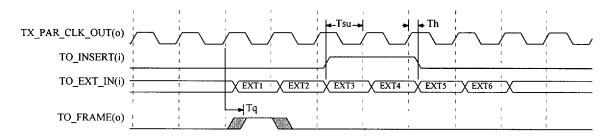

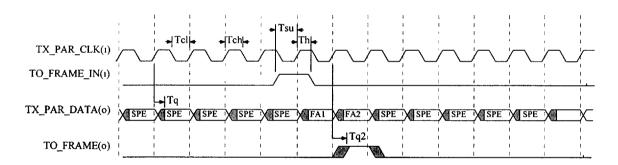

The relationship between serial and parallel timing is shown in Figure 11. All parallel inputs and outputs must be associated with the parallel clock output signal, TX\_PAR\_CLK\_OUT.

Figure 11. Transmit Parallel Timing

| Symbol | Parameter                  | Signals                                                 | Min | Max | Unit |

|--------|----------------------------|---------------------------------------------------------|-----|-----|------|

| Fc     | TX_SER_CLK frequency       |                                                         |     | 45  | MHz  |

| Tch1   | TX_SER_CLK high            |                                                         | 9   |     | ns   |

| Tcll   | TX_SER_CLK low             |                                                         | 9   |     | ns   |

| Th1    | TX_PAR_CLK_OUT hold time   | TO_RAI, TO_EXT_STUFF, TO_FRAME_IN, TO_INSERT, TO_EXT_IN | 0   |     | ns   |

| Tsu1   | TX_PAR_CLK_OUT setup time  | TO_RAI, TO_EXT_STUFF, TO_FRAME_IN, TO_INSERT, TO_EXT_IN | 31  |     | ns   |

| Tq1    | TX_SER_CLK-to-output delay | TX_PAR_CLK_OUT                                          |     | 23  | ns   |

| Tq2    | TX_SER_CLK-to-output delay | TO_FRAME, /TPHY_AEMPTY                                  |     | 30  | ns   |

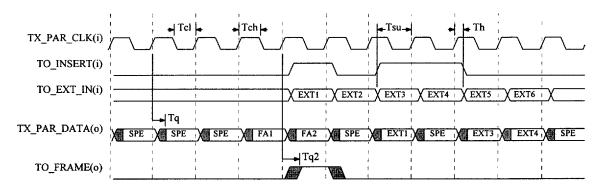

Figure 12 shows the relationship between TO\_FRAME and the insertion data via the TO\_EXT\_IN and TO\_INSERT signals. Bytes in the PLCP data stream are overwritten only when TO\_INSERT is asserted. The pulse on TO\_INSERT shown in the diagram below, for example, overwrites the HD2 and HD3 bytes following Z6 of the current PLCP with the TO\_EXT\_IN data (EXT3 and EXT4). The frame pulse, TO\_FRAME, occurs once per PLCP frame (once every 688 TX\_PAR\_CLK\_OUT cycles), and can be used to determine when to assert TO\_INSERT to overwrite any particular byte of the PLCP data stream. The frame pulse is asserted when the first POH byte (Z6) can be overwritten via the TO\_EXT\_IN signals.

NOTE: If GFC\_EN (A=00h, D5) is a 1, then TO\_EXT\_IN(7:4) are used to overwrite GFC(3:0) of each cell header, and should not be used to overwrite the PLCP data stream.

The timing parameters for Tsu, Th, and Tq can be derived from the relationships established in Figure 11.

Figure 12. Transmit PLCP Insertion Timing

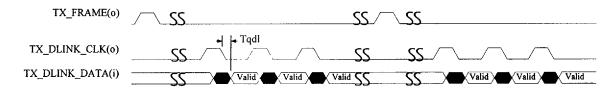

## 6. 1. 4. Transmit Data Link Channel Timing

Figure 13 shows the timing associated with inserting data into the data link channel of the DS3 frame. TX\_FRAME indicates the beginning of the DS3 frame (occurring once every 4760 clock cycles). The TX\_DLINK\_CLK is pulsed three times per DS3 frame and should be used to generate the TX\_DLINK\_DATA.

Figure 13. Transmit Data Link Channel Timing

| Symbol | Parameter                    | Signals       | Min | Max | Unit |

|--------|------------------------------|---------------|-----|-----|------|

| Tqdl   | TX_DLINK_CLK-to-output delay | TX_DLINK_DATA |     | 200 | ns   |

## 6. 2. Receiver Timing

### 6. 2. 1. UTOPIA PHY Layer FIFO Output

The receive UTOPIA PHY Layer FIFO timing signals are compatible with the UTOPIA cell-by-cell specification (refer to "Appendix B. References" on page 123). Table 23 lists the receive FIFO signal names and their corresponding UTOPIA designations.

Table 23. Receive Signal Names and Corresponding UTOPIA Designations

| Signal Name   | UTOPIA Name     |

|---------------|-----------------|

| RPHY_DATA     | RxData          |

| RPHY_SOC      | RxSOC           |

| /RPHY_READ_EN | RxEnb*          |

| RPHY_CLAV ·   | RxEmpty*/RxClav |

| RPHY_CLK      | RxClk           |

| RO_FRAME      | RxRef*          |

| /RPHY_AEMPTY  | Not Available   |

| Not Available | RxPrty          |

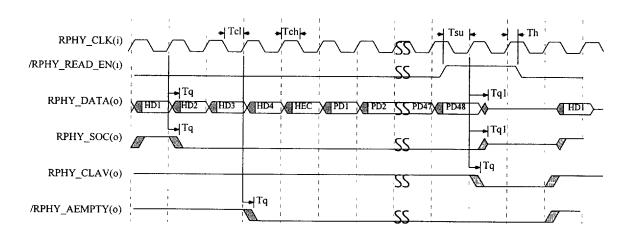

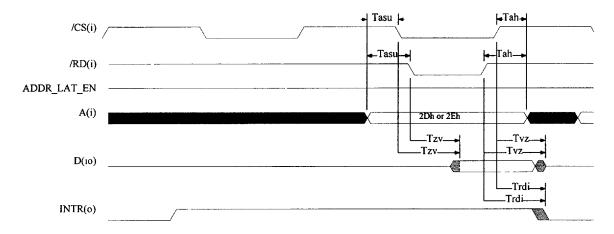

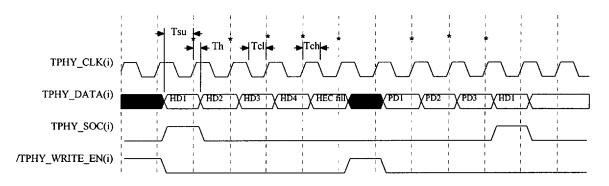

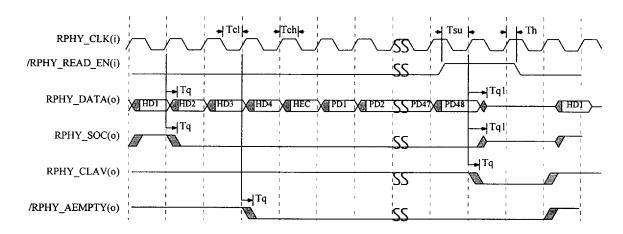

Figure 14 shows the output format of the internal receive UTOPIA PHY layer FIFO data. The symbols used in Figure 14 are defined in the table that follows the diagram. Table 24 defines the contents of the RPHY\_DATA byte. The receiver presents new data on the rising edge of RPHY\_CLK one clock cycle after /RPHY\_READ\_EN is asserted (low) and the receive FIFO has at least one cell. The deassertion of /RPHY\_READ\_EN will cause RPHY\_DATA and RPHY\_SOC to go into tristate. The RPHY\_CLAV flag is deasserted (low) one clock cycle after the last data byte is presented at RPHY\_DATA. The /RPHY\_AEMPTY flag is asserted whenever fewer than 50 bytes are left in the FIFO. The start-of-cell marker, RPHY\_SOC, is asserted when the first byte of the header is available on the RPHY\_DATA pins. Under normal circumstances, the RPHY\_SOC is asserted once for every 53 bytes read from the FIFO. RPHY\_DATA7 is the first of the eight bits received in the serial data stream. RPHY\_DATA0 is the last of the eight bits received in the serial data stream.

Figure 14. Receive UTOPIA PHY Layer FIFO Timing

| Symbol | Parameter                       | Signals                                         | Min | Max | Unit |

|--------|---------------------------------|-------------------------------------------------|-----|-----|------|

| Fc     | RPHY_CLK frequency              |                                                 |     | 25  | MHz  |

| Tch    | RPHY_CLK high                   |                                                 | 18  |     | ns   |

| Tcl    | RPHY_CLK low                    |                                                 | 18  |     | ns   |

| Th     | RPHY_CLK hold time              | /RPHY_READ_EN                                   | 1   |     | ns   |

| Tsu    | RPHY_CLK setup time             | /RPHY_READ_EN                                   | 8   |     | ns   |

| Tq     | RPHY_CLK-to-output delay        | RPHY_DATA, RPHY_SOC,<br>/RPHY_AEMPTY, RPHY_CLAV |     | 19  | ns   |

| Tq1    | RPHY_CLK-to-output enable delay | RPHY_DATA, RPHY_SOC                             |     | 24  | ns   |

Table 24. Definitions of RPHY\_DATA Byte Contents

| Symbol | Definition      | Symbol | Definition         |

|--------|-----------------|--------|--------------------|

| HD1    | 1st header byte | HEC    | Corrected HEC byte |

| HD2    | 2nd header byte | PD1    | 1st payload byte   |

| HD3    | 3rd header byte | PD2    | 2nd payload byte   |

| HD4    | 4th header byte | PD48   | 48th payload byte  |

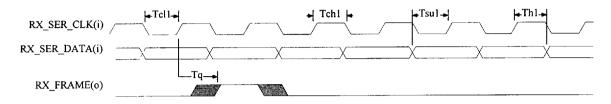

## 6. 2. 2. Receive Serial Timing

For DS3 operation, the SER\_IO\_EN signal must be set high. Figure 15 shows the relationship for RX\_SER\_CLK, RX\_SER\_DATA, and RX\_FRAME. The frame pulse, RX\_FRAME, indicates the start of a DS3 frame and occurs once per DS3 frame (once every 4760 clock cycles).

Figure 15. Receive Serial Timing

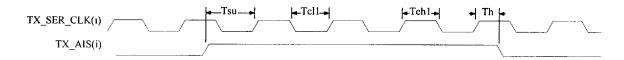

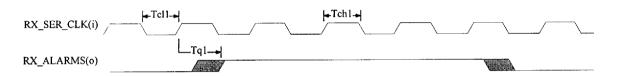

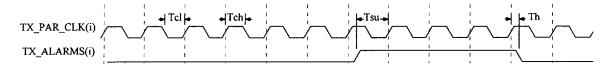

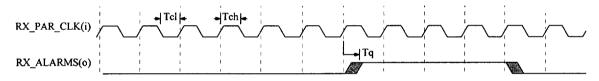

The timing for the DS3 serial alarms is shown in Figure 16. All alarms are active high and remain high for the duration of the event. The DS3 serial alarms detected by the receiver include RX\_AIS, RX\_OOF, and RX\_LOS. The example in Figure 16 shows the detection of an alarm for four clock cycles.

Figure 16. Receive Serial Alarm Timing

| Symbol | Parameter                  | Signals                | Min | Max | Unit |

|--------|----------------------------|------------------------|-----|-----|------|

| Fc     | RX_SER_CLK frequency       |                        |     | 45  | MHz  |

| Tch1   | RX_SER_CLK high            |                        | 9   |     | ns   |

| Tcl1   | RX_SER_CLK low             |                        | 9   |     | ns   |

| Th1    | RX_SER_CLK hold time       | RX_SER_DATA            | 3   |     | ns   |

| Tsul   | RX_SER_CLK setup time      | RX_SER_DATA            | 2   |     | ns   |

| Tq     | RX_SER_CLK-to-output delay | RX_FRAME               |     | 18  | ns   |

| Tq1    | RX_SER_CLK-to-output delay | RX_AIS, RX_OOF, RX_LOS |     | 20  | ns   |

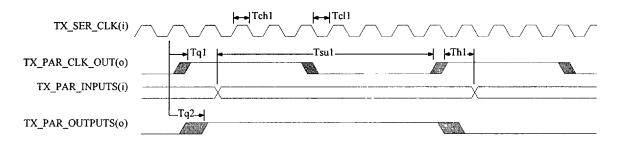

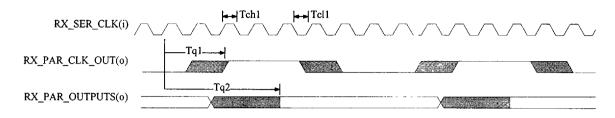

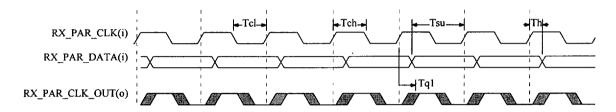

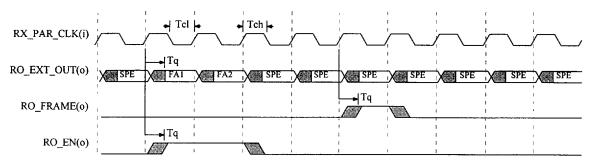

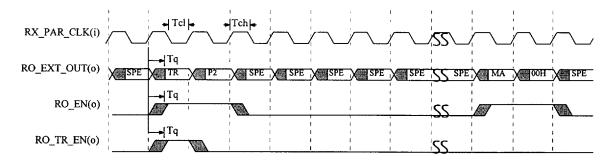

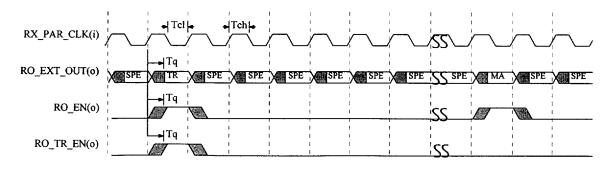

# 6. 2. 3. Receive Parallel Timing

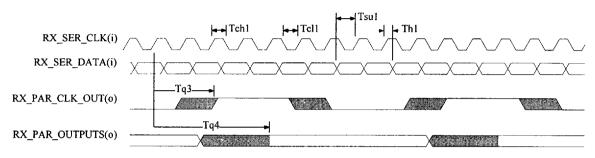

The relationship between serial and parallel timing is shown in Figure 17. All parallel outputs must be associated with the parallel clock output signal, RX\_PAR\_CLK\_OUT.

Figure 17. Receive Parallel Timing

| Symbol | Parameter                  | Signals                                                               | Min | Max | Unit |

|--------|----------------------------|-----------------------------------------------------------------------|-----|-----|------|

| Fc     | RX_SER_CLK frequency       |                                                                       |     | 45  | MHz  |

| Tch1   | RX_SER_CLK high            |                                                                       | 9   |     | ns   |

| Tell   | RX_SER_CLK low             |                                                                       | 9   |     | ns   |

| Tq1    | RX_SER_CLK-to-output delay | RX_PAR_CLK_OUT                                                        |     | 23  | ns   |

| Tq2    | RX_SER_CLK-to-output delay | RM_OCD, RO_RAI, RO_OOF, RO_LOF, RO_FRAME, RO_EN, RO_TR_EN, RO_EXT_OUT |     | 33  | ns   |

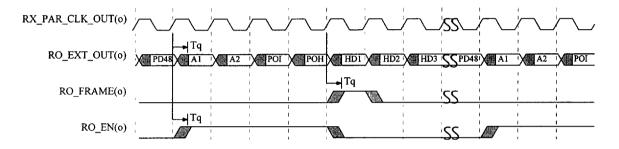

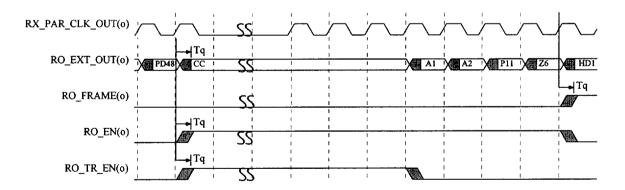

Figure 18 and Figure 19 reveal the relationship for RO\_EXT\_OUT, RO\_FRAME, RO\_EN, and RO\_TR\_EN. These signals can be used to determine the location of the overhead bytes and ATM cells in the PLCP frame. (Refer to Figure 4 on page 8 for details on the DS3 PLCP framing structure.) RO\_FRAME is asserted for one clock cycle when valid frame words (A1 and A2) are detected. Typically, the RO\_FRAME pulse occurs 12 times per PLCP frame and when RO\_EXT\_OUT contains the HD1 byte of the ATM cell. RO\_EN is an active high signal indicating that an overhead byte is present on RO\_EXT\_OUT. RO\_TR\_EN is an active high signal indicating that the trailer nibbles are present on RO\_EXT\_OUT. Note that in Figure 19, RX\_PAR\_CLK\_OUT is gapped during the reception of the Trailer nibbles. When the trailer length is 13 nibbles, RX\_PAR\_CLK\_OUT is gapped for a period of six nibbles, and when the trailer length is 14 nibbles, RX\_PAR\_CLK\_OUT is gapped for a period of seven nibbles.

NOTE: If GFC\_EN (A=00h, D5) is a 1, then RO\_EXT\_OUT(7:4) are used to present the received GFC(3:0) of each cell header, and should not be used to extract the PLCP data stream.

Figure 18. Receive External Timing

Figure 19. Receive External Timing with RO\_TR\_EN

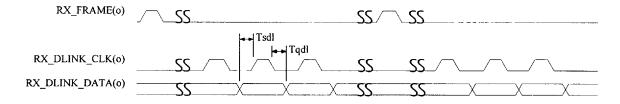

# 6. 2. 4. Receive Data Link Channel Timing

Figure 20 shows the timing associated with accessing data from the data link channel of the DS3 frame. RX\_FRAME indicates the beginning of the DS3 frame (occurring once every 4760 clock cycles). The RX\_DLINK\_CLK is pulsed three times per DS3 frame and is used to indicate that RX\_DLINK\_DATA is valid. Note that in Figure 20, RX\_DLINK\_DATA is valid prior to the rising edge of RX\_DLINK\_CLK and after the falling edge of RX\_DLINK\_CLK.

Figure 20. Receive Data Link Channel Timing

| Symbol | Parameter                    | Signals       | Min  | Max  | Unit |

|--------|------------------------------|---------------|------|------|------|

| Tsdl   | RX_DLINK_CLK setup time      | RX_DLINK_DATA | 1700 |      | ns   |

| Tqdl   | RX_DLINK_CLK-to-output delay | RX_DLINK_DATA | 1600 | 1800 | ns   |

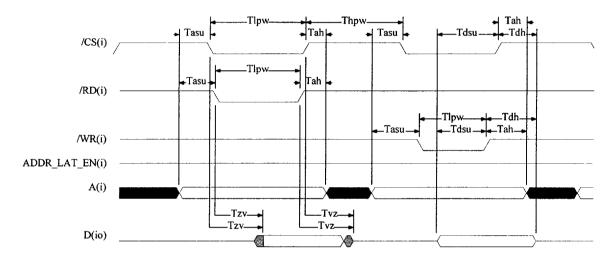

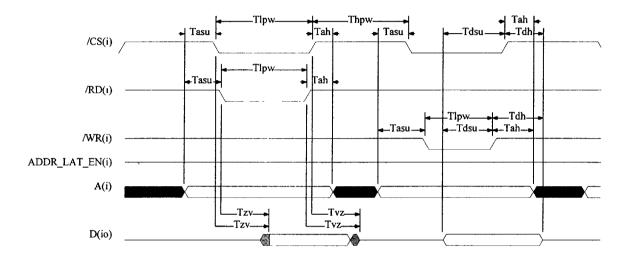

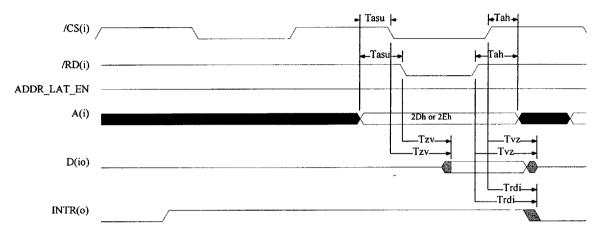

## 6. 3. Microprocessor Timing

Figure 21 displays the timing for typical microprocessor read/write cycles without the use of ADDR\_LAT\_EN. In the example below, the read cycle precedes the write cycle. The setup, hold, and delay times are given with respect to several signals (/CS, /RD, and /WR). Parameter times are determined by the relationships of the various signals as shown in the table below; for example, the Tdsu parameter definition is "data setup time prior to /CS or /WR, whichever comes first". This definition indicates that the data, D, must be valid *Tdsu* nanoseconds before /CS or /WR, whichever comes first. In the write cycle example below, since /WR is deasserted before /CS, the data must be valid *Tdsu* nanoseconds before the /WR signal, and has no minimum setup time with respect to the /CS signal.

Figure 21. Microprocessor Read and Write Cycle Timing

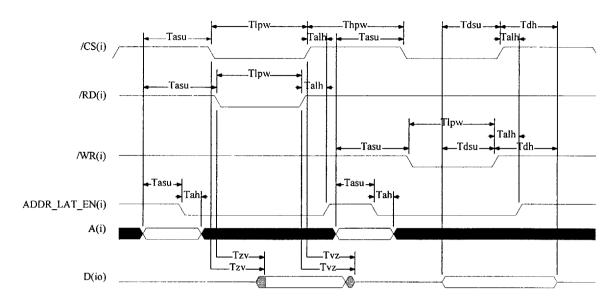

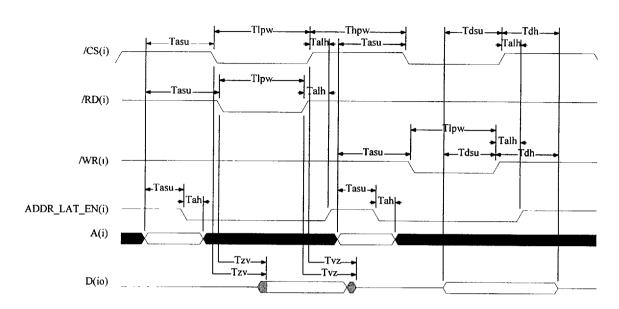

Figure 22 displays the timing for typical microprocessor read/write cycles with the use of ADDR\_LAT\_EN. In the example below, the read cycle precedes the write cycle.

Figure 22. Microprocessor Read and Write Cycle Timing with ADDR\_LAT\_EN

| Symbol | Parameter                                                                       | Signals       | Min | Max | Unit |

|--------|---------------------------------------------------------------------------------|---------------|-----|-----|------|

| Tasu   | address setup time prior to /CS, /RD, /WR, or ADDR_LAT_EN, whichever comes last | A             | 12  |     | ns   |

| Tah    | address hold time prior to /CS, /RD, /WR, or ADDR_LAT_EN, whichever comes first | A             | 2   |     | ns   |

| Talh   | address latch hold time prior to /CS, /RD, /WR, whichever comes first           | ADDR_LAT_EN   | 0   |     | ns   |

| Tdsu   | data setup time prior to /CS or /WR, whichever comes first                      | D             | 12  |     | ns   |

| Tdh    | data hold time prior to /CS or /WR, whichever comes first                       | D             | 0   |     | ns   |