|                                         | V51C259HL-12 | V51C259HL-15 | V51C259HL-20 |

|-----------------------------------------|--------------|--------------|--------------|

| Maximum Access Time (ns)                | 120          | 150          | 200          |

| Maximum Column Address Access Time (ns) | 55           | 65           | 85           |

| Maximum CMOS Standby Current (mA)       | 0.1          | 0.1          | 0.1          |

## Features

- Static Column Mode Operation

- · Continuous data rate over 13 MHz

- · Random access from address within row

- $t_{CAC} = 25, 30, 35 \text{ ns}$

- $t_{OAC} = 20, 25, 30 \text{ ns}$

- Low Input/Output Capacitance

- Low Power Data Retention

- Standby current, CMOS—100 μA (max.)

- · Refresh period, RAS-Only-32 ms (max.)

- Data Retention Current—230 μA (max.)

- TTL and HCT Compatible

- High Reliability Plastic—18 Pin DIP

## Description

The Vitelic V51C259HL is a high speed 65,536 x 4 dynamic Random Access Memory. Fabricated with Vitelic's VICMOS III technology, the V51C259HL offers features not provided by an NMOS dynamic RAM: Static Column Mode for high data bandwidth, fast useable speed, and CMOS standby current and extended RAS-Only refresh for low standby power. All inputs and outputs are compatible to both TTL and HCT logic families while the input and output capacitances are significantly lowered to allow increased system performance.

Static Column Mode operation allows random or sequential access of all 256 bits within a row simply by changing the column address. Because column address access time is as fast as 55 ns, a continuous data rate of over 13 million 4 bit nibbles per second can be achieved. The V51C259HL offers high performance while relaxing many critical system timing requirements for fast usable speed. These features make the V51C259HL ideally suited for graphics, digital signal processing, and high performance systems.

The V51C259HL offers a maximum standby current of 100  $\mu$ A when  $\overline{\text{RAS}} \geq V_{DD} - 0.5 \text{V}$ . During standby (i.e. refresh only cycles), the refresh period can be extended to 32 ms to reduce the total current required to retain data to less than 230  $\mu$ A (max.). The V51C259HL combines this low power with high density for portable and battery backup applications.

#### LOGIC SYMBOL Αa A۱ 1/01 A<sub>2</sub> Аз 1/02 A₄ I/O<sub>3</sub> A<sub>5</sub> A<sub>6</sub> Α7 1/04 -c RAS -C CAS WE OE

#### **PIN NAMES**

| FIAS                  | Row Address Strobe    |

|-----------------------|-----------------------|

| CAS                   | Column Address Strobe |

| WE                    | Write Enable          |

| ŌĒ                    | Output Enable         |

| A <sub>0-A7</sub>     | Address Inputs        |

| I/O <sub>1-I/O4</sub> | Data In/Data Out      |

| $V_{DD}$              | Power ( + 5V)         |

| VSS                   | Ground                |

# Absolute Maximum Ratings†

| Ambient Temperature Under Bias10°C to +80°C                                        |

|------------------------------------------------------------------------------------|

| Storage Temperature (Plastic)55°C to + 125°C                                       |

| Voltage on Any Pin except $V_{DD}$ and $D_{OUT}$ Relative to $V_{SS}$ 2.0V to 7.5V |

| Voltage on V <sub>DD</sub> Relative to V <sub>SS</sub> 1.0V to 7.5V                |

| Voltage on $D_{OUT}$<br>Relative to $V_{SS}$ 2.0V to $V_{DD}$ + 1V                 |

| Data Out Current                                                                   |

| Power Dissipation                                                                  |

#### †COMMENT

Stresses above those listed under "Absolute Maximum Rating" may cause damage to the device. This is a stress rating only and functional operation of the device at these or at any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### D.C. Characteristics1

$T_A = 0$  °C to 70 °C,  $V_{DD} = 5V \pm 10\%$ ,  $V_{SS} = 0V$ , unless otherwise noted.

|                  |                                                            | V                    | /51C259H | L                   | Unit | Test Conditions                                                                                               | Notes    |

|------------------|------------------------------------------------------------|----------------------|----------|---------------------|------|---------------------------------------------------------------------------------------------------------------|----------|

| Symbol           | Parameter                                                  | Min.                 | Typ2     | Max.                | Unit | lest Conditions                                                                                               | MOTRS    |

|                  |                                                            |                      | 60       | ,70                 |      | -12                                                                                                           |          |

| I <sub>DD1</sub> | V <sub>DD</sub> Supply Current, Operating                  |                      | 49       | 60                  | mA   | $t_{RC} = t_{RC} \text{ (min.)}$                                                                              | 3,4      |

| -                |                                                            |                      | 40       | 50                  |      | -20                                                                                                           |          |

| I <sub>DD2</sub> | V <sub>DD</sub> Supply Current, TTL Standby                |                      | 0.5      | 2                   | mA   | $\overline{RAS}$ and $\overline{CAS}$ at $V_{IH}$ , all other inputs and outputs $\geq V_{SS}$                |          |

| -                | V <sub>DD</sub> Supply Current,                            |                      | 57       | 70                  |      | -12                                                                                                           |          |

| I <sub>DD3</sub> | RAS-only Refresh                                           |                      | 45       | 60                  | mA   | $t_{RC} = t_{RC} \text{ (min.)}$                                                                              | 4        |

|                  | Trac-only Herican                                          |                      | 36       | 50                  |      | -20_                                                                                                          | <u> </u> |

|                  |                                                            |                      | 27       | 70                  |      | -12                                                                                                           | 1        |

| I <sub>DD4</sub> | V <sub>DD</sub> Supply Current, Static Column Mode         |                      | 23       | 60                  | mA   | Minimum Cycle15                                                                                               | 3,4      |

|                  |                                                            |                      | 21       | 50                  |      | _20                                                                                                           | <u> </u> |

| I <sub>DD5</sub> | V <sub>DD</sub> Supply Current,<br>Standby, Output Enabled |                      | 1.5      | 4                   | mA   | RAS at $V_{IH}$ , CAS at $V_{IL}$ , all other inputs and outputs $\geq V_{SS}$                                | 3        |

| I <sub>DD6</sub> | V <sub>DD</sub> Supply Current,<br>CMOS Standby            |                      | 0.01     | 0.1                 | mA   | $\overline{RAS} \ge V_{DD}$ -0.5V and $\overline{CAS}$ at $V_{IH}$ , all other inputs and output $\ge V_{SS}$ |          |

| ااررا            | Input Load Current (any pin)                               |                      |          | 1                   | μА   | $V_{IN} = V_{SS}$ to $V_{DD}$                                                                                 | <u></u>  |

| I <sub>LO</sub>  | Output Leakage Current,<br>High Impedance State            |                      |          | 1                   | μА   | RAS and CAS at V <sub>IH</sub> , D <sub>OUT</sub> = V <sub>SS</sub> to V <sub>DD</sub>                        | <u> </u> |

| V <sub>IL</sub>  | Input Low Voltage (all inputs)                             | -0.3                 |          | 0.8                 | ٧    |                                                                                                               | 5        |

| V <sub>IH</sub>  | Input High Voltage (all inputs)                            | 2.4                  |          | V <sub>DD</sub> + 1 | ٧    |                                                                                                               | 6        |

|                  | Q                                                          |                      |          | 0.4                 | ٧    | I <sub>OL</sub> = 4.2 mA                                                                                      | 6        |

| V <sub>OL</sub>  | Output Low Voltage                                         |                      |          | 0.1                 | ٧    | I <sub>OL</sub> = 100 μA                                                                                      | <u> </u> |

|                  | Outside Make and (all autside)                             | 2.4                  |          |                     | ٧    | I <sub>OH</sub> = -5 mA                                                                                       | 6        |

| V <sub>OH</sub>  | Output High Voltage (all outputs)                          | V <sub>DD</sub> -0.1 |          |                     | ٧    | $I_{OH} = -100 \mu\text{A}$                                                                                   | <u> </u> |

- 1. All voltages referenced to V<sub>SS</sub>.

- 2. Typical values are at  $T_A = 25$  °C and  $V_{DD} = +5$ V.

- 3. I<sub>DD</sub> is dependent upon output loading when the device output is selected. I<sub>DD</sub> (max) is measured with the output open.

- 4. Î<sub>DD</sub> is dependent upon the number of address transitions. Specified I<sub>DD</sub> (max) is measured with a maximum of two transitions per address cycle in Static Column Mode.

- Specified V<sub>IL</sub> (min) is steady state operation. During transitions, V<sub>IL</sub> may undershoot to −1.0V for periods not to exceed 20 ns. All A.C. parameters are measured with V<sub>IL</sub> (min) ≥ V<sub>SS</sub> and V<sub>IH</sub> (max) ≤ V<sub>DD</sub>.

- 6. Test conditions apply only for D.C. Characteristics. All A.C. parameters are measured as noted in the A.C. Characteristics section.

### Capacitance

$T_A = 25$  °C,  $V_{DD} = 5$ V  $\pm$  10%,  $V_{SS} = 0$ V, unless otherwise noted.

| Symbol           | Parameter        | Тур. | Max. | Unit |

|------------------|------------------|------|------|------|

| C <sub>IN1</sub> | Address          | 4    | 5    | рF   |

| C <sub>IN2</sub> | RAS, CAS, WE, OE | 3    | 5    | ρF   |

| C <sub>1/O</sub> | Data In/Out      | 4    | 6    | pF   |

### A.C. Characteristics 1, 2, 3

$T_A = 0$ °C to 70°C,  $V_{DD} = 5V \pm 10\%$ ,  $V_{SS} = 0V$ , unless otherwise noted.

### Read, Write and Refresh Cycles

| No. | JEDEC               | Symbol             | Parameter                          | V51C | 259HL-12 | V51C | 259HL-15 | V51C     | 259HL-20 |      |       |

|-----|---------------------|--------------------|------------------------------------|------|----------|------|----------|----------|----------|------|-------|

| NO. | Symbol              | Зутий              | Parameter                          | Min. | Max.     | Min. | Max.     | Min.     | Max.     | Unit | Notes |

| 1   | t <sub>RL1RH1</sub> | t <sub>RAS</sub>   | RAS Pulse Width                    | 120  | 75000    | 150  | 75000    | 200      | 75000    | ns   |       |

| 2   | t <sub>RL2RL2</sub> | t <sub>RC</sub>    | Random Read or Write Cycle Time    | 185  |          | 240  |          | 310      |          | ns   |       |

| 3   | t <sub>RH2RL2</sub> | t <sub>RP</sub>    | RAS Precharge Time                 | 55   |          | 80   |          | 100      |          | ns   |       |

| 4   | t <sub>RL1CH1</sub> | t <sub>CSH</sub> * | CAS Hold Time                      | 120  |          | 150  |          | 200      |          | ns   |       |

| 5   | t <sub>CL1CH1</sub> | t <sub>CAS</sub> * | CAS Pulse Width                    | 25   |          | 30   |          | 35       |          | ns   |       |

| 6   | t <sub>WH2RL2</sub> | t <sub>WRP</sub>   | Write Enable to RAS Precharge Time | 10   |          | 10   |          | 10       |          | ns   |       |

| 7   | t <sub>RL1WL2</sub> | t <sub>RWH</sub>   | RAS to Write Enable Hold Time      | 20   |          | 20   |          | 25       |          | ns   |       |

| 8   | t <sub>AVRL2</sub>  | t <sub>ASR</sub>   | Row Address Set-up Time            | 0    |          | 0    |          | 0        |          | ns   |       |

| 9   | t <sub>RL1AX</sub>  | t <sub>RAH</sub>   | Row Address Hold Time              | 15   | 7 /      | 20   |          | 25       |          | ns   |       |

| 10  | t <sub>CH2QZ</sub>  | t <sub>HZ</sub>    | OE or CAS to Output High Impedance |      | 20       |      | 25       | <u> </u> | 30       | ns   | 4,5   |

| 11  | t <sub>CL2QX</sub>  | t <sub>LZ</sub>    | OE or CAS to Output Low Impedance  | 0    |          | 0    |          | 0        |          | ns   | 4,5   |

|     | t <sub>RVRV</sub>   | t <sub>REF1</sub>  | Time Between Refresh               |      | 4        |      | 4        |          | 4        | ms   | 6     |

| -   | t <sub>RVRV</sub>   | t <sub>REF2</sub>  | Time Between Refresh (RAS-Only)    |      | 32       |      | 32       |          | 32       | ms   | 6     |

|     | t <sub>T</sub>      | t⊤                 | Transition Time (Rise and Fall)    | 1    | 25       | 1    | 25       | 1        | 25       | ns   | 7     |

<sup>\*</sup>This parameter not applicable if operated with CAS grounded.

<sup>1.</sup> All voltages referenced to  $V_{\rm SS}$ .

An initial pause of 100 microseconds is required after power up followed by a minimum of eight initialization cycles (any combination of cycles

containing a RAS clock such as a RAS-Only refresh). Eight initialization cycles are required after extended periods of bias without clocks (greater than

32 ms).

<sup>3.</sup> A.C. Characteristics assume  $t_T$  = 5 ns. All A.C. parameters are measured with  $V_{OL}$  = 0.8V at  $I_{OL}$  - 2.2 mA,  $V_{OH}$  = 2.4V at  $I_{OH}$  = -2.0 mA with a 50 pF load,  $V_{IL}$  (min)  $\geq V_{SS}$  and  $V_{IH}$  (max)  $\leq V_{DD}$

<sup>4.</sup> Assumes three state test load (5 pF and a 380 Ohm Thevenin equivalent).

<sup>5.</sup> At any given temperature and voltage combination, coincident deselection/selection is permissible for wired-OR devices.

<sup>6.</sup> The V51C259HL extends the refresh period to 32 ms during RAS-Only refresh periods.

<sup>7.</sup>  $t_T$  is measured between  $V_{IH}$  (min) and  $V_{IL}$  (max).

# A.C. Characteristics (Cont'd.)

## Read Cycle

|     | JEDEC               |                       |                                          | V51C | 259HL-12 | V51C2 | 59HL-15 | V51C2 | 59HL-20 | Unit | Notes    |

|-----|---------------------|-----------------------|------------------------------------------|------|----------|-------|---------|-------|---------|------|----------|

| No. | Symbol              | Symbol                | Parameter                                | Min. | Max.     | Min.  | Max.    | Min.  | Max.    | Unit | MULES    |

| 12  | t <sub>RL1QV</sub>  | tRAC                  | Access Time From RAS                     |      | 120      |       | 150     |       | 200     | ns   | 8        |

| 13  | t <sub>CL1QV</sub>  | t <sub>CAC</sub>      | Access Time From CAS                     |      | 25       |       | 30      |       | 35      | ns   |          |

| 14  | t <sub>GL1QV</sub>  | toac                  | Access Time From OE                      |      | 20       |       | 25      |       | 30      | ns   |          |

| 15  | t <sub>AVQV</sub>   | t <sub>CAA</sub>      | Access Time From Column Address          |      | 55       |       | 65      |       | 85      | ns   | 14       |

| 16  | t <sub>CL1RH1</sub> | t <sub>RSH(R)</sub> * | RAS Hold Time (Read Cycle)               | 10   |          | 10    |         | 10    |         | ns   |          |

| 17  | t <sub>WH2CL2</sub> | t <sub>RCS</sub> *    | Read Command Set-up Time                 | 0    |          | 0     |         | 0     | _       | ns   |          |

| 18  | t <sub>AVRH1</sub>  | t <sub>CAR</sub>      | Column Address to RAS Set-up Time        | 55   |          | 65    |         | 85    |         | ns   | <u> </u> |

| 19  | t <sub>RL1AX</sub>  | t <sub>ARR</sub>      | Column Address Hold Time From RAS (Read) | 110  |          | 140   |         | 190   |         | ns   | <u> </u> |

| 20  | t <sub>CH2WX</sub>  | t <sub>RCH</sub> *    | Read Command Hold Time Referenced to CAS | 5    |          | 5     |         | 5     |         | ns   | <u> </u> |

| 21  | t <sub>RH2WX</sub>  | t <sub>BRH</sub>      | Read Command Hold Time Referenced to RAS | 10   |          | 10    |         | 10    |         | ns   | <u> </u> |

| 22  | t <sub>RH2AX</sub>  | t <sub>ABH</sub>      | Column Address Hold Time to RAS          | 0    |          | 0     |         | 0     |         | ns   |          |

| 23  | t <sub>RL1AV</sub>  | t <sub>RAD</sub>      | RAS to Column Address Delay Time         | 20   | 65       | 25    | 85      | 30    | 115     | ns   | 9        |

| 24  | t <sub>AXQX</sub>   | t <sub>OHA</sub>      | Output Hold Time From Address Change     | 10   |          | 10    |         | 10    |         | ns   |          |

| 25  | t <sub>GH1OX</sub>  | t <sub>OH</sub>       | Output Hold Time From OE or CAS          | 0    |          | 0     |         | 0     |         | ns   |          |

### Write Cycle

|     | JEDEC               |                      |                                             | V51C2 | 259HL-12 | V51C2 | 259HL-15 | V51C259HL-20 |      | Unit | Notes  |

|-----|---------------------|----------------------|---------------------------------------------|-------|----------|-------|----------|--------------|------|------|--------|

| No. | Symbol              | Symbol               | Parameter                                   | Min.  | Max.     | Min.  | Max.     | Min.         | Max. | Unit | 140162 |

| 26  | t <sub>CL1RH1</sub> | t <sub>RSH</sub> (W) | RAS Hold Time (Write Cycle)                 | 30    |          | 35    |          | 40           |      | ns   |        |

| 27  | t <sub>RL1WL2</sub> | t <sub>WDR</sub>     | RAS to Write Command Lead Time              | 25    | 90       | 30    | 115      | 35           | 160  | ns   |        |

| 28  | t <sub>WL1RH1</sub> | t <sub>RWL</sub>     | Write Command to RAS Lead Time              | 25    |          | 30    |          | 35           |      | ns   |        |

| 29  | t <sub>WL1CH1</sub> | t <sub>CWL</sub> *   | Write Command to CAS Lead Time              | 25    |          | 30    |          | 35           |      | ns   |        |

| 30  | t <sub>WL1WH1</sub> | t <sub>WP</sub>      | Write Command Pulse Width                   | 25    |          | 30    |          | 35           |      | ns   |        |

| 31  | t <sub>wh2wL2</sub> | twcp                 | Write Command Precharge Time                | 5     |          | 10    |          | 15           |      | ns   |        |

| 32  | t <sub>WL1CL2</sub> | twcs*                | Write Command Set-up Time                   | 0     |          | 0     |          | 0            |      | ns   | 10     |

| 33  | t <sub>CL1WH1</sub> | twc+*                | Write Command Hold Time                     | 25    |          | 30    |          | 35           |      | ns   |        |

| 34  | t <sub>BL1WH1</sub> | twca                 | Write Command Hold Time From RAS            | 80    |          | 90    |          | 100          |      | ns   |        |

| 35  | t <sub>AVWL2</sub>  | t <sub>AWS</sub>     | Column Address to Write Command Set-up Time | 0     |          | 0     |          | 0            |      | ns   |        |

| 36  | t <sub>WL1AX</sub>  | t <sub>AWH</sub>     | Column Address to Write Command Hold Time   | 20    |          | 25    |          | 30           |      | ns   |        |

- \*This parameter not applicable if operated with CAS grounded.

- 8. Assumes that  $t_{RAD} \le t_{RAD}$  (max) if  $t_{RAD} > t_{RAD}$  (max), then  $t_{RAC}$  will increase by the amount that  $t_{RAD}$  exceeds  $t_{RAD}$  (max).

- 9. t<sub>RAD</sub> is specified for reference only.

- 10. t<sub>WCS</sub>, t<sub>RWD</sub> t<sub>CWD</sub>, t<sub>AWD</sub> and t<sub>OWD</sub> are specified as reference points only. If t<sub>WCS</sub> ≥ t<sub>WCS</sub> (min), the cycle is a CAS controlled write cycle and the data out pin will remain in high impedance for the duration of WE low. If t<sub>CWD</sub> ≥ t<sub>CWD</sub> (min) and t<sub>RWD</sub> ≥ t<sub>RWD</sub> (min) and t<sub>OWD</sub> ≥ t<sub>OWD</sub> (min) and t<sub>AWD</sub> ≥ t<sub>AWD</sub> (min), then the cycle is a read-modify-write cycle.

# A.C. Characteristics (Cont'd.)

## Write Cycle (Cont'd.)

| No. | JEDEC<br>Symbol     | Symbol           | l Parameter                               | V51C259HL-12 |      | V51C259HL-15 |      | V51C259HL-20 |      | Unit | Notes |

|-----|---------------------|------------------|-------------------------------------------|--------------|------|--------------|------|--------------|------|------|-------|

| MU. |                     |                  |                                           | Min.         | Max. | Min.         | Max. | Min.         | Max. | Unit | Notes |

| 37  | t <sub>RL1AX</sub>  | t <sub>ARW</sub> | Column Address Hold Time From RAS (Write) | 70           |      | 80           |      | 90           |      | ns   |       |

| 38  | t <sub>DVWL2</sub>  | t <sub>DS</sub>  | Data-In Set-up Time                       | 0            |      | 0            |      | 0            |      | ns   |       |

| 39  | t <sub>WL1DX</sub>  | t <sub>DH</sub>  | Data-In Hold Time                         | 20           |      | 25           |      | 30           |      | ns   |       |

| 40  | t <sub>GH2WH1</sub> | tows             | OE Set-up Time From End of Write          | 15           |      | 20           |      | 25           |      | ns   |       |

| 41  | <sup>t</sup> CH1GL2 | t <sub>COH</sub> | OE Hold Time From CAS                     | 20           |      | 25           |      | 30           |      | ns   |       |

### Read-Modify-Write Cycle (11)

| No. | JEDEC               | Symbol             | Devente                                 | V51C | 259HL-12 | V51C259HL-15 |       | V51C259HL-20 |       |      | N-4   |

|-----|---------------------|--------------------|-----------------------------------------|------|----------|--------------|-------|--------------|-------|------|-------|

| NO. | Symbol              |                    | Parameter                               | Min. | Max.     | Min.         | Max.  | Min.         | Max.  | Unit | Notes |

| 42  | t <sub>RL2RL2</sub> | t <sub>RWC</sub>   | Read-Modify-Write (RMW) Cycle Time      | 240  |          | 305          |       | 385          |       | ns   |       |

| 43  | t <sub>RL1RH1</sub> | t <sub>RRW</sub>   | RAS Pulse Width (RMW)                   | 175  | 75000    | 215          | 75000 | 275          | 75000 | ns   |       |

| 44  | t <sub>CL1CH1</sub> | <sup>‡</sup> CRW   | CAS Pulse Width (RMW)                   | 80   |          | 95           |       | 110          |       | ns   |       |

| 45  | t <sub>RL1AX</sub>  | t <sub>AR</sub>    | Column Address Hold Time From RAS (RMW) | 165  |          | 205          |       | 265          |       | ns   |       |

| 46  | t <sub>RL1WL2</sub> | t <sub>RWD</sub>   | RAS to WE Delay                         | 145  |          | 95           |       | 120          |       | ns   | 12    |

| 47  | t <sub>AVWL2</sub>  | t <sub>AWD</sub>   | Column Address to WE Delay              | 80   |          | 95           |       | 120          |       | ns   | 12    |

| 48  | t <sub>CL1WL2</sub> | t <sub>CWD</sub> * | CAS to WE Delay                         | 50   |          | 60           |       | 70           |       | ns   | 12    |

| 49  | t <sub>GH2WL2</sub> | town               | OE to WE Delay                          | 25   |          | 30           |       | 35           |       | ns   | 12    |

### Static Column Mode (13)

| No. | JEDEC               | Symbol           | Parameter                              | V51C | V51C259HL-12 |      | V51C259HL-15 |      | V51C259HL-20 |      | Ī.,   |

|-----|---------------------|------------------|----------------------------------------|------|--------------|------|--------------|------|--------------|------|-------|

| NU. | Symbol              |                  |                                        | Min. | Max.         | Min. | Max.         | Min. | Max.         | Unit | Notes |

| 50  | t <sub>WL2WL2</sub> | t <sub>swc</sub> | Static Column Write Cycle Time         | 55   |              | 65   |              | 85   |              | ns   |       |

| 51  | t <sub>wH2QV</sub>  | t <sub>WPA</sub> | Write Precharge Access Time            |      | 55           |      | 65           |      | 85           | ns   | 14    |

| 52  | t <sub>WL1QV</sub>  | t <sub>WRA</sub> | Write-Read Access Time                 |      | 105          |      | 120          |      | 145          | ns   | 14    |

| 53  | t <sub>WL1GL2</sub> | 1 <sub>WOH</sub> | Write to OE Hold Time                  | 25   |              | 30   |              | 35   |              | ns   |       |

| 54  | t <sub>RL1WL2</sub> | t <sub>SWH</sub> | Delay from HAS to Second Write Command | 120  |              | 150  |              | 200  |              | ns   |       |

<sup>\*</sup>This parameter not applicable if operated with CAS grounded.

<sup>11.</sup> The parameters shown in the Read-Modify-Write timing diagrams which are not listed in the table are previously specified.

<sup>12.</sup> t<sub>WCS</sub>, t<sub>RWD</sub>, t<sub>CWD</sub>, t<sub>AWD</sub> and t<sub>OWD</sub> are specified as reference points only. If t<sub>WCS</sub> ≥ t<sub>WCS</sub> (min), the cycle is a CAS controlled write cycle and the data out pin will remain in high impedance for the duration of WE low. If t<sub>CWD</sub> ≥ t<sub>CWD</sub> (min) and t<sub>RWD</sub> ≥ t<sub>RWD</sub> (min) and t<sub>OWD</sub> ≥ t<sub>OWD</sub> (min) and t<sub>AWD</sub> ≥ t<sub>AWD</sub> (min), then the cycle is a read-modify-write cycle.

<sup>13.</sup> All previously specified A.C. characteristics are applicable.

<sup>14.</sup> Access time from a write command or a read command is determined by the longer of t<sub>CAA</sub> or t<sub>WPA</sub> or t<sub>WPA</sub>.

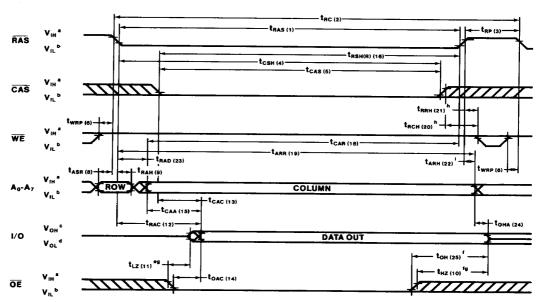

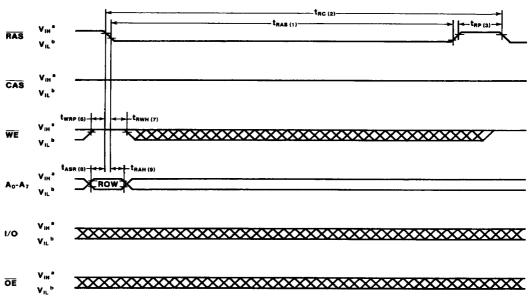

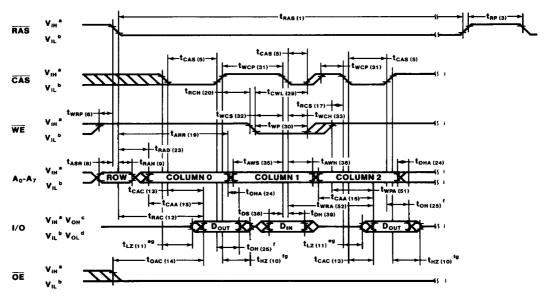

## Waveforms of Read Cycle

- a., b. VIH (min) and VIL (max) are reference levels for measuring timing of input signals.

- c., d. V<sub>OH</sub> (min) and V<sub>OL</sub> (max) are reference levels for measuring timing of D<sub>OUT</sub>

- e. t<sub>LZ</sub> is referenced to the later of RAS, CAS, and OE low transition.

- f. t<sub>HZ</sub> and t<sub>OH</sub> are referenced to the earlier of CAS or OE high transition.

- g. Transition is measured +500 mV from steady state voltage with specified three state load (5 pF and a 380 Ohm Thevenin equivalent).

- h. Either t<sub>RCH</sub> or t<sub>RRH</sub> must be satisfied.

- i. If t<sub>RRH</sub> ≥ t<sub>ARH</sub> (min), then data from the last address will be latched on D<sub>OUT</sub> by a RAS high transition, until either a CAS or OE high transition releases the data.

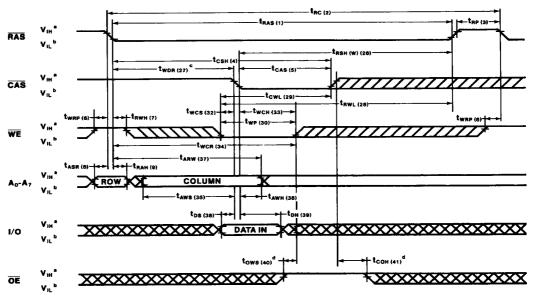

## Waveforms of Write Cycle (CAS Controlled) e

- a., b.  $V_{IH}$  (min) and  $V_{IL}$  (max) are reference levels for measuring timing of input signals.

- c. t<sub>WDR</sub> is reference to the later of the CAS or WE low transition.

- d. If the low transition of WE occurs before or simultaneously with the low transition of CAS and the high transition of CAS or RAS occurs before the high transition of WE, then the outputs remain in a high impedance state (i.e., OE is a don't care).

- e. WE is low prior to or simultaneously with CAS low transition. CAS is high prior to RAS low transition.

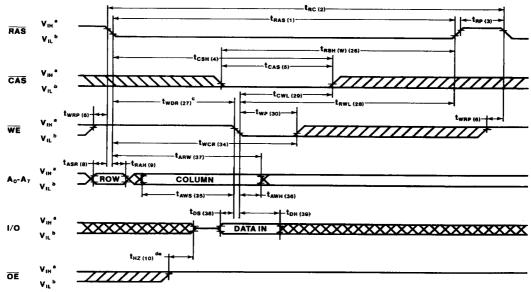

## Waveforms of Write Cycle (WE Controlled) f

- a., b.  $V_{IH}$  (min) and  $V_{IL}$  (max) are reference levels for measuring timing of input signals.

- c. t<sub>WDR</sub> is reference to the later of the CAS or WE low transition.

- d. t<sub>HZ</sub> is referenced to the earlier of the CAS or OE high transition or WE low transition.

- e. Transition is measured ± 500 mV from steady state voltage with specified three state load (5 pF and a 380 Ohm Thevenin equivalent).

- f. CAS is low prior to the WE low transition.

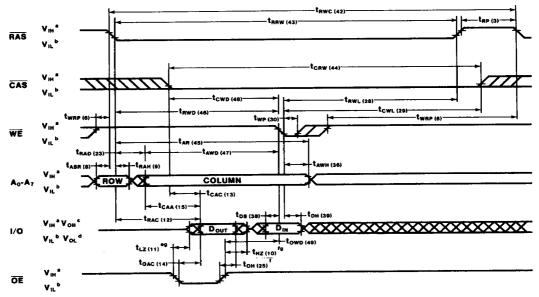

## Waveforms of Read/Modify/Write Cycle

- a., b.  $V_{\text{IH}}$  (min) and  $V_{\text{IL}}$  (max) are reference levels for measuring timing of input signals.

- c., d.  $V_{OH}$  (min) and  $V_{OL}$  (max) are reference levels for measuring timing of  $D_{OUT}$

- e.  $t_{LZ}$  is referenced to the later of  $\overline{RAS}$ ,  $\overline{CAS}$ , and  $\overline{OE}$  low transition.

- f.  $t_{HZ}$  and  $t_{OH}$  are referenced to the earlier of the CAS or  $\overline{OE}$  high transition.

- g. Transition is measured ± 500 mV from steady state voltage with specified three state load (5 pF and a 380 Ohm Thevenin equivalent).

## Waveforms of RAS-Only Refresh Cycle

#### NOTE:

a., b.  $V_{IH}$  (min) and  $V_{IL}$  (max) are reference levels for measuring timing of input signals.

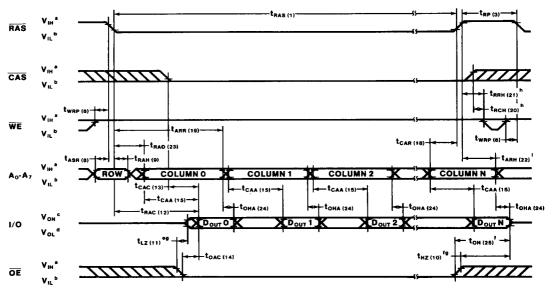

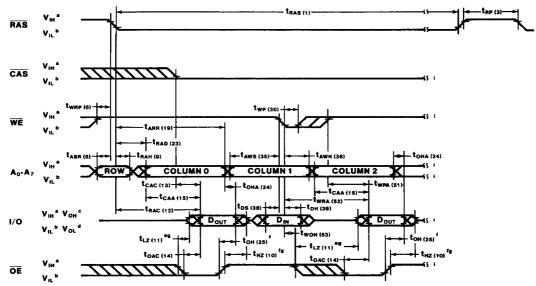

### Waveforms of Static Column Mode Read Cycle

- a., b.  $V_{iH}$  (min) and  $V_{iL}$  (max) are reference levels for measuring timing of input signals.

- c., d. V<sub>OH</sub> (min) and V<sub>OL</sub> (max) are reference levels for measuring timing of D<sub>OUT</sub>

- e.  $t_{LZ}$  is referenced to the later of  $\overline{RAS}$ ,  $\overline{CAS}$ , and  $\overline{OE}$  low transition.

- f.  $t_{HZ}$  and  $t_{OH}$  are referenced to the earlier of the  $\overline{CAS}$  or  $\overline{OE}$  high transition.

- g. Transition is measured ± 500 mV from steady state voltage with specified three state load (5 pF and a 380 Ohm Thevenin equivalent).

- h. Either t<sub>RCH</sub> or t<sub>RRH</sub> must be satisfied.

- i. If t<sub>ARH</sub> ≥ t<sub>ARH</sub> (min), then data from the last address will be latched on D<sub>OUT</sub> by a RAS high transition, until either a CAS or OE high transition releases the data.

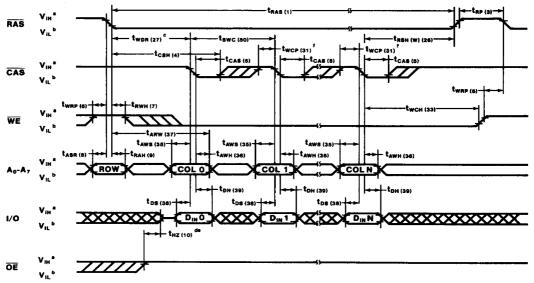

## Waveforms of Static Column Mode Write Cycle (CAS Controlled) 9

- a., b. VIH (min) and VIL (max) are reference levels for measuring timing of input signals.

- c.  $t_{WDR}$  is reference to the later of the  $\overline{\text{CAS}}$  or  $\overline{\text{WE}}$  low transition.

- d. t<sub>HZ</sub> is referenced to the earlier of the CAS or OE high transition or WE low transition.

- e. Transition is measured ± 500 mV from steady state voltage with specified three state load (5 pF and a 380 Ohm Thevenin equivalent).

- f. twcp is measured from the earlier of CAS or WE high transition to the later of CAS or WE low transition.

- g. WE is low prior to or simultaneously with a CAS low transition. CAS is high prior to a RAS low transition.

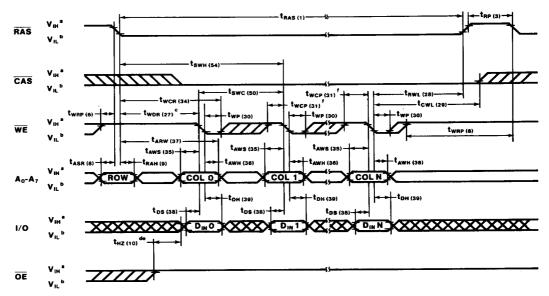

# Waveforms of Static Column Mode Write Cycle (WE Controlled) g

- a., b.  $V_{IH}$  (min) and  $V_{IL}$  (max) are reference levels for measuring timing of input signals.

- c. two is reference to the later of the CAS or WE low transition.

- d.  $t_{\rm HZ}$  is referenced to the earlier of the RAS or CAS or  $\overline{\rm OE}$  high transition.

- e. Transition is measured ± 500 mV from steady state voltage with specified three state load (5 pF and a 380 Ohm Thevenin equivalent).

- f. t<sub>WCP</sub> is measured from the earlier of CAS or WE high transition to the later of CAS or WE low transition.

- g. CAS is low prior to a WE low transition.

## Waveforms of Static Column Mode Read/Write/Read...Cycle (CAS Controlled) h

- a., b.  $V_{iH}$  (min) and  $V_{ii}$  (max) are reference levels for measuring timing of input signals.

- c., d. V<sub>OH</sub> (min) and V<sub>OL</sub> (max) are reference levels for measuring timing of D<sub>OUT</sub>

- e.  $t_{LZ}$  is referenced to the later  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{OE}$  are low transition.

- f.  $t_{HZ}$  and  $t_{OH}$  are referenced to the earlier of  $\overline{CAS}$  or  $\overline{OE}$  high transition.

- g. Transition is measured ± 500 mV from steady state voltage with specified three state load (5 pF and a 380 Ohm Thevenin equivalent).

- h. WE is low prior to or simultaneously with a CAS low transition.

- i. The cycle can be terminated by either a read or a write operation followed by a RAS high transition. See pages 36 or 37 for timings.

## Waveforms of Static Column Mode Read/Write/Read...Cycle (WE Controlled) h

- a., b.  $V_{IH}$  (min) and  $V_{IL}$  (max) are reference levels for measuring timing of input signals.

- c., d.  $V_{OH}$  (min) and  $V_{OL}$  (max) are reference levels for measuring timing of  $D_{OUT}$

- e. t<sub>LZ</sub> is referenced to the later of RAS CAS, and OE high transition.

- f. t<sub>HZ</sub> and t<sub>OH</sub> are referenced to the earlier of CAS or OE high transition if RAS and CAS and OE are low.

- g. Transition is measured ± 500 mV from steady state voltage with specified three state load (5 pF and a 380 Ohm Thevenin equivalent).

- h. CAS is low prior to a WE low transition.

- i. The cycle can be terminated by either a read or a write operation followed by a RAS high transition. See pages 36 or 38 for timings.

### Functional Description

The V51C259HL is a CMOS dynamic RAM optimized for the high data bandwidth and low power applications. The functionality is similar to a traditional dynamic RAM. The V51C259HL reads and writes 4 bits of data at a time by multiplexing a 16 bit address into an 8 bit row and an 8 bit column address. The row address is latched in by the Row Address Strobe  $\overline{(RAS)}$ . The column address, however, is only latched during a write cycle by the later of either Column Address Strobe  $\overline{(CAS)}$  or Write Enable  $\overline{(WE)}$ . During the read cycle, the column address is not latched and continuously flows through the internal input latches. Access time is primarily dependent on a valid column address.  $\overline{CAS}$  acts as chip select signal and may remain low during the entire memory operation.

### **Memory Cycle**

The memory cycle is initiated by bringing RAS low. Any memory cycle once initiated must not be ended or aborted prior to fulfilling the minimum t<sub>RAS</sub> timing specification. This ensures proper device operation and data integrity. Additionally, a new cycle cannot be initiated until the minimum precharge time, t<sub>RP</sub>, has elapsed.

### Read Cycle

A read cycle is performed by maintaining the Write Enable (WE) signal high during the RAS operation. The column address must be held for a minimum time specified by t<sub>ARR</sub>. CAS may either be held low or be pulsed similar to the traditional CAS operation. Data out is controlled by the Output Enable (OE) and CAS which is discussed in the Data Out Operation.

For applications where  $\overline{\text{CAS}}$  is held low, the data out becomes valid when  $t_{\text{RAC}}$ ,  $t_{\text{CAA}}$ , and  $t_{\text{OAC}}$  are all satisfied.

For applications where  $\overline{\text{CAS}}$  is pulsed similar to the traditional  $\overline{\text{CAS}}$  operation, the additional timing specifications noted by the asterisks in the A.C. Characteristics are applicable. Data out becomes valid only when  $t_{\text{RAC}}$ ,  $t_{\text{CAA}}$ ,  $t_{\text{OAC}}$ , and  $t_{\text{CAC}}$  are all satisfied. Consequently, the access time is dependent upon the timing relationship among  $t_{\text{RAC}}$ ,  $t_{\text{CAA}}$ ,  $t_{\text{OAC}}$ , and  $t_{\text{CAC}}$ . For example, the access time is limited by  $t_{\text{CAA}}$  when  $t_{\text{RAC}}$ ,  $t_{\text{OAC}}$ , and  $t_{\text{CAC}}$  are all satisfied.

### Write Cycle

A write cycle is performed by taking WE low during a RAS operation. To simplify the system design, the column address is latched in by the later of WE or CAS. As in the read cycle, CAS may either be held low or be pulsed similar to the traditional CAS operation. For applications where CAS is held low, the input data must be valid at or before the falling edge of WE. For applications where CAS is pulsed similar to the traditional CAS operation, the additional timing specifications noted by the asterisks in the A.C. Characteristics are applicable. The input data must be valid at or before the falling edge of WE or CAS. whichever occurs last. Consequently, the write cycle can be WE controlled or CAS controlled depending upon the later of WE or CAS low transition. In a CAS controlled write cycle, (the leading edge of WE occurs prior to or coincident with the CAS low transition) the input/output (I/O) pin will be in the high impedance state at the beginning of the write function. Terminating the write action with CAS will maintain the I/O in the high impedance state; terminating with WE allows the output to go active, and the OE must be brought high to allow for inputs on the I/O.

## Refresh Cycle

To retain data, a refresh operation is performed by clocking each of the 256 row addresses ( $A_0$  through  $A_7$ ) with  $\overline{RAS}$  at least every 4 milliseconds. Any read, write, read-modify write, or  $\overline{RAS}$ -Only cycle will perform refresh.

### **Extended Refresh Cycle**

The V51C259HL extends the refresh cycle period to 32 milliseconds for  $\overline{\rm RAS}$ -Only refresh cycles. This feature reduces the total current consumption to a maximum of 230  $\mu{\rm A}$ , and typically 90  $\mu{\rm A}$ , for data retention. The low standby current can significantly extended battery life in battery back-up applications. Current consumption is calculated from the following equation:

$$I = \frac{((t_{RC})(I_{Active}) + (t_{RI} - t_{RC})(I_{Standby}))}{t_{RI}}$$

where  $t_{RC} = \text{refresh}$  cycle time, and  $t_{RI} = \text{refresh}$  interval time or  $t_{REF}/256$

### Static Column Mode Operation

Static column mode operation permits all 256 columns within a selected row of the device to be randomly accessed at a high data rate. Read, write and read-write-read cycles can be performed during static column mode operation. The row address is internally retained by maintaining RAS active. Following the entry cycle into static column mode operation, the data are accessed simply by changing the column address. Because the column address buffer acts as a transparent or flow-through latch, access begins from a valid column address. Thus, the V51C259HL operates like a static RAM for multiple accesses within the same row.  $\overline{CAS}$  acts as an output enable.

## **Data Out Operation**

The V51C259HL Input/Output (I/O) is controlled by  $\overline{OE}$ ,  $\overline{CAS}$ ,  $\overline{WE}$  and  $\overline{RAS}$ . A  $\overline{RAS}$  low transition enables data to transfer into and from a selected row address. A  $\overline{RAS}$  high transition disables data transfer and will latch the output data if the output is enabled. After a memory cycle is initiated by a  $\overline{RAS}$  low transition, a  $\overline{CAS}$  low transition or a  $\overline{CAS}$  low level enables the internal I/O data path. A  $\overline{CAS}$  high transition or a  $\overline{CAS}$  high transition or a  $\overline{CAS}$  high transition or a  $\overline{CAS}$  low transition while  $\overline{RAS}$  is high has no effect on the I/O

data path, nor on the output driver. An  $\overline{OE}$  low transition or an  $\overline{OE}$  low level enables the output driver when the I/O data path is enabled. An  $\overline{OE}$  high level disables the output driver, but does not disable the data latch when it has been enabled. A  $\overline{WE}$  low level disables the output driver when a  $\overline{CAS}$  low level occurs. If the  $\overline{WE}$  low transition occurs after the  $\overline{CAS}$  low transition such that the output driver is enabled prior to the  $\overline{WE}$  low transition, it is necessary to use  $\overline{OE}$  to disable the output driver prior to the  $\overline{WE}$  low transition to allow data in set-up time (tDS). A  $\overline{WE}$  high transition passes control of the output drive to  $\overline{OE}$ .

### Power On

An initial pause of 100  $\mu s$  is required after the application of the  $V_{DD}$  supply, followed by a minimum of eight initialization cycles (any combination of cycles containing a  $\overline{RAS}$  clock such as  $\overline{RAS}$ -Only refresh). Eight initialization cycles are required after extended periods of bias without clocks (greater than 32 ms).

The  $V_{DD}$  current ( $I_{DD}$ ) requirement of the V51C259HL during power on is dependent upon the input levels of  $\overline{RAS}$  and  $\overline{CAS}$ . If  $\overline{RAS} = V_{SS}$  during power on, the device will go into an active cycle and  $I_{DD}$  will exhibit large current transients. It is recommended that  $\overline{RAS}$  and  $\overline{CAS}$  track with  $V_{DD}$  or be held at a valid  $V_{IH}$  during power on.