## 11

#### 1.0 INTRODUCTION

#### 1.1 DESCRIPTION

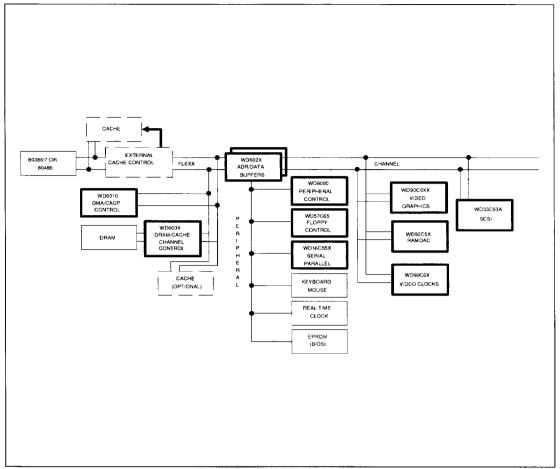

As part of the Western Digital® Micro Channel compatible chip sets (WD6500, WD6400SX, WD6400SX/LP), the WD6000 CPU and Peripheral Control Logic integrated circuit significantly facilitates the design and implementation of system boards compatible with IBM's Micro Channel architecture. It decreases the design complexity and saves space by combining the functions of many discrete arrays and components, while reducing system cost and increasing system reliability.

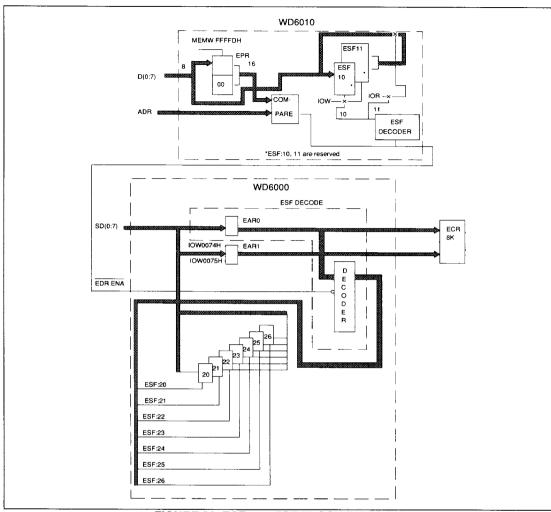

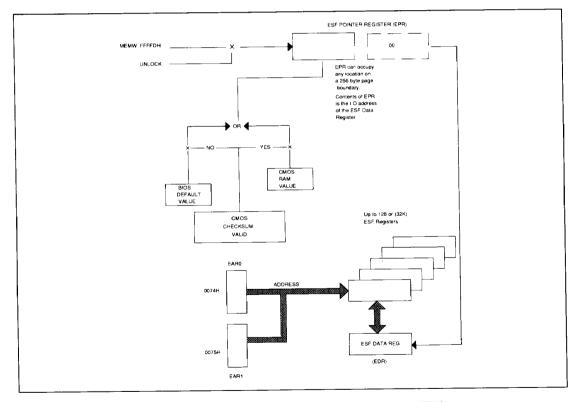

The Extended Setup Facility (ESF) is a fully compatible enhancement that allows designers to easily configure additional functionality such as a Winchester controller, LAN adapter, or an additional serial port on the system board. This facility can help reduce costs and provide system level product differentiation. Figure 1 shows a typical system diagram using Western Digital's Micro Channel compatible chip sets.

### 1.2 FEATURES

- Hardware (Register Level) and Software Compatible to the IBM Personal System/2 Micro Channel implementations

- Functionality equivalent to the following:

Two 8259 Interrupt Controllers

8254 Timer

Watchdog Timer Logic

System Board I/O Decode Logic

Peripheral Bus Control Generator

NMI Generator

Error Control Logic

- · Interfaces Directly to the Micro Channel

- Operates in an 80486, 80386DX or 80386SX System

- Math Coprocessor Support (80387/80387SX, Weitek 4167/3167 or compatible)

- Programmable Option Select (POS) Logic

- Clock Generation Logic for Math Coprocessor and Keyboard Controller

- Support for External CMOS RAM for storage of Configuration Data

- Extended Setup Facility<sup>™</sup> (ESF<sup>™</sup>)

- Low Power 1.25 Micron CMOS Technology

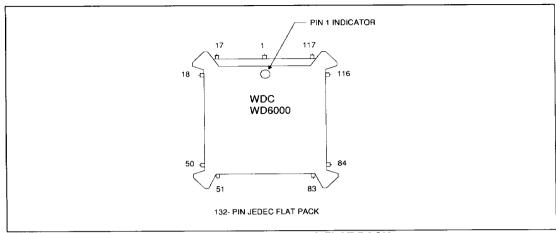

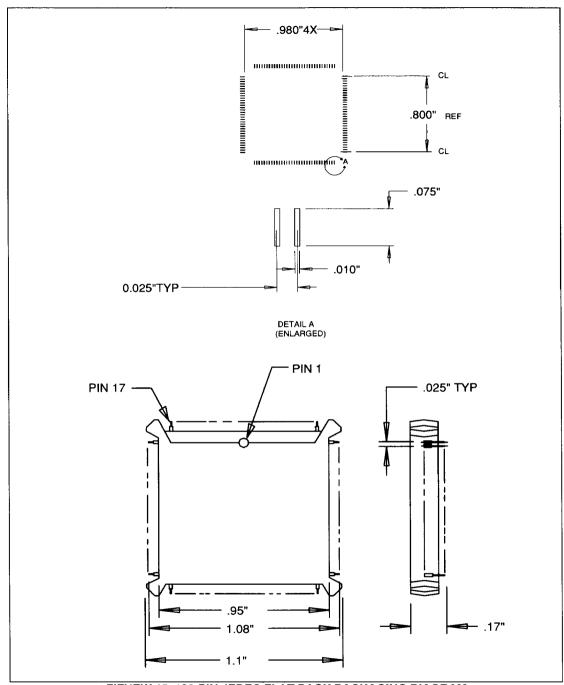

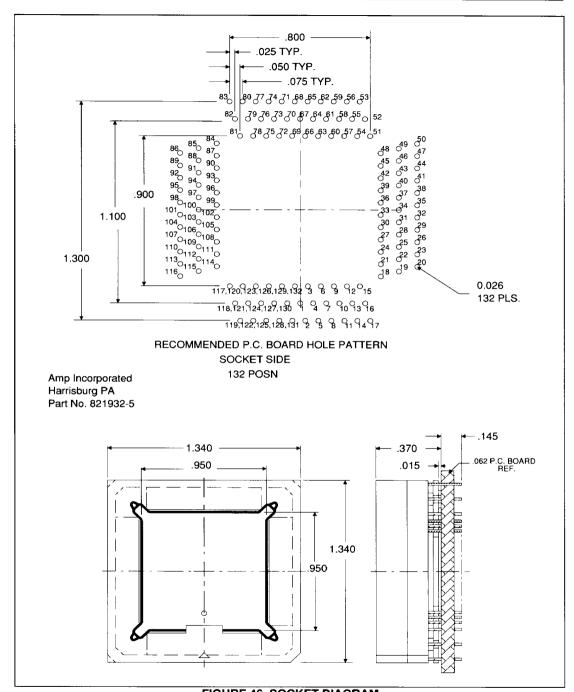

- 132-Lead JEDEC Plastic Quad Flat Pack

FIGURE 1. SYSTEM DIAGRAM

(DEVICES WITH BOLD OUTLINES AVAILABLE FROM WESTERN DIGITAL CORPORATION)

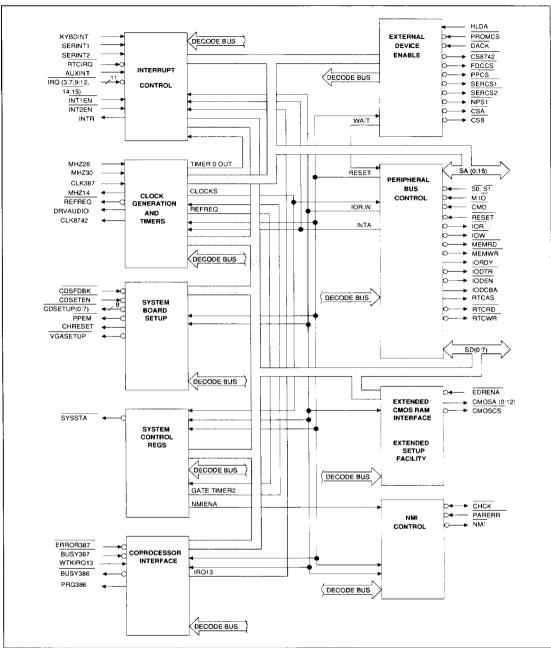

FIGURE 2. WD6000 BLOCK DIAGRAM

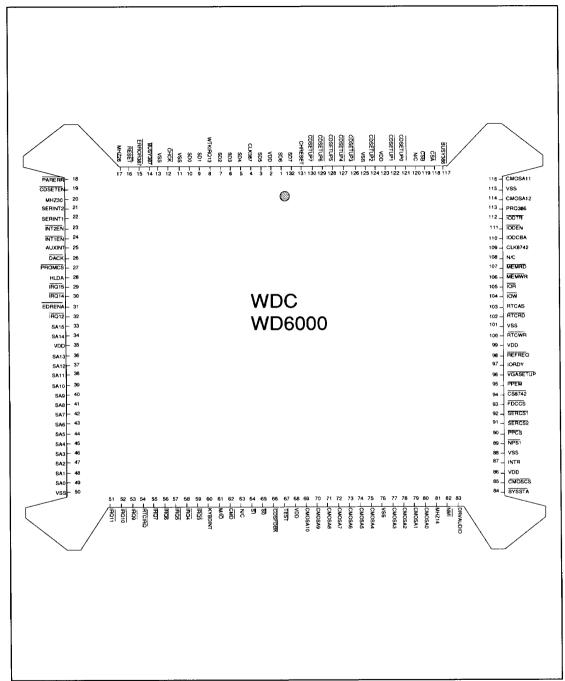

## 2.0 PIN DESCRIPTION

FIGURE 1. 132-PIN JEDEC FLAT PACK

| PIN    | NAME            | PIN | NAME      | PIN | NAME         | PIN | NAME            |

|--------|-----------------|-----|-----------|-----|--------------|-----|-----------------|

| 1      | SD6             | 34  | SA14      | 67  | TEST         | 100 | RTCWR           |

| 2<br>3 | $V_{DD}$        | 35  | $V_{DD}$  | 68  | $V_{DD}$     | 101 | V <sub>SS</sub> |

| 3      | SD5             | 36  | SA13      | 69  | CMOSA10      | 102 | RTCRD           |

| 4      | CLK387          | 37  | SA12      | 70  | CMOSA9       | 103 | RTCAS           |

| 5      | SD4             | 38  | SA11      | 71  | CMOSA8       | 104 | ĪOW             |

| 6      | SD3             | 39  | SA10      | 72  | CMOSA7       | 105 | ĪŌŔ             |

| 7      | SD2             | 40  | SA9       | 73  | CMOSA6       | 106 | MEMWR           |

| 8      | WTKIRQ13        | 41  | SA8       | 74  | CMOSA5       | 107 | MEMRD           |

| 9      | SD1             | 42  | SA7       | 75  | CMOSA4       | 108 | N/C             |

| 10     | SD0             | 43  | SA6       | 76  | $V_{SS}$     | 109 | CLK8742         |

| 11     | Vss             | 44  | SA5       | 77  | CMOSA3       | 110 | IODCBA          |

| 12     | CHCK            | 45  | SA4       | 78  | CMOSA2       | 111 | IODEN           |

| 13     | V <sub>SS</sub> | 46  | SA3       | 79  | CMOSA1       | 112 | IODTR           |

| 14     | BUSY387         | 47  | SA2       | 80  | CMOSA0       | 113 | PRQ386          |

| 15     | ERROR387        | 48  | SA1       | 81  | MHZ14        | 114 | CMOSA12         |

| 16     | RESET           | 49  | SA0       | 82  | NMI          | 115 | $V_{SS}$        |

| 17     | MHZ28_          | 50  | Vss       | 83  | DRVAUDIO     | 116 | CMOSA11         |

| 18     | PARERR          | 51  | IRQ11     | 84  | SYSSTA       | 117 | BUSY386         |

| 19     | CDSETEN         | 52  | IRQ10     | 85  | CMOSCS       | 118 | CSA             |

| 20     | MHZ30           | 53  | IRQ9      | 86  | $V_{DD}$     | 119 | CSB             |

| 21     | SERINT2         | 54  | RTCIRQ    | 87  | INTR         | 120 | N/C             |

| 22     | SERINT1         | 55  | IRQ7      | 88  | Vss          | 121 | CDSETUP0        |

| 23     | INT2EN          | 56  | IRQ6      | 89  | NPS1         | 122 | CDSETUP1        |

| 24     | INT1EN          | 57  | IRQ5      | 90  | PPCS         | 123 | $V_{DD}$        |

| 25     | AUXINT          | 58  | IRQ4      | 91  | SERCS2       | 124 | CDSETUP2        |

| 26     | DACK            | 59  | ĪRQ3      | 92  | SERCS1       | 125 | Vss             |

| 27     | PROMCS          | 60  | KYBDINT   | 93  | FDCCS        | 126 | CDSETUP3        |

| 28     | HLDA            | 61  | M/IO      | 94  | CS8742       | 127 | CDSETUP4        |

| 29     | IRQ15           | 62  | CMD       | 95  | PPEM         | 128 | CDSETUP5        |

| 30     | IRQ14           | 63  | N/C       | 96  | VGASETUP     | 129 | CDSETUP6        |

| 31     | EDRENA          | 64  | <u>§1</u> | 97  | <u>IORDY</u> | 130 | CDSETUP7        |

| 32     | IRQ12           | 65  | <u>S0</u> | 98  | REFREQ       | 131 | CHRESET         |

| 33     | SA15            | 66  | CDSFDBK   | 99  | $V_{DD}$     | 132 | SD7             |

| PIN NO.                                                        | NAME                                                                                      | TYPE      | FUNCTION                                                                                                                                                                                                                        |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                |                                                                                           | INTERRUP  | T CONTROL                                                                                                                                                                                                                       |

| 60                                                             | KYBDINT                                                                                   | I         | KEYBOARD INTERRUPT - Driven by the system keyboard controller.                                                                                                                                                                  |

| 22                                                             | SERINT1                                                                                   | •         | SERIAL INTERRUPT 1 - Internally switched with SERINT2 to share IRQ3 and IRQ4 under software control. The Program Control Register (PCR) and Setup Register 0102H are used to assign the serial interrupt signals.               |

| 21                                                             | SERINT2                                                                                   | I         | SERIAL INTERRUPT 2 - Internally switched with<br>SERINT1 to share IRQ3 and IRQ4 under<br>software control. The Program Control Register<br>(PCR) and Setup Register 0102H are used to as-<br>sign the serial interrupt signals. |

| 54                                                             | RTCIRQ                                                                                    | 1         | REAL-TIME CLOCK INTERRUPT - Generated by the system Real-Time Clock module.                                                                                                                                                     |

| 25                                                             | AUXINT                                                                                    | 1         | AUXILIARY INTERRUPT - Driven by the system keyboard controller.                                                                                                                                                                 |

| 59<br>58<br>57<br>56<br>55<br>53<br>52<br>51<br>32<br>30<br>29 | IRQ3<br>IRQ4<br>IRQ5<br>IRQ6<br>IRQ7<br>IRQ9<br>IRQ10<br>IRQ11<br>IRQ12<br>IRQ14<br>IRQ15 | 1         | INTERRUPT REQUESTS - Asynchronous inputs that may be shared by other interrupting devices.                                                                                                                                      |

| 24                                                             | INT1EN                                                                                    | 1         | SERIAL INTERRUPT 1 ENABLE - System generated programmable output that gates the interrupt signal SERINT1 from the associated serial device. This line must be grounded to enable the interrupt.                                 |

| 23                                                             | INT2EN                                                                                    | ı         | SERIAL INTERRUPT 2 ENABLE - System generated programmable output that gates the interrupt signal SERINT2 from the associated serial device. Line must be grounded to enable the interrupt.                                      |

| 87                                                             | INTR                                                                                      | 0         | INTERRUPT - Drives the system CPU interrupt pin.                                                                                                                                                                                |

|                                                                | CL                                                                                        | OCK GENER | RATION & TIMERS                                                                                                                                                                                                                 |

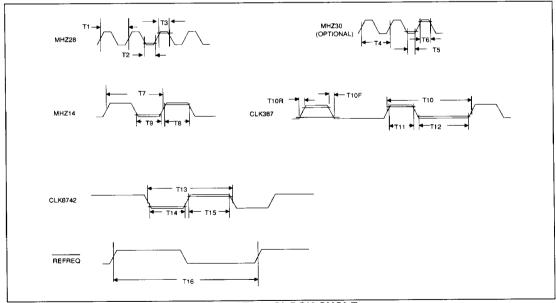

| 17                                                             | MHZ28                                                                                     | 1         | 28.636 MHz - Basic clock used for all WD6000 internal functions (timers, wait generator, bus interface logic.                                                                                                                   |

| NAME     | TYPE                                                           | FUNCTION                                                                                                                                                                                                                                      |

|----------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | GENERATION                                                     | & TIMERS, Continued                                                                                                                                                                                                                           |

|          | ı                                                              | 30.0 MHz - Drives the coprocessor and keyboard                                                                                                                                                                                                |

|          |                                                                | clock outputs appropriately. See Pin 109 below.                                                                                                                                                                                               |

| MHZ14    | 0                                                              | 14.318 MHz - This clock output drives the Chan-                                                                                                                                                                                               |

|          |                                                                | nel OSC line.                                                                                                                                                                                                                                 |

| REFREQ   | 0                                                              | REFRESH REQUEST - Timer output used to re-                                                                                                                                                                                                    |

|          |                                                                | quest a refresh cycle by the CACP and DMA con-                                                                                                                                                                                                |

|          |                                                                | troller.                                                                                                                                                                                                                                      |

| DRVAUDIO | 0                                                              | DRIVE AUDIO - Drives the audio summing net-                                                                                                                                                                                                   |

|          | ·                                                              | work shared by the Channel audio line and Timer                                                                                                                                                                                               |

|          |                                                                | 2 OUT gated by Control Port B (0061H) bit 0.                                                                                                                                                                                                  |

| CLK8742  | 0                                                              | 8742 CLOCK - Drives the keyboard controller. It                                                                                                                                                                                               |

|          |                                                                | is derived from the 30 MHz clock input divided by                                                                                                                                                                                             |

|          |                                                                | 3 if the MHZ30 clock input is present. If the                                                                                                                                                                                                 |

|          |                                                                | MHZ30 clock input is connected to the MHZ28                                                                                                                                                                                                   |

|          |                                                                | clock, then the keyboard clock (CLK8742), is derived from the MHZ28 clock input divided by 3,                                                                                                                                                 |

|          |                                                                | and a math coprocessor will not be supported.                                                                                                                                                                                                 |

| CI V297  | 1                                                              | For systems using an 80387 or 80387SX, this                                                                                                                                                                                                   |

| CLN367   | '                                                              | pin should be connected to the CLK phase of the                                                                                                                                                                                               |

|          |                                                                | coprocessor. It is used to synchronize the                                                                                                                                                                                                    |

|          |                                                                | coprocessor logic to the coprocessor clock. For                                                                                                                                                                                               |

|          |                                                                | systems with non-Intel coprocessors, this pin                                                                                                                                                                                                 |

|          |                                                                | should be left unconnected.                                                                                                                                                                                                                   |

|          | SYSTEM B                                                       | OARD SETUP                                                                                                                                                                                                                                    |

| CDSFDBK  | I                                                              | CARD SELECTED FEEDBACK - This Channel                                                                                                                                                                                                         |

|          |                                                                | signal indicates the addressed slave is present.                                                                                                                                                                                              |

| CDSETEN  | 1                                                              | CARD SETUP ENABLE - Timing decode for the                                                                                                                                                                                                     |

|          |                                                                | 0100H-0107H from the WD6010.                                                                                                                                                                                                                  |

| CDSETUP0 | 0                                                              | CARD SETUP - Each signal drives a Channel                                                                                                                                                                                                     |

|          |                                                                | slot.                                                                                                                                                                                                                                         |

|          |                                                                |                                                                                                                                                                                                                                               |

|          |                                                                |                                                                                                                                                                                                                                               |

|          |                                                                |                                                                                                                                                                                                                                               |

|          |                                                                |                                                                                                                                                                                                                                               |

|          |                                                                |                                                                                                                                                                                                                                               |

|          |                                                                | DARALLEL PORT EXTENDED MODE When                                                                                                                                                                                                              |

| PPEM     | U                                                              | PARALLEL PORT EXTENDED MODE - When asserted, this signal puts the parallel port into Ex-                                                                                                                                                      |

|          |                                                                |                                                                                                                                                                                                                                               |

| OURSOFT  |                                                                | tended (bidirectional) Mode.                                                                                                                                                                                                                  |

| CHRESET  | U                                                              | CHANNEL RESET - This software-generated sig-<br>nal resets all Channel resident adapters and sys-                                                                                                                                             |

|          |                                                                | tem board I/O devices only. Located in register                                                                                                                                                                                               |

|          |                                                                | 0096H Bit 7.                                                                                                                                                                                                                                  |

| VOACETUD | +                                                              | VGA SETUP - Tells the VGA device to enter                                                                                                                                                                                                     |

| VGASETUP |                                                                | I VOA SETUE FIENS THE VOA GEVICE TO CHIEN                                                                                                                                                                                                     |

|          | CLOCK MHZ30 (optional) MHZ14 REFREQ  DRVAUDIO  CLK8742  CLK387 | CLOCK GENERATION MHZ30   1 (optional) MHZ14   O  REFREQ   O  DRVAUDIO   O  CLK8742   O  CLK387   I  CDSETUPO   O  CDSETUPO   O  CDSETUP1   CDSETUP2   CDSETUP3   CDSETUP4   CDSETUP4   CDSETUP5   CDSETUP6   CDSETUP7   PPEM   O  CHRESET   O |

| PIN NO. | NAME     | TYPE      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | SY       | STEM CONT | ROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                   |

| 84      | SYSSTA   | 0         | SYSTEM STATUS - This signal is used to drive a hard disk active LED.                                                                                                                                                                                                                                                                                                                                            |

|         | С        | OPROCESS  | OR INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                    |

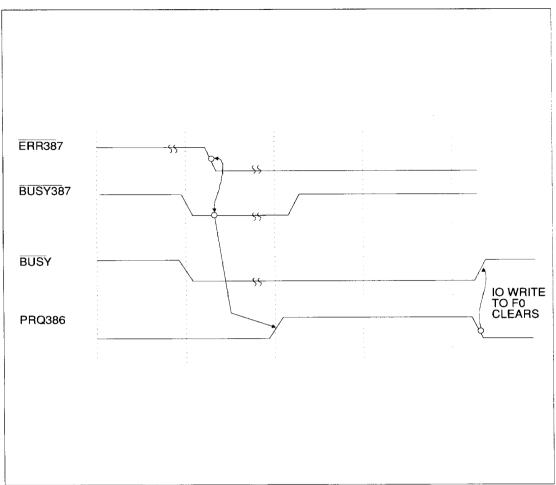

| 15      | ERROR387 | l         | ERROR 387 - Driven by the coprocessor, this signal indicates the coprocessor has encountered an error condition which causes an interrupt (13H) to be issued and holds the BUSY386 signal in the busy state. The busy and interrupt are cleared by issuing an 8-bit I/O write command to location 00F0H with data equal to 00H. For 80387/80387SX-based systems, this pin should be connected to the ERROR pin. |

| 14      | BUSY387  | I         | BUSY 387 - Driven by the coprocessor, this signal indicates the coprocessor is currently executing a command. This can also be used on 80386SX/80387SX-based systems.                                                                                                                                                                                                                                           |

| 117     | BUSY386  | 0         | BUSY 386 - Indicates the coprocessor is currently executing a command.                                                                                                                                                                                                                                                                                                                                          |

| 8       | WTKIRQ13 | 1         | For systems implementing a Weitek 4167/3167 (or compatible) math coprocessor, this pin should be connected to the IRQ13 pin of the EMC (Extended Math Coprocessor) socket. It is used to generate an interrupt 13 to the system when the Weitek coprocessor requires service.  This pin has dual functions. At power up (trailing                                                                               |

|         |          |           | edge of RESET), the state of this pin is latched to determine whether the WD6000 will implement an 80386 or 80386SX-compatible math interface.                                                                                                                                                                                                                                                                  |

|         |          |           | For an 80386/80386SX/80486 system, this pin should be pulled down with a 100 ohm resistor.                                                                                                                                                                                                                                                                                                                      |

|         |          |           | For an 80386/80386SX/80486 system which includes a Weitek (or compatible) coprocessor, this pin should be connected to the IRQ13 pin of the Weitek device.                                                                                                                                                                                                                                                      |

| 113     | PRQ386   | 0         | The PRQ386 signal is OR'ed with the coprocessor request (PEREQ) to drive the PRQ386 signal to the CPU high to allow the coprocessor to complete any pending data transfers.                                                                                                                                                                                                                                     |

|         | E        | XTERNAL D | EVICE ENABLE                                                                                                                                                                                                                                                                                                                                                                                                    |

| 28      | HLDA     | 1         | BUS HOLD ACKNOWLEDGE - This line indicates when the CPU has given the system local bus to another master (Channel bus master or DMA controller). It is used to prevent non-system CPU access to locations 0000-00FFH in the WD6000 during master cycles.                                                                                                                                                        |

| PIN NO.                          | NAME                                                 | TYPE      | FUNCTION                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------|------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FIN NO.                          |                                                      |           | ENABLE, Continued                                                                                                                                                                                                                                                                                                                                    |

| 27                               | PROMCS                                               | I         | PROM CHIP SELECT - This signal indicates an access to a PROM location and is activated on read accesses to the PROM address spaces E0000 - FFFFFH, FE0000 - FFFFFFH (80386SX systems), or FFFE0000 - FFFFFFFH (80386 systems). This line is used by the Wait/Ready in the WD6030 logic to control the length of the channel cycle for PROM accesses. |

| 26                               | DACK                                                 | 1         | FLOPPY DMA ACKNOWLDGE - This pin is activated on a DMA Transfer to the floppy disk. It is used by the Wait/Ready logic in the WD6030 to control the length of the channel cycle for the floppy DMA.                                                                                                                                                  |

| 94                               | CS8742                                               | 0         | CHIP SELECT 8742 - This signal is the chip select to the keyboard/auxiliary device controller.                                                                                                                                                                                                                                                       |

| 93                               | FDCCS                                                | 0         | FLOPPY DISK CONTROLLER CHIP SELECT -<br>This signal is the chip select to the floppy disk<br>controller.                                                                                                                                                                                                                                             |

| 90                               | PPCS                                                 | 0         | PARALLEL PORT CHIP SELECT - This signal is the chip select to the parallel port controller.                                                                                                                                                                                                                                                          |

| 92                               | SERCS1                                               | 0         | SERIAL CHIP SELECT 1 - This signal is the chip select for the first serial port controller.                                                                                                                                                                                                                                                          |

| 91                               | SERCS2                                               | 0         | SERIAL CHIP SELECT 2 - This signal is the chip select for the second serial port controller.                                                                                                                                                                                                                                                         |

| 89                               | NPS1                                                 | 0         | NUMERIC PROCESSOR SELECT - This signal is the chip select for the math coprocessor.                                                                                                                                                                                                                                                                  |

| 118                              | CSA                                                  | 0         | CHIP SELECT A - This signal is a software-programmable chip select.                                                                                                                                                                                                                                                                                  |

| 119                              | CSB                                                  | 0         | CHIP SELECT B - This signal is a software-programmable chip select.                                                                                                                                                                                                                                                                                  |

|                                  | P                                                    | ERIPHERAL | BUS CONTROL                                                                                                                                                                                                                                                                                                                                          |

| 10<br>9<br>7<br>6<br>5<br>3<br>1 | SD0<br>SD1<br>SD2<br>SD3<br>SD4<br>SD5<br>SD6<br>SD7 | I/O       | SYSTEM DATA - Theses bi-directional lines are the low byte of data from the Channel data bus (buffered).                                                                                                                                                                                                                                             |

| PIN NO. | NAME           | TYPE     | FUNCTION                                          |

|---------|----------------|----------|---------------------------------------------------|

|         | PERIPH         | ERAL BUS | CONTROL, Continued                                |

| 49      | SA0            | 1        | SYSTEM ADDRESS - These 16 address lines           |

| 48      | SA1            |          | are used to decode the appropriate locations of   |

| 47      | SA2            |          | the system CPU 64K I/O space. These lines         |

| 46      | SA3            |          | should be connected to the channel address bus    |

| 45      | SA4            |          | (015).                                            |

| 44      | SA5            |          |                                                   |

| 43      | SA6            |          |                                                   |

| 42      | SA7            |          |                                                   |

| 41      | SA8            |          |                                                   |

| 40      | SA9            |          |                                                   |

| 39      | SA10           |          |                                                   |

| 38      | SA11           |          |                                                   |

| 37      | SA12           |          |                                                   |

| 36      | SA13           |          |                                                   |

| 34      | SA14           |          |                                                   |

| 33      | SA15           |          |                                                   |

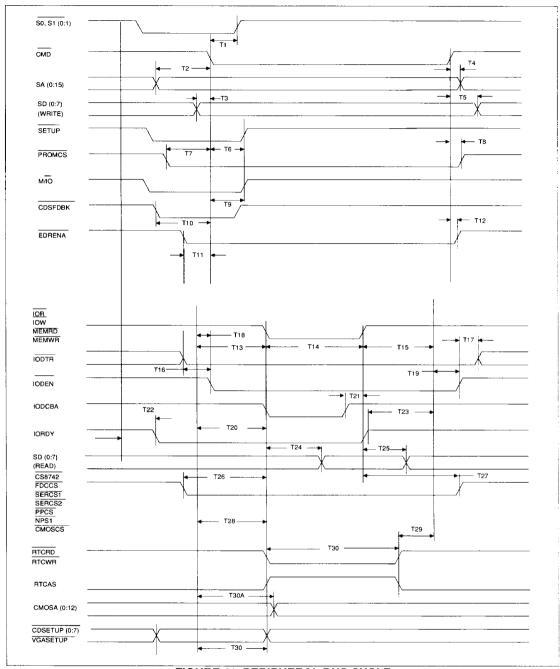

| 65      | <u>80</u>      | 1        | CHANNEL STATUS and MEMORY I/O - These             |

| 64      | <u>S1</u>      |          | three lines encode information on the type of     |

| 61      | M/ĪO           |          | Channel bus cycle.                                |

| 62      | CMD            | I        | COMMAND - This signal defines when data to or     |

|         |                |          | from the Channel is valid.                        |

| 16      | RESET          | I        | RESET - This signal initializes all the internal  |

|         |                |          | logic to a power-on state.                        |

| 105     | ĪOR            | 0        | I/O READ, I/O WRITE, MEMORY READ and              |

| 104     | <del>IOW</del> |          | MEMORY WRITE - These signals comprise the         |

| 107     | MEMRD          |          | command information for peripheral bus cycles     |

| 106     | MEMWR          |          | and track the Channel cycle.                      |

| 97      | IORDY          | 0        | I/O READY - This signal indicates the WD6000 is   |

|         |                |          | finished with the current bus cycle. It is deac-  |

|         |                |          | tivated to extend the current Channel cycle.      |

| 112     | IODTR          | 0        | I/O DATA TRANSMIT/RECEIVE, I/O DATA               |

| 111     | IODEN          | 0        | ENABLE, I/O DATA CLOCK (latches when clock        |

| 110     | IODCBA         | 0        | is low) - These three lines control the address   |

|         |                |          | and data buffer latches for the peripheral bus.   |

|         |                |          | The I/O data transmit/receive signal controls the |

|         |                |          | direction of the I/O data buffers inside the      |

|         |                |          | WD6022. If IODTR is low, the WD6022 drives        |

|         |                |          | data from IOD (0:15) to D (0:15), and if IODTR is |

|         |                |          | high, the WD6022 drives data from D (0:15) to     |

|         |                |          | IOD (0:15). IODEN enables the I/O data buffers.   |

|         |                |          | When active, the WD6022 drives either the D       |

|         |                |          | (0:15) to IOD (0:15), depending on the direction  |

|         |                |          | set by IODTR. The I/O data clock (IODCBA) is      |

|         |                |          | used to latch the data during reads from the      |

|         |                |          | Channel peripherals on the I/O bus.               |

| PIN NO.                                                               | NAME                                                                                          | TYPE      | FUNCTION                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                       | PERIP                                                                                         | HERAL BUS | CONTROL, Continued                                                                                                                                                                                                                                                                                                                                       |

| 103                                                                   | RTCAS                                                                                         | 0         | REAL-TIME CLOCK ADDRESS SELECT - This signal latches the address into the Real-Time Clock module.                                                                                                                                                                                                                                                        |

| 102<br>100                                                            | RTCRD<br>RTCWR                                                                                | 0         | REAL-TIME CLOCK READ/WRITE - These two lines are the command lines to the Real-Time Clock module.                                                                                                                                                                                                                                                        |

|                                                                       | EXT                                                                                           | ENDED CMO | S RAM INTERFACE                                                                                                                                                                                                                                                                                                                                          |

| 31                                                                    | EDRENÁ                                                                                        | I         | ESF DATA REGISTER PORT ENABLE - This sig nal from the WD6010 indicates that the ESF Data Register is being read or written to.                                                                                                                                                                                                                           |

| 80<br>79<br>78<br>77<br>75<br>74<br>73<br>72<br>71<br>70<br>69<br>116 | CMOSA0 CMOSA1 CMOSA2 CMOSA3 CMOSA4 CMOSA5 CMOSA6 CMOSA7 CMOSA8 CMOSA9 CMOSA10 CMOSA11 CMOSA12 | 0         | CMOS ADDRESS - These 13 lines are used to address the Extended CMOS RAM.                                                                                                                                                                                                                                                                                 |

| 85                                                                    | CMOSCS                                                                                        | 0         | CMOS CHIP SELECT - This line is used to select the Extended CMOS RAM.                                                                                                                                                                                                                                                                                    |

|                                                                       |                                                                                               | NMI C     | ONTROL                                                                                                                                                                                                                                                                                                                                                   |

| 12                                                                    | СНСК                                                                                          | I/O       | CHANNEL CHECK - This signal is the channel error indication. It is driven by bus resident adapters. During a bus master DRAM cycle, the system board drives this line if a parity error occurs. When this signal is an output, it is an open collector output.                                                                                           |

| 18                                                                    | PARERR                                                                                        | 1         | PARITY ERROR - This signal is the output of the<br>DRAM controller parity generator.                                                                                                                                                                                                                                                                     |

| 82                                                                    | NMI                                                                                           | 0         | NON-MASKABLE INTERRUPT - When driven be the WD6010 to the CPU, NMI indicates the CACP has reached a bus timeout condition while monitoring the bus. When the signal is received by the WD6010 fromn the WD6000, it instructs the CACP in the WD6010 to initiate an arbitration cycle to remove any bus masters so the the CPU can service the interrupt. |

| PIN NO.                           | NAME            | TYPE   | FUNCTION                                                                                                                                                                                                                                                                         |

|-----------------------------------|-----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   |                 | MISCEL | LANEOUS                                                                                                                                                                                                                                                                          |

| 2,35,68,<br>86,99,123             | V <sub>DD</sub> | I      | +5 Power Supply                                                                                                                                                                                                                                                                  |

| 11,13,50,<br>76,88,101<br>115,125 | V <sub>SS</sub> | ı      | 0 V Ground                                                                                                                                                                                                                                                                       |

| 63,108,<br>120                    | N/C             | -      | Not Connected                                                                                                                                                                                                                                                                    |

| 67                                | TEST            | ı      | TEST PIN - This is an active low pin that facilitates board-level testing. When low, this signal tri-states all outputs and bi-directional signal lines, allowing an ATE tester to drive these signals. When high, the outputs and bi-directional lines are enabled by the chip. |

The WD6500 and WD6400SX I/O map is shown in Table 1.

| ADDRESS RANGE                 | LOCATION | FUNCTION                              |

|-------------------------------|----------|---------------------------------------|

| 0000 to 000FH                 | WD6010   | DMA Controller, Channels 0-3 [1]      |

| 0018H                         | WD6010   | Extended Function Register [1]        |

| 001AH                         | WD6010   | Extended Function Execute [1]         |

| 0020 to 0021H                 | WD6000I  | Interrupt Controller 1 (Master)       |

| 0040, 0042-0044, 0047H        | WD6000   | System Timers                         |

| 0060H                         | WD6000   | Keyboard Data Port                    |

| 0061H                         | WD6000   | System Control Port B                 |

| 0064H                         | WD6000   | RD=Kybd status, WR=Kybd command       |

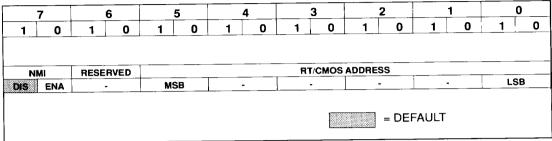

| 0070H                         | WD6000   | RTC/CMOS Addr. Register, NMI Mask     |

| 0071H                         | WD6000   | RTC/CMOS Data Port                    |

| 0074H                         | WD6000   | EAR0 Extended CMOS RAM, ESF           |

| 0075H                         | WD6000   | EAR1 Extended CMOS RAM                |

| 0076H                         | WD6000   | Extended CMOS RAM data port           |

| 0081 to 0083, 0087H           | WD6010   | DMA Page Registers (0-3)[1]           |

| 0089 to 008B, 008FH           | WD6010   | DMA Page Registers (4-7)[1]           |

| 0090H                         | WD6010   | Central Arbitration Control Point [1] |

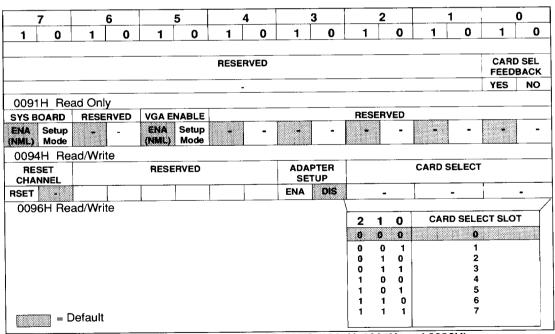

| 0091H                         | WD6000   | Card Selected Feedback                |

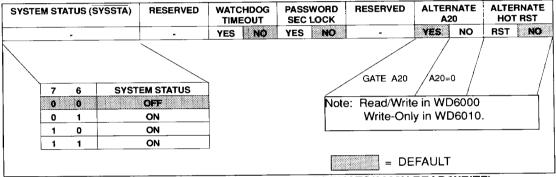

| 0092H                         | WD6000   | System Control Port A                 |

| 0094H                         | WD6000   | System Board Setup                    |

| 0096, 0097H                   | WD6000   | POS, Channel Connector Select         |

| 00A0 to 00A1H                 | WD6000   | Interrupt Controller 2 (Slave)        |

| 00C0 to 00DFH                 | WD6010   | DMA Controller (4 to 7)[1]            |

| 00F0H                         | WD6000   | Coprocessor Clear Busy                |

| 00F1H                         | WD6000   | Coprocessor Reset                     |

| 00F8 to 00FFH                 | WD6000   | Coprocessor                           |

| 0100, 0101H                   | WD6000   | System ID                             |

| 0102 to 0107H                 | WD6000   | System Board Configuration (POS)      |

| 0278 to 027BH                 | WD6000   | Parallel Port 3                       |

| 02F8 to 02FFH                 | WD6000   | Alternate Serial Port                 |

| 0378 to 037BH                 | WD6000   | Parallel Port 2                       |

| 03BC to 03BFH                 | WD6000   | Parallel Port 1                       |

| 03B4, 03B5, 03BA, 03C0-03C5H  | VIDEO    | Video Subsystem [2]                   |

| 03CE, 03CF, 03D4, 03D5, 03DAH | VIDEO    | Video Subsystem [2]                   |

| 03C6 to 03C9H                 | VIDEO    | Video DAC [2]                         |

| 03F0 to 03F7H                 | WD6000   | Diskette Drive Controller             |

| 03F8 to 03FFH                 | WD6000   | Primary Serial Port                   |

| 0700H                         | WD6010   | ESF Data Register (Default)           |

TABLE 1. SYSTEM LEVEL I/O MAP

<sup>[1]</sup> No Channel cycle is generated on these I/O addresses [2] I/O location 03C3H (VGA Enable Register) is in WD6010.

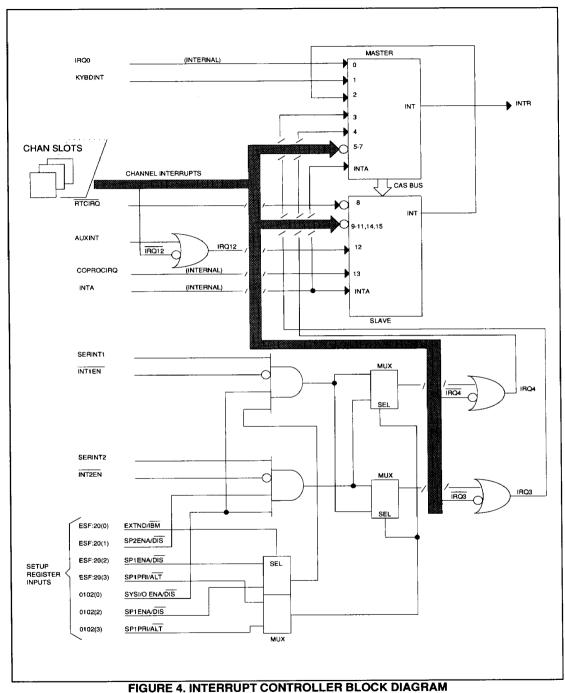

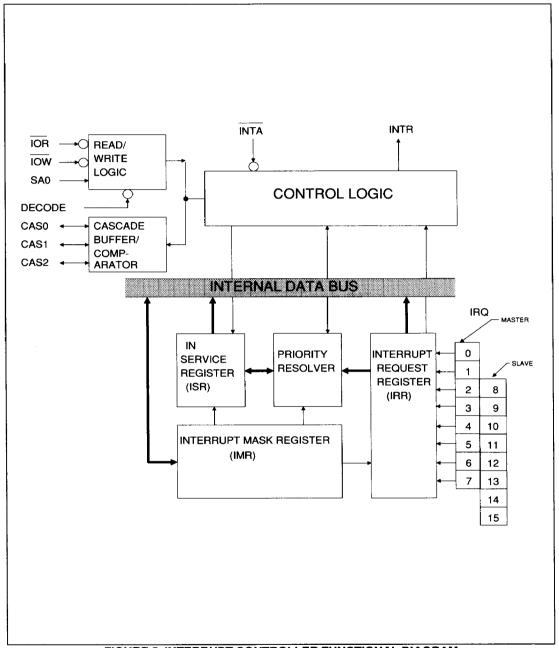

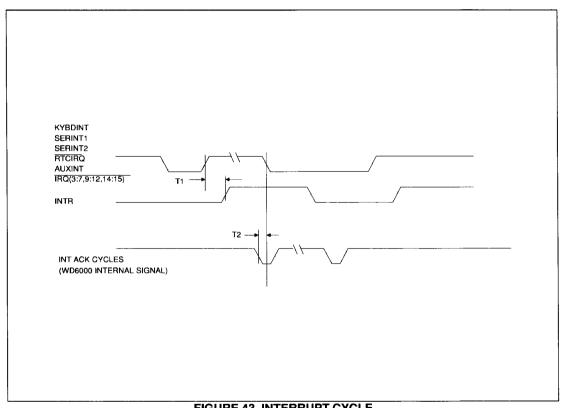

#### 3.0 INTERRUPT CONTROLLER

The Interrupt Controller is functionally equivalent to two Intel 8259 controllers cascaded together. It operates in level-sensitive mode and controls sixteen levels of interrupts, five interna,I and eleven system interrupts. Interrupt Controller 1 is the master controller, located at I/O space 0020H and 0021H. Interrupt Controller 2 is the slave and is located at I/O space 00a0H and 00A1H. Interrupt Request 2 (IRQ2) from Interrupt Controller 1 is used to cascade the two controllers, as illustrated in Figure 4.

The edge trigger mode is not available. Any or all of the interrupts may be masked. The non-maskable interrupt may be masked by setting Register (0070H) Bit 7.

Interrupts may be shared by more than one hardware interrupt. Table 2 shows the interrupt assignments in a typical system environment.

The auxiliary and serial port interrupt signals are discussed below:

- AUXINT is the interrupt from the auxiliary device. It is an active high input that is ORed with IRQ12 from the Channel. It is treated exactly like an IRQ12 interrupt.

- SERINT1 is an active high interrupt from Serial Port 1 (SP1). SERINT1 is masked by INT1EN, which must be low in order to detect SERINT1. SERINT1 is ORed with IRQ3 or IRQ4, depending on the programming. If SP1 is enabled (See Section 4.0), and it is programmed to Alternate Addresses 02F8 -02FFH, SERINT 1 is treated as IRQ3. It is treated as IRQ4 when SP1 is programmed to Primary Addresses 03F8 - 03FFH.

- SERINT2 is an active high interrupt from Serial Port 2 (SP2). SERINT2 is masked by INT2EN, which must be low in order to detect SERINT2. SERINT2 is ORed with IRQ3 or IRQ4, depending on the programming. If SP2 is enabled (See Section 9.2.3), and it is programmed to Primary Addresses 03F8 -03FFH, SERINT2 is treated as IRQ4. It is treated as IRQ3 when SP2 is programmed to Alternate Addresses 02F8 - 02FFH.

## 3.1 INTERRUPT CONTROLLER OPERATION

Figure 5 contains a functional diagram of an interrupt controller in the WD6000, providing an operational representation of how each controller works. The various interrupt controller functions are described below.

# 3.1.1 Interrupt Request Register (IRR) and In-Service Register (ISR)

Interrupts are handled by the IRR and the ISR. The IRR stores all the interrupt levels that are being serviced.

## 3.1.2 Priority Resolver

This function decodes the priorities of the bits set in the IRR. The highest priority is selected and strobed into the corresponding bit of the ISR during the INTA cycle.

### 3.1.3 Interrupt Mask Register

The IMR stores the bits that mask selected interrupt lines. Masking a higher priority input does not affect lower priority interrupt request lines.

## 3.1.4 Read/Write Control Logic

This function accepts commands from the CPU and allows the status of the Interrupt Controller to be read on the Data Bus. It contains the Initialization Command Word (ICW) and Operation Command Word (OCW) registers, that store the various control formats for device operation.

## 3.1.5 Cascade Buffer/Comparator

This function stores and compares the ID of the slave controller. In the WD6000 Interrupt Controller configuration, the CAS bus is an output from the master and an input to the slave. When a slave request line is activated and acknowledged, the master sends the ID of the slave, fixed at 2, to the CAS bus. This enables the slave to send its pre-programmed subroutine address to the data bus during the second INTA cycle. All handshaking is handled internally.

| SYSTEM SOURCE        | CHANNEL | LEVEL  |

|----------------------|---------|--------|

| Timer                | -       | 0 [1]  |

| Keyboard Port        | -       | 1      |

| Cascade              |         | 2 [1]  |

| Alternate Srial Port | IRQ3    | 3      |

| Primary Serial Port  | IRQ4    | 4      |

| Reserved             | IRQ5    | 5      |

| Floppy Disk          | IRQ6    | 6      |

| Parallel Port        | IRQ7    | 7      |

| RTC                  | -       | 8      |

| Cascade Redirectd    | IRQ9    | 9      |

| Reserved             | IRQ10   | 10     |

| Reserved             | 1RQ11   | 11     |

| Mouse/Auxiliary      | IRQ12   | 12     |

| Coprocessor          | -       | 13 [1] |

| Hard Disk            | IRQ14   | 14     |

| Reserved             | IRQ15   | 15     |

<sup>[1]</sup> This interrupt is internally generated in the WD6000.

**TABLE 2. INTERRUPT SHARING**

### 3.2 INTERRUPT SEQUENCE

The sequence of events that make up an interrupt system environment are described below:

- One or more interrupts arrive from a peripheral device which sets the corresponding bit(s) in the IRR.

- 2. The request is evaluated and if the interrupt has not been masked, it is passed to the priority circuit and the Interrupt Controller sends an interrupt (INTR) to the CPU.

- 3. The CPU responds to the interrupt with an INTA cycle.

- 4. When the INTA is received, the priority is frozen and the highest priority ISR bit is set. The Interrupt Controller does not drive the data bus during this cycle.

- 5. The CPU initiates another INTA cycle that causes the Interrupt Controller to send an 8-bit vector to the CPU. Either the master or slave may be programmed to send the byte of data. As long as the ISR bit is set, all interrupts at the same level or lower are inhibited. In Special Mask

Mode (SMM), only interrupts at the same level are inhibited. If a higher priority interrupt occurs during an interrupt service routine, it is only acknowledged if the CPU internal interrupt enable has been re-enabled.

When the slave issues an interrupt, other interrupts from the slave are locked out. To preserve priority in the slave, that is, to allow higher interrupts to occur when a power interrupt is being serviced, Special Fully Nested Mode (SFNM) should be programmed in the master. See Section 2.9.4 for more details.

6. At the end of the second INTA cycle, one or two End-of-Interrupt (EOI) commands must be issued to complete the interrupt; one for the master and the other for the slave. This clears the appropriate bit in the ISR.

### 3.3 END OF INTERRUPT

There are three EOI commands: Specific, Non-Specific, and Automatic. When the Interrupt Controller is programmed to operate in modes that preserve fully nested interrupts, the CPU can determine which ISR bit to reset on EOI, since the

FIGURE 5. INTERRUPT CONTROLLER FUNCTIONAL DIAGRAM

(TYPICAL MASTER OR SLAVE)

4

current highest priority ISR bit is necessarily the last level acknowledged and serviced. In this case, a non-specific EOI can be issued. In Special Mask Mode, an ISR bit that is masked in the IMR is not cleared by a non-specific EOI.

When the fully nested structure is not preserved, a Specific EOI must be issued at the end of the interrupt service routine, which includes the ISR bit to reset. Both Specific and Non-Specific EOIs are issued with OCW2.

Automatic EOI (AEOI) automatically occurs on the trailing edge of the second INTA cycle. AEOI can only be used for the master, not the slave. AEOI is set with ICW4.

#### 3.4 POLLED MODE

The Interrupt Controller may also be operated in Polled Mode. In this mode, interrupts should be masked by the CPU. An interrupt is detected when the software issues a poll command, setting P = 1 in OCW3. This results in an equivalent INTA cycle during the next read operation to the Interrupt Controller (i.e., IOR = 0, DECODE = 0) which sets the IS bit, if a request was made, and allows the priority level to be read. See Figure 6. The IRR remains frozen until the read cycle is complete. At the end of the process, Polled Mode is reset to zero.

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

| 1  | -  | -  | -  | -  | W2 | W1 | Wo |

W0-W2: Binary code of the highest priority level requesting service.

I: Equal to "1" if there is an interrupt.

## FIGURE 6. INTERRUPT PRIORITY LEVEL USING THE POLL COMMAND

## 3.5 INTERRUPT PRIORITY

There are three types of interrupt priority:

- Fixed Priority

- Automatic Rotation

- Specific Rotation

### 3.5.1 Fixed Priority

In this mode, the interrupts are fully nested; IRQ0 is assigned the highest priority, and IRQ7 the lowest priority. Fixed priority is the default condition, unless Automatic or Specific Rotation is programmed with OCW3.

#### 3.5.2 Automatic Rotation

Automatic Rotation is useful for applications where a number of interrupting devices have equal priority, as the priority is rotated between them. In this mode, the last interrupt serviced has the lowest priority. Figures 7 and 8 show the status of the ISR before and after Automatic Rotation. Once the interrupt with the highest priority (IRQ4 in Figure 7) has been serviced, its status changes from the highest to the lowest priority, as illustrated in Figure 7.

| IRQ7      | IRQ6     | IRQ5       | IRQ4 | IRQ3 | IRQ2     | IRQ1   | IRQ0         |

|-----------|----------|------------|------|------|----------|--------|--------------|

| 0         | 1        | 0          | 1    | 0    | 0        | 0      | 0            |

| IRQ       | STATL    | IS         |      |      | -        |        |              |

| 1         |          |            |      |      |          |        |              |

| Lowe      | est Pric | rity       |      |      | Hig      | hest P | riority      |

| Lowe<br>3 | est Pric | ority<br>1 | 0    | 7    | Hig<br>6 | hest P | riority<br>4 |

FIGURE 7. INTERRUPT PRIORITY BEFORE AUTOMATIC ROTATION

| IRQ                                          | 7 IRQ6   | IRQ5       | IRQ4    | IRQ3 | IRQ2     | IRQ1   | IRQ0          |  |  |  |  |

|----------------------------------------------|----------|------------|---------|------|----------|--------|---------------|--|--|--|--|

| 0 1 0 0 0 0 0                                |          |            |         |      |          |        |               |  |  |  |  |

| IRQ                                          | STATL    | JS         |         |      |          |        |               |  |  |  |  |

| IRQ STATUS  Lowest Priority Highest Priority |          |            |         |      |          |        |               |  |  |  |  |

| Lowe                                         | est Prid | ority      |         |      | Hig      | hest F | Priority      |  |  |  |  |

| Lowe<br>4                                    | est Prio | ority<br>2 | 1       | 0    | Hig<br>7 | hest F | Priority<br>5 |  |  |  |  |

| 4                                            |          | 2          | 1<br>JS | 0    | Hig<br>7 |        |               |  |  |  |  |

FIGURE 8. INTERRUPT PRIORITY AFTER AUTOMATIC ROTATION

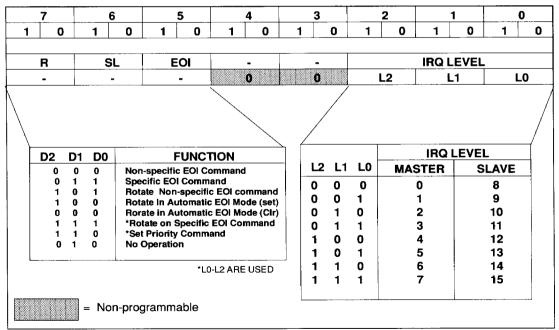

### 3.5.3 Specific Rotation

Specific Rotation fixes the priorities by assigning one interrupt the lowest priority, and thus changing the priorities of the rest. For example, if IRQ4 is programmed to have the lowest priority, then the new order of priority is 5, 6, 7, 0, 1, 2, 3, and 4, with IRQ5 having the highest priority and IRQ4 the lowest priority.

Specific Rotation is programmed with OCW2 in two ways, Rotate on Specific EOI, and Set Priority. Note that priority changes can only be made during an EOI command by using Rotate on Specific EOI.

### 3.6 SPECIAL MASK MODE

Special Mask Mode (SMM) allows the interrupt priority structure to be dynamically changed. In SMM, when a bit is masked in OCW1, interrupts are inhibited at that level; all other levels, lower or higher, that are not masked are enabled. This selectively enables interrupts by changing the IMR. SMM is programmed with OCW3.

### 3.7 READING REGISTER STATUS

The status of the IRR and ISR can be read at Address 020H (master) and 0A0H (slave). Prior to the read status operation, indicate the register to be read with OCW3. The contents of the selected register can be read again, unless Polled Mode is

selected, that is, there is no need to write another OCW3 to read the same register.

The IMR can be read at Addresses 021H and 0A1H.

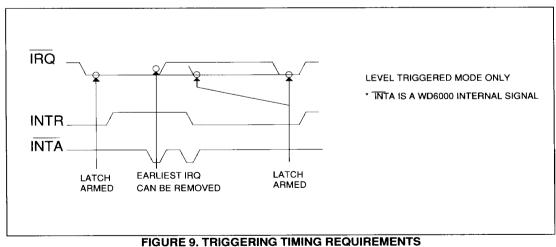

### 3.8 INTERRUPT TRIGGERING

An interrupt request is recognized by a low level on the RQ input. The interrupt request must be removed before the EOI is issued or before the CPU internal interrupt enable has been reenabled. Otherwise, a second interrupt is detected.

The IRQ inputs must remain low until after the falling edge of the first INTA as generated from interrupt acknowledge cycles from the CPU. See Figure 9. If the IRQ goes high before this time, the Interrupt Controller issues an Interrupt Level 7 vector during the second INTA cycle, thus ignoring the false interrupt. This allows false interrupts caused by spurious noise glitches on the interrupt inputs to be detected.

If IRQ7 is needed for another purpose, a false IRQ7 can still be detected by reading the ISR. A normal IRQ7 sets the corresponding ISR bit; a false IRQ7 does not, except when a false IRQ7 occurs during a normal IRQ7. In this case, it is necessary to keep track of IRQ7 occurrences to determine default occurrences that may follow.

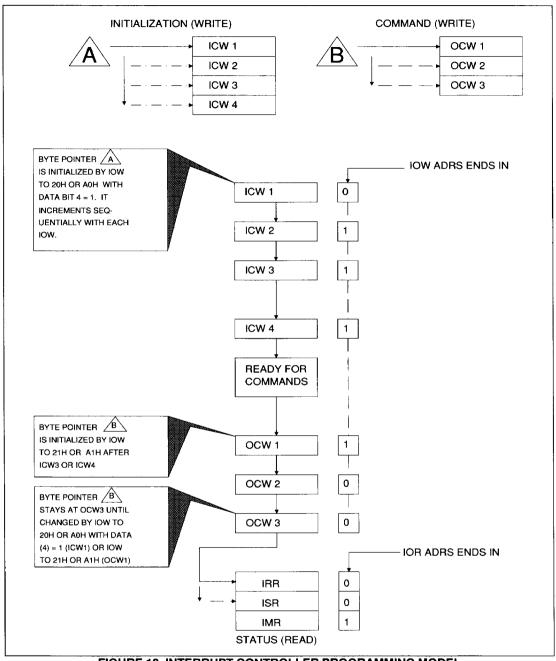

(NOTE: I/O ADDRESS 20/21H APPLIES TO MASTER, A0/A1H APPLIES TO SLAVE)

FIGURE 10. INTERRUPT CONTROLLER PROGRAMMING MODEL

(NOTE: I/O ADDRESS 20/21H APPLIES TO MASTER, A0/A1H APPLIES TO SLAVE)

### 3.9 PROGRAMMING

The Interrupt Controller is initialized by writing a series of Initialization Command Words (ICWs) to each controller, whether master or slave. See Figure 10 for more information. After initialization, the controllers are ready to accept interrupt requests. Operation Control Words (OCWs) can

then be used to change operating modes and command the controllers for various functions. The master and slave can be programmed to work in different modes.

Table 3 indicates each read/write function and its corresponding address for Interrupt Controllers 1 and 2, master and slave respectively.

| INTERRUPT<br>CONTROLLER | ADDRESS      | FUNCTION | READ/WRITE |  |  |

|-------------------------|--------------|----------|------------|--|--|

| 1                       | 020          | ICW1     | Fixed      |  |  |

| 1                       | 021          | ICW2     | Write      |  |  |

| 1                       | 021          | ICW3     | Write      |  |  |

| 1                       | 021          | ICW4     | Write      |  |  |

| 1                       | 021          | OCW1     | Write      |  |  |

| 1                       | 020          | OCW2     | Write      |  |  |

| 1                       | 020          | OCW3     | Write      |  |  |

| 1                       | 020          | IRR      | Read       |  |  |

| 1                       | 020          | ISR      | Read       |  |  |

| 1                       | 021          | IMR      | Read       |  |  |

| 2                       | 0A0          | ICW1     | Write      |  |  |

| 2                       | 0A1          | ICW2     | Write      |  |  |

| 2                       | 0A1          | ICW3     | Write      |  |  |

| 2                       | 0A1          | ICW4     | Write      |  |  |

| 2                       | 0A1          | OCW1     | Write      |  |  |

| 2                       | 0A0          | OCW2     | Write      |  |  |

| 2                       | 0A0          | OCW3     | Write      |  |  |

| 2                       | 0A0          | IRR      | Read       |  |  |

| 2                       | 0 <b>A</b> 0 | ISR      | Read       |  |  |

| 2                       | 0A1          | IMR      | Read       |  |  |

TABLE 3. INTERRUPT CONTROLLER FUNCTION MAP

# 3.9.1 Initialization Command Word 1 (ICW1)

The initialization sequence is started by writing ICW1 to Address 020H or 0A0H. ICW1 has a fixed format, illustrated in Figure 11. Initialization accomplishes the following:

1. The Interrupt Mask Register is cleared.

- 2. Fixed Priority Mode is selected.

- 3. The Slave Mode address is set to 2.

- 4. Special Mask Mode is cleared.

- 5. IRR is set for Status Read.

The next three commands to Addresses 021H or 0A1H load ICW2 through ICW4.

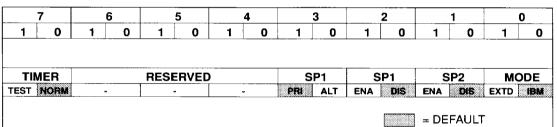

|   | • | 7 |   | 6 |   | 5 |    | 4 |     | 3         |   | 2 |     | 1    | (    | 0 |

|---|---|---|---|---|---|---|----|---|-----|-----------|---|---|-----|------|------|---|

| 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1_ | 0 | 1   | 0         | 1 | 0 | 1   | 0    | 1    | 0 |

|   |   |   |   |   |   |   |    |   |     |           |   |   |     |      |      |   |

|   |   | - |   | • |   | - |    | - | MOE | TRIG<br>E |   | - | MOD | CADE | ICW4 |   |

|   |   | 0 |   | 0 |   | 0 |    | 1 |     | 1         |   | 0 |     | 0    |      | 1 |

FIGURE 11, ICW1

=

= Nonprogrammable

# 3.9.2 Initializaation Command Word 2 (ICW2)

Bits 3-7 are the five most significant bits of the interrupt vector (T3-T7); they are programmable by the CPU. Bits 0-2 are generated by the Priority

Resolver during the INTA cycle, according to the interrupt level. Refer to Table 2. Figure 12 shows the format for ICW2.

| 7      | 6      |     | 5   |              | 4     |       | 3     |      | 2 1   |     |     |      | 0  |

|--------|--------|-----|-----|--------------|-------|-------|-------|------|-------|-----|-----|------|----|

| 1 0    | 1 0    | 1   | 0   | 1            | 0     | 1_    | 0     | 1    | 1 0 1 |     |     | 1    | 0  |

|        |        |     |     |              |       |       |       |      |       |     |     |      |    |

|        |        |     | INT | <b>TERRU</b> | PT LE | VEL H | IAS S | LAVE |       |     |     |      |    |

| YES NO | YES NO | YES | No  | YES          | NO    | YES   | NO    | YES  | NO    | YES | NO  | YES  | NO |

| 0      | 0      |     | 0   |              | 0     |       | 0     |      | 0     |     | 1   | 1    | 0  |

|        |        |     |     |              |       |       |       |      |       |     |     |      |    |

|        |        |     |     |              |       |       |       |      |       | LEV | ÆL. |      |    |

|        |        |     |     |              |       | D2    | D1 [  | 00   | MAST  | ER  | SI  | _AVE |    |

|        |        |     |     |              |       | 0     | 0     | 0    | 0     |     |     | 8    |    |

|        |        |     |     |              |       | 0     | 0     | 1    | 1     |     |     | 9    |    |

|        |        |     |     |              |       | 0     | -     | 0    | 2     |     |     | 10   |    |

|        |        |     |     |              |       | 0     | 1     | 1    | 3     |     |     | 11   |    |

|        |        |     |     |              |       | 1     | _     | 0    | 4     |     |     | 12   | 1  |

|        |        |     |     |              | i     | 1     | 0     | 1    | 5     |     |     | 13   |    |

|        |        |     |     |              |       | 1     | 1     | 0    | 6     |     |     | 14   |    |

|        |        |     |     |              |       | 1     | 1     | 1    | 7     |     |     | 15   |    |

|        |        |     |     |              |       |       |       |      |       |     |     |      |    |

FIGURE 12. ICW2 FORMATS

# 3.9.3 Initialization Command Word 3 (ICW3)

ICW3 initializes the master and slave. For the master, ICW3 sets a 1 for each IRQ input used to cascade a slave. For the slave, bits 0-2 of ICW3 provide the Slave Mode address. Figure 13

shows the format for ICW3 for master and slave. The formats are fixed and must be written as shown in order to function.

|     | 7  |     | 6  |     | 5   |      | 4     |       | 3     |     | 2  | <u> </u> | 1     |       | 0  |

|-----|----|-----|----|-----|-----|------|-------|-------|-------|-----|----|----------|-------|-------|----|

| 1   | 0  | _1  | 0  | 1   | 0   | 1    | 0     | 1     | 0     | 1   | 0  | 1        | 0     | 1     | 0  |

|     |    |     |    |     |     |      |       |       |       |     |    |          |       |       |    |

|     |    |     |    |     | INT | ERRU | PT LE | VEL H | AS SL | AVE |    |          |       |       |    |

| YES | NO | YES | NO | YES | No  | YES  | NO    | YES   | NO    | YES | NO | YES      | NO    | YES   | NO |

|     | 0  | 1   | 0  |     | 0   |      | 0     | l     | 0     |     | 0  |          | 1     |       | 0  |

|     |    |     |    |     |     |      |       |       |       |     |    |          |       |       |    |

|     |    |     |    |     |     |      | T     | D2    | D1    | DO  |    | SLA      | VE ID | ) = 2 | 7  |

|     |    |     |    |     |     |      |       | 0     | 0     | 0   |    |          | 0     |       |    |

|     |    |     |    |     |     |      |       | 0     | 0     | 1   |    |          | 1     |       | -  |

|     |    |     |    |     |     |      |       | 0     | 1     | 0   |    |          | 2     |       |    |

|     |    |     |    |     |     |      |       | 0     | 1     | 1   |    |          | 3     |       |    |

|     |    |     |    |     |     |      | İ     | 1     | 0     | 0   |    |          | 4     |       |    |

|     |    |     |    |     |     |      | -     | 1     | 0     | 1   |    |          | 5     |       |    |

|     |    |     |    |     |     |      |       | 1     | 1     | 0   |    |          | 6     |       |    |

|     |    |     |    |     |     |      |       | 1     | 1     | 1   |    |          | 7     |       |    |

|     |    |     |    |     |     |      | L     |       |       |     |    |          |       |       |    |

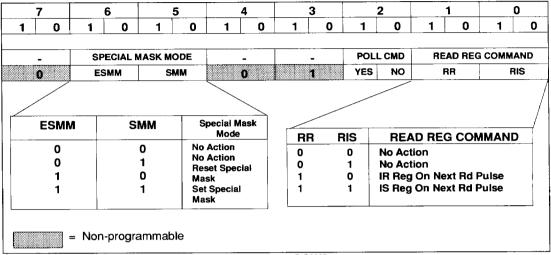

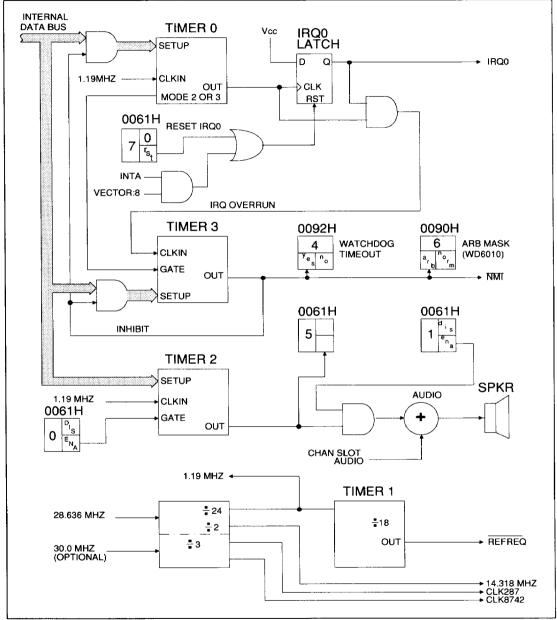

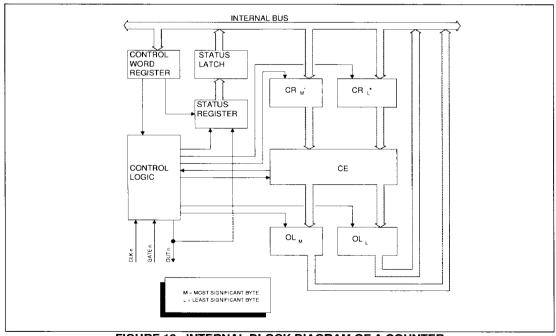

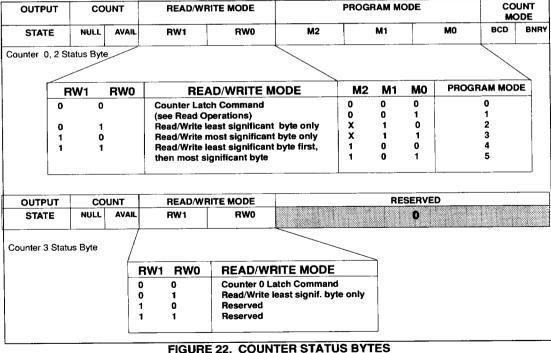

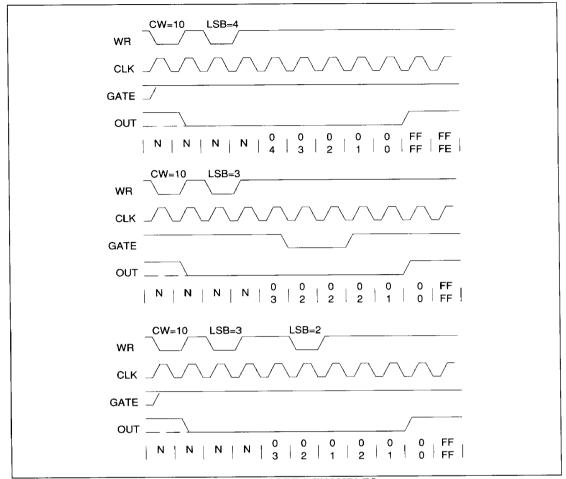

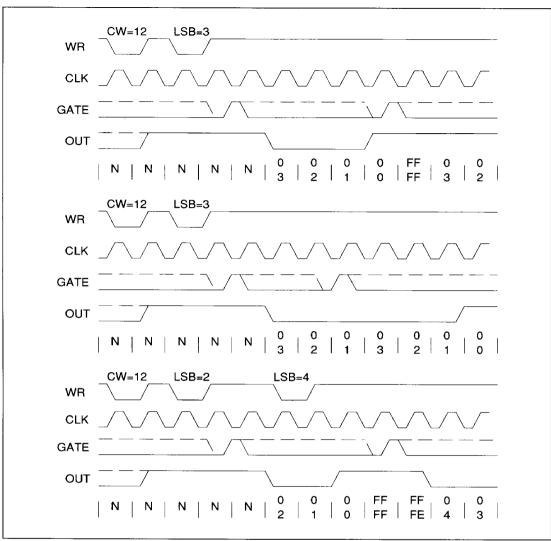

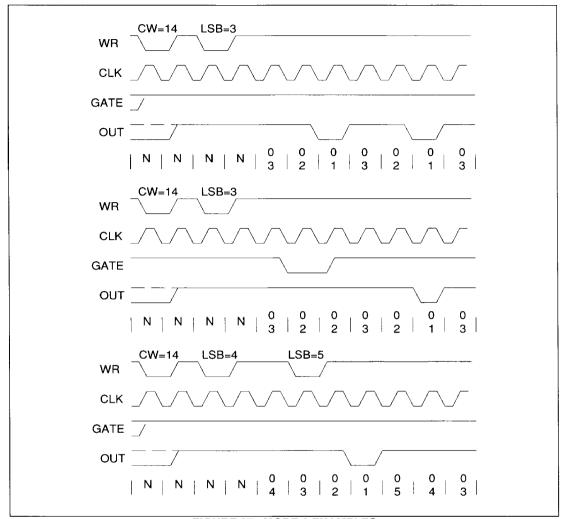

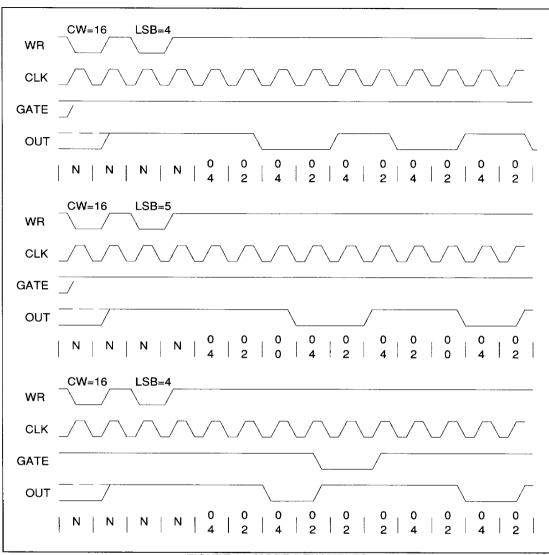

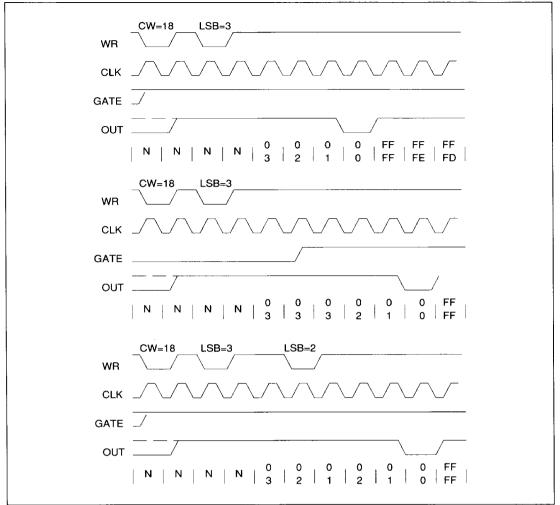

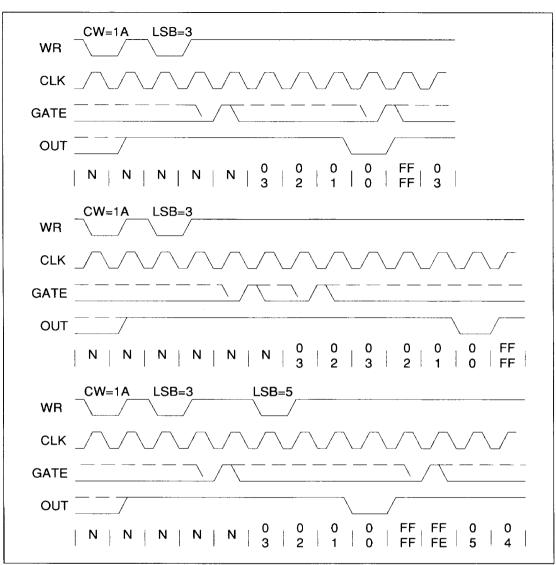

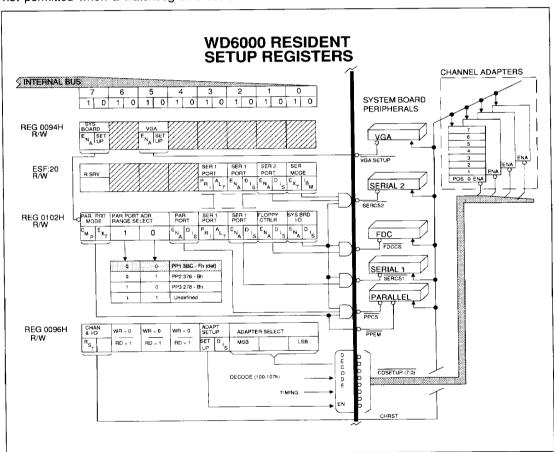

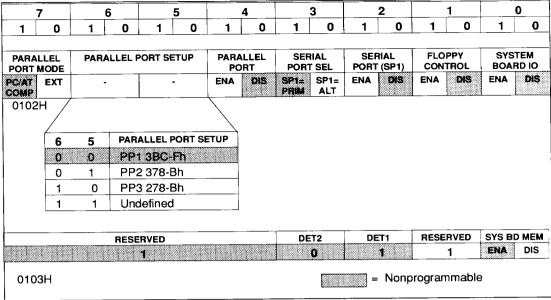

FIGURE 13. ICW3 FORMATS