# 1. Introduction

The WL102B is a highly integrated low power CMOS Wireless Data Controller, designed to dramatically reduce the cost of radio data applications. It forms the DE6038 chip set together with the WL600C receiver chip and WL800 transmitter chip to offer a complete solution for a frequency-hopping spread spectrum radio in the 2.4 to 2.5 GHz ISM band. It is also interfaces with the GPS DE6003 radio transceiver.

Its flexible design means that it can also be used in a wide range of other applications using a range of microprocessors, protocols and additional memory options, as well as radios at other frequencies. It is designed for low power and minimum cost systems, it is particularly suited for hand-held applications.

# 1.1 Features

- Complete Low Power CMOS Single-Chip Radio Transceiver Controller

- Embedded 8051 Processor for Control of Media Access Control (MAC) Protocol

- On-chip Dual Port 6.4kbyte Network Data Buffer

- On-chip 4kbyte System RAM

- Provision for External Processor, 64kbyte Data Buffer and System RAM

- Capability for In-system Re-programming of External Flash Code Memory

- 8-bit Host Processor Interface to Buffer, with Support for PCMCIA Interface

- Radio Transceiver Interface Provided by Generic Communications Control Block (CCB)

- Up to 1 Mbit/s with 2-level, or 2 Mbit/s with 4-level GFSK Operation

- Block Power-down Facility to Reduce Power

- Power Efficient Dedicated DMA Transfer Mode between Buffer RAM and CCB

- Available in 100 and 144 pin Thin Quad Flatpack Packages

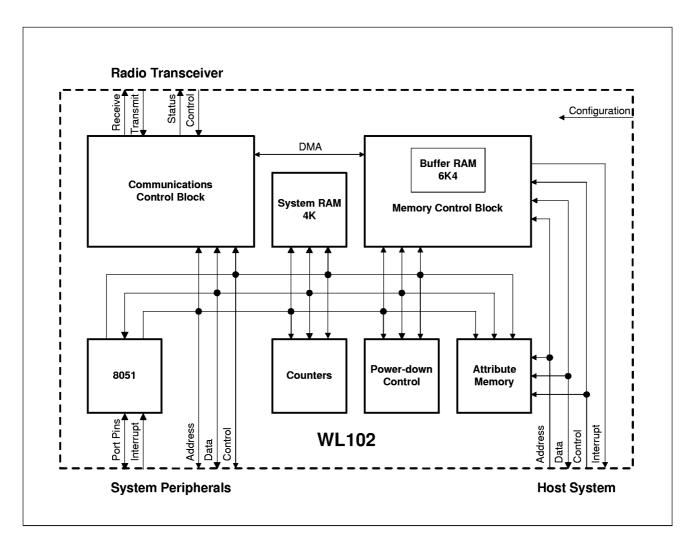

Figure 1. WL102 Block Diagram

## 1.2 WL102 System Overview

The WL102 is a highly integrated digital wireless transceiver controller suitable for controlling multiple channel radios with data rates up to 1Mbit/s 2-level data or 2Mbits/s 4-level data. It has been designed to interface easily with the WL600 and WL800 radio transceiver chips.

The use of low power synchronous on-chip RAM and selective power down of system blocks makes the WL102 ideally suited to power sensitive applications. Also, the WL102 can be operated from 3V or 5V supply rails with level translation between the Host and MAC system built in to the Host interface. A minimum configuration of the WL102 with a 64Kbtye external ROM for code storage makes it ideal for small footprint applications, and the option of 100 pin or 144 pin TQFP 1mm packages make it suitable for PC-Card applications.

It is envisaged that the WL102 hardware will allow the development of a wireless network to the Media Access layer of the IEEE model for networking, with the addition of an LLC layer providing the equivalent of the Data Link layer of the ISO network model. In such a system the Host interface buffer RAM would provide the boundary between the LLC layer running on the Host and the MAC layer running on the internal WL102 8051 processor, or an optional external MAC system processor.

Figure 1 shows the internal architecture of the WL102.

The WL102 provides an interface between a Host system and the radio transceiver, controlled by the MAC system processor.

The host interface, such as to a PC or PDA, can be either a PC-Card interface or an 8 bit microprocessor bus. The Memory Control Block (MCB) provides a buffer and interrupt signalling mechanisms between the Host and Mac system processors. The Attribute Memory provides PC-Card Card Information Structure (CIS) and Configuration Option Register (COR).

The Communications Control Block (CCB) interfaces with either the DE6038 (WL600/WL800) or the DE6003 radio transceivers. The CCB performs transmit and receive operations directly to the MCB buffer RAM, using a dedicated DMA bus, so minimising the load on the MAC system processor.

The MAC system processor is then only required to provide the timing and control functions of Media Access Control. A minimum controller system configuration would be the WL102 plus an external code memory device.

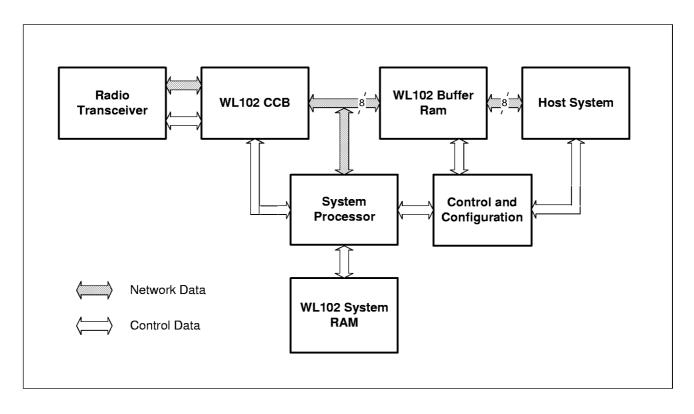

Figure 2 shows the control and network packet data flows through the WL102. The network data packet transfer between the Radio Transceiver and the Host system is directly between the CCB and the MCB Host Buffer RAM. The system processor provides the management control; it has direct access to the network management packets.

Figure 2. Data Flow in a WL102 Based System

# 1.3 WL102 Hardware Blocks

#### 1.3.1 System Processor

The WL102 contains an embedded processor; identical in operation to an industry-standard 8051microcontroller, with the exception that the internal data memory is increased from 128 to 256 bytes. System busses and strobes allow the 8051 to access the full 64 kbytes of external code memory.

Internal connections exist to the processor's two interrupt inputs, and to the two timer inputs. Two I/O port pins are internally connected to blocks within the WL102, whilst four of the remaining I/O port pins are brought out to external pins, including the serial receive and transmit port pins.

Internal address decoding provides access to the other blocks of the device, with 36 kbytes of the processor's 64 kbytes address range being un-assigned and available for the addition of external peripheral devices.

The 8051 demultiplexed address and data bus are available externally to allow for the addition of extra memory or other peripheral devices.

The 8051 is clocked at the internal system clock frequency of 10MHz.

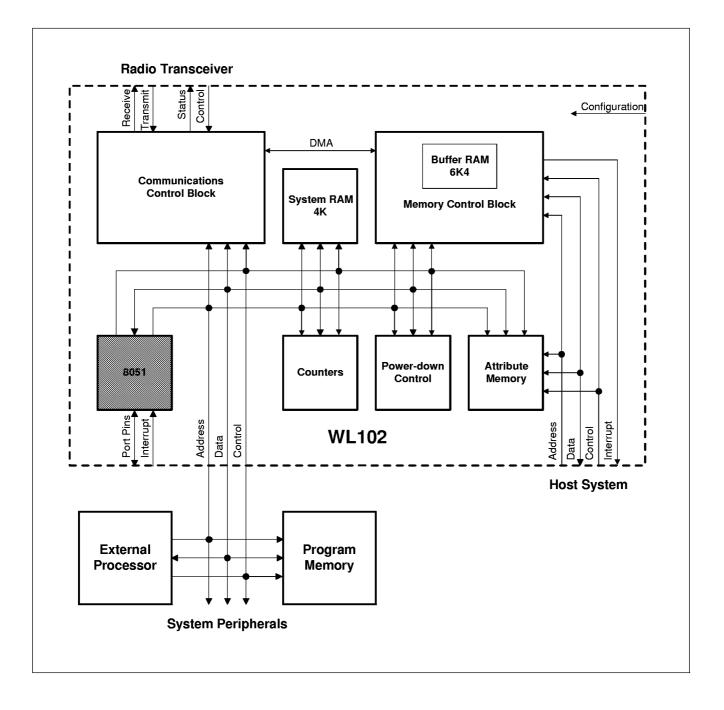

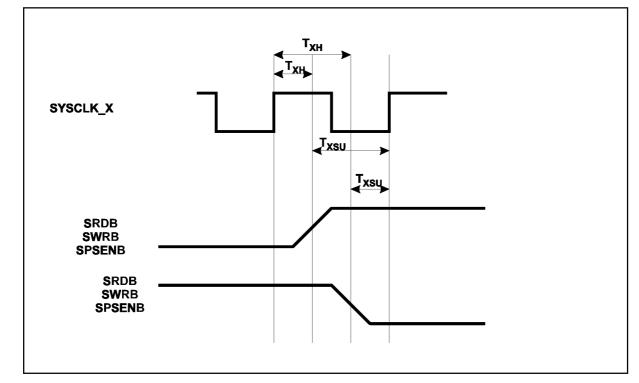

If additional processing power is required for a particular application, the WL102 may also be used with an external processor instead of the internal 8051 as shown in Figure 3. This external processor also accesses the WL102 blocks via the internal address decode. Interrupt and Counter outputs are brought to external pins, and two control input signals must also be provided to the WL102. The internal 8051 is disabled to save power.

## 1.3.2 Data RAM

The WL102 contains 4 kbytes of static RAM which the processor may use for variable storage etc. If additional storage space is required, an external static RAM may also be used, and mapped to an unused area of the WL102 memory map.

#### 1.3.3 Memory Control Block

The Memory Control Block (MCB) allows access to the dual port buffer used to communicate between the Host and WL102 System processes. The control logic of the buffer RAM allows the Host System to asynchronously read or write data at the same time as the WL102 MAC system. To help arbitrate the access to this buffer space, a hardware semaphore system is also included.

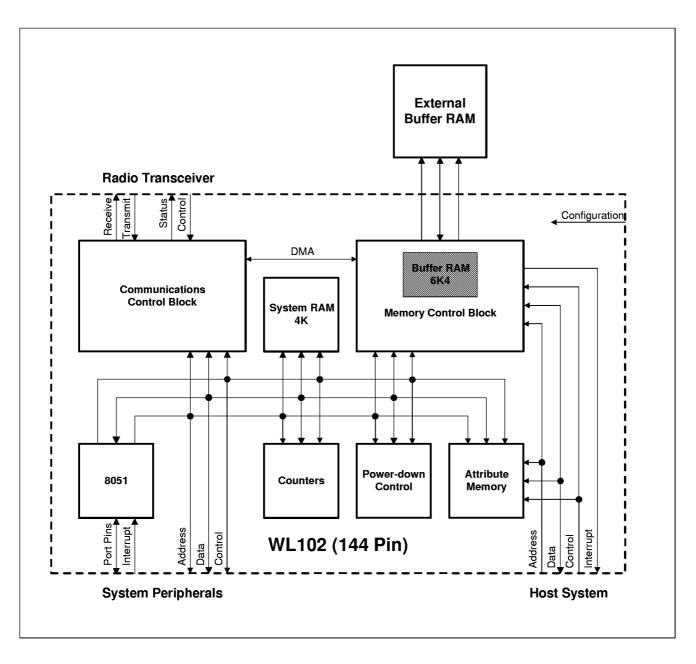

The WL102 contains 6784 bytes of low power buffer RAM on chip. The 144-pin package option also allows for an external (single port) SRAM to be used to increase the buffer RAM space, as shown inFigure 4, up to 64KBytes. The MCB provides access to the Buffer RAM, which is accessible by both the Host and the MAC systems simultaneously, and also to a control register which allows the Host to reset or interrupt the MAC processor and performs some other control functions on the WL102.

Packets of data are typically buffered in the buffer RAM before being transmitted or transferred from the MAC system to the host.

The MCB has been designed to be flexible enough to allow its use from small microprocessor systems to PC-Card slots. In a minimum configuration it uses only 4 address locations and standard microprocessor-type read or write cycles.

The 8-bit interface is microprocessor and PCMCIA-compatible. The MCB may be used by any microprocessor-type interface which can supply two bits of address, a chip enable signal, read/write strobes and 8 bits of data, subject to timing requirements of the WL102. The interface also provides an interrupt signalling mechanism between the Host and MAC system as well as some other control functions, such as a hardware semaphore and reset circuitry.

Figure 4. WL102 Using External Buffer RAM

## 1.3.4 Attribute Memory

The attribute memory is PCMCIA-compatible providing a dedicated 255 bytes RAM for Card Information Structure(CIS) and Configuration Option Register(COR) used for the configuration and control of a PC-Card.

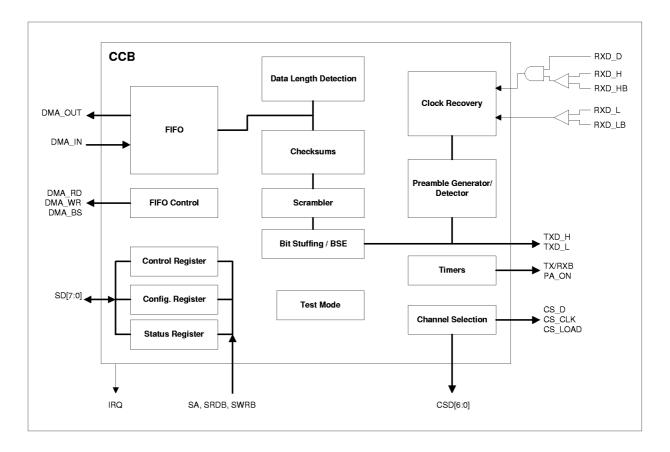

# 1.3.5 Communications Control Block

This block of the WL102 performs many of the functions required for transmission and reception of data packets, and interfaces directly to the radio transceiver. For power sensitive applications the configuration registers can have their clocks switched off once the initial configuration is complete and for protocols which allow the transceiver to sleep for periods of time, the clocks to the entire block can be disabled via the Power Control register.

The CCB handles all the control signals for the radio and can be configured for the timings required by the transceiver being used. The CCB can directly access data stored in the buffer RAM, via a DMA bus separate to the processor bus. Once configured, the CCB will fully handle a transmission or reception, including CRC checking, address matching, optional data scrambling and Bias suppression encoding, and transfer of the data to/from the buffer RAM. For shorter network management packets the MAC system processor can directly read/write up to 64 bytes of data from/to the CCB FIFO.

The CCB generates maskable interrupts to the MAC system processor at defined points in the receive/transmit process to allow the processor to perform any additional processing required to successfully complete the receive or transmit sequence.

The high level of hardware integration dramatically reduces the load on the WL102 system processor and provides a number of configuration options to suit different wireless protocols.

The features of the CCB include:

Transmission and reception of 2-level and 4-level GFSK bit streams at 625Kbps, 1Mbps and 2Mbps

Configurable Preamble/Frame word generation and recognition Checksum generation and validation (CRC-16 and CRC-32)

Optional data coding schemes: bit-stuffing, scrambling and bias suppression encoding (as per draft IEEE 802.11) Dedicated data path for DMA transfer to and from buffer RAM

Address matching on received data packets

Analysis of received signal for performing clear channel assessment, including 16-bit countdown timer

8 (maskable) interrupt sources to optimise operation of the system software

Automatic synthesiser channel loading for Rx/Tx when using WL600/WL800.

#### 1.3.6 Counters

The two 16-bit counters are provided which are configured by setting a reload value. When enabled, the counters decrement continuously at 10MHz, generating a terminal count signal to the processor and automatically reloading the reload value when the count reaches zero.

The terminal count outputs are internally connected to the 8051 Timer inputs when using the internal 8051, and to external pins when using an external processor.

#### 1.3.7 Power Control

A power-down function is provided under the control of the WL102 system. Power-down enable signals are provided to each major block; the clocks of the individual blocks being disabled when the appropriate power-down bit is set. In addition, the internal processor's PCON register will disable the 8051 core in the usual manner.

#### 1.3.8 System Supply Voltages

The WL102 has two separate digital supply rails, allowing for use in mixed 3V/5V systems. The host interface has its own independent supply, whilst a second supply powers the core of the WL102 and its interface to the memory and radio transceiver subsystems. Both power supplies may be operated at either 3 or 5 volts (nominal); with the restriction that the host interface supply voltage must be greater than or equal to the voltage powering the WL102 core and radio transceiver.

### 1.4 Manufacturing Enhancements

#### 1.4.1 Radio Test Mode

The WL102 radio test mode is a mode of operation which allows an attached radio transceiver to be tested more easily in a complete assembled unit. In this mode the usual functions of the WL102 are suspended and the control and status signals of the CCB radio interface are connected to the pins of the Host interface. This allows the operation of the radio to be directly controlled by a test system connected to the Host interface, with the WL102 providing the status signals back from the radio interface. The comparators on the receive data stream are still used and so the test system is provided with the digital version of this radio output. In addition the operation of the CCB preamble and frame word recognition can be tested as well as the clock recovery and recovered data stream.

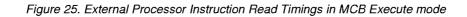

#### 1.4.2 MCB Execute Mode

This mode of operation is used to allow programming of the external code memory if a re-programmable device is used, via special software run on the Host. Using this mode, the WL102's code memory may be completely reprogrammed regardless of its current state i.e. no 'boot-block' code is required in the WL102 system. This allows complete radio modules to be manufactured without the need for pre-programming the code memory. At final test the MAC software image can be downloaded or test software can be downloaded and used prior to the final software.

This facility also allows the completed radio module to be upgraded in the field or for diagnostic software to be downloaded as necessary.

# 2. Pin Descriptions

# 2.1 Host Interface Pins

All logic high and low levels correspond to HVdd and Gnd respectively.

| Pin                                              | Туре                         | Description                                                                                                                                                                         |

|--------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                  |                              |                                                                                                                                                                                     |

| <b>HA7 - 0</b><br>Host Address Bus               | Input<br>(Pull down)         | HA0 through HA7 are the host address bus input lines.                                                                                                                               |

| <b>HD7 - 0</b><br>Host Data Bus                  | Input /Output<br>(Pull down) | HD0 through HD7 are the bi-directional host data bus.                                                                                                                               |

| HREGB<br>PCMCIA Attribute Memory / I/O Select    | Input<br>(Pull Up)           | HREGB is an active-low input which selects attribute<br>memory and I/O space. The WL102 does not<br>respond to common memory access (when HREGB<br>is high.)                        |

| HRDB<br>I/O Read Strobe                          | Input<br>(Pull Up)           | The HRDB input is made active to read data from the chip's I/O space. The HREGB and HCEB inputs must also be active for I/O transfer to take place.                                 |

| HWRB<br>I/O Write Strobe                         | Input<br>(Pull Up)           | The HWRB input is made active to write data to the chip's I/O space. The HREGB and HCEB inputs must also be active for the I/O transfer to take place.                              |

| HOEB<br>PCMCIA Attribute Memory Read Strobe      | Input<br>(Pull Up)           | HOEB is an active-low output enable input. HOEB is used to gate attribute memory read data from the WL102 onto the HD bus.                                                          |

| HWEB<br>PCMCIA Attribute Memory Write Strobe     | Input<br>(Pull Up)           | HWEB is an active-low write enable input. HWEB is used to strobe attribute memory write data into the WL102 from the HD bus.                                                        |

| HCEB<br>Chip Enable                              | Input<br>(Pull Up)           | The HCEB line is an active-low chip enable.                                                                                                                                         |

| HRESET<br>System Reset                           | Input<br>(Pull Up)           | HRESET is an active-high input that resets the entire WL102.                                                                                                                        |

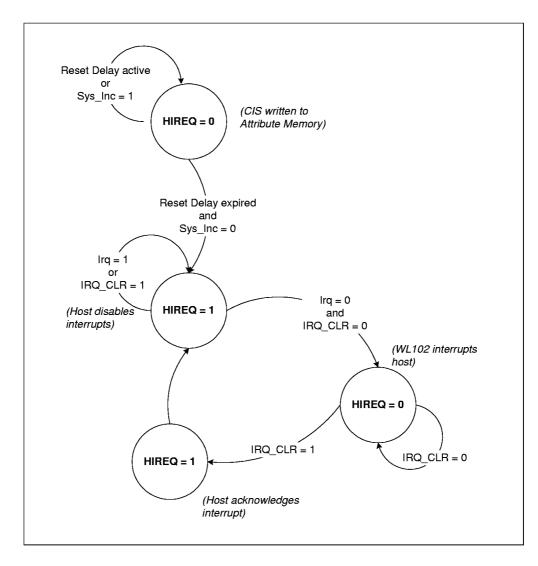

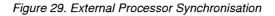

| HRDY (HIREQ)<br>PCMCIA Ready / Interrupt Request | Output                       | HRDY (PCMCIA Memory Mode) is an active-high<br>output. On reset the WL102 sets this output low<br>until the system microprocessor sets it high after<br>configuring the CIS memory. |

|                                                  |                              | HIREQ (PCMCIA I/O Mode) is an active-low output.<br>HIREQ is used to indicate to the host that software<br>service is required.                                                     |

|                                                  |                              | The control of this pin is described in Section 6                                                                                                                                   |

| Pin                           | Туре   | Description                                                                                                                                                                                                                                                                         |

|-------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HWAITB<br>Extend Bus Cycle    | Output | The HWAITB output is asserted by the chip to delay completion of the access currently in progress.                                                                                                                                                                                  |

| HVdd<br>Host Interface Supply |        | HVdd is the Host Interface power supply pin. The voltage on this pin must be greater than or equal to that on SVdd. If a 5 volt supply is used, the LOWVDD bit of the host MCB control register should be set to '0', or the configuration Option register bit should be set to '1' |

# 2.2 System Interface Pins

All logic high and low levels correspond to SVdd and Gnd respectively, unless otherwise stated.

| Pin                                                                            | Туре                              | Description                                                  |

|--------------------------------------------------------------------------------|-----------------------------------|--------------------------------------------------------------|

| <b>SA15 - 0</b><br><i>Internal Processor Mode</i><br>System Memory Address Bus | Output                            | SA15 through SA0 are the demultiplexed system address lines. |

| External Processor Mode<br>System Address Bus                                  | Input                             | SA15 through SA0 are the system address lines.               |

| <b>SD7 - 0</b><br>Internal/ External Processor Mode<br>System Memory Data Bus  | Input/ Output<br>(Pull Down)      | SD7 through SD0 are the bi-directional system data lines     |

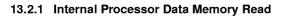

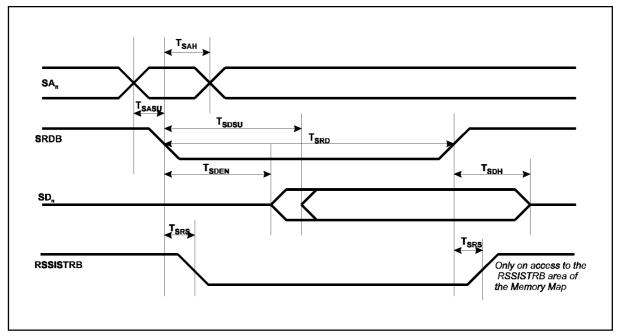

| SRDB<br>Internal Processor Mode<br>System Data Memory Read Strobe              | Open Drain<br>Output<br>(Pull Up) | SRDB is an active-low data memory read strobe.               |

| External Processor Mode<br>System Read Strobe                                  | Input                             | SRDB is an active-low data output enable input.              |

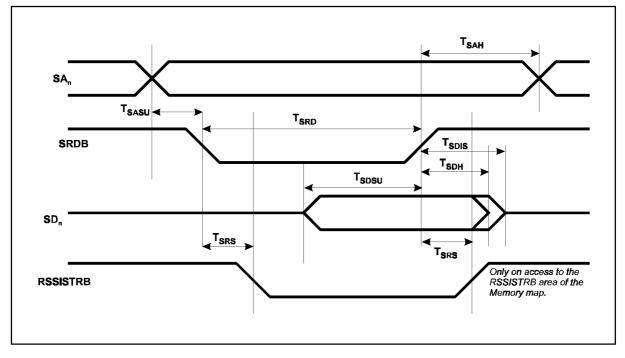

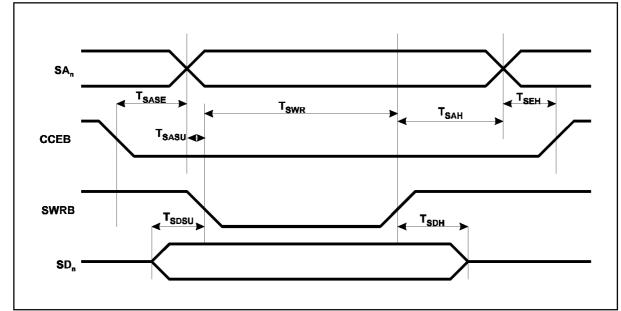

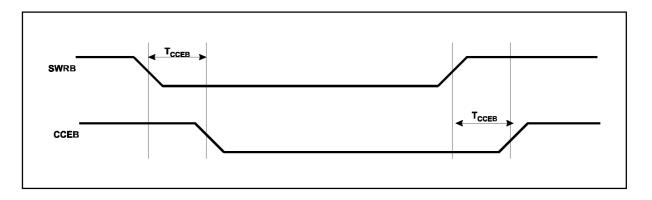

| SWRB<br>Internal Processor Mode<br>System Data Memory Write Strobe             | Output<br>(Pull Up)               | SWRB is an active-low data memory write strobe.              |

| External Processor Mode<br>System Write Strobe                                 | Input                             | SWRB is an active-low write strobe.                          |

| Pin                                                                       | Туре                              | Description                                                                                                                                                  |

|---------------------------------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCEB                                                                      |                                   |                                                                                                                                                              |

| Internal / External Processor Mode<br>Program Memory Enable               | Output                            | CCEB is an active-low program memory chip enable.                                                                                                            |

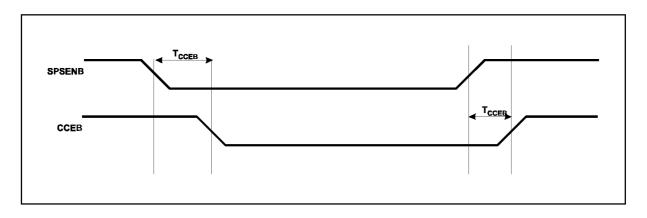

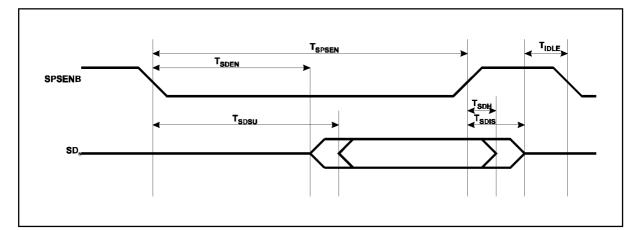

| SPSENB<br>Internal Processor Mode<br>System Program Memory Read Strobe    | Open drain<br>Output<br>(Pull Up) | SPSENB is an active-low program memory read strobe.                                                                                                          |

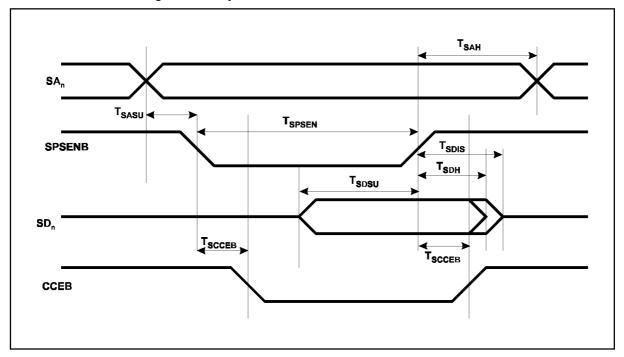

| <i>External Processor Mode</i><br>System Program Memory Read Strobe       | Input<br>(Pull Up)                | SPSENB is an active-low program memory read<br>strobe. This input is used to generate CCEB, and is<br>also used to enable the MCB Execute mode<br>operation. |

| SWAKEUP / EPTCNT2<br>Internal Processor Mode<br>Wakeup Interrupt          | Input                             | SWAKEUP is internally inverted and ORed with the CCB interrupt to drive the INT0 input of the internal 8051.                                                 |

| External Processor Mode<br>Counter2 Terminal Count                        | Output                            | EPTCNT2 is the active-high terminal count output of Counter2.                                                                                                |

| <b>P1[3] / EPCINTR</b><br><i>Internal Processor Mode</i><br>8051 Port 1.3 | Open Drain<br>I/O                 | P1[3] is the Port1 bit 3 open drain I/O of the internal 8051.                                                                                                |

| External Processor Mode<br>CCB Interrupt                                  | Open Drain<br>Output              | EPCINTR is the active-low CCB interrupt output.                                                                                                              |

| P1[5] / EPTCNT1<br>Internal Processor Mode<br>8051 Port 1.5               | Open Drain<br>I/O                 | P1[5] is the Port1 bit 5 open drain I/O of the internal 8051.                                                                                                |

| External Processor Mode<br>Counter1 Terminal Count                        | Open Drain<br>Output              | EPTCNT1 is the active-high terminal count output of Counter1.                                                                                                |

| <b>P3[1]</b> / <b>EPMINTR</b><br>Internal Processor Mode<br>8051 Port 3.1 | Open Drain<br>I/O (Pull Up)       | P3[1] is the Port3 bit 1 open drain I/O of the internal 8051.                                                                                                |

| <i>External Processor Mode</i><br>MCB Interrupt                           | Open Drain<br>Output<br>(Pull Up) | EPMINTR is the active-low MCB interrupt output                                                                                                               |

| Pin                                                                                          | Туре                  | Description                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSSISTRB                                                                                     |                       |                                                                                                                                                                                                                                                                                                                                  |

| Internal / External Processor Mode<br>External ADC Strobe for RSSI                           | Output                | RSSISTRB is an active-low read strobe generated by a read from the RSSI Strobe memory area.                                                                                                                                                                                                                                      |

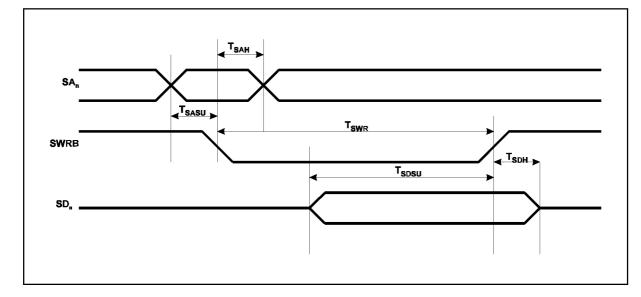

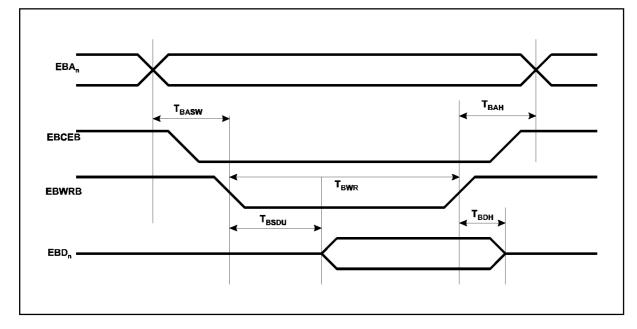

| SYSCLK_X<br>External Processor Mode<br>10MHz Reference Clock                                 | Output                | SYSCLK_X is the 10MHz system clock output.<br>This clock is generated from the SYSCLK_D<br>(10MHz) or SYSCLK (20MHz) input. In External<br>processor mode SWRB, SRDB, SPSENB must be<br>synchronised to this clock (see timing diagrams.)                                                                                        |

| Internal Processor Mode                                                                      |                       | Disabled                                                                                                                                                                                                                                                                                                                         |

| <b>P3[0] EPSYSINC</b><br>Internal Processor Mode<br>8051 Port 3.0<br>External Processor Mode | Input                 | P3[0] is the Port 3 bit 0 input of the internal 8051                                                                                                                                                                                                                                                                             |

| MCB System Increment                                                                         | Input                 | EPSYSINC is an active-high input which enables<br>auto-increment for the system MCB address counter.<br>In addition it controls the HRDY output as detailed in<br>Section 6                                                                                                                                                      |

| <b>EPRSTB</b><br><i>External Processor Mode Only</i><br>Processor Reset                      | Output                | EPRSTB is an active-low reset output, generated<br>from the internal reset logic. Following a host reset it<br>is guaranteed to be 64 clocks long.<br>This pin is also controlled by the Host MCB control<br>register bit 0, allowing the host to reset the system<br>microprocessor independently of the rest of WL102<br>chip. |

| <b>EPRDYB</b><br>External Processor Mode Only<br>Control of HRDY(HIREQ)                      | Input                 | EPRDYB is used by an external processor to control<br>the HRDY (HIREQ) output. During external<br>processor reset its function is disabled, after which<br>EPRDYB controls the HIREQ signal as detailed in<br>Section 6.                                                                                                         |

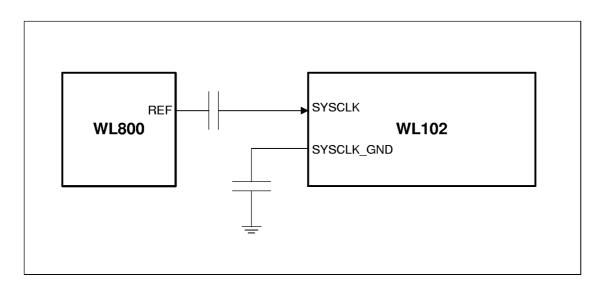

| SYSCLK<br>20MHz System Clock                                                                 | Analogue<br>Input     | SYSCLK is the 20MHz single-ended system clock input. If this input is used SYSCLK_D must be tied to Gnd.                                                                                                                                                                                                                         |

| SYSCLK_GND<br>20MHz System Clock Ground                                                      | Analogue<br>Input     | SYSCLK_GND is the 20MHz system clock ground                                                                                                                                                                                                                                                                                      |

| SYSCLK_D<br>10MHz System Clock                                                               | Input                 | SYSCLK_D is the 10MHz digital system clock input.<br>If this input is used SYSCLK pin must be tied to Gnd<br>and SYSCLK_GND must be tied to SVdd.                                                                                                                                                                                |

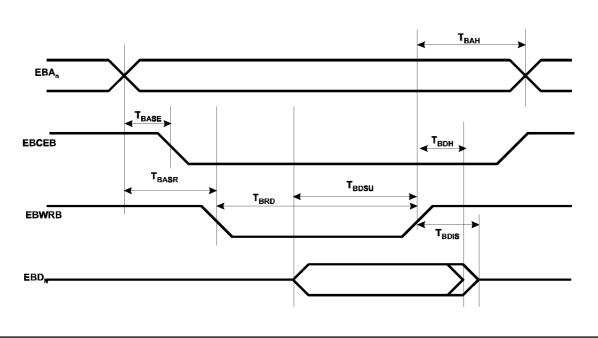

| <b>EBA7 - 0</b><br>External Buffer RAM Address Bus                                           | Output<br>(Pull down) | EBA0 through EBA7 are the external buffer RAM<br>address outputs. These pins are only available on<br>the 144-pin package                                                                                                                                                                                                        |

| Pin                                             | Туре                         | Description                                                                                                                                                                                       |

|-------------------------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EBD7 - 0                                        |                              |                                                                                                                                                                                                   |

| External Buffer RAM Data Bus                    | Input /Output<br>(Pull Down) | EBD0 through EBD7 are the bi-directional external buffer RAM data bus. These pins are only available on the 144-pin package.                                                                      |

| EBRDB<br>External Buffer RAM Read Strobe        | Output                       | EBRDB is an active low read strobe for the external buffer RAM. This pin is only available on the 144 pin package.                                                                                |

| EBWRB<br>External Buffer RAM Write Strobe       | Output                       | EBWRB is an active low write strobe for the external buffer RAM. This pin is only available on the 144 pin package.                                                                               |

| <b>EBCEB</b><br>External Buffer RAM Chip Enable | Output                       | EBCEB is an active low chip enable signal for the external buffer RAM. This pin is only available on the 144 pin package.                                                                         |

| ENIBRAMB<br>Enable Internal Buffer RAM          | Input<br>(Pull Down)         | ENIBRAMB is an active-low input which enables the internal buffer RAM. This pin must be connected to SVdd if an external buffer RAM is used.                                                      |

| <b>ENI8051B</b><br>Enable Internal 8051         | Input                        | ENI8051B is an active-low input which enables the internal 8051 processor. This pin must be connected to the Host Interface supply HVdd or Gnd.                                                   |

| THREEV<br>System 3 Volt Supply Mode             | Input                        | The THREEV input must be set according to the SVdd voltage;<br>'1' = 3 volt operation, '0' = 5 volt operation.                                                                                    |

| <b>TEST1-0</b><br>Enable Test Mode              | Input                        | Test0 and Test1 are used to enable the WL102 test<br>modes, and must be set to '0' for normal operation.<br>These pins must be connected to the Host Interface<br>supply HVdd or Gnd.             |

| SVdd<br>System Interface Supply                 |                              | SVdd is the System power supply pin. The THREEV<br>pin must be connected according to the voltage on<br>this pin. When using the WL102 with the DE6003<br>radio, SVdd (and HVdd) must be 5 volts. |

| <b>Gnd</b><br>Ground                            |                              |                                                                                                                                                                                                   |

# 2.3 Radio Transceiver Interface Pins

All logic high and low levels correspond to SVdd and Gnd respectively.

| Pin                                                                                                                  | Function          | Description                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| <b>RXD_L &amp; RXD_LB</b><br><i>4-Level Modulation Mode</i><br>LSB of Receive Data<br><i>2-Level Modulation Mode</i> | Analogue<br>Input | The Least Significant Bit of the decoded symbol from<br>the demodulated signal.<br>These pins are un-used and must be tied to opposite |

| Pin                                                                                              | Function          | Description                                                                                                                                 |

|--------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                  |                   | known states.                                                                                                                               |

| <b>RXD_H &amp; RXd_HB</b><br><i>4-Level Modulation Mode</i><br>MSB of Receive Data               | Analogue<br>Input | The Most Significant Bit of the decoded symbol from the demodulated signal.                                                                 |

| <i>2-Level Modulation Mode</i><br>Serial Receive Data                                            | Analogue<br>Input | Receive Data from the demodulated signal.<br>Note: If this differential input is used the RXD_D<br>input must be tied to SVdd.              |

| <b>RXD_D</b><br>2-Level Mode Only<br>Serial Receive Data                                         | Input             | Receive Data input.<br>Note: If this input is used the RXD_L and RXD_H<br>must be tied to SVdd and RXD_HB and RXD_LB<br>must be tied to Gnd |

| <b>TXD_L</b><br>4-Level Modulation Mode Only<br>LSB of Transmit Data                             | Output            | The Least Significant Bit of the Transmit data.                                                                                             |

| 2-Level Modulation Mode.<br>Not Used.                                                            |                   |                                                                                                                                             |

| <b>TXD_H / TXD</b><br>4-Level Modulation Mode<br>MSB of Transmit Data<br>2-Level Modulation Mode | Output            | The Most Significant Bit of the Transmit data.                                                                                              |

| 4-Level Modulation Mode Only                                                                     |                   | Transmit Data output. This pin connects to the WL800 TXD input via a 20KOhm resistor                                                        |

| <i>DE6003 Mode</i><br>Serial Transmit Data                                                       | Output            | Transmit Data output.                                                                                                                       |

| <b>TX/RXB / RX/TXB</b><br><i>DE6038 Mode</i><br>Transmit / Receive Control                       | Output            | TX/RXB is used to control the Transmit or Receive state of the radio. ('1' = Transmit, '0' = Receive ).                                     |

| <i>DE6003 Mode</i><br>Receive / Transmit Control                                                 | Output            | RX/TXB is used to control the Transmit or Receive state of the radio. ('1' = Receive, '0' = Transmit).                                      |

| PA_ON<br>PA On / Off Control                                                                     | Output            | Power Amplifier control. ('1' = On, '0' = Off)                                                                                              |

| LCK_DETB<br>Lock Detect                                                                          | Input             | LCK_DETB is an active-low input which indicates that the radio's on-board synthesiser is in lock.                                           |

| STDBYB<br>Radio Power Down Control                                                               | Output            | STDBYB is an active-low output which puts the DE6003/DE6038 into standby mode.                                                              |

| Function | Description                                                                                                                                                        |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                                                                                                                                                    |

| Output   | MOD2LEVB switches the transceiver between 2<br>Level and 4-Level modulation modes.('0' = 2-Level,                                                                  |

|          | 1' = 4-Level).                                                                                                                                                     |

|          |                                                                                                                                                                    |

|          |                                                                                                                                                                    |

| Output   | Clocks channel select data into synthesiser A & M registers.                                                                                                       |

| Output   | Selects between Antenna1 & Antenna2. ('0' = ANT1,<br>'1' = ANT2)                                                                                                   |

|          |                                                                                                                                                                    |

| Input    | This input signal can control the operation of the CCA timer and is reflected in the CCB status register (21h).                                                    |

|          |                                                                                                                                                                    |

| Output   | Channel select data for the WL800 synthesiser                                                                                                                      |

|          | registers.                                                                                                                                                         |

| Output   | PWR_LOB selects between 10mW and 100mW output power ('0' = 10mW, '1' = 100mW).                                                                                     |

|          |                                                                                                                                                                    |

| Output   | CS_LOADB is held low to enable channel load.<br>Data is latched on rising edge.                                                                                    |

|          |                                                                                                                                                                    |

| Output   | LOADB latches parallel channel data into the synthesiser.                                                                                                          |

|          |                                                                                                                                                                    |

|          |                                                                                                                                                                    |

| Output   | CSD0 through CSD6 are the parallel channel select<br>data. These pins are only available on the 144-pin<br>package, and are powered from the HVdd power<br>supply. |

|          | AVdd is the System analogue power supply pin.<br>The voltage on this pin must be equal to that on<br>SVdd.                                                         |

|          | AGnd is the System Analogue Ground.                                                                                                                                |

|          | Output<br>Output<br>Input<br>Output<br>Output<br>Output                                                                                                            |

# 2.4 Device Pin Out

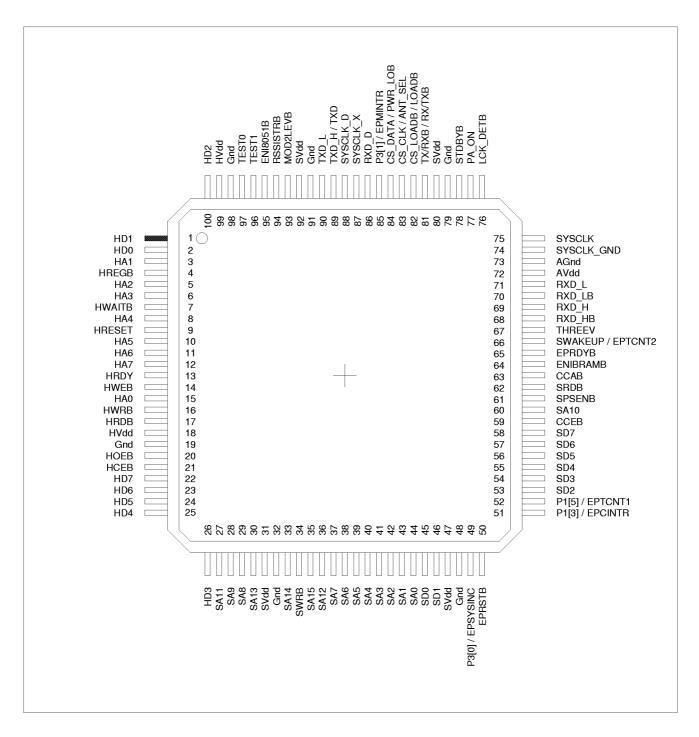

Figure 5. WL102 100 Pin Package Pin Out

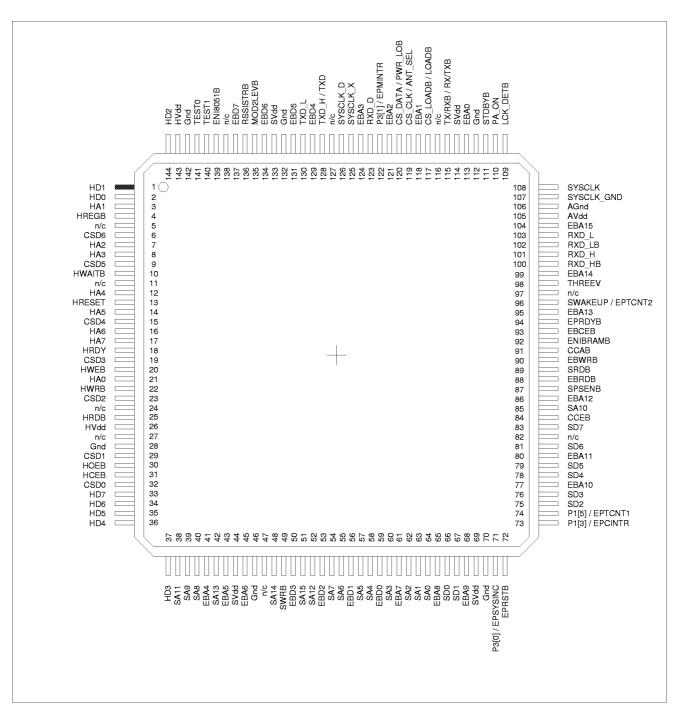

Figure 6. WL102 144 Pin Package Pin Out

# 3. Functional Block Description

### 3.1 Internal 8051 Processor

The WL102 contains an embedded 8051 microcontroller core, operating at a 10MHz clock frequency, and containing 256 bytes of internal RAM. Connections to the 8051 which are internal to the WL102 are:

| ALE            | Latches the high address byte.                                                               |

|----------------|----------------------------------------------------------------------------------------------|

| Port1.4        | Output only. Drives the RDYB/HIREQ logic.                                                    |

| Port1.2        | Output only. Drives the MCB address<br>increment control.                                    |

| INT0 / Port3.2 | Input only. Driven by logical OR of the CCB interrupt output and the SWAKEUP pin (inverted). |

| INT1 / Port3.3 | Input only. Driven by the MCB interrupt output.                                              |

| T0 / Port3.4   | Input only. Driven by the Counter1 terminal count output.                                    |

| T1 / Port3.5   | Input only. Driven by the Counter2 terminal count output.                                    |

Available external connections to the 8051 (when in internal processor mode only) are:

Data bus and demultiplexed Address bus Memory strobes Port1.3 Port1.5 Port 3.1 / TxD Port 3.0 / RxD (Input only)

Internal decode logic latches the processor address and provides enable signals to the blocks defined by the WL102 memory map.

#### 3.1.1 System Memory Map in Normal Mode

All program memory accesses (SPSENB active) select the code memory enable (CCEB), in the range 0000 to FFFF. Data memory accesses (SRDB or SWRB active) are decoded as follows:

| Address (hex)             |        | Decoded block                  |

|---------------------------|--------|--------------------------------|

|                           |        |                                |

| 0000                      | - 7FFF | Not assigned                   |

| 8000                      | - 8FFF | MCB                            |

| 9000                      | - 9FFF | Attribute Memory               |

| A000                      | - BFFF | Internal Data RAM              |

| C000                      | - CFFF | Power Control + Counters       |

| D000                      | - DFFF | RSSISTRB output (on SRDB only) |

| E000                      | - EFFF | ССВ                            |

| F000                      | - FFFF | Not assigned                   |

| Table 1 System Memory Man |        |                                |

Table 1. System Memory Map

# 3.2 System Memory Map in MCB Execute Mode

All program memory accesses (SPSENB active) select the MCB data register, whilst all data memory accesses (SRDB or SWRB active) select the code memory enable (CCEB).

# 3.3 Data RAM

The WL102 contains 4K bytes of static RAM, mapped into the data memory space of the processor (accessed by SRDB or SWRB cycles) which the processor may use for variable storage etc. If additional storage space is required, an external static RAM may also be used, and mapped to an unused area of the WL102 memory map (see 3.1.1).

# 3.4 Buffer RAM

The WL102 contains 6784 bytes of RAM, which is accessed via the Memory Control Block, providing a dual-port buffer area, accessible by the system processor and via the host interface. Alternatively, with the 144-pin package only, an external RAM may be used (up to 64K bytes). In this case, the internal buffer RAM must be disabled by connecting the ENIBRAMB pin to SVdd.

# 3.5 Power Control

A power-down function is provided under the control of the system processor. Power-down enable signals are provided to each major block. Clocks of individual blocks are disabled when the appropriate power-down bit is cleared. The reset condition is all powered up (ones).

# 3.6 Counters

The two 16 bit counters can be loaded by writing to address locations specified below. Both counters decrement until a terminal count of zero is detected. The terminal count then reloads the latest count start value and generates a 3.2µs active high pulse on the terminal count output. This output is connected to the 8051 Timer input (internal processor) or to the EPTCNT1/EPTCNT2 output pin (external processor). Each counter is stopped by resetting the "Enable counter" bit. The counters load the start value at each enable.

Registers are decoded as follows:

| Addres | SS    | Function                              |

|--------|-------|---------------------------------------|

| 00     | Bit 0 | CCB power-down                        |

|        | Bit 1 | Not used                              |

|        | Bit 2 | Counter 1 power-down                  |

|        | Bit 3 | Counter 2 power-down                  |

| 01     | Bit 0 | Enable Counter1                       |

| 02     |       | Counter 1 start value count high byte |

| 03     |       | Counter 1 start value count low byte  |

| 09     |       | Enable Counter2                       |

| 0A     |       | Counter 2 start value count high byte |

| 0B     |       | Counter 2 start value count low byte  |

|        |       |                                       |

Table 2. Power Down / Counter Registers

# 4. Memory Control Block

# 4.1 I/O Address Space

The MCB I/O space allows access to the dual port buffer RAM used to communicate between the Host and System processes. Access to the buffer RAM is fully dual port, with the Host side being able to asynchronously read or write data at the same time as the system. This potentially leads to design issues when deciding on how to arbitrate between the Host and System having access to the buffer RAM space. Therefore a hardware semaphore system is also included is this block, although the semaphore does not electrically prevent or allow access to the buffer RAM. The WL102 has 6784 bytes of RAM on chip, or an external single port SRAM can be added for increased buffer RAM space, up to 64KBytes. Using external buffer RAM disables the internal RAM block.

The following address decode is used for external and internal access to the buffer RAM for each interface.

| Host Access | System Access | Description                 |

|-------------|---------------|-----------------------------|

| 00          | N/A           | Control register            |

| 01          | 01            | Address pointer (high byte) |

| 02          | 02            | Address pointer (low byte)  |

| 03          | 03            | Data register               |

| 04          | 04            | Semaphore                   |

Table 3. Memory Control Block Register Addresses

In addition the system side of the MCB has the following signals:

| INT1/EPMINTR     | This is the output of Host control register bit 3            |

|------------------|--------------------------------------------------------------|

| 8051RESET/EPRSTB | This is the output of Host control register bit 0            |

| Port1.2/EPSYSINC | This input controls auto increment of the system MCB address |

### 4.1.1 Host Control Register

The Host control register is used to control the type of access to the buffer RAM, and also to control various miscellaneous aspects of the WL102 operation. The register contains the following bits:

| Bit | Name        | Reset Condition |

|-----|-------------|-----------------|

| 0   | SYS_RESET   | 1               |

| 1   | HST INC     | 0               |

| 2   | MCB_EXECUTE | 0               |

| 3   | SYS INT     | 1               |

| 4   |             | 0               |

| 5   | IRQ CLR     | 0               |

| 6   | LOWVDD      | 1               |

| 7   | SEMA4       | 1               |

Table 4. Host Control Register

### 4.1.1.1 SYS\_RESET

This bit controls the Reset line of the internal 8051 block, when in internal 8051 mode, once the Power-on reset has completed. Therefore a '0' in this bit will hold the internal processor in the reset state. Care should be taken that sufficient clocks are allowed to correctly reset the internal 8051 (24 minimum, 2.4uS @ 10MHz). In external processor mode this bit will control the state of the EPRSTB signal directly.

#### 4.1.1.2 HST\_INC

This bit controls the operation of the Host MCB address counter. If this bit is high then the MCB address will automatically increment after each read/write cycle. If this bit is low then the address will not increment (although the data will be re-read/re-written).

#### 4.1.1.3 MCB\_EXECUTE

This bit is used to switch the address map of the WL102 so that instruction read cycles from the system processor will fetch data from the MCB buffer RAM. A high in this bit will switch to MCB Execute mode. In this mode any SPSENB strobe will cause a read of the MCB buffer RAM. The system address counter is set into auto-increment mode (regardless of the state of the internal 8051 Port1 bit6 or the EPSYSINC pin) and cannot be loaded by the system processor. In order to allow a Flash ROM to be written in this mode all system write cycles cause the CCEB ROM enable signal to become active.

In summary, in MCB Execute mode:

The system address counter is forced into increment mode.

The system counter cannot be loaded.

All SPSENB cycles cause MCB buffer RAM reads.

All SWRB cycles cause the CCEB signal to become active.

For a full description of the MCB Execute mode see Section 8.

#### 4.1.1.4 SYS\_INT

This bit is used to drive the internal processors INT1 pin, which can be configured in system software to be edge or level sensitive. In external processor mode this bit directly controls the EPMINTR pin.

### 4.1.1.5 IRQ\_CLR

This bit controls the generation of interrupts from the WL102 to the Host. See Section 6 for a full description.

#### 4.1.1.6 LOWVDD

This bit controls the slew rate of the Host interface outputs in order to minimise power and noise. A '0' is the slow 5V option, a logic '1' is the fast 3V option. On power up the WL102 defaults to the fast speed for the Host interface pins. See Section 11 for a full description.

### 4.1.1.7 SEMA4

This bit allows access to the semaphore logic, in addition to address 04 of the MCB block. The semaphore logic is a dual port lock which guarantees that only one port can have a successful lock at any time. In order to queue a lock request a '0' is written to this bit. Its value is then read back with a '0' indicating a successful lock and a '1' indicating a pending lock. If a '1' is returned the bit can be repeatedly polled until a lock is granted, or the queued lock request can be cancelled by writing a '1' to the bit. To release a granted lock a '1' is written to this bit.

## 4.2 Operation

The System and Host Address pointers are used to set the address of the buffer RAM access. Both pointers are read/write which allows for easier interrupt handling, since the address pointers can be read and restored around any interrupt handling code.

The Host and System Data registers are used to read and write data to or from the buffer RAM itself. If auto-increment is enabled, any read or write cycle to these registers causes an increment for the relevant address pointer.

For a write cycle the data written to the data register is used to program the location pointed to by the address pointer.

For a read cycle the data read is always for the previous address. This is a one cycle latency for the read cycle allowing a fast read time which forces the next byte to be pre-loaded into the read register between read accesses. This means that in order to read an address (or addresses) the following must be performed:

| Switch on/off auto-increment for the port<br>Load the address pointers with the address required. | Optional                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Perform a dummy read cycle on the data register.                                                  | The value read will be for the address held before the address pointers were loaded - so discard.                                                                                                                                              |

| Perform a read cycle.                                                                             | The data read will be for the address loaded into the address pointers.                                                                                                                                                                        |

| Perform a read cycle.                                                                             | If increment is on the data read will be from the<br>address loaded + 1.<br>If increment was off then the address will be re-read.<br>If the other port has modified the data at this address<br>then this will be reflected in the data read. |

In this way the MCB buffer RAM can be polled at a particular location or a packet of data can be read or written. It is envisaged that buffer management can be performed by allocating a portion of the buffer RAM to be lockable, by the semaphore, in software. This will allow the memory in the buffer to be allocated dynamically or statically as the particular system configuration requires.

# 5. Communications Control Block

### 5.1 Introduction

The CCB interfaces directly with the radio transceiver. It has a number of configuration options which allow it to use a variety of transmission/reception protocols. It has principally been designed to be compatible with both the DE6003 radio and the DE6038 radio.

The CCB is configured and controlled by either the internal 8051 micro-controller or an external processor (in the remainder of this section the word 'processor' will apply to either controller). After the processor switches the CCB into receive/transmit, the CCB directly transfers received/transmitted data to/from the MCB. The functions performed by the CCB are described below, together with some recommendations on how to configure the CCB.

### 5.2 Generic Packet Format

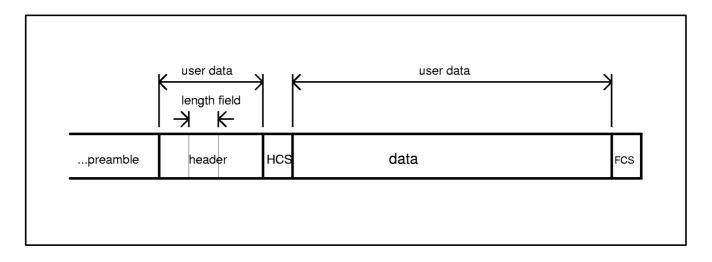

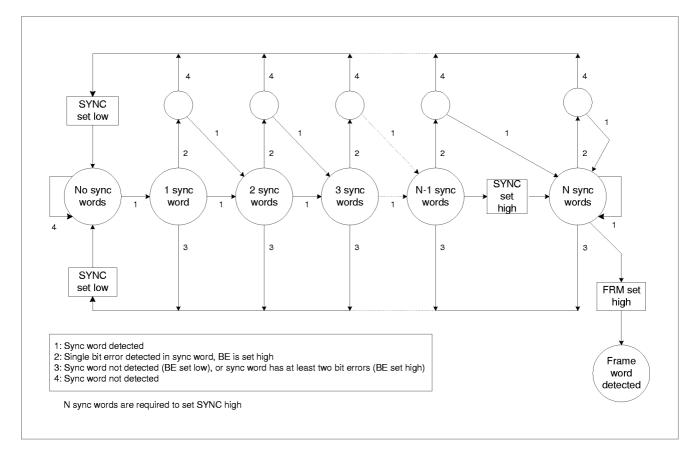

The CCB has principally been designed to work with data packets in the format illustrated in Figure 7.

The 'preamble' consists of a Sync. Word, repeated several times, followed by a Frame Word. The 'header' must contain the data length field, which can be between 8 and 16 bits long. The HCS (Header Checksum) and FCS (Frame Checksum) fields are CRC generated codes which the CCB can add in order to detect errors in the received data.

Whenever possible, the sub-blocks have been designed to work in any configuration. However, some blocks expect certain information in order to work properly. In particular, the 4-level blocks have only been designed to work with an IEEE 802.11 type of packet (see Section 5.11 for further details on restrictions for 4-level transmission/reception).

# 5.3 CCB Sub-blocks

Figure 8 illustrates the sub-blocks of the CCB.

Figure 8. CCB Sub-blocks

### 5.3.1 CCB control

The operations of the CCB are controlled by either the internal 8051 micro-controller, or by an external processor. The processor can read from or write to the Control Registers, which control the operation of the CCB (discussed in Section 5.4). The processor can also read and write to the Configuration Registers, which are discussed in Section5.5. The processor can read the Status Registers (discussed in Section 5.6) which provide feedback on the current state of the CCB.

### 5.3.2 FIFO

The CCB includes a 64-byte FIFO, to provide a buffer in the transfer of data between the radio and the Memory Control Block. Reading and writing to the FIFO from the radio side is independent of DMA transfers to the MCB.

In transmit mode, if the FIFO is not full, a byte will be read from the MCB on every other 'bit\_clk' cycle (a 'bit\_clk' cycle will either be 1µS or 1.6µS depending on the CCB configuration (Section 5.5.18.1). When the FIFO is full, the CCB will wait until the radio side removes a byte, and then the CCB will 'top-up' the FIFO from the MCB side. This will continue until the number of bytes read from the MCB equals the number of bytes expected by the 'Data Length' detection block (Section 5.3.3).

In receive mode, data received by the radio will be stored in the FIFO until the processor gives permission to transfer the data to the MCB. Once the processor gives permission, the CCB will wait for a pre-programmed period. It will then write to the MCB on every other 'bit\_clk' cycle until the FIFO is empty. The CCB will then transfer data to the MCB as soon as it is available from the radio side, until all of the received packet has been transferred to the MCB.

In FIFO access mode (Section 5.5.18.4), the processor can write to Addr. 05h, which writes bytes into the FIFO. The pointers in the CCB will be updated in the same way as they would be for a DMA read. When the CCB starts a transmission, as soon as a byte is available in the FIFO, the CCB pre-loads four bytes into the BSE registers. With the usual DMA delay mechanism this would wait until the DMA starts. However, if the processor writes bytes directly into the FIFO, at the start of a transmission the CCB will immediately try to pre-load the BSE registers. Therefore, either the DMA delay should be very small, or preferably, the processor should write a minimum of four bytes to the FIFO prior to starting the transmission (otherwise a FIFO read error will be generated).

Also, in FIFO access mode, Addr. 40h to 7Fh are mapped to the FIFO read address. When the processor reads the FIFO this way it does not affect the CCB pointers (i.e. the data is left in the FIFO, waiting to be transferred to the MCB).

Addr. 28h contains the FIFO in-pointer, and Addr. 29h contains the FIFO out-pointer. The in-pointer indicates the address of the last byte written to the FIFO (either from the radio side in receive mode, from the MCB during transmit, or from ADDR. 05h in FIFO access mode). The out-pointer indicates the address of the next byte to be read from the FIFO (either by the radio side in transmit mode, or by the MCB after an 'Upload Grant' has been given).

The FIFO access mode should not be used to read the FIFO during either transmit, or after an 'Upload Grant' has been given in receive. The FIFO access mode should not be used to write to the FIFO while either the Commence Transmit or Commence Receive bits are low.

#### 5.3.3 Data Length Detection

All packets must contain a 'Data Length' field in the Header. The Data Length field consists of a pair of bytes which specify how many bytes are in the frame. The location of the 'Data Length' field is specified in Addr. 1Bh (Section5.5.14). The second byte of the 'Data Length' field is 'ANDed' with the contents of Addr. 1Ah (Section5.5.13). If the Legacy bit (Section 5.5.18.2) is set, the 'Data Length' field applies to the frame length excluding the length of the Frame Checksum. When the Legacy mode bit is clear, the 'Data Length' applies to the frame length including a 32-bit Frame Checksum. (N.B. Four is added to the data length excluding the Frame Checksum, irrespective of the type of Frame Checksum being used (Addr. 1Eh, Bit 0). Therefore, when the Legacy mode bit is clear, a 32-bit Frame Checksum should always be used). In Legacy mode (bit set), if any of the three MSB of the second byte of the 'Data Length' field are set, the 'Data Length' field is cleared to zero. If the 'Data Length' field is zero the transmission/reception state machine will terminate after the Header Checksum.

#### 5.3.4 CRC Checksum

The CCB actually contains three CRC Checksum generators, which are used to detect errors in the received data. All three Checksum generators are initially loaded with the 'Net Key', which is the seed of the CRC. One CRC Checksum generator is used to generate/check the Checksum of the header. It can be configured to be either 16 or 32 bits long. The second Checksum generator is used to generate/check the Checksum of the frame. It can also be configured to be either 16 or 32 bits long. The advantage of having the Frame Checksum (FCS) generator independent of the Header Checksum (HCS) generator is that the FCS can start before the HCS finishes (when the FCS starts in the header, it is disabled while the HCS is being received/transmitted). The third CRC Checksum is used in 4-level GFSK mode. The 4-level Checksum starts when the CCB switches to 4-level mode (discussed in Section 5.11), and the Checksum can only be 32 bits long.

All three Checksum's implement the same CRC code, which is the same as the code used in the IEEE 802.11 standard. The 16-bit CRC uses the generator polynomial:

$$x^{16}+x^{12}+x^{5}+1$$

The checksum transmitted can either be the Checksum remainder, in which case the remainder after reception should be zero, or the ones complement of the Checksum remainder, in which case the remainder after reception should be: x<sup>12</sup>+x<sup>11</sup>+x<sup>10</sup>+x<sup>8</sup>+x<sup>3</sup>+x<sup>2</sup>+x<sup>1</sup>+1

The 32-bit CRC uses the generator polynomial:

$$X^{32}+X^{26}+X^{23}+X^{22}+X^{16}+X^{12}+X^{11}+X^{10}+X^8+X^7+X^5+X^4+X^2+X+1$$

.

The checksum transmitted can either be the Checksum remainder, in which case the remainder after reception should be zero, or the ones complement of the Checksum remainder, in which case the remainder after reception should be:

$$x^{31}+x^{30}+x^{26}+x^{25}+x^{24}+x^{18}+x^{15}+x^{14}+x^{12}+x^{11}+x^{10}+x^{8}+x^{6}+x^{5}+x^{4}+x^{3}+x+1$$

However, in the CCB, CRC's are implemented in reverse order (i.e. L.S.B. is actually M.S.B.). Therefore, the 'Net Key' and the CRC remainder registers are in reverse order to those specified in the IEEE 802.11 standard. The CRC remainder register should contain F0B8h for a ones complement 16-bit CRC, and DEBB20E3h for a ones complement 32-bit CRC.

#### 5.3.5 Scrambler

The scrambler implements the following generator polynomial, which generates a 127-bit repeating pattern:

x<sup>7</sup>+x<sup>4</sup>+1

The generator is initialised to all ones at the start of reception/transmission, and serially scrambles all bits except the BSE stuff symbol. If BSE is used, scrambling will start after the first stuff bit (i.e. after 17 bits if 16/17 BSE is used, or 33 bits if 32/33 BSE is used). If BSE is not used, scrambling starts with the first bit after the Sync. Frame Delimiter.

#### 5.3.6 Bit Stuffing/BSE

Two mutually exclusive encoding options are included to make the data more suitable for radio transmission. The Bit stuffing option can be configured to either add an extra bit after 8 or 16 bits. The stuff bit added will be of the inverse polarity to the last bit transmitted. (N.B. When data scrambling is used with bit stuffing, the scrambler generator is incremented during the stuff bit, but the newly generated scramble bit is ignored so that the bit output is the inverse of the last bit output). The main advantage of bit stuffing is that it ensures there will be at least one edge in the data every 9 or 17 bits, which helps with clock recovery (and there is a requirement for the DE6003 radio that the data polarity should change within 27us).

Bias Suppression Encoding (BSE) is implemented as described in the IEEE 802.11 (Draft 5) standard. It minimises the cumulative bias of a packet (i.e. ratio of '1's to '0's) by deciding whether inverting a block of data will increase or decrease the bias. The block size can be configured to be either 16 or 32 symbols (plus a stuff symbol to indicate if the block has been inverted).

## 5.4 Control Registers

The CCB has five control registers (from Addr. 00h to Addr. 04h), which are used to control the operation of the CCB after the initial configuration period. The registers control whether the CCB is trying to transmit or receive, which channel is to be used, the address matching options, and which conditions cause an interrupt. In addition, there is the FIFO Write register (which can only be used in FIFO access mode), and the CCA Timer register.

The registers can be both read and written to, and all the control registers will be set to a specified default condition by a hardware reset. The control registers are not affected by a software reset (A software reset is explained in Section 5.4.1.7).

### 5.4.1 Control Register 00h

#### 5.4.1.1 Configuration Enabled bit (Addr. 00h, Bit 0)

When this bit is set, the configuration registers discussed in Section 5.5 can be loaded. When the bit is cleared, the clock to the configuration registers is disabled. The registers retain the value they were last loaded with, but cannot be loaded with a new value. Disabling the configuration registers saves power.

The Configuration Enabled bit is set by a hardware reset.

#### 5.4.1.2 Channel Hop bit (Addr. 00h, Bit 1)

The WL102 has two different channel selection methods, one for the DE6003 radio, and the other for the DE6038 radio (DE6003/DE6038 configuration discussed in Section 5.5.18.1). In either case, the Channel Hop bit will be set by a hardware reset.

#### 5.4.1.2.1 Channel selection in DE6038 mode

The DE6038 radio uses the WL800 Frequency Synthesiser which is programmed serially, using a three wire bus to load an 8-bit number. The value loaded for receive mode should be 43MHz less than the value loaded for transmit mode (The values loaded are discussed further in Section 5.4.2.1). The Channel Hop bit (CH) is used to enable the automatic channel load sequence. When CH is low, the WL800 will be loaded with a new channel every time either CT (Commence Transmission) or CR (Commence Receive) are taken low. If CH is high, a new channel will not be loaded.

The CH bit can be cleared either at the same time as, or before CT or CR is cleared to enable the channel load sequence.

#### 5.4.1.2.2 Channel selection in DE6003 mode

The DE6003 uses a 7-bit bus to specify the channel, plus a strobe signal to load the channel. The falling edge of the Channel Hop bit triggers the state machine, which causes the channel strobe signal to pulse low for  $\mu$ S, which loads the DE6003 channel. The CH bit then needs to be set again before the next channel load sequence can be triggered. The channel loaded is discussed in Section 5.4.2.2.

#### 5.4.1.3 Commence Receive (Addr. 00h, Bit 2)

The Commence Receive bit (active low) is the bit which tells the CCB to try to receive a packet. The Commence Receive bit being low causes an internal bit called Commence Receive (CR) to go low. CR being low enables the RXD buffers and the clock recovery block. However, CR can be over-ridden by the Commence Transmit bit and subsequent transmit sequence. The state of the internal CR bit can be read from Addr. 21, bit 6 (see Section 5.6.2.7).

The Commence Receive bit is set by a hardware reset.

#### 5.4.1.4 Commence Transmit (Addr. 00h, Bit 3)

The Commence Transmit bit (active low) is the bit which tells the CCB to transmit a packet. As with the Commence Receive bit, there is an internal bit called Commence Transmit (CT). If CR was low, CT will wait three 'bit\_clk' cycles (as if CCB configured for 1 or 2Mbit/s, 4.8us if CCB configured for 625kbit/s) to allow CR to terminate cleanly before CT goes low. The CT bit will always over-ride the CR bit. Clearing the Commence Transmit bit also acts as the DMA Grant trigger. After the delay period programmed into Addr. 3Eh (Section 5.5.21), the CCB will assume it has access to the MCB and begin DMA transfers.

The Commence Transmit bit is automatically set high when the Tx. DMA Transfer Complete interrupt is generated. The Commence Transmit bit should not be set low again until the radio finishes transmitting, indicated by Tx. DMA Transfer Complete status bit being cleared (Addr. 20h, bit 4) and the RXTX bit being set high (Addr. 21h, bit 4).

The Commence Transmit bit is set by a hardware reset.

#### 5.4.1.5 CCB Software Reset (Addr. 00h, Bit 4)

The CCB Software Reset bit (active low) resets all the internal registers and state machines in the CCB (e.g. clock recovery, BSE, CRC, FIFO, Receive/Transmit state machines). However, it does not effect the Control or Configuration registers (i.e. the registers described in Sections 5.4 and 5.5). A reset is caused by clearing the bit. The reset bit will automatically be set again on the clock cycle after the access.

The CCB Software Reset bit is set by a hardware reset. (The hardware reset is applied to all the registers reset by the software reset as well as the Control and Configuration registers).

### 5.4.1.6 Interrupt Clear (Addr. 00h, Bit 5)

The Interrupt Clear bit will clear an interrupt due to CCA Timer Equal Zero, a Frame Upload Complete, a Frame Upload Request, a Header Upload Request, or a Tx. DMA Transfer Complete. It will not clear an interrupt due to a FIFO Read Error or a FIFO Write Error. An interrupt due to the PLL lock detect signal will be cleared, but if the PLL lock detect signal is still in the fail state (i.e. set) the interrupt will immediately re-occur. Interrupt masks are discussed in Section 5.4.5, and interrupt identification is discussed in Section 5.6.1.

To clear an interrupt the Interrupt Clear bit needs to be set. Two 'bit\_clk' cycles later, or after writing to Addr. 00h is complete (which ever is longest), the Interrupt Clear bit will automatically be cleared. The Interrupt Clear bit is cleared by a hardware reset.

### 5.4.1.7 Standby (Addr. 00h, Bit 6)

The Standby bit controls an output pin to the radio. It does not affect any of the functions of the CCB. Powering-down the CCB will not affect the state of the Standby pin to the radio. The Standby bit is cleared by a hardware reset, which is sleep mode for both the DE6003 and the DE6038 radios.

### 5.4.1.8 Upload Grant (Addr. 00h, Bit 7)

The Upload Grant bit should be set in response to an Upload Request. In receive mode, the CCB will generate a Header Upload Request when it finds valid preamble plus the frame word. At this point it will store data in it's 64 byte FIFO until it has been given an Upload Grant. The Upload Grant signal gives the CCB permission to transfer the header data into the MCB (after the delay period specified in Addr. 3Eh).

After the header data has been transferred to the MCB, the CCB generates a Frame Upload Request. The Upload Grant bit should then be set again to permit the transfer of the frame to the MCB. In either case of upload request, if an Upload Grant isn't given and the FIFO becomes full, a FIFO Write Error will occur.

The Upload Grant bit is automatically cleared after the DMA state machine has started. The Upload Grant bit is also cleared by a hardware reset.

#### 5.4.2 Channel Select register "SDT" (Addr. 01h)

The Channel Select Register "SDT" holds the code for the frequency which will be loaded into the radio. In DE6003 mode, the "SDT" register is used to store the channel for both transmit and receive mode. In DE6038 mode, the "SDT" register is used to store the transmit channel only. Section 5.12 contains a table showing how the code relates to the final frequency. A hardware reset will load the "SDT" register with 6Bh.

#### 5.4.2.1 Channel selection in DE6038 mode

The DE6038 radio uses a frequency synthesiser which is serially programmed by the WL102. The frequency synthesiser can synthesise 144 frequencies in 1MHz steps. The 8-bit number serially loaded into the synthesiser gives the division ratios required for the two counters in the synthesiser's programmable divider system to generate the required channel. The division ratio required to transmit on a specific channel is different from the divide ratio required to receive on the same channel. Table 22 shows the values which should be loaded into the WL800 frequency synthesiser.

The "SDT" register holds the value which will be loaded in transmit mode. On the falling edge of CT (Commence Transmit discussed in Section 5.4.1.4), if CH (Channel Hop bit discussed in Section 5.4.1.2) is low, the channel load state machine is started. The "SDT" register will be clocked out of the "CS\_D" pin at the system clock rate (i.e. one bit every 100ns), MSB (Most Significant Bit) first. The "CS\_CLK" pin will be the inverted system clock, active during the channel load sequence, with the rising edge approximately 50nS after "CS\_D" changes. The "CS\_LOAD" pin will go low at the start of the channel load sequence, and then high again at the end of the channel load sequence.

#### 5.4.2.2 Channel selection in DE6003 mode

In DE6003 mode the frequency synthesiser is programmed by a 7-bit bus, with a strobe signal. The same value is used for both the transmit and receive channel. Therefore, "SDT" is used both in transmit mode and receive mode. Section 5.12 shows how the value loaded relates to a channel. The falling edge of CH (discussed in Section 5.4.1.2.2) starts the channel load state machine. The seven LSBs are output on the CSD pins. "CS\_LOAD" will pulse low for  $\mu$ S, which loads CSD into the DE6003. After the channel load state machine finishes, the CH bit needs to be set manually before another channel load sequence is triggered.

#### 5.4.3 Channel Select Register "SDR" (Addr. 02h)

The Channel Select register "SDR" holds the code for the frequency which will be loaded at the start of receive in DE6038 mode. Section 5.12 contains a table showing how the code relates to the final frequency. The channel load sequence is as described in Section 5.4.2.1, except it is triggered by the falling edge of CR (discussed in Section 5.4.1.3) instead of CT. A hardware reset will load the "SDR" register with 30h.

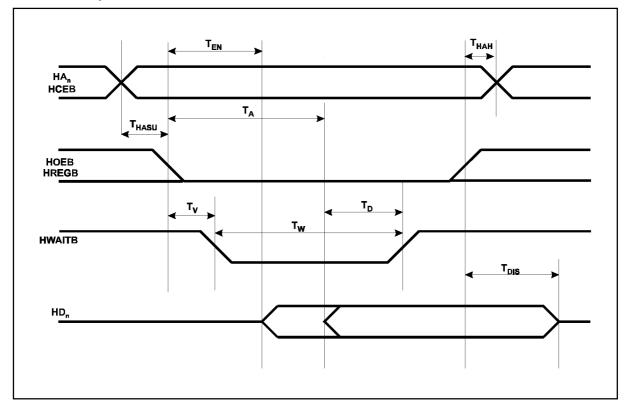

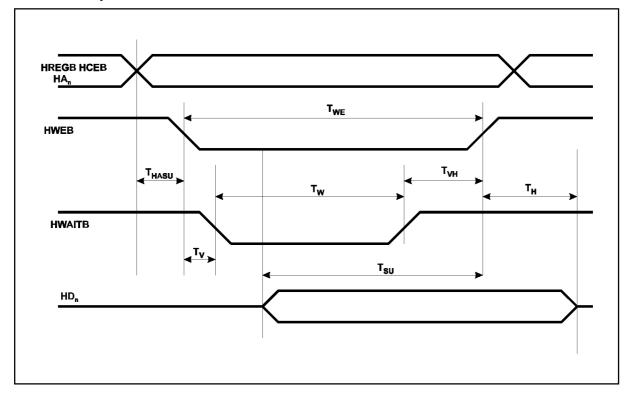

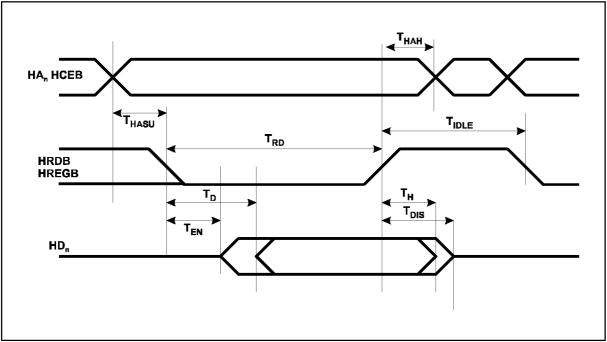

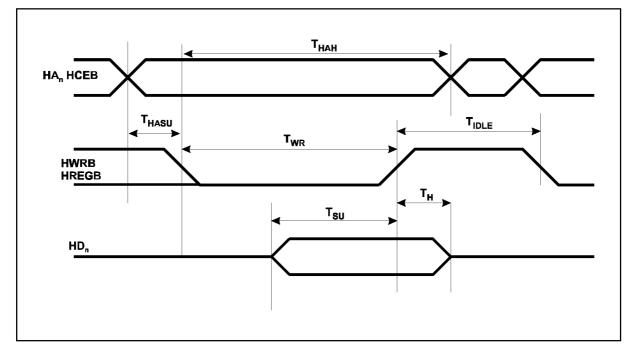

#### 5.4.3.1 Antenna Select (Addr. 02h, Bit 0)