Data Book

## **FEATURES**

### **■** Complete PC telephony solution

- Up to 33.6-kbps data rates

- Highly integrated three- or four-chip set

- Controller-based robust platform

- Exceeds Microsoft® PC 95 requirements

- Full-duplex, echo-cancelled digital speakerphone

- ITU-V.70 DSVD (digital simultaneous voice and data) upgrade option

- ITU-V.80 videoconferencing

- International telephony support

#### Data modulation

- ITU-T V.34 (33,600 to 2400 bps) symmetric and asymmetric operation

- ITU-T V.32 bis, V.23, V.22 bis, V.21

- Bell® 212A and 103

#### Fax modulation

ITU-T V.17, V.29 to 14,400 bps

## Voice telephony

- Full-duplex, echo-cancelled digital speakerphone

- Radish® VoiceView™ upgrade option Telephone emulation for headset applications

- Microsoft® Windows® TAPI-compliant

- ITU-V.70 DSVD upgrade option

- ITU-V.80 for videophone

#### ■ Voice coder

- Voice compression: ADPCM, linear, and CL1

- 4800, 7200, 8000, 9600, and 11025 samples per second

(cont. next page)

# V.34+ FastPath™ 33.6-kbps Data/Fax/Voice **Chipset Family**

### OVERVIEW

The V.34+ FastPath™ chipset family is an ideal solution for today's PC telephony applications, and it is a robust platform that will support future communication standards. With a complete complement of industry-standard features for data, fax, and voice applications, the V.34+ family satisfies internal, standalone, and PC Card applications, plus advanced features such as 33.6-kbps modulation speeds and DSVD.

## Integrated, Open Architecture

The FastPath platform owes its capabilities to the sophisticated architecture of its controller and DSP (digital signal processor). Each component's highly integrated design minimizes part count and board area. The single-platform design means that no additional circuitry is needed for features including DSVD, speakerphone, PC Card, serial inter-

(cont. next page)

## System **Block Diagram**

Version 1.1

## FEATURES (cont.)

## ■ Data link layer protocols

- Error correction: ITU V.42 and MNP® 2–4

- Data compression: ITU V.42 bis and MNP® 5

## DTE integrated interface alternatives

- Serial RS-232/V.24 interface

- ISA bus direct or plug-and-play

- PCMCIA bus interface

## **■** Controller functionality

- Industry-standard AT command driven

- Fax Class 1 commands

- Voice IS-101 commands

#### ■ Minimal-component design

- Direct connection to ISA bus

- Single crystal

- Passive hybrid

#### Low power requirements

- Single +5-V power source; 3.3-V DSP option

- Automatic sleep and wake-up modes

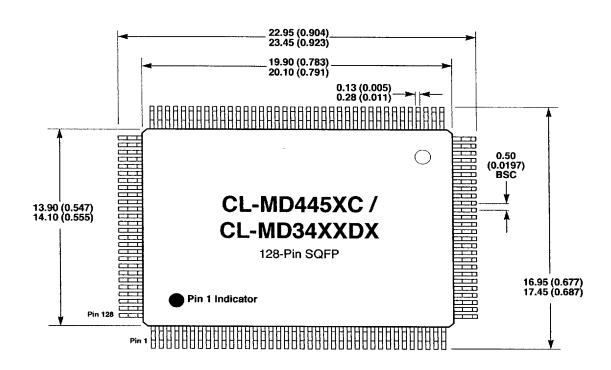

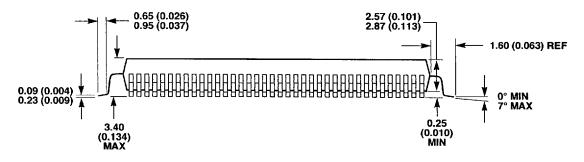

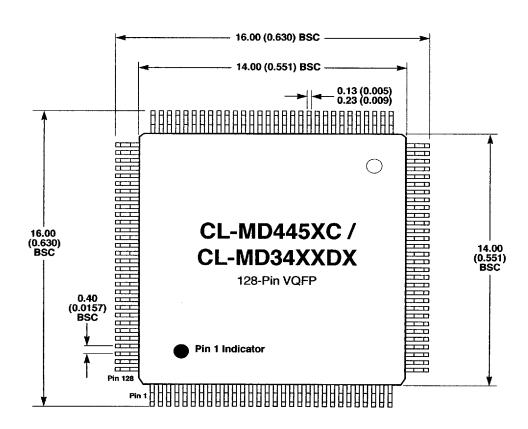

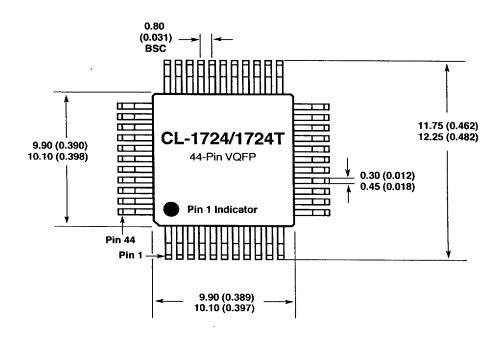

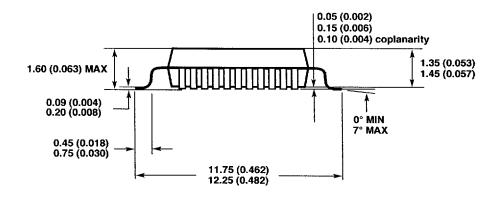

## Small package options

- Controller and DSP: 128-pin SQFP or VQFP packages

- SAFE: 44-pin VQFP package

## **OVERVIEW** (cont.)

face, and ISA plug-and-play compatibility. The single platform serves all levels of product, from basic feature sets to full-featured DSVD/speakerphone applications. The V.34+ family exceeds Microsoft® PC 95 specifications for Windows® and legacy applications.

## **Satisfies Legacy Applications**

The FastPath™ platform supports all requirements for PC-based communications, whether for internal, standalone, or PC Card applications. With its robust controller and powerful DSP, the V.34+ supports even the most demanding DOS gaming applications. The CL-MD34XX supports all industry-standard AT commands for data, IS-101 voice, and Class 1 fax.

## **Comprehensive Telephony Features**

Voice telephony is becoming increasingly important in modem-based products. This chipset family offers a complete telephony interface with features such as Caller ID, voice mail, and answering machine capabilities that include call progress detection and tone generation.

For more advanced voice features, the V.34+ platform adds telephone emulation for headset applications and a Radish® VoiceView™ upgrade option for alternate transfers of voice and data over the same connection. The DSVD upgrade option enables data transfer in realtime during a voice conversation, an essential for whiteboard applications and sophisticated customer support. Additionally, the CL-MD34XX's full-duplex, echocancelled digital speakerphone offers the latest technology for hands-free computer telephony.

The speakerphone operates in all modes, including DSVD. All voice features are fully compliant with Microsoft's Unimodem-V and TAPI standards, and all commands comply with IS-101 voice command standards.

## International Telephony Support

V.34+ chipsets support international applications for PC Card, ISA, and serial bus designs. Cirrus Logic's configuration utility modifies the chipset firmware to comply with international standards. Cirrus Logic also provides international DAA design recommendations.

#### Platform of the Future

The FastPath™ family is a solid base for future innovation. The controller's embedded RISC processor uses a unique caching architecture that enables the use of lower-cost memory chips. The controller code is open for modification in a C code development environment. A Flash memory interface and configuration utility allow downloading of code and customization of features.

The DSP delivers the bandwidth to handle multiple tasks simultaneously and to support specialized functions. Many advanced features are already built in, including a full-duplex, echo-cancelled speakerphone and a DSVD vocoder. Concurrent operation is enabled for even the most advanced features, such as speakerphone operation in DSVD mode. Other built-in features are call progress and tone generation, including DTMF, CNG, and Caller ID. Tones can be tailored to special requirements.

## **REVISION HISTORY**

## Version 1.1 February 1997

Following are the major changes made since version 1.0:

### Features/Overview

Radish® VoiceView™ is optional.

Added ITU-V.80 for videoconferencing.

## Chapter 1

Section 1.1 on page 12: The DSP chip CL-MD3661DT was replaced with the CL-MD3660DT in all CL-MD34XX chipsets.

#### Chapter 3

Section 3.18 on page 20: A Cirrus Logic firmware downloading utility is now available.

#### Chapter 4

Section 4.4 on page 23: The NVRAM is never optional.

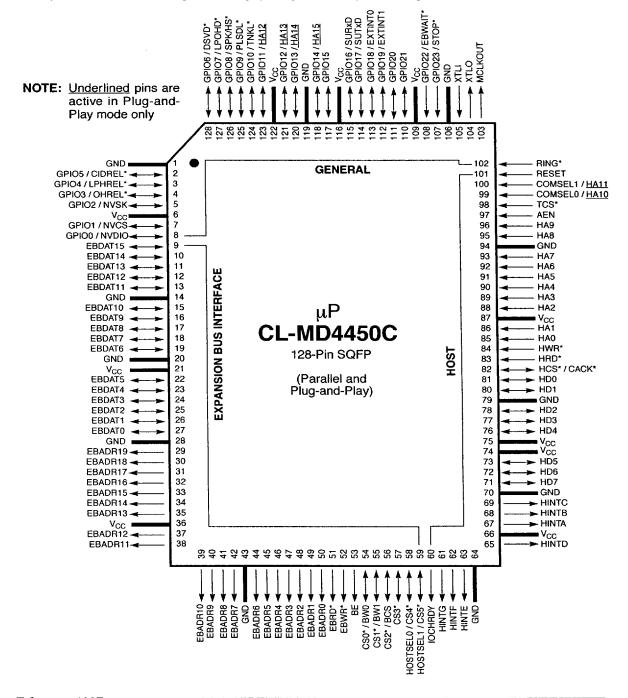

Section 6.1.1 on page 41: The following pins on the parallel and plug-and play  $\mu P$  (128-pin SQFP) pinout were changed:

- Pin 57: CS3\* An I/O pin, not an output pin

- Pin 59: HOSTSEL1, not HOSTEL1

- Pin 110: Removed INTA1. The INTA1 signal is no longer incorporated in the V.34+ chipsets.

- Pin 111: Removed INTA0. The INTA0 signal is no longer incorporated in the V.34+ chipsets.

- Pin 119: GND, not GGND.

## Chapter 6

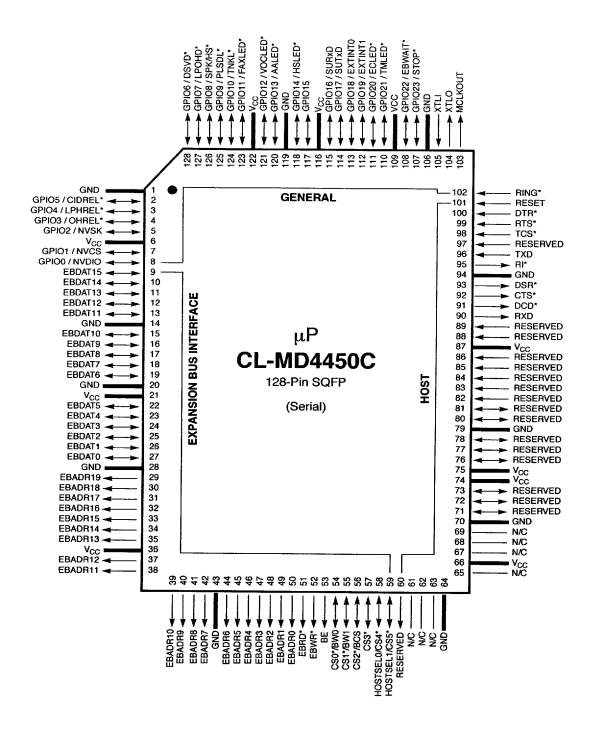

Section 6.1.2 on page 42: The following pins on the serial  $\mu P$  (128-pin SQFP) were changed:

- Pin 57: CS3\* An I/O pin, not an output pin

- Pin 59: HOSTSEL1, not HOSTEL1

- Pins 61–63, 65: These no-connect pins have no direction.

- Pin 110: Removed INTA1; changed to I/O from in.

- Pin 111: Removed INTA0

- Pin 119: Changed GGND to GND

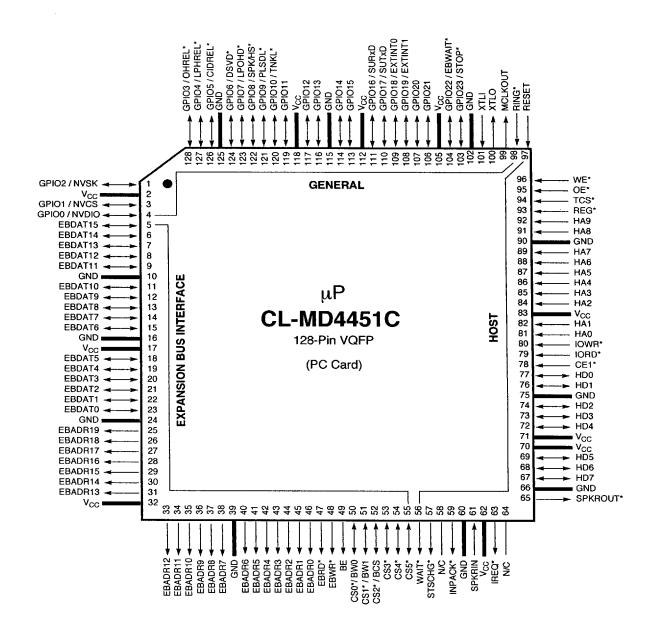

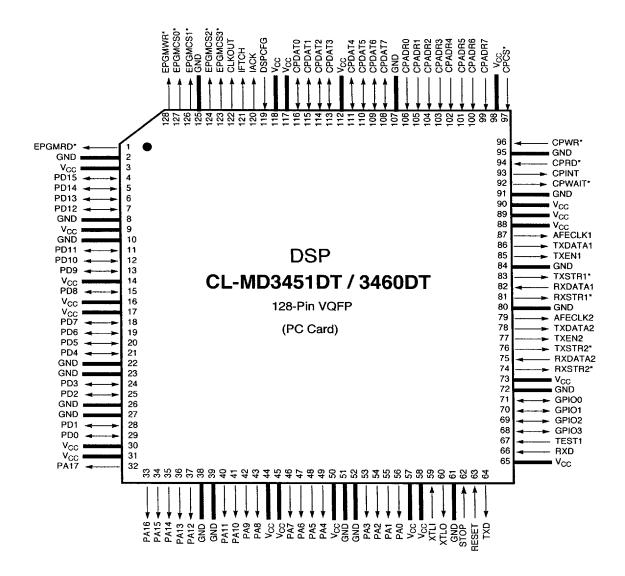

Section 6.1.3 on page 43: The following pins on the PC Card  $\mu$ P (128-pin VQFP) were changed:

- Pin 53: CS3\* An I/O pin, not an output pin

- Pins 86–89, 91: HA4–7, HA8: These host address pins are all inputs, not I/Os.

- Pin 106: Removed INTA1

- Pin 107: Removed INTA0

- Pin 115: Changed GGND to GND

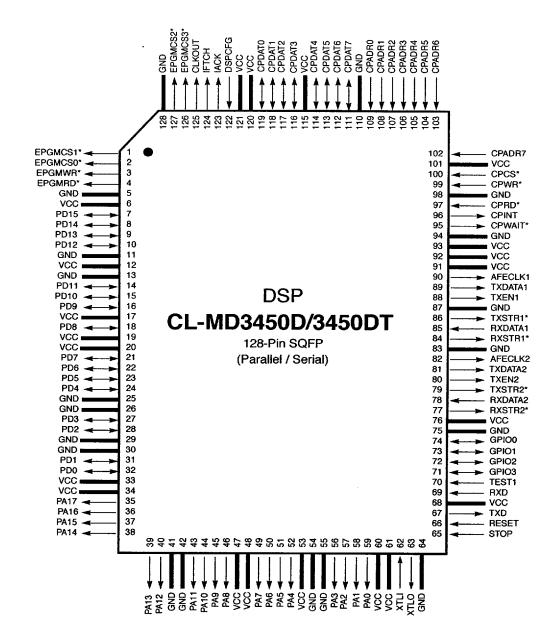

Section 6.2.1 on page 44: The following pins on the DSP's 128-pin SQFP pinout were changed:

- Pin 125: CLKOUT, not CLKOUT\*

- Pin 124: IFTCH, not IFTCH\*

- Pin 123: IACK, not IACK\*

- Pin 122: DSPCFG, not DSPCFG\*

Section 6.2.2 on page 45: The following pins on the DSP's 128-pin VQFP pinout were changed:

- Pin 62: STOP was changed from an output to an input

- Pin 122: CLKOUT, not CLKOUT\*

- Pin 121: IFTCH, not IFTCH\*

- Pin 120: IACK, not IACK\*

- Pin 119: DSPCFG, not DSPCFG\*

#### Chapter 7

Table 7-1 on page 47: HCS\*/CACK\* are no-connect for parallel and plug-and-play modes with internal address decode.

page 64: Changed connection instructions for CS2\*.

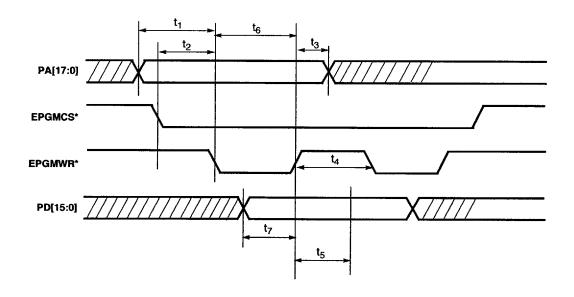

page 66: Changed descriptions of EPGMRD\*, EPG-MWR\*, and DSPCFG.

Section 7.1.1.2 on page 51: Changed reserved pin 84 to be connected to  $V_{cc}$  through a 47-k $\Omega$  resistor.

page 69: Changed descriptions of TXEN1 and TXEN2, TXSTR1\* and TXSTR2\*, and RXSTR1\* and RXSTR2\*.

page 64: The CS2\* pin can be connected to either  $V_{CC}$  or GND through a 10-K or larger resistor, not only a 47-K resistor.

February 1997

DATA BOOK v1.1

REVISION HISTORY

3

## Chapter 8

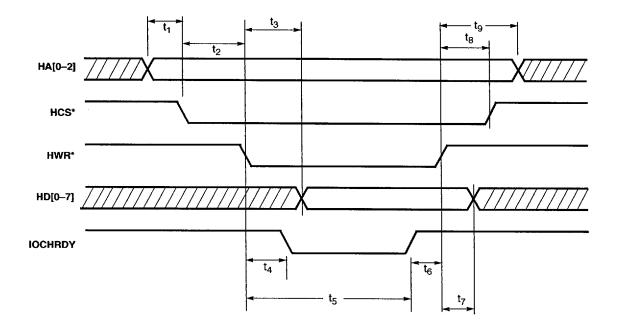

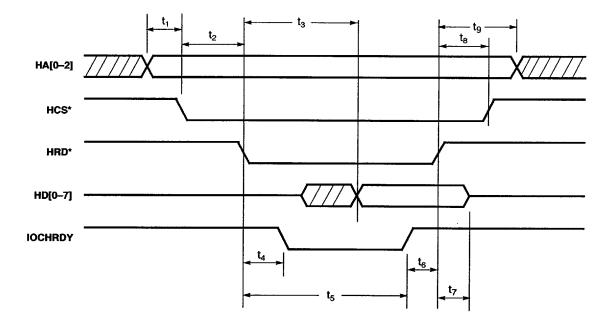

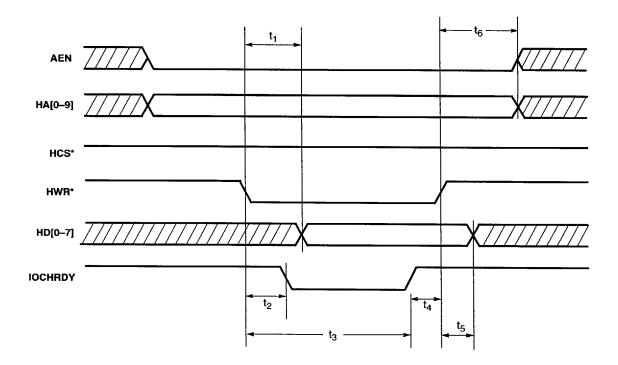

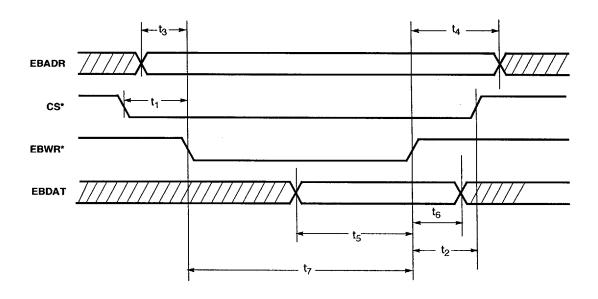

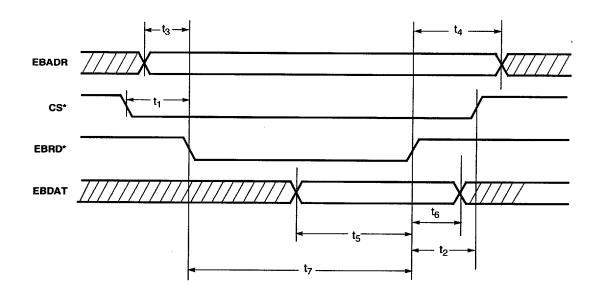

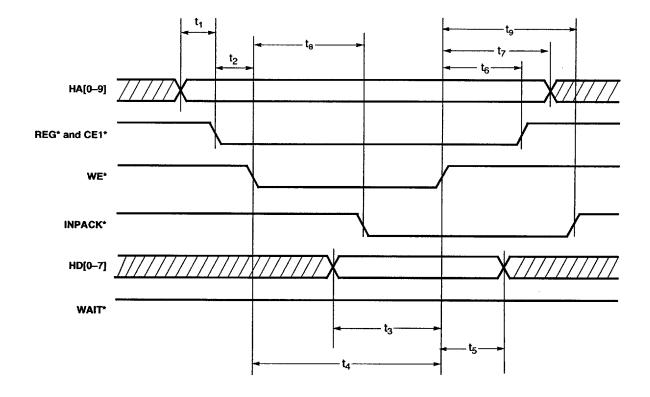

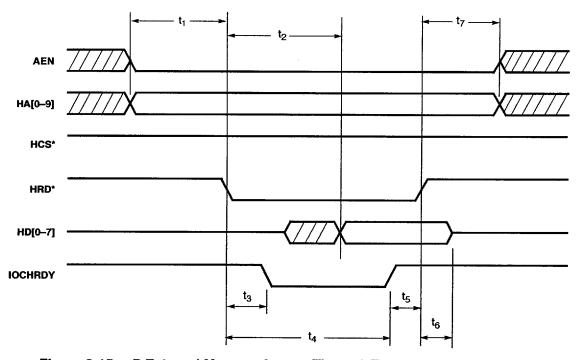

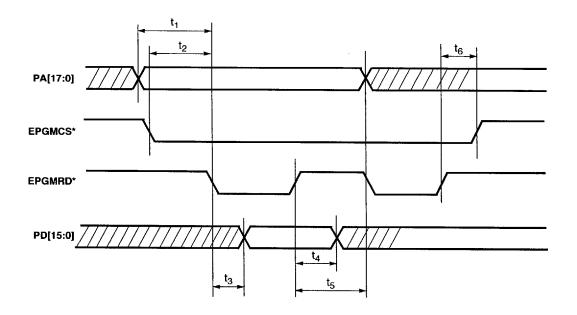

Figure 8-2 on page 78: Changed t<sub>8</sub> interval.

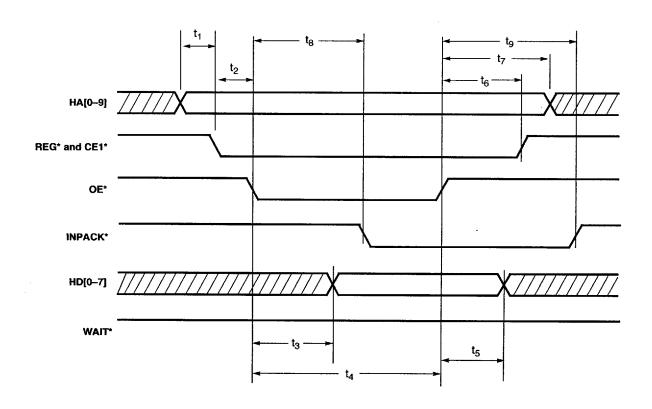

Table 8-5 on page 79: Changed former  $t_7$  to  $t_6$ ; eliminated old  $t_6$ .

Table 8-6 on page 80: Changed former  $t_7$  to  $t_6$ ; eliminated old  $t_6$ .

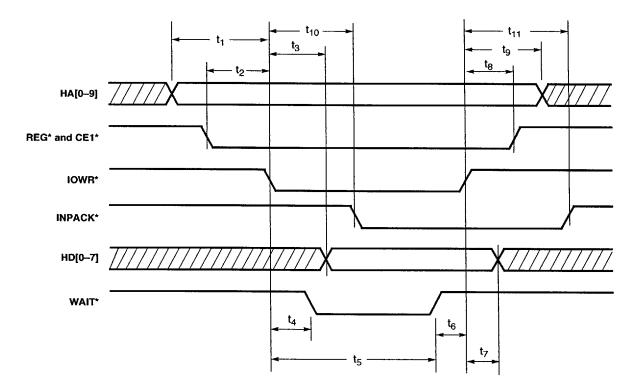

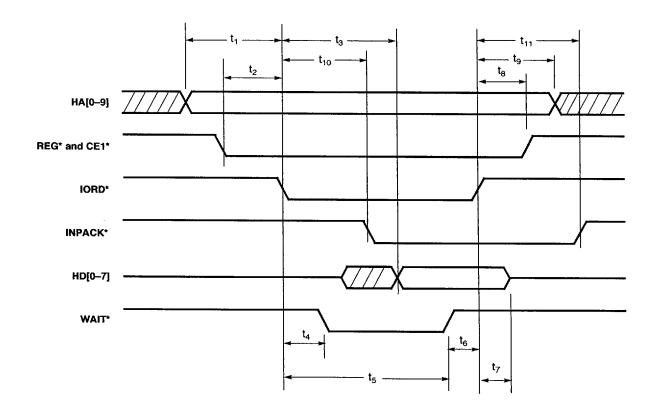

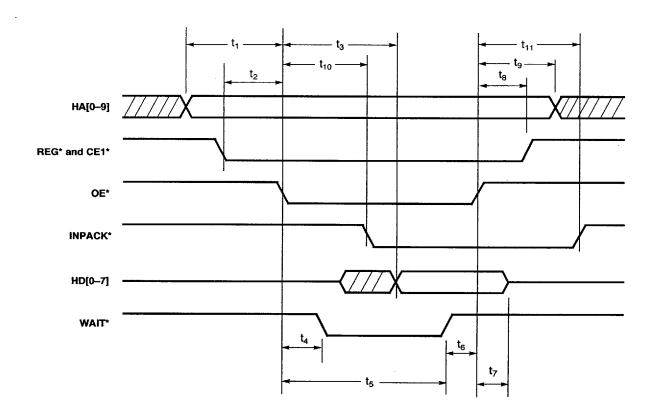

Figure 8-12 on page 90: Added note about WAIT\*.

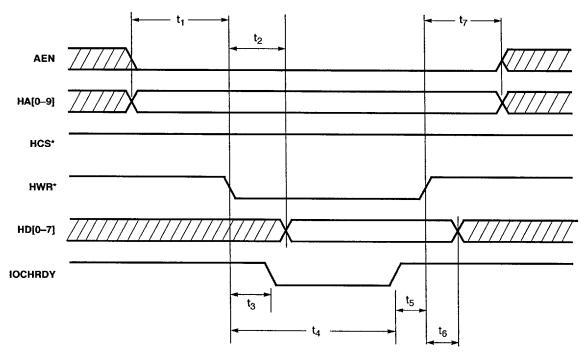

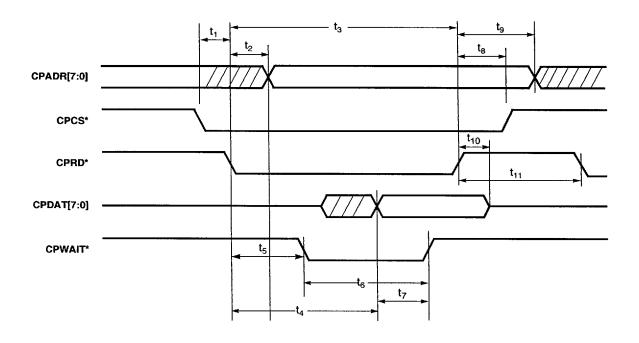

Table 8-18 on page 95: Changed description and values for  $t_2$ .

Table 8-19 on page 97: Changed values for t2.

Table 8-21 on page 99: Changed values for t<sub>3</sub>.

## Chapter 9

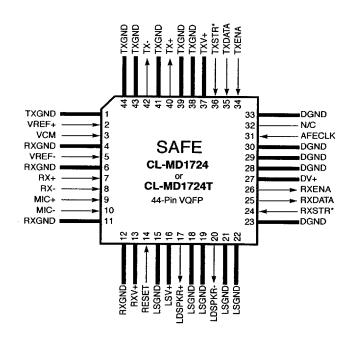

Section 9.3 on page 103: new VQFP 44-pin package.

#### Chapter 10

page 105: Changed the DSP's chip number in the CL-MD3463T chipset to CL-3660DT from CL-3661DT.

## Version 1.0 September 1996

Following are the major changes made since version 0.9:

## Chapters 6 and 7

Renamed all  $\mu P$  and DSP power and ground pins as simply  $V_{CC}$  and GND. Removed individually named pins from the  $\mu P$  and DSP pin descriptions.

Section 7.1.1.3 on page 52: Added power and ground pins for the  $\mu P$ 's parallel/plug-and-play and serial interfaces.

Section 7.1.1.5 on page 55: Added power and ground pins for the  $\mu P$ 's PC Card (PCMCIA) interface.

Section 7.2.5 on page 69: Added power and ground pins for the DSP's SQFP and VQFP packages.

### Version 0.9 August 1996

Following are the major changes made since version 0.8:

## Chapter 5

Table 5-5: Changed range for the **+VNH** command.

Table 5-7: Changed the hex code for the '~' response in the DCE  $\rightarrow$  DTE voice character pairs table.

Table 5-14: Added the -Tn manufacturing command.

#### Chapter 6

Section 6.1.2: Changed pin 97, 'XTC', to 'Reserved'.

## Chapter 7

Table 7-1: Changed serial values for HCS\*/CACK\*, COMSEL[0-1], AEN, and HA[0-9].

Section 7.1.1.1: Changed pin connection information for the parallel/plug-and-play pins HCS\*/CACK\* and TCS\*.

Section 7.1.1.2: Changed the pin connection information for the serial pins HOSTSEL1/CS5\*, HOSTSEL0/CS4\*, reserved pins, and TCS\*.

Section 7.1.1.4: Changed the pin connection information for the PC Card (PCMCIA) pins CS5\*, CS4\*, and TCS\*.

Section 7.1.1.2: Changed the description for pin 97, formerly 'XTC', now 'Reserved.'

4

## **TABLE OF CONTENTS**

|    | REVISIO | N HISTORY                                  | 3        |

|----|---------|--------------------------------------------|----------|

|    | CONVEN  | NTIONS                                     | <u>g</u> |

| 1. | AVAILAE | BLE CHIPSETS                               | 11       |

|    | 1.1     | Functional Block Diagrams                  | 12       |

| 2. | CHIPSE  | T DESCRIPTIONS                             | 15       |

|    | 2.1     | Microprocessor (μP)                        | _        |

|    | 2.2     | Digital Signal Processor (DSP)             |          |

|    |         | Sigma-Delta Analog Front End (SAFE) Device |          |

| 3. |         | OF OPERATION                               |          |

|    | 3.1     | Data Mode                                  |          |

|    | 3.2     | V.42/MNP® 2-4 and V.42 bis/MNP® 5 Modes    | 17       |

|    | 3.3     | Fax Mode                                   |          |

|    | 3.4     | Voice Mode                                 |          |

|    | 3.5     | Radish® VoiceView™ Mode                    | 17       |

|    |         | Digital Simultaneous Voice and Data (DSVD) |          |

|    | 3.7     | Videoconferencing (V.80) Support           | 19       |

|    | 3.8     | Full-Duplex Speakerphone                   | 19       |

|    | 3.9     | Power Management Modes                     | 19       |

|    |         | Loopback Test Modes                        |          |

|    |         | Transmit Levels                            |          |

|    |         | Transmit Tone Levels                       |          |

|    |         | Receive Level                              |          |

|    |         | Receiver Tracking                          |          |

|    |         | Equalizers                                 |          |

|    |         | Call Progress                              |          |

|    |         | Caller ID                                  |          |

|    |         | Firmware Soft Upgrades                     |          |

|    |         | International Support                      |          |

| 4. |         | ARE INTERFACES                             |          |

|    | 4.1     | Host Interfaces                            |          |

|    |         | 4.1.1 Serial RS-232 Interface              |          |

|    |         | 4.1.2 Parallel Bus Interface               |          |

|    |         | 4.1.3 Plug-and-Play Interface              |          |

|    |         | 4.1.4 PC Card Interface                    |          |

|    | 4.2     | Flash Interface                            | . 22     |

|    |         | Expansion Bus Interface                    |          |

|    | 4.4     | NVRAM Interface                            |          |

|    | 4.5     | DAA Interface                              |          |

|    | 4.6     | Speaker Interface                          |          |

|    | 4.7     | Microphone Interface                       |          |

|    | 4.8     | General-Purpose I/O Interface              | . 23     |

## TABLE OF CONTENTS (cont.)

| 5.         | AT COM  | IMAND SET                                                           | 25    |

|------------|---------|---------------------------------------------------------------------|-------|

|            | 5.1     | AT Command Descriptions                                             | 25    |

|            | 5.2     | AT Escape Sequences                                                 | 25    |

| 6.         | PIN DIA | GRAMS                                                               | 41    |

|            |         | Microprocessor (μP) Pin Diagrams (CL-MD4450C)                       |       |

|            |         | 6.1.1 µP Parallel and Plug-and-Play (128-pin SQFP) Pin Diagram      |       |

|            |         | 6.1.2 μP Serial Pin Diagram (128-pin SQFP)                          | 42    |

|            |         | 6.1.3 μP PC Card (PCMCIA) Pin Diagram (128-pin VQFP)                |       |

|            | 6.2     | - g g                                                               |       |

|            |         | 6.2.1 DSP CL-MD3450D/3450DT Pin Diagram (128-pin SQFP)              |       |

|            |         | 6.2.2 DSP PC Card CL-MD3451DT / 3460DT Pin Diagram (128-pin VQFP)   |       |

|            | 6.3     | SAFE Pin Diagram (44-pin VQFP)                                      | 46    |

| <b>7</b> . | PIN DES | SCRIPTIONS                                                          |       |

|            | 7.1     | 1                                                                   | 46    |

|            |         | 7.1.1 µP Host Interface Pin Descriptions                            |       |

|            |         | 7.1.2 µP General Pin Descriptions                                   |       |

|            |         | 7.1.3 µP Expansion Bus Interface Pin Descriptions                   |       |

|            | 7.2     | DSP Pin Descriptions                                                | 65    |

|            |         | 7.2.1 DSP Program Memory Interface Pin Descriptions                 |       |

|            |         | 7.2.2 DSP Control Processor (CP) Interface Pin Descriptions         |       |

|            |         | 7.2.3 DSP Clock/Reset Interface Pin Descriptions                    |       |

|            |         | 7.2.4 DSP-SAFE Interface Pin Descriptions                           |       |

|            | 7.3     | SAFE Pin Descriptions                                               |       |

|            | 7.0     | 7.3.1 SAFE General Pin Descriptions                                 |       |

|            |         | 7.3.2 SAFE Power Supply Pin Descriptions (CL-MD1724 or CL-MD1724T)  |       |

|            |         | 7.3.3 SAFE–DAA Interface Pin Descriptions (CL-MD1724 or CL-MD1724T) |       |

|            |         | 7.3.4 SAFE-DSP Interface Pin Descriptions (CL-MD1724 or CL-MD1724T) |       |

| 8.         | ELECTE  | RICAL SPECIFICATIONS                                                |       |

| •          | 8.1     | DSP 5-V DC Electrical Characteristics                               |       |

|            | 8.2     | DSP 3.3-V DC Electrical Characteristics                             | 74    |

|            | 8.3     | μP 5-V DC Electrical Characteristics                                |       |

|            | 8.4     |                                                                     | 76    |

|            | 8.5     | Index of Timing Information                                         |       |

| 9.         | SAMPLI  | E PACKAGE INFORMATION                                               | 101   |

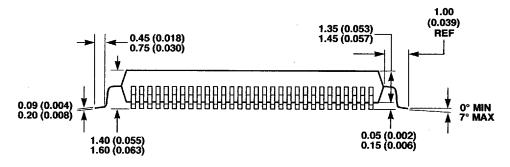

| •          | 9.1     | 128-Pin SQFP Package Outline                                        |       |

| •          |         | 128-Pin VQFP Package Outline                                        |       |

|            |         | 44-Pin VQFP Package Outline                                         |       |

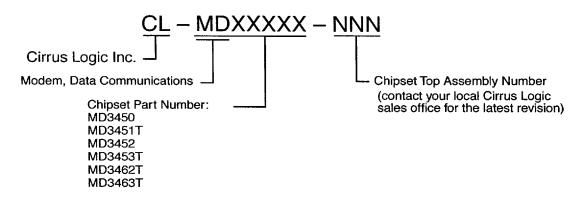

| 10.        |         | ING INFORMATION                                                     |       |

|            |         |                                                                     |       |

| 11.        |         | ID TELEPHONY INTERFACE DESIGN NOTES                                 | _     |

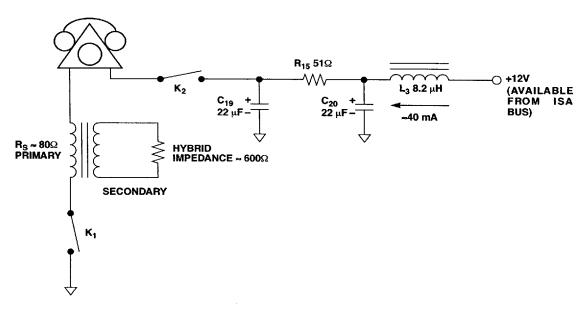

|            | 11.1    | Data Access Arrangement (DAA) Design                                | . 107 |

|            | 44.5    | 11.1.1 General Overview                                             |       |

|            | 11.2    | Pault Protection                                                    | 107   |

|            |         |                                                                     |       |

## TABLE OF CONTENTS (cont.)

| 11.2.1 Metallic Voltage Surge Test                 | 108 |

|----------------------------------------------------|-----|

| 11.2.2 Longitudinal Voltage Surge Test             |     |

|                                                    |     |

| 11.2.3 Leakage Test                                |     |

| 11.3 Radiated- and Conducted-Emissions Suppression |     |

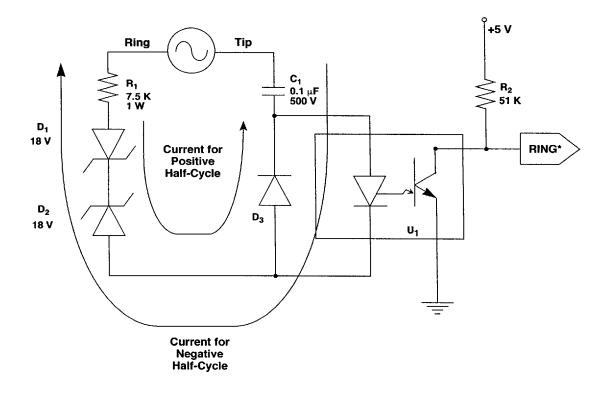

| 11.4 Ring Detection                                | 109 |

| 11.5 Special Features and Functions                | 110 |

| 11.5.1 Caller ID                                   | 110 |

| 11.6 Voice Interface                               |     |

| 11.6.1 Local Phone Voice Interface                 |     |

| 12. V.34+ REFERENCE DESIGNS                        | 117 |

| 12.1 Step 1                                        | 117 |

| 12.2 Step 2                                        |     |

| APPENDIXES                                         | 8   |

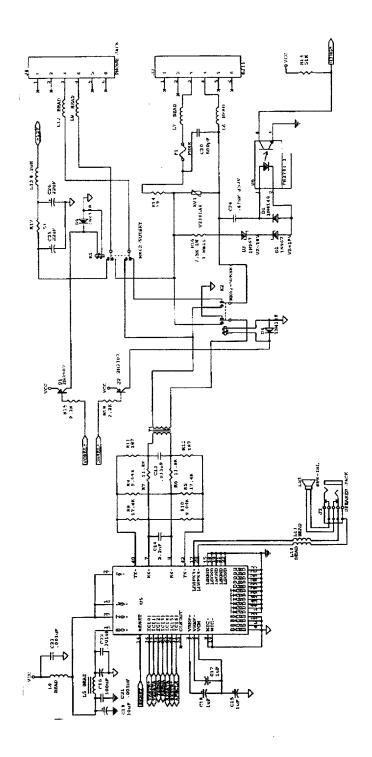

| A. ISA CARD INTERFACE DESIGNS                      | 119 |

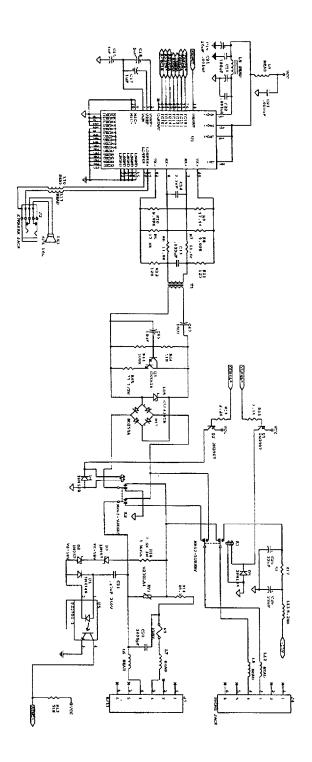

| B. SERIAL CARD INTERFACE DESIGNS                   | 123 |

| C. PC CARD (PCMCIA) INTERFACE DESIGNS              | 127 |

| D. AFE, DAA, AND MIC INTERFACE DESIGNS             | 131 |

## LIST OF TABLES

| Table 3-1.  | Communication Modes and Data Rates 18     | Table 8-7.  | Plug-and-Play Port Accesses —           |

|-------------|-------------------------------------------|-------------|-----------------------------------------|

| Table 3-2.  | Transmit Tones                            |             | Write Cycle81                           |

| Table 3-3.  | DTMF Tone Pairs                           | Table 8-8.  | Plug-and-Play Port Accesses —           |

| Table 4-1.  | Expansion Bus Access Times                |             | Read Cycle82                            |

| Table 4-2.  | Parallel Host Interface UART Register Bit | Table 8-9.  | μP Expansion Bus Timing Diagram —       |

|             | Assignments 24                            |             | Write Cycle83                           |

| Table 5-1.  | Basic Data Modem AT Commands              | Table 8-10. | μP Expansion Bus Timing Diagram —       |

| Table 5-2.  | V.42 / V.42 bis MNP® AT Commands 31       |             | Read Cycle84                            |

| Table 5-3.  | Fax Identity Commands                     | Table 8-11. | μP PC Card UART Interface Timing        |

| Table 5-4.  | Fax Class 1 AT Commands 33                |             | Diagram — Write Cycle85                 |

| Table 5-5.  | IS-101 Voice AT Commands34                | Table 8-12. | μP PC Card UART Interface Timing        |

| Table 5-6.  | Voice DTE→DCE Character Pairs 35          |             | Diagram — Read Cycle86                  |

| Table 5-7.  | Voice DTE←DCE Character Pairs35           | Table 8-13. | μP PC Card Configuration Register       |

| Table 5-8.  | VoiceView™ Commands36                     |             | Interface Timing — Write Cycle88        |

| Table 5-9.  | VoiceView™ Response Codes 37              | Table 8-14. | μP PC Card Configuration Register       |

| Table 5-10. | VoiceView™ <dle> Character Pairs 37</dle> |             | Interface Timing — Read Cycle89         |

| Table 5-11. | Dial Modifiers37                          | Table 8-15. | μP PC Card CIS Access Timing            |

| Table 5-12. | S-Registers Summary 38                    |             | Diagram — Read Cycle91                  |

| Table 5-13. | DTE-Modem Data Rate Response              | Table 8-16. | μP External Memory Access Through       |

|             | Codes                                     |             | Test Register — Write Cycle93           |

| Table 5-14. | Manufacturing-Only Commands 40            | Table 8-17. | μP External Memory Access Through       |

| Table 7-1.  | Pin Requirements for a Given Host         |             | Test Register — Read Cycle94            |

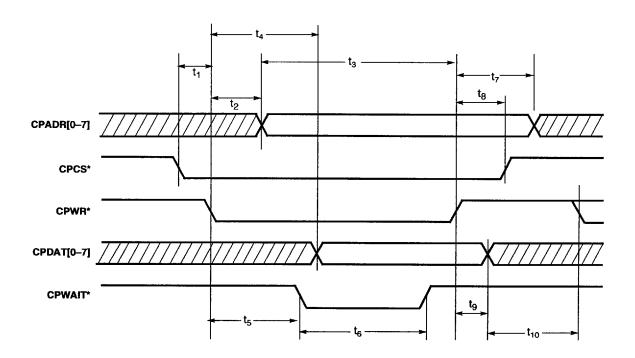

|             | Interface                                 | Table 8-18. | DSP Control Processor Timings —         |

| Table 8-1.  | Absolute Maximum Ratings73                |             | Write Cycle95                           |

| Table 8-2.  | Recommended Operating Conditions 73       | Table 8-19. | DSP Control Processor Timings —         |

| Table 8-3.  | μP Parallel Host Interface-to-UART        |             | Read Cycle                              |

|             | Timing (External Address Decode) —        | Table 8-20. | DSP Expansion Bus Timing Diagram —      |

|             | Write Cycle77                             |             | Write Cycle98                           |

| Table 8-4.  | μP Parallel Host Interface-to-UART        | Table 8-21. | DSP Expansion Bus Timing Diagram —      |

|             | Timing (External Address Decode) —        |             | Read Cycle                              |

|             | Read Cycle78                              | Table 10-1. | Cirrus Logic V.34+ FastPath™ Modem      |

| Table 8-5.  | μP Parallel Host Interface-to-UART        |             | Products                                |

|             | Timing (Internal Address Decode) —        | Table 11-1. | Caller ID Message Transmission Order112 |

|             | Write Cycle                               | Table 12-1. | Interface Schematics                    |

| Table 8-6.  | μP Parallel Host Interface-to-UART        | Table 12-2. | Feature Set Schematics                  |

|             | Timing (Internal Address Decode) —        | Table 12-3. | Feature Sets                            |

|             | Pood Cyale                                | 14010 12-0, | 1 Calare Octo 1 10                      |

## **LIST OF FIGURES**

| Figure 1-1. | CL-MD34XX Family Chipset               | Figure 8-9.     | μP PC Card UART Interface Timing       |       |

|-------------|----------------------------------------|-----------------|----------------------------------------|-------|

|             | Composition1                           | 1               | Diagram - Write Cycle                  | . 85  |

| Figure 1-2. | CL-MD3450 Functional Block Diagram 12  | 2 Figure 8-10.  | μP PC Card UART Interface Timing       |       |

| Figure 1-3. | CL-MD3452 Functional Block Diagram 12  | 2               | Diagram — Read Cycle                   | . 87  |

| Figure 1-4. | CL-MD3462T Functional Block Diagram 13 | B Figure 8-11.  | μP PC Card Configuration Register      |       |

| Figure 1-5. | CL-MD3451T PC Card Functional Block    |                 | Interface Timing Diagram - Write Cycle | . 88  |

|             | Diagram 1                              | 3 Figure 8-12.  | μP PC Card Configuration Register      |       |

| Figure 1-6. | CL-MD3453T / MD3463T PC Card           |                 | Interface Timing Diagram — Read Cycle. | . 90  |

|             | Functional Block Diagram 14            | 4 Figure 8-13.  | μP PC Card CIS Access Timing Diagram   |       |

| Figure 4-1. | Modem System Block Diagram             |                 | Read Cycle                             |       |

|             | (CL-MD3450)2                           | 1 Figure 8-14.  | μP External Memory Access Through      |       |

| Figure 8-1. | μP Parallel Host Interface-to-UART     |                 | Test Register — Write Cycle            | 93    |

|             | Timing (External Address Decode) —     | Figure 8-15.    | μP External Memory Access Through      |       |

|             | Write Cycle7                           | 7               | Test Register — Read Cycle             | 94    |

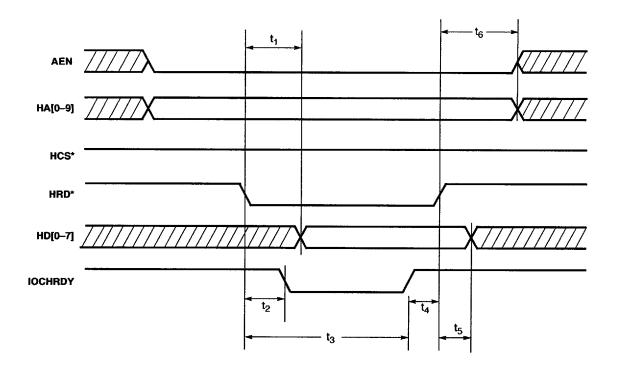

| Figure 8-2. | μP Parallel Host Interface-to-UART     | Figure 8-16.    | DSP Control Processor Timings —        |       |

|             | Timing (External Address Decode) —     |                 | Write Cycle                            | 96    |

|             | Read Cycle7                            | 8 Figure 8-17.  | DSP Control Processor Timings —        |       |

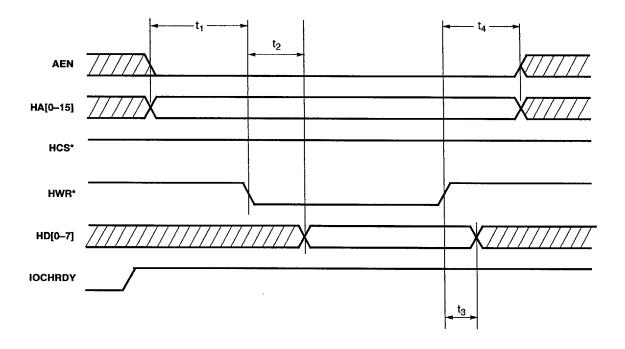

| Figure 8-3. | μP Parallel Host Interface-to-UART     |                 | Read Cycle                             | 97    |

|             | Timing (Internal Address Decode) —     | Figure 8-18.    | DSP Expansion Bus Timing Diagram -     |       |

|             | Write Cycle7                           | 9               | Write Cycle                            | 98    |

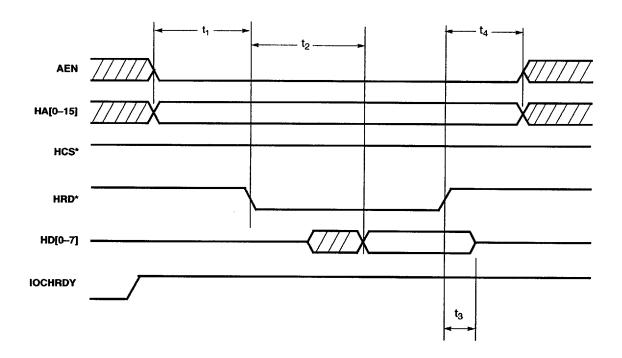

| Figure 8-4. | μP Parallel Host Interface-to-UART     | Figure 8-19.    | DSP Expansion Bus Timing Diagram —     |       |

|             | Timing (Internal Address Decode) —     |                 | Read Cycle                             | 99    |

|             | Read Cycle8                            | 0 Figure 11-1.  | Ring Circuit                           | 109   |

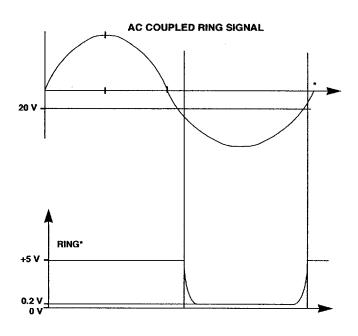

| Figure 8-5. | Plug and Play Port Accesses —          | Figure 11-2.    | AC-Coupled Ring Signal and Ring*       | 110   |

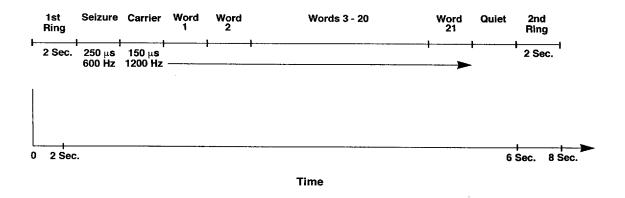

|             | Write Cycle8                           | 11 Figure 11-3. | Caller ID Interface                    | 111   |

| Figure 8-6. | Plug and Play Port Accesses —          | Figure 11-4.    | Caller ID Signal Timing                | 111   |

|             | Read Cycle8                            | 2 Figure 11-5.  | Local Phone in Voice Mode              | 113   |

| Figure 8-7. | μP Expansion Bus Timing Diagram —      | Figure 11-6.    | Complete Local Phone Voice Application |       |

|             | Write Cycle8                           | 33              | 'Wet' DAA                              | . 114 |

| Figure 8-8. | μP Expansion Bus Timing Diagram —      | Figure 11-7.    | Complete Local Phone Voice Application | _     |

|             | Read Cycle8                            | 34              | 'Dry' DAA                              | 115   |

## **CONVENTIONS**

This section lists conventions used in this data book.

## **Abbreviations**

| Symbol         | Units of measure                 |

|----------------|----------------------------------|

| °C             | degree Celsius                   |

| μF             | microfarad                       |

| μs             | microsecond (1,000 nanoseconds)  |

| Hz             | hertz (cycle per second)         |

| K (memory)     | kilobit (1,024 bits)             |

| kbits/second   | kilobit (1,000 bits) per second  |

| kHz            | kilohertz                        |

| kΩ             | kilohm                           |

| Mbyte (memory) | megabyte (1,048,576 bytes)       |

| MHz            | megahertz (1,000 kilohertz)      |

| mA             | milliampere                      |

| ms             | millisecond (1,000 microseconds) |

| ns             | nanosecond                       |

| pV             | picovolt                         |

| V              | volt                             |

| w              | watt                             |

## **Acronyms**

| Acronym | Definition                                                                             |

|---------|----------------------------------------------------------------------------------------|

| AC      | alternating current                                                                    |

| AT      | 'Attention' command prefix for<br>Hayes AT® command set (for exam-<br>ple, 'ATDT 123') |

| CMOS    | complementary metal-oxide semi-<br>conductor                                           |

| DC      | direct current                                                                         |

| DAA     | data access arrangement                                                                |

| DRAM    | dynamic random-access memory                                                           |

| DSVD    | digital simultaneous voice and data                                                    |

| EPROM   | electrically programmable read-only memory                                             |

| FIFO    | first in/first out                                                                     |

| HDLC    | high-level data link control                                                           |

| ISA     | industry-standard architecture                                                         |

| LSB     | least-significant bit                                                                  |

| MSB     | most-significant bit                                                                   |

| NVRAM   | non-volatile random-access memory                                                      |

| RAM     | random-access memory                                                                   |

| ROM     | read-only memory                                                                       |

| R/W     | read/write                                                                             |

| SQFP    | shrink quad flat pack                                                                  |

| SRAM    | static random-access memory                                                            |

| TTL     | transistor-transistor logic                                                            |

| UART    | universal asynchronous receiver transmitter                                            |

| VQFP    | very-tight-pitch quad flat pack                                                        |

10

CONVENTIONS

DATA BOOK v1.1

## 1. AVAILABLE CHIPSETS

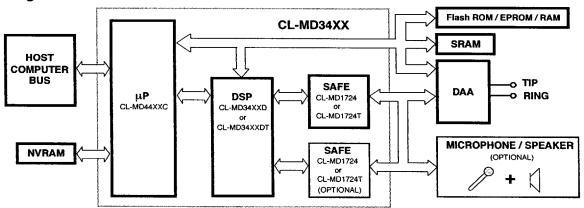

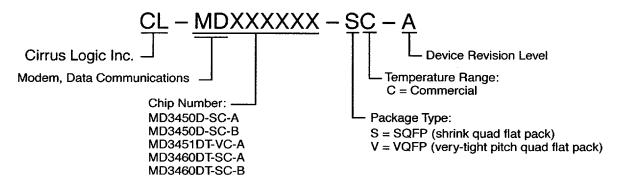

Figure 1-1. CL-MD34XX Family Chipset Composition

## Functional Block Diagrams

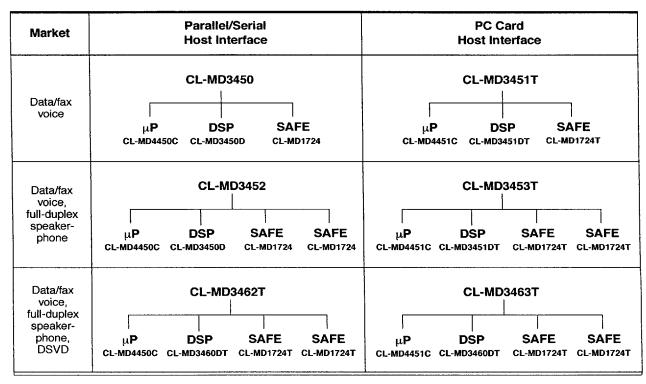

Figure 1-2. CL-MD3450 Functional Block Diagram

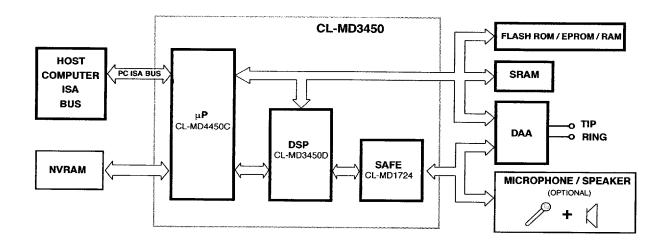

Figure 1-3. CL-MD3452 Functional Block Diagram

February 1997 AVAILABLE CHIPSETS DATA BOOK v1.1

13

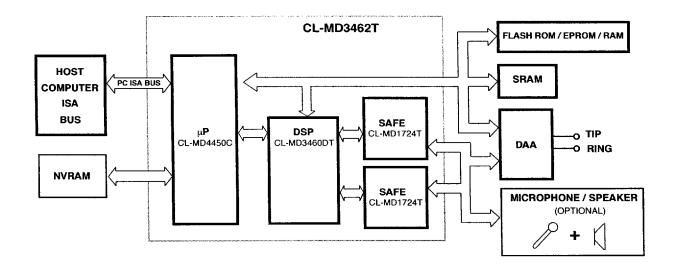

Figure 1-4. CL-MD3462T Functional Block Diagram

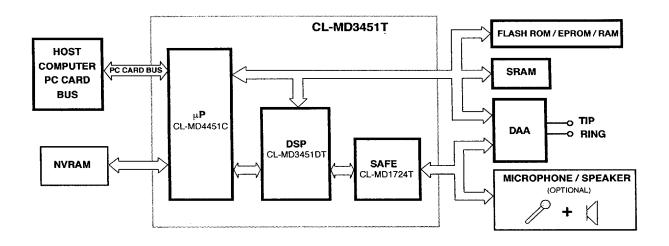

Figure 1-5. CL-MD3451T PC Card Functional Block Diagram

February 1997

DATA BOOK v1.1

AVAILABLE CHIPSETS

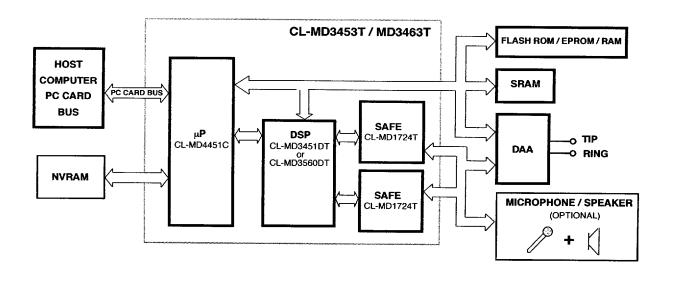

Figure 1-6. CL-MD3453T / MD3463T PC Card Functional Block Diagram

AVAILABLE CHIPSETS

DATA BOOK v1.1

## 2. CHIPSET DESCRIPTIONS

The V.34+ FastPath™ family is a three- or four-chip solution consisting of a µP (microprocessor), a DSP (digital signal processor), and one or two SAFE (sigma-delta analog front end) devices. These products (also known as smart modems) support a variety of applications and need no additional firmware development. Currently, there are six V.34+ chipset solutions. These are shown in Figure 1-1 on page 11 with their corresponding µP, DSP, and SAFE device part numbers.

## 2.1 Microprocessor (µP)

Each chipset contains a  $\mu P$  specifically designed for modem applications. The  $\mu P$  implements all AT commands and manages all modem relays and the transmission and reception of data. The  $\mu P$  interfaces with the DTE and DSP. The  $\mu P$ 's firmware contains code for all controller functions for Group 3 Fax mode, Data mode (without error correction or data compression), and Voice mode.

## 2.2 Digital Signal Processor (DSP)

The DSP performs all digital signal processing functions for the chipset, including modulation, echo cancellation, call progress monitoring, voice processing, and compression of voice and video signals.

The DSP offers two power options, depending on the chipset ordered. All PC Card (PCMCIA) chipsets use 3.3-V power. Initial production ISA-and serial-interface chipsets are 5 V only, but the DSP will be converted to a 3.3-V version to take advantage of the latest manufacturing technologies. Therefore, all board designs should include a 3.3-V regulator option (see schematics for details). The 3.3-V DSP not only reduces power consumption, it also enables the concurrent operation of speakerphone and DSVD using a single DSP.

# 2.3 Sigma-Delta Analog Front End (SAFE) Device

The SAFE device uses sigma-delta techniques to convert analog information from a telephone line to digital information that can be processed by the DSP. In addition to its analog circuitry, the modem's sigma-delta function incorporates unique and proprietary digital-to-analog and analog-to-digital features. These features improve receiver accuracy, which in turn improves performance at low levels of receive signal. Compared to other analog frontend technologies, the sigma-delta implementation better stabilizes the function of the SAFE devices and makes them less sensitive to board layout than other analog front end technologies. Since a significant amount of signal processing is performed by digital rather than analog techniques, sigma-delta analog-to-digital conversion considerably improves signal quality.

For basic Data, Fax, and Voice modes of operation, a single SAFE device is needed. To support DSVD or full-duplex speakerphone with echo cancellation, a second SAFE device is required.

**Notes**

PAGE(S) INTENTIONALLY BLANK

16

CHIPSET DESCRIPTIONS

DATA BOOK v1.1

## 3. MODES OF OPERATION

The CL-MD34XX family provides complete modem functions for the following modes: Group 3 Fax, Data, Voice, V.42/MNP 2-4, and V.42 bis/MNP 5 (Microcom Networking Protocol Class 5). Each mode has its own unique AT command set. The data rates and modulation schemes for Data and Fax modes are presented in Table 3-1 on page 18. Additionally, these modem chipsets provide special modes of operation for VoiceView, power management, and loopback testing.

#### 3.1 Data Mode

In the Data mode, the FastPath chipsets operate at up to 33.6 kbps. They implement all data rates and modulation schemes for ITU-T standards V.34, V.32 bis, V.32, V.22 bis, V.22, V.21, Bell 212A, and Bell 103. The V.34+ family implements a standard Data mode AT command set. This is compatible with any communication application software that supports the Hayes<sup>®</sup> AT command set. The standard AT commands for Data mode are listed in Table 5-1 on page 26.

# 3.2 V.42/MNP® 2-4 and V.42 bis/MNP® 5 Modes

The FastPath family supports error correction (V.42/MNP 2-4) and data compression (V.42 bis/MNP 5). Error correction ensures error-free data transfer. Data compression substantially increases the modem data throughput over the basic data rate throughput. Depending on the data stream, MNP 5 may provide up to two-to-one compression. Alternately, ITU-T V.42 bis may provide up to four-to-one compression. A description of the AT commands that support error correction and data compression are provided in Table 5-2 on page 31.

#### 3.3 Fax Mode

In Fax mode, the FastPath chipsets operate at up to 14.4 kbps (transmit and receive) and implement all the data rates and modulation schemes for ITU-T standards V.17, V.29, V.27 ter, and V.21 ch2. The chipsets implement a standard Fax mode AT

command set compatible with any communication application software that supports EIA/TIA-578 Fax Class 1 standards. The standard AT commands for Fax mode are listed in Table 5-3 and Table 5-4 on page 33.

## 3.4 Voice Mode

All chipsets support Telephone-Emulation mode, IS-101 voice commands, and record and playback message capabilities. Telephone-Emulation mode allows a handset/microphone-speaker and modem to be used as a complete telephone. In Telephone-Emulation mode, the received data from the SAFE (CL-MD1724 or CL-MD1724T) microphone interface is looped back to the SAFE analog transmit pins. In Voice mode, the message record and playback abilities are accessed by the extended AT command set, shown in Table 5-5 on page 34 through Table 5-7 on page 35.

# 3.5 Radish<sup>®</sup> VoiceView™ Mode

The V.34+ family gives the option to upgrade to Radish VoiceView, a widely supported protocol that alternates between voice and data. VoiceView enables data transfer during a regular telephone connection. It can be used in a variety of applications, such as customer service and technical support.

# 3.6 Digital Simultaneous Voice and Data (DSVD)

Each CL-MD3462 and CL-MD3463 chipset contains an embedded G.729A vocoder that supports digital simultaneous voice and data (DSVD), which allows data to be transferred realtime during a voice conversation. DSVD can be used for interactive applications such as whiteboard conferencing or real-time action games. DSVD is transparent to the application software. Enable DSVD by changing the program modem initialization string to include the DSVD AT command.

Table 3-1. Communication Modes and Data Rates

| Application | Mode             | Data Rate<br>(kbps)                                                                                      | Modulation                              | Baud Rate (symbols/sec.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Carrier Frequency (Hz)<br>(originate/answer)                                                                                                                                                                                                                                                             | Constellation Points                                                                                                                                                                                                        |

|-------------|------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fax         | V.17             | 14.4<br>12.0<br>9.6<br>7.2                                                                               | TCM<br>TCM<br>TCM<br>TCM                | 2400<br>2400<br>2400<br>2400                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1800<br>1800<br>1800<br>1800                                                                                                                                                                                                                                                                             | 128<br>64<br>32<br>16                                                                                                                                                                                                       |

|             | V.29             | 9.6<br>7.2<br>4.8                                                                                        | QAM<br>QAM<br>QAM                       | 2400<br>2400<br>2400<br>2400                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1700<br>1700<br>1700                                                                                                                                                                                                                                                                                     | 16<br>8<br>4                                                                                                                                                                                                                |

|             | V.27 ter         | 4.8<br>2.4                                                                                               | DPSK<br>DPSK                            | 1600<br>1200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1800<br>1800                                                                                                                                                                                                                                                                                             | 8 4                                                                                                                                                                                                                         |

|             | V.21             | 0.3                                                                                                      | FSK                                     | 300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1650 M/1850 S                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                           |

| Data        | V.34<br>V.32 bis | 33.6<br>31.2<br>28.8<br>26.4<br>24.0<br>21.6<br>19.2<br>16.8<br>14.4<br>12.0<br>9.6<br>7.2<br>4.8<br>2.4 | TCM | Variable <sup>a</sup> | Variable <sup>b</sup> Variable b | Variable c |

|             |                  | 9.6<br>7.2<br>4.8                                                                                        | TCM<br>TCM<br>TCM                       | 2400<br>2400<br>2400                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1800<br>1800<br>1800                                                                                                                                                                                                                                                                                     | 32<br>16<br>4                                                                                                                                                                                                               |

|             | V.32             | 9.6<br>9.6<br>4.8                                                                                        | TCM<br>QAM<br>QAM                       | 2400<br>2400<br>2400                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1800<br>1800<br>1800                                                                                                                                                                                                                                                                                     | 32<br>16<br>4                                                                                                                                                                                                               |

|             | V.22 bis         | 2.4                                                                                                      | QAM                                     | 600                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1200/2400                                                                                                                                                                                                                                                                                                | 16                                                                                                                                                                                                                          |

|             | V.22             | 1.2                                                                                                      | DPSK                                    | 600                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1200/2400                                                                                                                                                                                                                                                                                                | 4                                                                                                                                                                                                                           |

|             | V.21             | 0.3                                                                                                      | FSK                                     | 300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 980 M/1650 M<br>1180 S/1850 S                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                           |

|             | Bell 212A        | 1.2                                                                                                      | DPSK                                    | 600                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1200/2400                                                                                                                                                                                                                                                                                                | 4                                                                                                                                                                                                                           |

|             | Bell 103         | 0.3                                                                                                      | FSK                                     | 300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1270 M/2225 M<br>1070 S/2025 S                                                                                                                                                                                                                                                                           | 1                                                                                                                                                                                                                           |

<sup>&</sup>lt;sup>a</sup> Cirrus Logic supports five of the six baud rates specified by the ITU-T (International Telecommunications Union-Telecommunications): 2400, 2743, 3000, 3200, and 3429 symbols/second. The ITU-T's optional baud rate of 2800 symbols/second is not supported.

<sup>&</sup>lt;sup>b</sup> The high and low carrier frequencies specified by ITU-T are supported for each baud rate.

<sup>&</sup>lt;sup>c</sup> Cirrus Logic supports the normal and expanded constellations for each baud and data rate.

## 3.7 Videoconferencing (V.80) Support

All versions of the CL-MD34XX chipset family support the ITU-V.80 recommendation. This feature ensures compatibility with host-based H.324 videoconferencing application software. The CL-MD34XX family supports both transparent and framed submodes of the V.80 synchronous access mode.

## 3.8 Full-Duplex Speakerphone

The V.34+ FastPath family supports full-duplex speakerphone with internal adaptive echo cancellation. Phone users can talk simultaneously without the remote user hearing an echo. This speakerphone feature also is supported by DSVD.

## 3.9 Power Management Modes

The CL-MD34XX family provides both Sleep and Stop modes to reduce power consumption when the modem is inactive. Stop mode turns off all modem power except for the circuitry needed to maintain the host interface signals at the appropriate high-impedance state. To enter Stop mode, the host asserts the  $\mu P$  stop pin. When the stop pin is deasserted, the modem exits Stop mode, performs an internal reset, and enters Power-on mode. After the modem internal reset, the DTE reconfigures the modem.

Power-on mode consists of an Operational mode and a Sleep (or power-down) mode. In Operational mode, the modem chipset is fully powered and is either communicating with the host and/or another modem or is performing internal processing. In Sleep mode, power is turned off to most of the internal circuitry of the  $\mu P$ , DSP, and SAFE. Sleep mode is controlled by S-register S33. When enabled, the  $\mu P$  enters Sleep or Power-down mode whenever the modem has been inactive for a user-programmable time delay.

The modem is considered to be in an inactive state when:

- 1) No internal processing is being performed;

- No activity occurs between the host and the modem within a specified time period (S-register S33);

- 3) The modern is on-hook.

The modem exits Sleep mode whenever the host writes to the modem or when a ring signal is detected. The modem does not wake up when the host reads the UART registers.

See Section 8.3 on page 75 for the  $\mu P$ 's DC electrical characteristics.

## 3.10 Loopback Test Modes

Testing with local analog loopback, local analog loopback with self-test, remote digital loopback, and remote digital loopback with self-test are provided for testing modem-to-modem and modem-to-DTE communication integrity. These tests are accessed through the AT&Tn command and are explained in more detail in the CL-MD34XX Programmer's Guide.

#### 3.11 Transmit Levels

The factory default transmit level is -10 dBm  $\pm$  1 dB at Tip and Ring. Data and fax use separate transmission levels. The transmit level can be programmed using the firmware configuration utility.

#### 3.12 Transmit Tone Levels

The modem generates DTMF, answer, call, and guard tones. The specification for each tone is provided in Table 3-2 and Table 3-3 on page 20. DTMF tones are transmitted at -6 dBm for Tone 1 and -4 dBm for Tone 2. The transmit level can be programmed using the firmware configuration utility.

### 3.13 Receive Level

The receiver can accommodate a receive signal from -9 dBm to -43 dBm. The DCD (data carrier detect) function is activated at -43 dBm and above; it is deactivated at -48 dBm and below.

## 3.14 Receiver Tracking

The receiver compensates for up to  $\pm 7$  Hz of carrier-frequency offset.

## 3.15 Equalizers

Automatic adaptive and compromise equalizers are provided to compensate for line distortions.

## 3.16 Call Progress

The modem monitors the detection of callprogress tones during call origination and reports them to the DTE. Call-progress tones include dial, busy, ringback, and answer.

## 3.17 Caller ID

Caller ID is a service that allows the user to see the caller's telephone number. Caller ID also provides information on call date and time. For more information about this service, refer to Appendix A of the CL-MD34XX Programmer's Guide.

## 3.18 Firmware Soft Upgrades

CL-MD34XX chipsets that are Flash memorybased can be upgraded via communication software. See the Firmware Downloading Instructions in the CL-MD34XX-XX Applications Book for more information.

## 3.19 International Support

The FastPath chipsets support international applications. To obtain the settings for a particular country, download new modem specifications from the Cirrus Logic BBS and modify the firmware using the international configuration utility supplied by Cirrus Logic. For information on specific countries, contact your local Cirrus Logic sales office at the address listed on the back cover of this document.

Table 3-2. Transmit Tones

| Tone         | Value   | Application      |  |

|--------------|---------|------------------|--|

| Calling tone | 1100 Hz | Fax originator   |  |

| Calling tone | 1300 Hz | Data originator  |  |

| Answer tone  | 2100 Hz | Data/fax (ITU-T) |  |

| Answer tone  | 2225 Hz | Data (Bell mode) |  |

| Guard tone   | 1800 Hz | Data/fax         |  |

| Guard tone   | 550 Hz  | (answer mode)    |  |

Table 3-3. DTMF Tone Pairs

| Dial<br>Digit | Tone 1<br>(Hz) | Tone 2<br>(Hz) |

|---------------|----------------|----------------|

| 0             | 941            | 1336           |

| 1             | 697            | 1209           |

| 2             | 697            | 1336           |

| 3             | 697            | 1447           |

| 4             | 770            | 1209           |

| 5             | 770            | 1336           |

| 6             | 770            | 1477           |

| 7             | 852            | 1209           |

| 8             | 852            | 1336           |

| 9             | 852            | 1447           |

| *             | 941            | 1209           |

| #             | 941            | 1447           |

| А             | 697            | 1633           |

| В             | 770            | 1633           |

| С             | 852            | 1633           |

| D             | 941            | 1633           |

## 4. HARDWARE INTERFACES

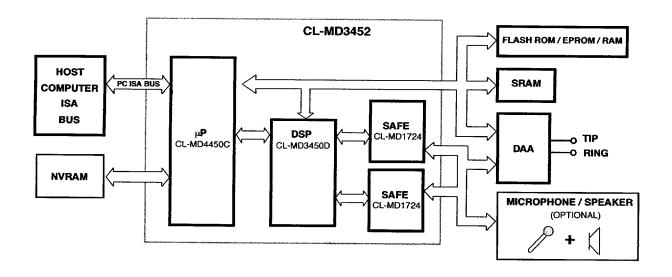

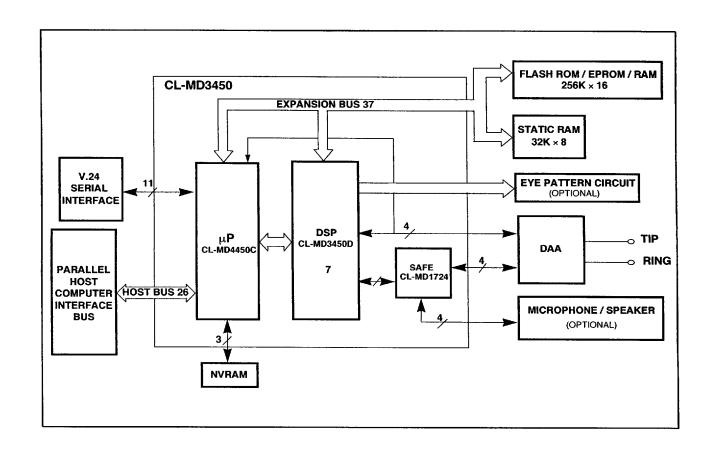

The V.34+ FastPath chipsets support hardware interfaces for the host, Flash memory, expansion bus, NVRAM, DAA, speaker, microphone, and general-purpose I/O functions. The hardware interfaces are demonstrated in Figure 4-1, the CL-MD3450 system block diagram.

### 4.1 Host Interfaces

Some chipsets can support either a parallel or a serial host interface. The interface type is selected by connecting the  $\mu P$  HOSTSEL0/CS4\* and HOSTSEL1/CS5\* pins to  $V_{CC}$  or ground through a resistor. Other chipsets support PC Card host interfaces.

#### 4.1.1 Serial RS-232 Interface

The serial interface that supports TTL levels is compatible with an RS-232 interface.

Figure 4-1. Modem System Block Diagram (CL-MD3450)

February 1997

DATA BOOK v1.1

**HARDWARE INTERFACES**

## 4.1.2 Parallel Bus Interface

The parallel interface emulates the electrical and register functions of 16C550A and 16C450 UARTs. Upon modem reset, the UART interface defaults to a 16C450 UART. The DTE can then configure the UART to function as a 16C550A UART. Table 4-2 on page 24 shows the UART register bit assignments.

The parallel UART interface can be selected to internally decode the addresses for COM ports 1 through 4 using the COMSEL0 and COMSEL1 settings. For applications not using COM ports 1 through 4, the standard method of selecting the modem with external address decoding also is provided. The type of address decoding is selected by either asserting or deasserting the signal at the  $\mu P$  HOSTSEL0 and HOSTSEL1 hardware pins.

The parallel UART also provides an internal tristate bus interface that eliminates the need for external bus drivers between the host bus and the modem UART. These features eliminate the need for a 74HCT245 and a 74HCT30 device, and they facilitate system designs with lower chip counts, power requirements, and costs.

## 4.1.3 Plug-and-Play Interface

Additionally, the chipsets support a parallel plugand-play host interface. The chipset allows an OEM to design one board to support both plugand-play and non-plug-and-play PC bus applications. The additional plug-and-play pin requirements are described in Section 7.1.1 on page 46 of this document.

### 4.1.4 PC Card Interface

The CL-MD34XX family integrates a PC Card host interface that allows the modem to be connected directly to a PC Card bus without additional hardware. This host interface also provides a 16C450/16C550 register-compatible UART. Upon modem reset, the UART interface defaults to a 16C450 emulation. The DTE can then configure the UART to function as a 16C550A. Table 4-2 on page 24 shows the UART register bit assignments.

A built-in CIS (card information structure) eliminates the need for an external CIS ROM. The CIS contents are stored in the external  $\mu P$  microcontroller memory (such as Flash ROM or EPROM).

To customize the modem design, the factory default CIS may be overridden by changing the microcontroller firmware CIS contents using the modem's configuration utility program.

### 4.2 Flash Interface

A Flash interface allows OEMs and end users to quickly and easily download new features as they become available. The FastPath chipsets' Flash interface works with the parallel and PC Card host interfaces and allows the microcontroller firmware code to be downloaded from a PC to the modem Flash ROM or RAM. When firmware is downloaded, it goes through the UART interface, thus eliminating the need for the additional address space and extra hardware required by competing designs.

## 4.3 Expansion Bus Interface

An expansion bus provides access to external memory and circuitry. The expansion bus is used for the  $\mu P$  microcontroller firmware and SRAM. The  $\mu P$ 's firmware bus access time is 70 ns for the  $\mu P$ 's Flash ROM, RAM, or EPROM (see Table 4-1). For standard products, this memory device can be 128K × 16 bits or 256K × 8 bits. Additional memory may be required for special applications.

A 32K × 8 bit, 25-ns SRAM is required for all CL-MD34XX-based modems. The SRAM is used to buffer data during data, voice, DSVD, fax, and V.42/MNP modes of operation.

Table 4-1. Expansion Bus Access Times

| Memory                      | Access Times |  |  |

|-----------------------------|--------------|--|--|

| EPROM Flash 128 K x 16 bits | 150 ns       |  |  |

| EPROM Flash 256 K × 8 bits  | 70 ns        |  |  |

| SRAM 32 K × 8 bits          | 25 ns        |  |  |

### 4.4 NVRAM Interface

A serial interface is provided for a 2 K bit (x 8 configuration) non-volatile RAM (NVRAM). An NVRAM may be used for storing modem configurations and telephone numbers. Plug-and-play designs require NVRAM for the board's serial number information.

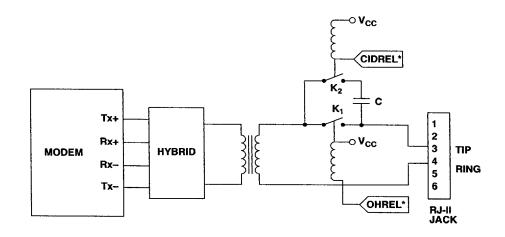

### 4.5 DAA Interface

A DAA (Data Access Arrangement) is the interface between the modem chipset and the telephone network. The DAA interface controls the telephone line off-hook relays, detects ring signals, and transmits and receives analog signals.

## 4.6 Speaker Interface

The SAFE device internally implements both the volume control and amplifier necessary to drive an external speaker. The output of the internal amplifier can be connected directly to a speaker or to the input of the host speaker amplifier. The internal amplifier is capable of driving a minimum load of 8  $\Omega$  up to a maximum load of 100  $\Omega$ . The speaker volume is controlled by the **ATLn** command.

## 4.7 Microphone Interface

The CL-MD1724or CL-MD1724T SAFE device provides a microphone interface that connects a microphone or handset to the modem with a minimum of external parts. This microphone input can then be used for local Voice record mode or for Telephone-Emulation mode.

## 4.8 General-Purpose I/O Interface

To customize the modem design, the  $\mu P$  provides 24 general-purpose pins that can be used to control or monitor external circuitry.

Some of the general-purpose pins can be configured for specific functions (such as a Caller ID relay, CIDREL\*). Pin functions can be selected using the µP firmware's configuration utility program. Some Voice mode functions are enhanced by adding external circuitry for remote hang-up detection, extension phone pickup, or hang-up detection (see Table 5-7, "Voice DTE←DCE Character Pairs", on page 35).

Table 4-2. Parallel Host Interface UART Register Bit Assignments

| REGISTER    | REGISTER<br>NAME                                          | REGISTER BIT NUMBER                         |                                              |                                                       |                                   |                                                  |                                                           |                                                                 | · · · · · · · · · · · · · · · · · · ·                   |

|-------------|-----------------------------------------------------------|---------------------------------------------|----------------------------------------------|-------------------------------------------------------|-----------------------------------|--------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------|

| ADDRESS     |                                                           | 7                                           | 6                                            | 5                                                     | 4                                 | 3                                                | 2                                                         | 1                                                               | 0                                                       |

| 7           | Scratch<br>Register<br>(SCR)                              |                                             | Scratch Register (SCR)                       |                                                       |                                   |                                                  |                                                           |                                                                 |                                                         |

| 6           | Modem<br>Status<br>Register<br>(MSR)                      | Data<br>Carrier<br>Detect<br>(DCD)          | Ring<br>Indicator<br>(RI)                    | Data<br>Set<br>Ready<br>(DSR)                         | Clear<br>to<br>Send<br>(CTS)      | Delta Data Carrier Detect (DDCDD)                | Trailing<br>Edge of<br>Ring<br>Indicator<br>(TERI)        | Delta<br>Data<br>Set<br>Ready<br>(DDSR)                         | Delta<br>Clear<br>to<br>Send<br>(DCTS)                  |

| 5           | Line<br>Status<br>Register<br>(LSR)                       | Error in<br>RCVR<br>FIFO<br>(Note 1)        | Transmitter<br>Empty<br>(TEMT)               | Transmitter<br>Holding<br>Register<br>Empty<br>(THRE) | Break<br>Interrupt<br>(BI)        | Framing<br>Error<br>(FE)                         | Parity<br>Error<br>(PE)                                   | Overrun<br>Error<br>(OE)                                        | Data<br>Ready<br>(DR)                                   |

| 4           | Modem<br>Control<br>Register<br>(MCR)                     | 0                                           | 0                                            | 0                                                     | Loop                              | Out 2                                            | Out 1                                                     | Request<br>to<br>Send<br>(RTS)                                  | Data<br>Terminal<br>Ready<br>(DTR)                      |

| 3           | Line<br>Control<br>Register<br>(LCR)                      | Divisor<br>Latch<br>Access<br>Bit<br>(DLAB) | Set<br>Break<br>(SBRK)                       | Stick<br>Parity<br>(SPAR)                             | Even<br>Parity<br>Select<br>(EPS) | Parity<br>Enable<br>(PEN)                        | Number<br>of<br>Stop Bits<br>(STB)                        | Word<br>Length<br>Select<br>Bit 1<br>(WLS1)                     | Word<br>Length<br>Select<br>Bit 0<br>(WLS0)             |

| 2           | FIFO<br>Control<br>Register<br>[Write only]<br>(FCR)      | RCVR<br>Trigger<br>(MSB)                    | RCVR<br>Trigger<br>(LSB)                     | Reserved                                              | Reserved                          | Reserved                                         | XMIT<br>FIFO<br>Reset<br>(XFIFOR)                         | RCVR<br>FIFO<br>Reset<br>(RFIFOR)                               | FIFO<br>Enable<br>(FIFOE)                               |

| 2           | Interrupt<br>Identity<br>Register<br>[Read only]<br>(IIR) | FIFOs<br>Enabled<br>(See note)              | FIFOs<br>Enabled<br>(See note)               | 0                                                     | O                                 | Interrupt<br>ID<br>Bit 2<br>(See note )          | Interrupt<br>ID<br>Bit 1                                  | Interrupt<br>ID<br>Bit 0                                        | '0' if<br>Interrupt<br>pending                          |

| 1<br>DLAB=0 | Interrupt<br>Enable<br>Register<br>(IER)                  | 0                                           | 0                                            | o                                                     | 0                                 | Modem<br>Status<br>Interrupt<br>Enable<br>(MSIE) | Receiver<br>Line Status<br>Interrupt<br>Enable<br>(RLSIE) | Transmitter<br>Holding Reg.<br>Empty<br>Int. Enable<br>(THREIE) | Received<br>Data<br>Available<br>Int. Enable<br>(RDAIE) |

| 0<br>DLAB=0 | Transmit<br>Holding<br>Register<br>[Write only]<br>(THR)  |                                             | Transmit Holding Register (THR) [Write only] |                                                       |                                   |                                                  |                                                           |                                                                 |                                                         |

| 0<br>DLAB=0 | Receiver<br>Buffer<br>Register<br>[Read only]<br>(RBR)    |                                             | Receiver Buffer Register (RBR) [Read only]   |                                                       |                                   |                                                  |                                                           |                                                                 |                                                         |

| 1<br>DLAB=1 | Divisor<br>Latch<br>(MS)<br>(DLM)                         | Divisor Latch (MS)                          |                                              |                                                       |                                   |                                                  |                                                           |                                                                 |                                                         |

| 0<br>DLAB=1 | Divisor<br>Latch<br>(LS)<br>(DLL)                         |                                             |                                              | Į.                                                    | Divisor Latch (LS                 | 3)                                               |                                                           |                                                                 |                                                         |

NOTE: These bits are always '0' in 16C450 mode.

24 HARDW

HARDWARE INTERFACES

DATA BOOK v1.1

## 5. AT COMMAND SET

## 5.1 AT Command Descriptions

The FastPath chipsets' AT command set and S-registers are divided into four categories: Group 3 fax, data, V.42/MNP, and voice. Summaries of all commands are provided in Table 5-1 on page 26 through Table 5-14 on page 40, while Table 5-12 on page 38 provides a summary of all S-registers.

All command lines sent to the modem, except for A/, must be preceded by an 'AT' and terminated by the contents of S-register S3 (typically a carriage return <CR>). AT stands for 'attention' and prompts the modem to receive a command line from the DTE. A <CR> informs the modem that the entire command string has been transmitted and that the modem should begin processing all the commands in the command line. A command line may include one or more AT commands. The commands may be separated by a space, if desired, but no punctuation is needed except for fax and voice commands. In a multiple-command line, fax and voice AT commands must be separated from following commands by a semicolon (;).

Examples:

ATS1?<CR>

A/

AT &F &D2 +FCLASS=?<CR>

AT +FCLASS=80; S0=1<CR>

The modem provides status information to the DTE in the form of response codes. The supported response codes are listed in Table 5-13 on page 39.

After sending an AT command string to the modem, the DTE must wait for a response code from the modem before sending a new AT command string to the modem.

## 5.2 AT Escape Sequences

The CL-MD34XX provides two industry-standard escape sequences: the Hayes<sup>®</sup> Escape Sequence and the Time Independent Escape Sequence (TIES).

Currently, most modems implement the Hayes Escape Sequence; but because licensing may be required, the V.34+ chipsets include TIES as an alternative. TIES is designed to work with existing communication software written for the Hayes Escape Sequence.

## TIES/Hayes® Escape Sequences

The Cirrus Logic CL-MD34XX modem chipset is manufactured with TIES (Time Independent Escape Sequence) as the default setting. It is Hayes' position that you must have a valid license from Hayes Micro Computer of Norcross, Georgia, before producing modem systems that use the Hayes Escape Sequence.