#### **FEATURES**

#### Microcontroller Interface

- Supports high-speed processors (e.g., 16-MHz 8051, 16-MHz 68HC11)

- Supports multiplexed/non-multiplexed address and data bus

- Supports interrupt- or polled-processor interface

- Provides microcontroller access to six external switch settings

- Four-level power-down capability when idle, automatic power-up when command is received

- Supports host- and disk-interrupt pins

#### Formatter Interface

- Supports NRZ disk data rates up to 32 Mbits/ second

- Works with all disk encoding schemes

- Diskinterfaces supported include ST506/412, ESDI and SMD

- Supports non-interleaved operations

- User-modifiable RAM-based disk formatter control store (31 x 4 bytes)

- Multiple WCS branch and WCS data field branch capability

- Variable split data field support for constant-density-recording formats

- Full-track multi-sector transfer capability with no microcontroller intervention (cont.)

# High-Performance PC XT/AT Disk Controller

#### **OVERVIEW**

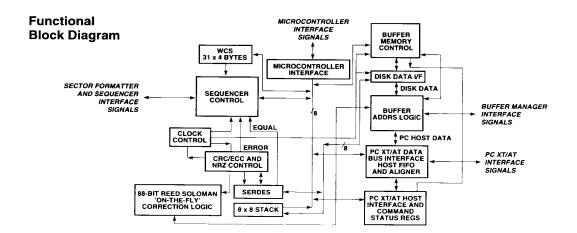

The CL-SH360 is a VLSI component that provides the majority of the hardware necessary to build a PC Winchester disk controller. It is typically configured with buffer memory and a microcontroller — with system RAM and ROM — to create a complete intelligent PC Winchester disk controller. The device combines an advanced Winchester disk formatter, a dual-port buffer memory manager, and extensive hardware support, including direct bus connection with 24-mA drivers.

A static RAM (SRAM) buffer is controlled by the CL-SH360 memory manager. It supports disk data rates up to 32 Mbits/second, and simultaneously provides the handshake for PC-bus-programmed I/O or DMA data transfer at rates up to 4 Mwords/second. (cont.)

#### FEATURES (cont.)

#### Formatter Interface (cont.)

- Scheduled WCS access

- User-programmable sector length up to a full track

- 16-bit CRC and 88-bit ECC polynomial with 'onthe-fly' hardware correction circuitry

- Flexible sector-level defect handling

- Buffer-derived ID field during format

- Two index timeout circuit for sector searches

- Programmable read synchronization timeout

#### Buffer Manager

- Dual-port circular buffer control with access priority resolver

- Direct-buffer addressing up to 64K bytes of static RAM

- Fixed and variable buffer segmentation support

- Scheduled microcontroller write/read to/from buffer

- Supports internal division of buffer clock by one, two, three and four for ease of implementation

- Supports buffer memory throughput to 12 Mbytes/ second

- Provides host overrun control

- Dual-buffer-chip enables for 64K buffers

#### PC XT/AT and Other Compatible Interface

True real-time hardware and software compatibility with PC XT/AT and other compatible computers

- Direct bus interface logic with on-chip 24-mA drivers

- Supports 8- as well as 16-bit host bus transfer

- Supports any host speed with programmable and auto-wait-state generation

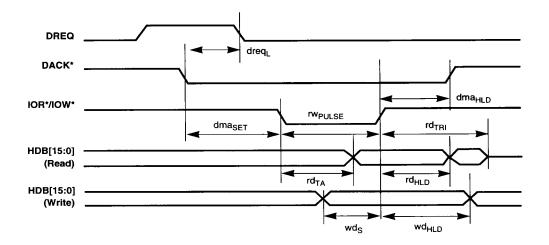

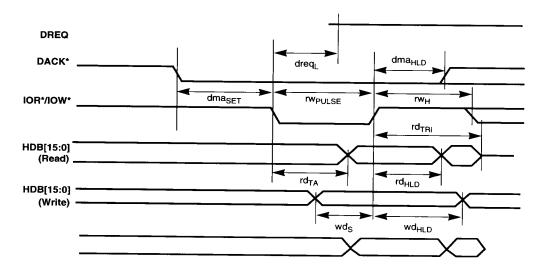

- PC XT/AT DMA handshake logic handles transfer to/from buffer memory at rates up to 4 Mwords/ second

- Demand Mode DMA handshake logic (EISA Type 'B')

- Buffer data transfer supported under DMA or programmed I/O for both PC XT and PC AT

- FIFOs provided to synchronize buffer RAM access with the PC bus and formatter

- Emulates the IBM® task file for PC AT and IBM command descriptor block for PC XT

- Provides logic to speed-up command response

- Provides logic for daisy-chaining two XT- or ATembedded drives

- Support of AT Master/Slave DASP\* and PDIAG\* Signals

- Separate status for bus reset and host program reset

#### Technology

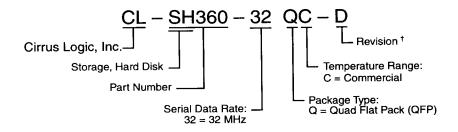

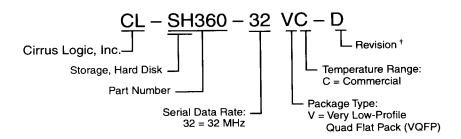

- 100-pin PQFP and VQFP packages

- Advanced, low-power, double-metal CMOS technology

#### **OVERVIEW** (cont.)

The CL-SH360 Disk Formatter consists of a serializer/deserializer, a flexible RAM-based Sequencer, 16-bit CRC polynomial and an 88-bit Reed-Solomon ECC generator with on-the-fly hardware correction capability. The Formatter also supports variable split data fields for constant density recording formats.

The CL-SH360 is designed to work with a local processor. It has multiplexed or non-multiplexed address and data bus similar to that provided by the

Intel® 8051 and Motorola® 68HC11 family of controllers. The local processor interface also supports separate host and disk interrupt pins.

The CL-SH360 has a highly sophisticated power management capability. It supports four levels of power-down when idle in full support of the ATA Specification. The extremely low power requirements of the CL-SH360 make it an ideal choice for laptop or other power-sensitive applications.

## **Table of Contents**

| 1.         | PIN        | INFORMATION                                                        |                |

|------------|------------|--------------------------------------------------------------------|----------------|

|            | 1.1        | Pin Diagram for the 100-Pin Plastic Quad Flat Pack (PQFP)          |                |

|            | 1.2        | Pin Diagram for the 100-Pin Very Low-Profile Quad Flat Pack (VQFP) |                |

| 2.         | DIN        |                                                                    |                |

| <b>~</b> · | 2.1        | ASSIGNMENTS                                                        | 3              |

| 2          |            |                                                                    |                |

| 3.         |            | ISTER TABLES                                                       |                |

|            | 3.1        | Buffer Manager Registers                                           | 18             |

|            | 3.2        | PC Interface Registers                                             |                |

|            | 3.3        | Formatter Registers                                                |                |

|            | 3.4        | Control Registers                                                  |                |

|            | 3.5        | Sequencer Registers                                                | 1              |

|            | 3.6<br>3.7 | Register Initialization                                            | 18             |

|            |            | Register Memory Map                                                |                |

| 4.         | FUN        | CTIONAL DESCRIPTION                                                | 2 <sup>-</sup> |

|            | 4.1        | Microcontroller Interface                                          | 2              |

|            |            | 4.1.1 Access to External Buses                                     | 2              |

|            |            | 4.1.2 Power-Down Mode                                              |                |

|            | 4.2        | Sector Formatter and Sequencer                                     | 2              |

|            |            | 4.2.1 Extended-Data-Handling Operations                            |                |

|            |            | 4.2.2 Functional Operation                                         |                |

|            |            | 4.2.3 Two Index Counter                                            | 28             |

|            |            | 4.2.4 Synchronization Timer                                        | 28             |

|            | 4.3        | Buffer Manager Interface                                           | 29             |

|            |            | 4.3.1 SRAM Addressing Operation                                    | 29             |

|            |            | 4.3.2 Buffer Segmentation                                          |                |

|            |            | 4.3.3 SRAM Read/Write Access Control                               |                |

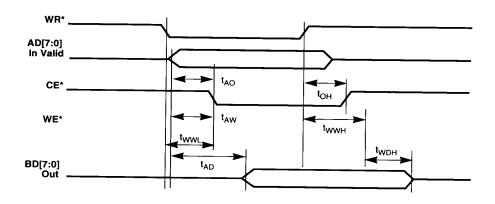

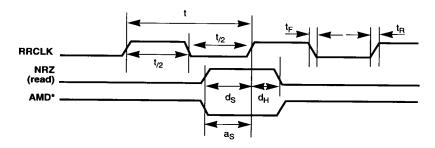

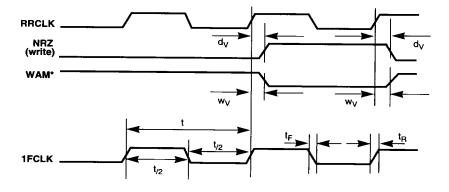

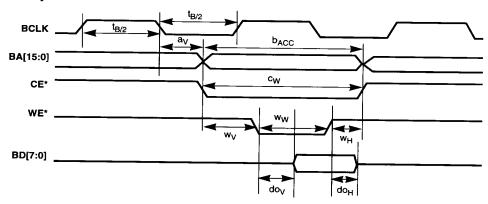

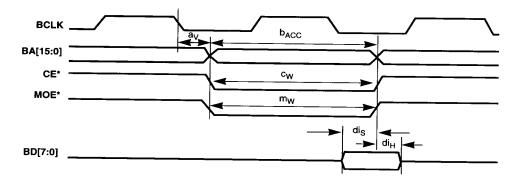

|            |            | 4.3.4 SRAM Signal Timing                                           |                |

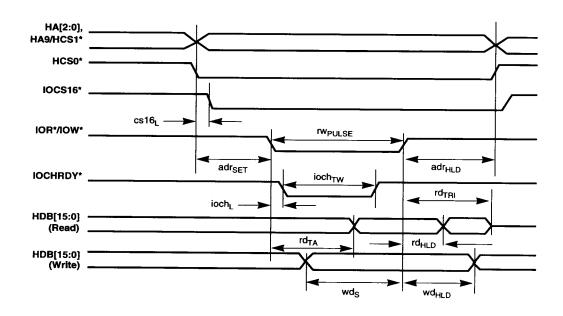

|            | 4.4        | PC XT/AT Interface                                                 | 3              |

|            |            | 4.4.1 PC Transfers                                                 | 31             |

|            |            | 4.4.2 PC Host Wait States                                          |                |

|            |            | 4.4.3 PC Host Auto-Commands                                        |                |

|            |            | 4.4.4 PC Host Long Commands                                        | 33             |

|            |            | 4.4.5 PC Host Master/Slave Operation                               | 33             |

| 5.         | DET        | AILED INTERNAL REGISTER DESCRIPTION                                | 34             |

|            | 5.1        | Register 9FH: Buffer Start Address High (BSAH) (Read/Write)        | 34             |

|            | 5.2        | Register BFH: Buffer Start Address Low (BSAL) (Read/Write)         | 34             |

|            | 5.3        | Register DFH: Buffer End Address High (BEAH) (Read/Write)          | 34             |

|            | 5.4        | Register FFH: Buffer End Address Low (BEAL) (Read/Write)           | 34             |

|            | 5.5        | Register 48H: Auxiliary Control 0 (Read/Write)                     | 34             |

|            | 5.6        | Register 4DH: 68H and 70H Read Data Register (Read Only)           | 36             |

|            | 5.7        | Register 4EH: Sector Size (Read/Write)                             | 36             |

|            |            |                                                                    |                |

## **Table of Contents** (cont.)

| 5.8   | Register 4FH: | Auxiliary Control 1 (Read/Write)              | 36   |

|-------|---------------|-----------------------------------------------|------|

| 5.9   |               | PC Interrupt Status (Read Only)               |      |

| 5.10  | Register 51H: | PC Interrupt Enable (Read/Write)              | 38   |

| 5.11  | Register 52H: | Miscellaneous Control/Status (Read/Write)     | 39   |

| 5.12  | Register 53H: |                                               | 40   |

| 5.13  | Register 54H: | Buffer Size/Segment Address (Read/Write)      | 41   |

| 5.14  | Register 58H: | PC Mode Control (Read/Write)                  | 42   |

| 5.15  | Register 59H: | Buffer Manager/PC Reset Control (Read/Write)  | 43   |

| 5.16  | Register 5AH: | Disk Address Pointer High (DAPH) (Read/Write) | .43  |

| 5.17  | Register 5BH: | Disk Address Pointer Low (DAPL) (Read/Write)  | .43  |

| 5.18  | Register 5CH: | Host Address Pointer High (HAPH) (Read/Write) | . 43 |

| 5.19  | Register 5DH: | Host Address Pointer Low (HAPL) (Read/Write)  | .44  |

| 5.20  | Register 5EH: | Stop Pointer High (SPH) (Read/Write)          | . 44 |

| 5.21  | Register 5FH: | Stop Pointer Low (SPL) (Read/Write)           | . 44 |

| 5.22  | Register 68H: | Scheduled Buffer Data (Read/Write)            | . 45 |

| 5.23  | Register 69H: | Sector Status Register (Read Only)            | . 46 |

| 5.24  | Register 69H: | Increment Sector Count Register (Write Only)  | . 46 |

| 5.25  | Register 6AH: | Sector Target Register (Read/Write)           | . 46 |

| 5.26  | Register 6BH: | Sector Count Register (Read/Write)            | . 46 |

| 5.27  | Register 6CH: | React Branch Register (Read/Write)            | . 47 |

| 5.28  | Register 6DH: | Sector Remaining Counter MSB (Read/Write)     | . 47 |

| 5.29  | Register 6EH: | Sector Remaining Counter LSB (Read/Write)     | .47  |

| 5.30  | Register 6FH: | Revision Register (Read Only)                 | .47  |

| 5.31  | Register 70H: | Microcontroller Buffer Access (Read/Write)    | . 47 |

| 5.32  | Register 71H: | ECC Control (Read/Write)                      | . 48 |

| 5.33  |               | Syndrome Shift Register (Read Only)           |      |

| 5.34  | Register 72H: | Correction Done Reset (Write Only)            | . 49 |

| 5.35  | Register 73H: | Auto-Command 'Lock' Release (Write Only)      | . 49 |

| 5.36  | Register 74H: | Offset Count Register (MSB) (Read/Write)      | .49  |

| 5.37  | Register 75H: | Offset Count Register (LSB) (Read/Write)      | . 49 |

| 5.38  | Register 76H: | Synchronization Byte-Count Limit (Read/Write) | . 50 |

| 5.39  | Register 77H: | Formatter Mode Selection (Read/Write)         | . 50 |

| 5.40  |               | Branch Address (Write Only)                   |      |

| 5.41  | Register 79H: | Formatter Status (Read Only)                  | 51   |

| 5.42  |               | Sequencer Start (Write Only)                  |      |

| 5.43  | Register 7AH: | Operation Control (Read/Write)                | 53   |

| 5.44  | Register 7BH: | WAM Control (Read/Write)                      | 54   |

| 5.45  | Register 7CH: | AMD Control (Read/Write)                      | 54   |

| 5.46  |               | Formatter Interrupt Status (Read Only)        |      |

| 5.47  | Register 7EH  | Formatter Interrupt Enable (Read/Write)       | 55   |

| 5.48  | Register 7FH: | Clock Control (Write Only)                    | 56   |

| 5.49  | Register 7FH: | Top of Stack (Read Only)                      | 57   |

| J. TJ |               | · -E -· - · · · · · · · · · · · · · · ·       |      |

# Table of Contents (cont.)

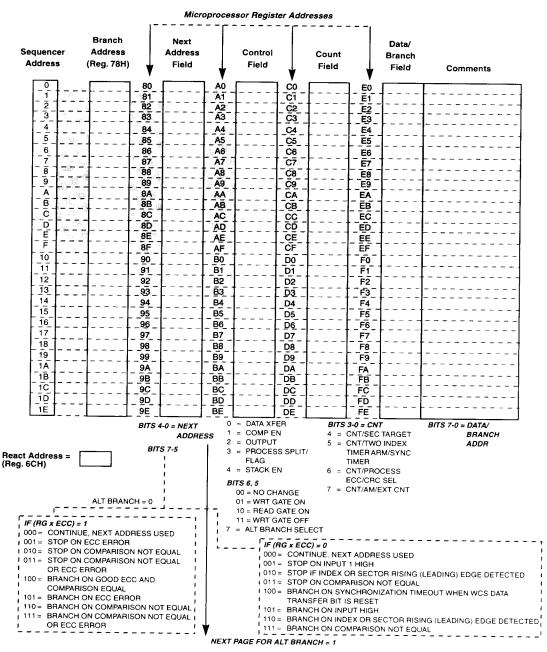

| 6. | SEC  | UENCE   | R RAM FIELD DESCRIPTION                                              | . 58 |

|----|------|---------|----------------------------------------------------------------------|------|

|    | 6.1  |         | ddress Field Register Description                                    |      |

|    |      | 6.1.1   | Registers 80H-9EH Next Address Field (Read/Write)                    |      |

|    | 6.2  | Count   | Field Register Description                                           |      |

|    |      | 6.2.1   | Registers C0H-DEH Count Field (Read/Write)                           |      |

|    | 6.3  | Data F  | ield Register Description                                            |      |

|    |      | 6.3.1   | Registers E0H-FEH Data Field (Read/Write)                            |      |

|    | 6.4  | Contro  | Field Register Description                                           |      |

|    |      | 6.4.1   | Registers A0H-BEH Control Field (Read/Write)                         | 63   |

|    | 6.5  | WCS V   | Vorksheet                                                            | 65   |

|    | 6.6  | WCS V   | Vorksheet Example                                                    | 67   |

| 7. | LOC  |         | ROCONTROLLER-HOST INTERFACE                                          |      |

|    | 7.1  | XT Loc  | cal Processor Interface                                              | 68   |

|    |      | 7.1.1   | XT Registers 40H-47H (60H-67H): Command/General-Purpose (Read/Write) |      |

|    |      | 7.1.2   | XT Register 55H: Mode/Status (Read/Write)                            | 69   |

|    |      | 7.1.3   | XT Register 56H: Drive Type (Read/Write)                             | 70   |

|    |      | 7.1.4   | XT Register 57H: DRV/DMA/IRQ (Read Only)                             |      |

|    | 7.2  | AT Loc  | cal Microcontroller Interface                                        | 71   |

|    |      | 7.2.1   | AT Register 40H (60H): Error Status Register (Read/Write)            |      |

|    |      | 7.2.2   | AT Register 41H (61H): Features Register (Read/Write)                |      |

|    |      | 7.2.3   | AT Register 42H (62H): Sector Count Register (Read/Write)            |      |

|    |      | 7.2.4   | AT Register 43H (63H): Sector Number Register (Read/Write)           |      |

|    |      | 7.2.5   | AT Register 44H (64H): Cylinder High Register (Read/Write)           | 72   |

|    |      | 7.2.6   | AT Register 45H (65H): Cylinder Low Register (Read/Write)            |      |

|    |      | 7.2.7   | AT Register 46H (66H): Drive/Head Register (Read/Write)              |      |

|    |      | 7.2.8   | AT Register 47H (67H): Command Register (Read/Write)                 |      |

|    |      | 7.2.9   | AT Register 55H: Control/Status Register (Read/Write)                |      |

|    |      | 7.2.10  | AT Register 56H: Drive 0 Control/Status Register (Read/Write)        |      |

|    |      | 7.2.11  | AT Register 57H: Drive 1 Control/Status Register (Read/Write)        | 75   |

| 8. | PÇ I | DISK CO | NTROLLER INTERFACE DESCRIPTION                                       | . 76 |

|    | 8.1  |         | k Controller Interface Description                                   |      |

|    |      | 8.1.1   | Read Data Register (Port 0 Read)                                     |      |

|    |      | 8.1.2   | Write Data Register (Port 0 Write)                                   |      |

|    |      | 8.1.3   | Status Register (Port 1 Read)                                        |      |

|    |      | 8.1.4   | Reset Register (Port 1 Write)                                        |      |

|    |      | 8.1.5   | Drive Type Register (Port 2 Read)                                    |      |

|    |      | 8.1.6   | Controller Select Register (Port 2 Write)                            |      |

|    |      | 8.1.7   | DRV/DMA/IRQ Enable Register (Port 3 Write)                           | 79   |

|    | 8.2  | AT Dist | k Controller Interface Description                                   | 70   |

|    |      | 8.2.1   | Read Data Register (Read Only)                                       |      |

|    |      | 8.2.2   | Write Data Register (Write Only)                                     |      |

|    |      | 8.2.3   | Error Status Register (Read Only)                                    | 81   |

|    |      |         |                                                                      |      |

## **Table of Contents** (cont.)

|     |      | 8.2.4   | Features Register (Write Only)                  | 82 |

|-----|------|---------|-------------------------------------------------|----|

|     |      | 8.2.5   | Sector Count Register (Read/Write)              | 82 |

|     |      | 8.2.6   | Sector Number Register (Read/Write)             | 82 |

|     |      | 8.2.7   | Cylinder Low Register (Read/Write)              | 82 |

|     |      | 8.2.8   | Cylinder High Register (Read/Write)             | 82 |

|     |      | 8.2.9   | Drive/Head Register (Read/Write)                | 82 |

|     |      | 8.2.10  |                                                 | 83 |

|     |      | 8.2.11  |                                                 | 84 |

|     |      | 8.2.12  |                                                 | 84 |

|     |      |         | Fixed Disk Register (Write Only)                | 84 |

|     |      | 8.2.14  | Digital Input Register (Read Only)              | 84 |

| 9.  | FLEC | CTRICA  | AL SPECIFICATIONS                               | 85 |

| ٠.  | 9.1  | Ahsolu  | ite Maximum Ratings                             | 8  |

|     | 9.2  | DC Ch   | naracteristics                                  | 8  |

|     | 9.3  | AC Ch   | aracteristics/Timing Information                | 8  |

|     | 3.0  | 9.3.1   | Index of Timing Information                     | 8  |

| 10. | SAM  | DI F PA | ACKAGE                                          |    |

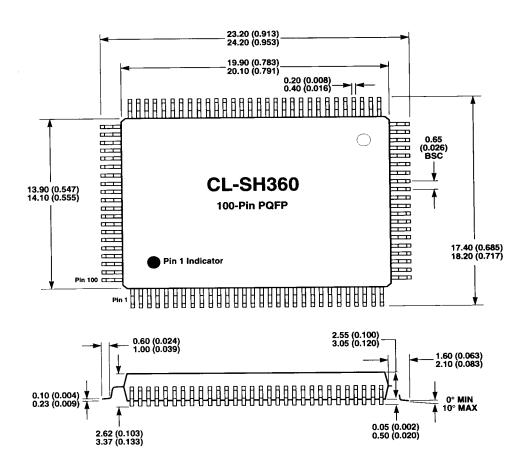

| 10. | 10.1 |         | in Plastic Quad Flat Pack (PQFP, EIAJ)          |    |

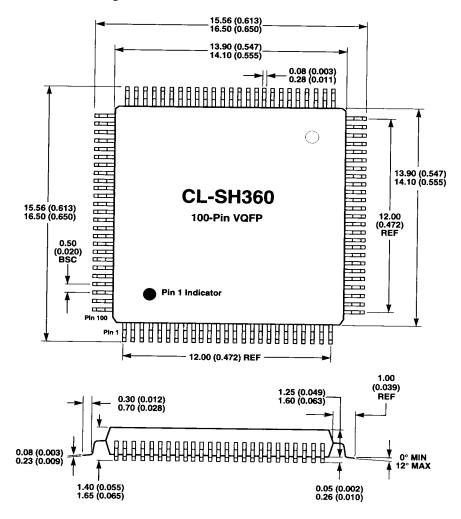

|     | 10.1 |         | In Very Low-Profile Quad Flat Pack (VQFP, EIAJ) |    |

| 44  |      |         | INFORMATION                                     |    |

### 1. PIN INFORMATION

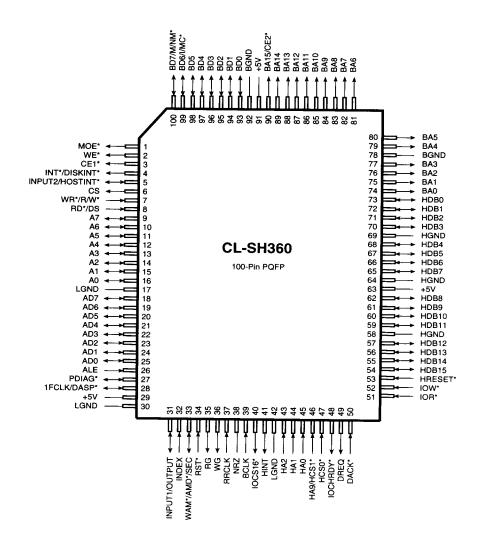

## 1.1 Pin Diagram for the 100-Pin Plastic Quad Flat Pack (PQFP)

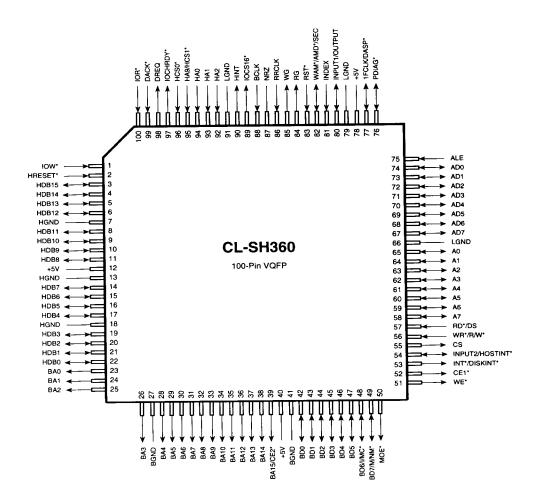

# 1.2 Pin Diagram for the 100-Pin Very Low-Profile Quad Flat Pack (VQFP)

### 2. PIN ASSIGNMENTS

The following conventions are used in the pin assignment table: (I) indicates an input; (O) indicates an output; (I/O) indicates an input/output; (OD) indicates an open-drain output; (Z) indicates a tri-state output or an input/output; (\*) denotes a negative-true (active-low) signal.

## 2.1 100-Pin PQFP and VQFP Pin Assignments

NOTE: Unless otherwise specified, all references to pin locations include PQFP/VQFP pin numbers.

| Symbol    | PQFP<br>No.    | VQFP<br>No.    | Туре  | Description                                                                                                                                                                                                                                                                                                                                 |

|-----------|----------------|----------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BA15/CE2* | 90             | 39             | 0     | BUFFER ADDRESS LINE 15/BUFFER CHIP ENABLE 2: Bit 15 is for addressing buffer memory or the second 32K buffer chip enable.                                                                                                                                                                                                                   |

| BA[14:0]  | 89-79<br>77-74 | 38-28<br>26-23 | 0     | <b>BUFFER ADDRESS LINES:</b> Bits 14-0 are for addressing buffer memory.                                                                                                                                                                                                                                                                    |

| BD7/M/NM* | 100            | 49             | I/O   | BUFFER DATA BUS/MULTIPLEXED/NON-MULTIPLEXED ADDRESS CONFIGURATION: This is Bit 7 of the 8-bit buffer data bus. The CL-SH360 is initialized to Multiplexed Mode if this input is connected to an external pull-up resistor (~20K ohm) after deassertion of the RST* Signal (Pin 34/83). Otherwise, it is configured in Non-multiplexed Mode. |

| BD6/I/MC* | 99             | 48             | Ī/O   | BUFFER DATA BUS INTEL/MOTOROLA: This is Bit 6 of the 8-bit buffer data bus. The CL-SH360 is initialized to Motorola if this input is connected to an external pull-down resistor (~20K ohm) after deassertion of the RST* (Pin 34/83) Signal. Otherwise, it is configured in Intel Mode.                                                    |

| BD[5:0]   | 98-93          | 47-42          | : I/O | <b>BUFFER DATA BUS:</b> These six signals are Bits 5-0 of the 8-bit buffer data bus.                                                                                                                                                                                                                                                        |

| MOE*      | 1              | 50             | 0     | <b>MEMORY OUTPUT ENABLE:</b> This signal is asserted low when a RAM Buffer Operation is active. It is recommended that MOE* be connected to the RAM output enable for high-speed operation.                                                                                                                                                 |

| WE*       | 2              | 51             | 0     | WRITE ENABLE: This signal is asserted low when a buffer memory Write Operation is active.                                                                                                                                                                                                                                                   |

| CE1*      | 3              | 52             | 0     | <b>BUFFER CHIP ENABLE 1:</b> This signal is the control signal for the full-buffer chip enable or the first 32K chip enable.                                                                                                                                                                                                                |

## 2.1 100-Pin PQFP and VQFP Pin Assignments (cont.)

| Symbol              | PQFP<br>No. | VQFP<br>No. | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------|-------------|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT*/<br>DISKINT*   | 4           | 53          | O,OD | INTERRUPT/DISK INTERRUPT: This is the microcontroller Interrupt*/Disk Interrupt* Pin, programmable for either push-pull or open-drain output circuitry. This pin contains an internal pull-up resistor. The INT*/DISKINT* pull-up can be disabled if the Interrupt Enable Bit (Register 77H, Bit 3) is set, and the Interrupt Pin Pull-up Disable Bit (Register 77H, Bit 4) is set.                                                                         |

| INPUT2/<br>HOSTINT* | 5           | 54          | I/O  | INPUT2/HOST INTERRUPT: This is the microcontroller Host Interrupt* Pin, programmable for either push-pull or open-drain output circuitry. This pin can also be used as an edge-sensitive second input to the sequencer. This pin contains an internal pull-up resistor which can be disabled by setting Bit 4 in Register 4FH.                                                                                                                              |

| CS                  | 6           | 55          | Ī    | <b>CHIP SELECT:</b> This signal must be asserted to access the CL-SH360 registers.                                                                                                                                                                                                                                                                                                                                                                          |

| WR*/R/W*            | 7           | 56          | I    | WRITE STROBE/READ/WRITE: When the Intel bus control interface is selected (the I/MC* Signal (Pin 99/48) is asserted high), this signal acts as the WR* Signal. When the Write Strobe Signal is asserted low and the CS Signal (Pin 6/55) is asserted high, the data on the AD lines will be written to the specified register.                                                                                                                              |

|                     |             |             |      | When the Motorola bus control interface is selected (the <i>IMC*</i> Signal (Pin 99/48) is deasserted low), this signal acts as the R/W* Signal. A high on this input, along with the RD*/DS Signal (Pin 8/57) asserted and the CS Signal (Pin 6/55) asserted high, it indicates a Read Operation. A low on this input, along with the RD*/DS Signal (Pin 8/57) asserted and CS Signal (Pin 6/55) asserted high, it indicates a Write Operation.            |

| RD*/DS              | 8           | 57          | Ī    | READ STROBE/DATA STROBE: When the Intel bus control interface is selected (the <i>I/MC*</i> Signal (Pin 99/48) is asserted high), this signal acts as the RD* Signal. When the Read Strobe Signal is asserted low and the CS Signal (Pin 6/55) is asserted high, the data from the specified register will be driven onto the AD lines.                                                                                                                     |

|                     |             |             |      | When the Motorola bus control interface is selected (the <i>VMC*</i> Signal (Pin 99/48) is deasserted low), this signal acts as the Data Strobe Signal. A high on this input, along with the WR*/R/W* Signal (Pin 7/56) asserted and the CS Signal (Pin 6/55) asserted high, it indicates a Read Operation. A high on this input, along with the WR*/R/W* (Pin 7/56) deasserted and the CS Signal (Pin 6/55) asserted high, it indicates a Write Operation. |

## 2.1 100-Pin PQFP and VQFP Pin Assignments (cont.)

| Symbol                   | PQFP<br>No. | VQFP<br>No. | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------|-------------|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[7:0]                   | 9-16        | 65-58       | I/O  | LOCAL MICROCONTROLLER ADDRESS BUS: These are non-multiplexed address input or demultiplexed address output lines.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AD[7:0]                  | 18-25       | 74-67       | 1/0  | LOCAL MICROCONTROLLER ADDRESS/DATA: These are tri-state address/data lines that interface with a multiplexed microcontroller address/data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ALE                      | 26          | 75          | 1    | ADDRESS LATCH ENABLE: In Multiplexed Mode, this signal will latch the address from the AD bus; A[7:0] are the latched address outputs. When Non-multiplexed Mode is selected, this signal should be driven high, and A[7:0] are the demultiplexed address inputs.                                                                                                                                                                                                                                                                                                                                                                      |

| PDIAG*                   | 27          | 76          | I/O  | PASS DIAGNOSTICS: This signal is used between two embedded AT drives for communicating drive diagnostic results. This pin contains an internal pull-up resistor that can be disabled by setting Bit 4 in Register 4FH.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1FCLK/DASP               | * 28        | 77          | I/O  | <b>1FCLK/SLAVE PRESENT</b> : The 1FCLK can be used for the ECC corrector circuit. For embedded AT drives, this pin can also function as the Slave Present Signal. This pin contains an internal pull-up resistor that can be disabled by setting Bit 4 in Register 4FH.                                                                                                                                                                                                                                                                                                                                                                |

| INPUT1/<br>OUTPUT        | 31          | 80          | I/O  | INPUT1/OUTPUT: The state of this pin is sampled by reading Register 7DH, Bit 2. It is also a branch input to the sequencer RAM. When the pin is programmed for outputs, it is controlled by Bit 2 of the Control Field (A0H-BEH) of the Sequencer WCS RAM. This pin contains an internal pull-up resistor. The resistor is disabled when the pin is configured as an output.                                                                                                                                                                                                                                                           |

| INDEX                    | 32          | 81          | Ĭ    | <b>INDEX:</b> This is an input for the index pulse received from the drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| WAM*/<br>AMD*/<br>SECTOR | 33          | 82          | I/O  | WRITE ADDRESS MARK/ADDRESS MARK DETECT/<br>SECTOR: This signal can be configured to operate in Hard or<br>Soft Sector Mode by initializing the Hard/Soft* Sector Mode<br>Control Bit of the Formatter Mode Selection Register (Register<br>77H, Bit 7). The default is Soft Sector Mode. In Soft Sector<br>Mode, when the RG Signal (Pin 35/84) is asserted, a low-level<br>input on this signal indicates Address Mark detected. Also, in<br>Soft Sector Mode, a 1-bit wide pulse is an output when WG<br>(Pin 36/85) is active and an address mark is to be written. In<br>Hard Sector Mode, this is the input for the sector pulse. |

## 100-Pin PQFP and VQFP Pin Assignments (cont.)

| Symbol    | PQFP<br>No. | VQFP<br>No. | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|-------------|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

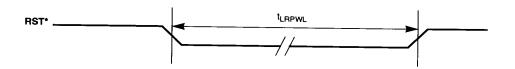

| RST*      | 34          | 83          | ı    | <b>RESET:</b> When this signal is asserted low, it stops all operations within the chip and deasserts the RG Signal (Pin 35/84), the WG Signal (Pin 36/85), and the NRZ Signal (Pin 38/87). All I/O signals and host outputs are set to a high-impedance state. See <i>Register Initialization</i> , Section 3.6.                                                                                                                                     |

| RG        | 35          | 84          | 0    | <b>READ GATE:</b> This signal is asserted when the CL-SH360 is reading NRZ data from the storage device.                                                                                                                                                                                                                                                                                                                                              |

| WG        | 36          | 85          | 0    | WRITE GATE: This signal is asserted when the CL-SH360 is writing NRZ data to the storage device.                                                                                                                                                                                                                                                                                                                                                      |

| RRCLK     | 37          | 86          | l    | READ REFERENCE CLOCK: This is a multiplexed input sourced from the VFO oscillator during a Read Gate; otherwise, it is from the write oscillator. This is the primary clock for the Formatter section and must be present at all times, including during a Reset Operation.                                                                                                                                                                           |

| NRZ       | 38          | 87          | I/O  | NRZ: This is a Read Data Input from the disk when the RG Signal (Pin 35/84) is active; this is a Write Data Output to the disk when the WG Signal (Pin 36/85) is active.                                                                                                                                                                                                                                                                              |

| BCLK      | 39          | 88          | l    | <b>BUFFER CLOCK:</b> This is a clock input that is used to generate buffer memory access cycles.                                                                                                                                                                                                                                                                                                                                                      |

| IOCS16*   | 40          | 89          | OD   | <b>16-BIT DATA TRANSFER:</b> This signal indicates that a 16-bit data transfer is active on the PC bus.                                                                                                                                                                                                                                                                                                                                               |

| HINT      | 41          | 90          | O,Z  | <b>HOST INTERRUPT:</b> This signal, when enabled, sends an interrupt to the PC host.                                                                                                                                                                                                                                                                                                                                                                  |

| HA[2:0]   | 43-45       | 92-9        | 4 I  | PC BUS ADDRESS LINES: The address lines HA[9,2:0] address the various AT/XT Control, Status, and Data Registers. Only the HA[1:0] lines are used for PC XT operation.                                                                                                                                                                                                                                                                                 |

| HA9/HCS1* | 46          | 95          | ı    | PC ADDRESS LINE 9 or CHIP SELECT 1: This is a Multiplexed Input Signal. When the HCS1 Mode Enable Bit (Register 52H, Bit 3) is reset, this input is PC Address Line 9; when the bit is set, the input is Host Chip Select 1. When this signal is configured as HCS1*, this input is ignored when the DACK* Signal (Pin 50/99) is asserted low. This pin contains an internal pull-up resistor which can be disabled by setting Bit 4 in Register 4FH. |

12

## 2.1 100-Pin PQFP and VQFP Pin Assignments (cont.)

| Symbol    | PQFP<br>No.                        | VQFP<br>No. | Туре | Description                                                                                                                                                                                                                                                                                                                          |

|-----------|------------------------------------|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HCS0*     | 47                                 | 96          | 1    | CHIP SELECT 0: When this signal is asserted low, this input selects access to the Control, Status and Data Registers. This input is ignored during DMA data transfers, i.e., when the DACK* Signal (Pin 50/99) is asserted low. This pin contains an internal pull-up resistor. It can be disabled by setting Bit 4 in Register 4FH. |

| IOCHRDY*  | 48                                 | 97          | 0    | VO CHANNEL READY: This signal is asserted low to extend host transfer cycles when the controller is not ready to respond.                                                                                                                                                                                                            |

| DREQ      | 49                                 | 98          | O,Z  | <b>DMA REQUEST:</b> The DMA Request Signal is used during DMA transfer between the host and controller. This signal is issued by the controller to start a DMA transfer.                                                                                                                                                             |

| DACK*     | 50                                 | 99          | I    | DMA ACKNOWLEDGE: The DMA Acknowledge Signal is used during DMA to complete the DMA handshake for data transfer between the host and the CL-SH360. The signal is active for each transfer on the host bus. This pin contains an internal pull-up resistor.                                                                            |

| IOR*      | 51                                 | 100         | I    | I/O READ STROBE: This signal is asserted low by the host during a Host Read Operation. When this signal is asserted low with the HCS0*/HCS1* or the DACK* Signal, it enables status or data onto the host data bus.                                                                                                                  |

| IOW*      | 52                                 | 1           | t    | I/O WRITE STROBE: This signal is asserted low by the host during a Host Write Operation. When this signal is asserted low with the HCS0*/HCS1* or the DACK* Signal, data from the host data bus is strobed into the CL-SH360.                                                                                                        |

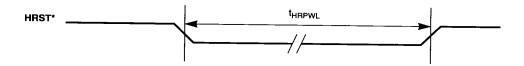

| HRST*     | 53                                 | 2           | I    | <b>HOST RESET</b> : When this signal is asserted, it initializes the Control/Status Registers and stops any command in process. See <i>Register Initialization</i> , Section 3.6. This pin contains an internal pull-up resistor.                                                                                                    |

| HDB[15:0] | 54-57,<br>59-62,<br>65-68<br>70-73 | ,           |      | HOST DATA BUS: During PC AT operations, HDB[15:8] are used in conjunction with HDB[7:0] for word transfers between the sector buffer and the host; Bits HDB[7:0] are used for control status and ECC byte access. During PC XT operation, only HDB[7:0] lines are used; the HDB[15:8] lines are tri-stated.                          |

## 2.1 100-Pin PQFP and VQFP Pin Assignments (cont.)

| Symbol | PQFP VQFP<br>No. No. Typ | e Description      |  |

|--------|--------------------------|--------------------|--|

| HGND   | 58, 64, 7, 13<br>69 18   | HOST GROUND.       |  |

| BGND   | 78, 92 27, 41            | BUFFER BUS GROUND. |  |

| LGND   | 17, 30, 66, 79<br>42 91  | LOGIC GROUND.      |  |

| +5V    | 29, 91, 12, 40<br>63 78  | POWER SUPPLY (+5)  |  |

## 3. REGISTER TABLES

## 3.1 Buffer Manager Registers

| Address Type* |     | Description/Function                                                                                                                                                                                                                                                                               |  |  |

|---------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 9FH/BFH       | R/W | Buffer Start Address                                                                                                                                                                                                                                                                               |  |  |

| DFH/FFH       | R/W | Buffer End Address                                                                                                                                                                                                                                                                                 |  |  |

| 68H           | R/W | Scheduled Microcontroller Buffer Data Access                                                                                                                                                                                                                                                       |  |  |

| 53H           | R/W | Buffer Transfer Control                                                                                                                                                                                                                                                                            |  |  |

| 54H           | R/W | Buffer Size/Segment Address                                                                                                                                                                                                                                                                        |  |  |

| 59H           | R/W | Buffer/PC Reset Register                                                                                                                                                                                                                                                                           |  |  |

| 5AH-5BH       | R/W | Disk Address Pointer                                                                                                                                                                                                                                                                               |  |  |

| 5CH-5DH       | R/W | Host Address Pointer                                                                                                                                                                                                                                                                               |  |  |

| 5EH-5FH       | R/W | PC Stop Pointer                                                                                                                                                                                                                                                                                    |  |  |

| 70H           | R/W | Microcontroller Buffer Access                                                                                                                                                                                                                                                                      |  |  |

| 73H           | W   | Auto-Command 'Lock' Release: A write to this register unlocks the Buffer Manager Registers. The registers were locked when the host issued an Auto-Command. The affected registers are 53H, 5C-5FH, 68H and 70H. Also, the Local Microcontroller Power-Down Bit is unlocked (Register 4FH, Bit 5). |  |  |

## 3.2 PC Interface Registers

| Address Type       |     | Description/Function                                                                                             |  |  |

|--------------------|-----|------------------------------------------------------------------------------------------------------------------|--|--|

| 40H-47H<br>60H-67H | R/W | PC Interface Register File: These registers are for communication between the host PC and local microcontroller. |  |  |

| 55H-57H            | R/W | PC Interface Registers: These registers are for communication between the host PC and the local microcontroller. |  |  |

| 50H                | R/W | PC Interrupt Status Register                                                                                     |  |  |

| 51H                | R/W | PC Interrupt Enable Register                                                                                     |  |  |

| 52H                | R/W | Miscellaneous Control/Status Register                                                                            |  |  |

| 58H                | R/W | PC Mode Control Register                                                                                         |  |  |

**NOTE**: Register types are as follows: R/W = Read/Write; R = Read Only; W = Write Only.

## Formatter Registers

| Address | Type | Description/Function                                                                                                                                                                                                                                                                                |  |  |  |

|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 4DH     | R    | Data Latch Register (for read accesses of the data buffer through Registers 68H and 70H)                                                                                                                                                                                                            |  |  |  |

| 4EH     | R/W  | Sector Size Register (for larger than 512-byte data fields)                                                                                                                                                                                                                                         |  |  |  |

| 69H     | R    | Sector Status Register                                                                                                                                                                                                                                                                              |  |  |  |

| 69H     | W    | Increment Sector Count Register                                                                                                                                                                                                                                                                     |  |  |  |

| 6AH     | R/W  | Sector Target Register                                                                                                                                                                                                                                                                              |  |  |  |

| 6BH     | R/W  | Sector Count Register                                                                                                                                                                                                                                                                               |  |  |  |

| 6CH     | R/W  | React Branch Register                                                                                                                                                                                                                                                                               |  |  |  |

| 6DH     | R/W  | MSB Sector Remaining Counter                                                                                                                                                                                                                                                                        |  |  |  |

| 6EH     | R/W  | LSB Sector Remaining Counter                                                                                                                                                                                                                                                                        |  |  |  |

| 6FH     | R    | Revision Register                                                                                                                                                                                                                                                                                   |  |  |  |

| 71H     | R/W  | Control Register for ECC: Bit 5, which can be set from the RST* Pin or the microcontroller, is the Formatter reset. When set, a constant reset will be asserted that stops all operations within the Formatter and drops RG, WG, WAM and NRZ outputs. This reset also clears the interrupt enables. |  |  |  |

| 72H     | R    | ECC Syndrome Shift Register                                                                                                                                                                                                                                                                         |  |  |  |

| 72H     | W    | Correction Done Reset                                                                                                                                                                                                                                                                               |  |  |  |

| 74H     | R/W  | ECC Offset Correction Count (MSB)                                                                                                                                                                                                                                                                   |  |  |  |

| 75H     | R/W  | ECC Offset Correction Count (LSB)                                                                                                                                                                                                                                                                   |  |  |  |

| 76H     | R/W  | Synchronization Byte-Count Limit                                                                                                                                                                                                                                                                    |  |  |  |

| 77H     | R/W  | Formatter Mode Selection                                                                                                                                                                                                                                                                            |  |  |  |

| 78H     | W    | Branch Address Register                                                                                                                                                                                                                                                                             |  |  |  |

| 79H     | R    | Formatter Status Register                                                                                                                                                                                                                                                                           |  |  |  |

| 79H     | W    | Sequencer Start Address Register                                                                                                                                                                                                                                                                    |  |  |  |

| 7AH     | R/W  | Operation Control/Status Register                                                                                                                                                                                                                                                                   |  |  |  |

| 7BH     | R/W  | WAM Output Timing Control Register                                                                                                                                                                                                                                                                  |  |  |  |

|         |      |                                                                                                                                                                                                                                                                                                     |  |  |  |

16

## 3.3 Formatter Registers (cont.)

| Address    | Type   | Description/Function                                                                                                                         |  |  |

|------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7CH R/W    |        | Synchronous Byte Register (to be compared with NRZ read data): The number of bits to be compared is controlled by Register 7FH.              |  |  |

| 7DH        | R/W    | Formatter Interrupt Status Register                                                                                                          |  |  |

| 7EH        | R/W    | Formatter Interrupt Enable Register                                                                                                          |  |  |

| 7FH<br>7FH | W<br>R | Clock Control and Sync Compare Register Stack: When reading, contents of the top of stack are presented to the bus and the stack is rotated. |  |  |

## 3.4 Control Registers

| Address | Type | Description/Function                                                                                      |

|---------|------|-----------------------------------------------------------------------------------------------------------|

| 48H     | R/W  | Auxiliary Control Register 0 for mode selection of Formatter and buffer options.                          |

| 4FH     | R/W  | Auxiliary Control Register 1 for mode selection of Formatter and local microcontroller interface options. |

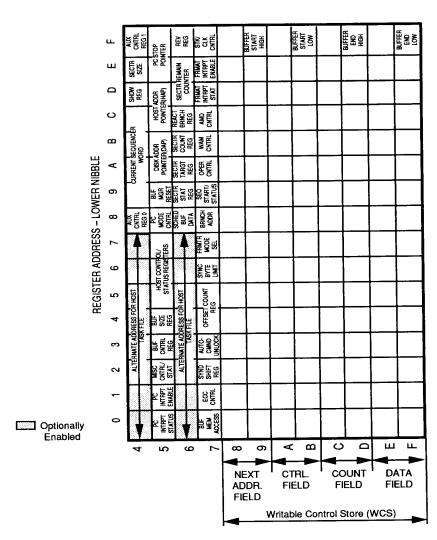

## 3.5 Sequencer Registers

| Address | Туре | Description/Function                                                                                                                                                                                          |

|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 80H-9EH | R/W  | Next Address Field of the WCS Word: This is the address that the Sequencer will go to after the down-counter has reached zero, and a branch has not been taken.                                               |

| A0H-BEH | R/W  | Control Field of the WCS Word                                                                                                                                                                                 |

| C0H-DEH | R/W  | Count Field of the WCS Word: This sets the initial value of the Sequencer counter when a new state is entered.                                                                                                |

| EOH-FEH | R/W  | Data Field of the WCS Word: This is the source for all overhead bytes of data used by the device during Write Operations. During Read Operations, it is one of the operands to the comparison logic.          |

| 49H-4CH | R/W  | This allows the microcontroller to access the Current Sequencer Word. There is no protection against access contention between the microcontroller and Sequencer. These registers are for test purposes only. |

## 3.6 Register Initialization

| REGISTER        | HRST*      | RST*        | HOST<br>PROG. | REG 59H  | REG 59H     | REG 71H     | REGISTER BIT VALUE NOTES |

|-----------------|------------|-------------|---------------|----------|-------------|-------------|--------------------------|

| Address         | (Pin 53/2) | (Pin 34/83) | Reset         | (Write)  | (Bit 0 = 1) | (Bit 5 = 1) | 7 6 5 4 3 2 1 0          |

| 40H/60H         |            |             |               |          |             |             | xxxxxxx                  |

| 41H/61H         | 1          |             |               |          |             |             | xxxxxxx                  |

| 42H/62H         |            |             |               |          |             |             | x x x x x x x x          |

| 43H/63H         |            |             |               |          |             |             | x x x x x x x x          |

| 44H/64H         |            |             |               |          |             |             | x x x x x x x x          |

| 45H/65H         |            |             |               |          |             |             | x x x x x x x x          |

| 46H/66H         | 1          | 1           | 1             |          |             |             | 0 0 0 0 0 0 0 0          |

| 47H/67H         |            |             |               |          |             |             | x x x x x x x x          |

| 48H             |            | 1           |               |          |             | 1           | 0 0 0 0 0 0 0 0 1        |

| 49H (Test only) |            | 1           |               |          |             | /           | 0 0 0 1 1 1 1 1          |

| 4AH (Test only) |            | 1           |               |          |             | 1           | 0 0 0 0 0 0 0            |

| 4BH (Test only) |            | 1           |               |          |             | /           | 0 0 0 0 0 0 0 0          |

| 4CH (Test only) |            | 1           |               |          |             | /           | 0 0 0 0 0 0 0 0          |

| 4DH             |            | 1           |               |          |             | 1           | 0 0 0 0 0 0 0            |

| 4EH             |            | /           |               |          |             |             | 0 0 0 0 0 0 0 0          |

| 4FH             |            |             |               |          |             |             | x x x x x x x x          |

| 50H             |            | 1           |               | "        | T           |             | x x x 0 0 0 0 0          |

| 51H             |            | /           |               |          |             |             | x x x 0 0 0 0 0          |

| 52H             |            | /           |               |          |             |             | 0 0 0 0 0 0 0 0 1        |

| 53H             |            | /           |               |          |             |             | 0 0 0 0 0 0 0 0 1        |

| 54H             |            | /           |               |          |             |             | 0 0 0 0 0 0 0            |

| 55H (XT Mode)   | 1          | 1           | 1             |          |             |             | 0 0 0 0 0 0 0 0 1        |

| 56H (XT Mode)   |            |             |               | <u> </u> |             |             | x x x x x x x x          |

| 57H (XT Mode)   | /          |             | 1             |          |             |             | x x x x x 0 0 0          |

| 55H (AT Mode)   | /          |             |               |          |             |             | 1 0 0 0 0 0 0 0 1        |

| 56H (AT Mode)   |            | /           |               |          |             |             | x x x 0 0 0 0 0          |

| 57H (AT Mode)   |            | /           |               |          |             |             | x x x 0 0 0 0 0          |

| 58H             |            | /           |               |          |             |             | 0 1 0 1 1 0 0 0          |

| 59H             |            | /           |               |          | 1           |             | X X X X X X X 1          |

| 5AH             |            | 1           |               | /        | 1           |             | 0 0 0 0 0 0 0 0          |

| 5BH             |            | 1           |               | /        | /           |             | 0 0 0 0 0 0 0            |

| 5CH             | 1          | /           |               | /        | /           |             | 0 0 0 0 0 0 0 0 2        |

| 5DH             | 1          | /           |               | 1        | /           |             | 0 0 0 0 0 0 0 0 2        |

| 5EH             |            | 1           |               | 1        | 1           |             | 0 0 0 0 0 0 0 1 3        |

| 5FH             |            | 1           |               | /        | 1           |             | 1 1 1 1 1 1 1 3          |

| REGISTER        | HRST*      | RST*        | HOST<br>PROG. | REG 59H  | REG 59H        | REG 71H     | REGISTER BIT VALUE NOTE |

|-----------------|------------|-------------|---------------|----------|----------------|-------------|-------------------------|

| Address         | (Pin 53/2) | (Pin 34/83) | Reset         | (Write)  | (Bit 0 = 1)    | (Bit 5 = 1) | 7 6 5 4 3 2 1 0         |

| 68H             | -          | /           |               | /        | 1              |             | 0 0 0 0 0 0 0 0         |

| 69H (Read)      |            | 1           |               |          | <u></u>        |             | X X X X X X 0 0         |

| 6AH             | † "-       | 1           |               |          |                |             | 0 0 0 0 0 0 0 0         |

| 6BH             |            | /           |               |          |                |             | 0 0 0 0 0 0 0 0         |

| 6CH             |            | /           |               |          |                | 1           | X X X O O O O O         |

| 6DH             |            | /           |               |          |                |             | X X X X O O O O         |

| 6EH             | -          | 1           | -             |          |                |             | 0 0 0 0 0 0 0 0         |

| 6FH             |            |             | 1             |          |                |             | xxxxxxx                 |

| 70H             |            |             |               |          |                |             | ×××××××                 |

| 71H             | ****       | 1           |               |          | <u> </u>       |             | 0 0 1 0 0 0 0 0 1       |

| 72H             |            | 1           | -             |          |                |             | 0 0 0 0 0 0 0 0         |

| 73H             |            | -           |               | <u> </u> |                |             | x x x x x x x x         |

| 74H             |            | 1           | - >-          |          | -              | /           | 0 0 0 0 0 0 0 0         |

| 75H             | _          | 1           |               |          |                | /           | 0 0 0 0 0 0 0 0         |

| 76H             |            | 1           |               |          |                |             | 0 0 0 0 0 0 0 0         |

| 77H             |            | 1           |               |          | <del>_</del> . |             | 0 0 0 0 0 0 0 0         |

| 78H             | -          | 1           |               |          |                | /           | X X X O O O O O         |

| 79H (Read)      | T          | 1           |               |          |                |             | 0 0 0 X X X 0 0 1       |

| 7AH             |            | 1           |               |          | <del>-</del>   | /           | 0 0 0 0 0 0 0 0         |

| 7BH             |            | 1           |               |          |                |             | 0 0 0 0 0 0 0           |

| 7CH             |            | 1           |               |          |                | _           | 0 0 0 0 0 0 0 0         |

| 7DH             |            | 1           |               |          |                | /           | X 0 0 0 0 0 0 0         |

| 7EH             |            | /           | ·             |          |                |             | X 0 0 0 0 0 0 0         |

| 7FH (Write)     |            | 1           |               |          | -              |             | 0 0 0 0 0 0 0 0         |

| 9FH             |            | 1           |               |          | 1              |             | 0 0 0 0 0 0 0 0         |

| BFH             |            | 1           |               |          |                |             | 0 0 0 0 0 0 0 0         |

| DFH             |            | 1           |               |          |                |             | 1 1 1 1 1 1 1           |

| FFH             |            | 1           |               |          |                |             | 1 1 1 1 1 1 1           |

| 80H-9 <b>EH</b> |            |             |               |          |                |             | x x x x x x x x         |

| A0-BEH          |            |             |               |          |                | -           | X X X X X X X X         |

| C0-DEH          |            |             |               |          |                |             | X X X X X X X X         |

| E0-FEH          |            |             |               |          |                |             | X X X X X X X X         |

NOTES: 1) This table only lists reset conditions that are common to all bits in each register. For reset conditions of individual bits in these registers, see the detail register descriptions in Section 5.

2) Registers 5CH and 5DH are also reset by an auto-command.

3) Registers 5EH and 5FH are also set to 01H and FFH, respectively, by an auto-command.

#### 3.7 **Register Memory Map**

REGISTER ADDRESS - UPPER NIBBLE

## 4. FUNCTIONAL DESCRIPTION

The CL-SH360 is designed to be used with a low-cost microcontroller that allows it to maintain a 'loose' synchronization with the real-time disk operation. The CL-SH360 maintains 'close' synchronization with the data to and from the disk drive and provides the signals necessary to control this path. Using the CL-SH360 means a lower-total-part count for an intelligent disk drive design with the PC XT/AT interface.

The CL-SH360 has four functional blocks:

- Microcontroller Interface

- Sector Formatter and Sequencer

- Buffer Manager Interface

- PC XT/AT Interface

#### 4.1 Microcontroller Interface

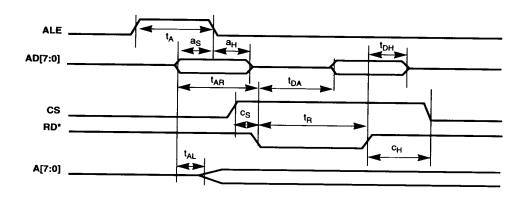

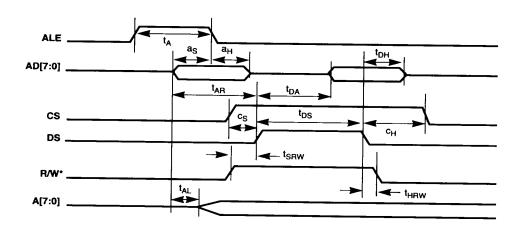

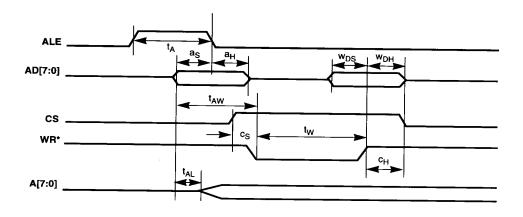

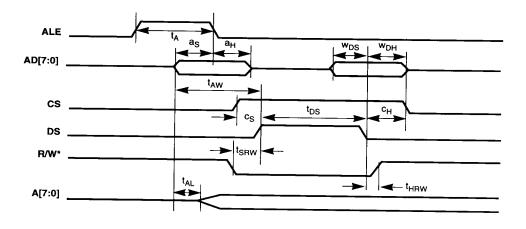

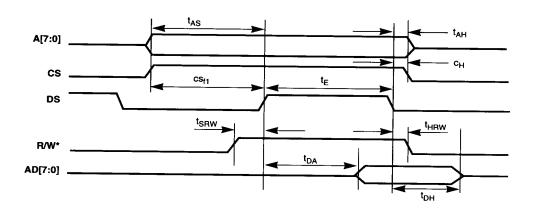

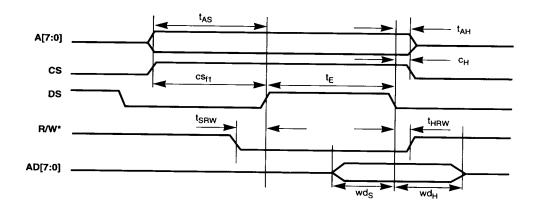

The microcontroller-to-CL-SH360 communication path is a multiplexed/non-multiplexed address and data bus similar to that provided by the Intel 8051 and the Motorola 68HC11 class of controllers. The CL-SH360 can use either the Intel or the Motorola method of data control. When the Intel interface is selected, the WR\*/R/W\* Signal (Pin 7/56) acts as a write strobe. In the case of a Write Operation, this write strobe provides the timing and control for the data transfers. Similarly, in the case of a Read Operation, the RD\*/DS Signal (Pin 8/57) acts as a read strobe to provide the timing and control for the data transfers.

The BD6/I/MC\* Signal (Pin 99/48) defaults to Intel Mode after reset, with no external resistor. An external pull-down resistor is required to operate in the Motorola Interface Mode. For the Motorola configuration, the WR\*/R/W\* Signal (Pin 7/56) is used only to determine the direction of the data transfer. When the input to this signal is high, a Read Operation is in progress; when it is low, a Write Operation is in progress. Data timing is derived with respect to the RD\*/DS Signal (Pin 8/ 57). In the case of a Read Operation, the rising (leading) edge of the RD\*/DS Signal (Pin 8/57) indicates when the CL-SH360 can start driving the data bus. In a Write Operation, the falling (trailing) edge is used by the CL-SH360 to latch the data from the microcontroller address/data bus.

The CL-SH360 uses the BD7/M/NM\* Signal (Pin 100/49) after a reset to select a multiplexed or a non-multiplexed address and data path. The BD7/M/NM\* Signal (Pin 100/49) has an internal pull-down. If this pin is connected to a pull-up resistor after reset, the CL-SH360 will recognize this condition and will automatically select Multiplexed Mode. Following reset, if the BD7/M/NM\* Signal (Pin 100/49) is only connected to the Data Port of the buffer RAM without an external pull-up resistor, the CL-SH360 will recognize the low level (internal pull-down) on this signal and select Non-multiplexed Mode.

The CL-SH360 decodes addresses from 40H to FFH. To prevent erroneous operations, the controller design should reserve the decoding of Addresses 40H to FFH for the controller chip only. The PC Interface Register File is mapped to 40H-47H or 60H-67H. Upon a local reset (RST\* — Pin 34/83), the access to the PC Register File is disabled until the Register File base address is programmed by the local microcontroller; this avoids contention on the read cycle, or errors on the write cycle.

The CL-SH360 has a programmable interrupt circuit. Four interrupt registers provide the status and mask programmability for interrupt sources. The programmable interrupt features include individual masks, a global enable, and an open-drain or push-pull output driver. The interrupt status registers may also be used as a focal point for microcontroller control when the CL-SH360 is being used in a Polled Mode. The interrupt sources are: PC Selection, PC Transfer Done, PC Reset, PC Transfer Overrun, Host Transfer Status Read Detected, Index Past, Sector Past, Disk Data Transfer Detected, ECC/Uncorrectable Error, Sequencer Stopped, Input Detected, and Sequencer Output Detected.

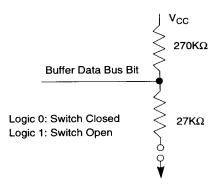

The processor-readable switches are multiplexed with the buffer data bus. These switches must be installed with relatively high-impedance pull-ups and pull-downs so that the resistor impedance does not affect the buffer performance. The processor accesses these switches by reading Registers 68H or 70H, with the MOE\* Disable Bit set (Register 52H, Bit 0).

#### Switch Example

#### 4.1.1 Access to External Buses

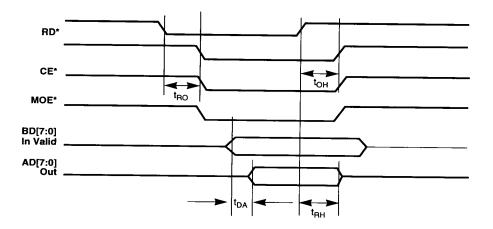

In addition to the normal data transfer operations, the CL-SH360 also supports microcontroller access to the buffer memory by addressing Registers 68H and 70H.

# 4.1.1.1 Microcontroller Scheduled Access to Buffer