# VG-100A CMOS V40™ MULTI-FUNCTION PERIPHERAL CHIP

February 1988

| Features                                        |

|-------------------------------------------------|

| ☐ Dynamic RAM controller                        |

| ☐ Refresh logic                                 |

| ☐ Peripheral I/O address decoder                |

| ☐ Memory address decoder (RAM and ROM)          |

| ☐ NMI control register                          |

| ☐ Speaker clock generator                       |

| ☐ 1.5 micron CMOS technology                    |

| G 64 pin shrink DIP package (optional flatnack) |

### **Description**

The VG-100A integrates the DRAM control and refresh functions, NMI control register, and address decoding functions. When used with the companion VG-200A and NEC's V40 microprocessor, a functionally compatible PC can be integrated by using just these three chips plus minimum glue logic.

### **Pin Description**

| Symbol              | Function                                                                                                                                                                                                                                                                             |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUFOFF              | This active high output should be connected to the BUFOFF input of the VG-200A. Signal goes high when any of the following I/O hex address are accessed: 00-0F, 20-2F, 40-4F, 60-6F, 72, 73, 80-8F, A0-AF, C0-CF, or E0-EF. A CPU access to F0000-FFFFF will also force BUFOFF high. |

| AD0-AD7             | V40 address/data lines 0-7. CMOS inputs.                                                                                                                                                                                                                                             |

| A8-A15              | V40 addresses 8-15. CMOS inputs.                                                                                                                                                                                                                                                     |

| A16-A19             | V40 address/status lines 16-19. CMOS inputs.                                                                                                                                                                                                                                         |

| MAD-MA7<br>(Note 1) | Multiplexed RAS/CAS and refresh addresses for DRAM. During RAS, CPU addresses A0-A7 are sent out; during CAS, addresses A9-A16 are transmitted; during a refresh, addresses A0-A7 are sent. These outputs must be buffered.                                                          |

| REFRO               | Refresh request from V40. CMOS input.                                                                                                                                                                                                                                                |

| MERROR              | Parity error output from VG-200A. Includes error results for both on-board and expansion RAMs. CMOS input.                                                                                                                                                                           |

| GND                 | System ground.                                                                                                                                                                                                                                                                       |

| CPUCLK              | V40 CMOS clock output; actually system clock divided by 2.                                                                                                                                                                                                                           |

| EXTRDY              | Ready line from expansion boards. A low indicates not ready. TTL input with internal pull-up.                                                                                                                                                                                        |

| RAS                 | Active low row select. Goes low during memory cycles and refresh cycles. Active from 0 to 1 Mbyte. Should be connected to all RAMs directly without decoding, although buffering is required.                                                                                        |

| CAS<br>(Note 2)     | Active low column select. Goes low during memory cycles and high during refresh. Active from 0 to 1 Mbyte. External bank decoding and buffering required.                                                                                                                            |

| Symbol | Function                                                                                                                                                                                                                                                                                                                                                                  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RD73   | Goes high when I/O $73_H$ is read. I/O $73_H$ is the internal read/write register of the VG-100A used by the BIOS during emulation. This output should be OR'd with BUFEN of the V40 to control the transceiver between the AD and local data bus.                                                                                                                        |

| RD72   | Goes low when I/O 72 <sub>H</sub> is read. This address is provided for a system configuration register. If a basic system is designed as shown in the App Note, this register is not needed, and DB7 should be pulled up. A high on DB7 when I/O 72 <sub>H</sub> is read indicates to the BIOS that there is no register. If the register is present, DB7 should be low. |

| SW2    | A high indicates that the 8087 co-processor chip is installed; a low indicates that it is not. CMOS input.                                                                                                                                                                                                                                                                |

| NMI    | Sent to V40 NMI input pin. This is an OR'ing of RAM parity results, 8087 interrupt, EXTNMI, and other proprietary logic. A high indicates an NMI, and the output will be 6 clock pulses wide regardless of the input pulse width.                                                                                                                                         |

| IORD   | Active low. CMOS I/O read control from the V40.                                                                                                                                                                                                                                                                                                                           |

| IOWR   | Active low. CMOS I/O write control from the V40.                                                                                                                                                                                                                                                                                                                          |

| MA8    | Multiplexed RAS/CAS and refresh address for DRAM. During RAS, CPU address A8 is sent out; during CAS, address A17 is transmitted; during a refresh, refresh address A8 is sent. This output must be buffered.                                                                                                                                                             |

| MA9    | Multiplexed RAS/CAS and refresh address for DRAM. During RAS, CPU address A18 is sent out; during CAS, address A19 is transmitted; during a refresh, MA9 is a don't care. This output must be buffered.                                                                                                                                                                   |

| PPSEL  | This directs one of two internally-decoded printer port addresses to appear on PRTCS. When low, I/O addresses 3BC <sub>H</sub> -3BF <sub>H</sub> will appear, and when high, addresses 378 <sub>H</sub> -37F <sub>H</sub> . CMOS input with internal pullup resistor.                                                                                                     |

| INT87  | 8087 interrupt; enabled by SW2. A high on this TTL input will cause an NMI.                                                                                                                                                                                                                                                                                               |

| EXTNMI | Extra NMI input: TTL with internal pullup. OR'd with other NMI inputs, and not controlled by NMI register.  Must be qualified with V40 control signal (IORD, IOWR, MRD, MWR).                                                                                                                                                                                             |

| BS1    | V40 CMOS bus status input. High = write; low = read.                                                                                                                                                                                                                                                                                                                      |

| BS2    | V40 CMOS bus status input. High $=$ memory; low $=$ 1/0.                                                                                                                                                                                                                                                                                                                  |

| LOROM  | Active low. Decoded memory address from F0000 to F7FFF. Intended for OEM ROM.                                                                                                                                                                                                                                                                                             |

| HIROM  | Active low. Decoded memory address from F8000 to FFFFF, Intended for BIOS ROM.                                                                                                                                                                                                                                                                                            |

| PRTCS  | Active low; Decoded I/O address for printer. See PPSEL.                                                                                                                                                                                                                                                                                                                   |

| RDY    | Ready output to V40                                                                                                                                                                                                                                                                                                                                                       |

|        |                                                                                                                                                                                                                                                                                                                                                                           |

# Pin Description (cont)

| Symbol          | Function                                                                                                                     |

|-----------------|------------------------------------------------------------------------------------------------------------------------------|

| PPICS           | Active low: Decoded I/O address (60 <sub>H</sub> -62 <sub>H</sub> — same as IBM) for 8255 controller or equivalent (VG-200A) |

| RESET           | Active high, TTL input. Low=run; high=reset.                                                                                 |

| SYSASTB         | Active high, TTL. The result of the OR'ing of the V40 ASTB and the 8087 ASTB.                                                |

| TCLK            | The CPUCLK divided by 6. Used by the V40 as TCU input clock. Output is 1.1913 MHz required for IBM compatibility.            |

| MRD             | Active low, CMOS. Memory read control from V40.                                                                              |

| MWR             | Active low, CMOS. Memory write control from V40.                                                                             |

| SA16-SA19       | System addresses. The result of input pins A16-A19 being latched internally by SYSASTB.                                      |

| V <sub>CC</sub> | 5 V power supply.                                                                                                            |

#### Notes:

- (1) Address multiplexer is designed to use either 256K x 1 or 1M x 1 DRAMS

- (2) If three banks of 256K or 1M DRAMs are located on the local bus, caution must be used when decoding for CAS. The standard PC display adapter resides in B0000-BFFFF and the EGA adapter starts at A0000. Therefore, decoding for CAS must insure that the DRAM is disabled when the display adapter is addressed. If 1M DRAMs are used, care must be taken to avoid bus conflicts above C0000 as well.

# **Absolute Maximum Ratings**

Storage temperature range

| 1A - 25°C                   |                                   |

|-----------------------------|-----------------------------------|

| Power supply voltage        | −0.5 to +7 V                      |

| Input voltage               | -0.5 to (V <sub>CC</sub> + 0.5) V |

| Output current              | 20 mA                             |

| Operating temperature range | -40 to +85°C                      |

Comment: Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage.

-65 to +150°C

### **Pin Configuration**

| BUF OFF  | 1  | 64 | b vcc          |

|----------|----|----|----------------|

| AD0 🖂    | 2  | 63 | □ SA19         |

| AD1 🗖    | 3  | 62 | □ SA18         |

| AD2      | 4  | 61 | ☐ SA17         |

| AD3 🗖    | 5  | 60 | □ SA16         |

| AD4 🗆    | 6  | 59 | D MWR          |

| AD5 🗖    | 7  | 58 | MRD            |

| AD6      | 8  | 57 | TCLK           |

| AD7      | 9  | 56 | ☐ SYSASTB      |

| A8 🗖     | 10 | 55 | □ RESET        |

| A9 🗖     | 11 | 54 | PPICS          |

| A10 🗖    | 12 | 53 | ☐ PRTCS        |

| A11 🗖    | 13 | 52 | HIROM          |

| A12 🗖    | 14 | 51 | ☐ <u>LOROM</u> |

| A13 🗖    | 15 | 50 | D BS2          |

| A14 🗖    | 16 | 49 | D BS1          |

| A15 🗖    | 17 | 48 | EXTNMI         |

| A16 🗖    | 18 | 47 | □ INT87        |

| A17 🗖    | 19 | 46 | D PPSEL        |

| A18 📮    | 20 | 45 | □ MA9          |

| A19 🗖    | 21 | 44 | □ MA8          |

| MAO 🗖    | 22 | 43 | □ IOWR         |

| MA1 🗖    | 23 | 42 | ORD            |

| MA2 🗆    | 24 | 41 | RDY            |

| MA3 🗆    | 25 | 40 | D NWI          |

| MA4 🗆    | 26 | 39 | □ SW2          |

| MA5 🗆    | 27 | 38 | □ RD72         |

| MA6      | 28 | 37 | □ RD73         |

| MA7 🗆    | 29 | 36 | CAS            |

| REFRQ 🗆  | 30 | 35 | □ RAS          |

| MERROR 🗆 | 31 | 34 | □ EXTRDY       |

| GND ☐    | 32 | 33 | CPUCLK         |

|          |    |    |                |

|          |    |    |                |

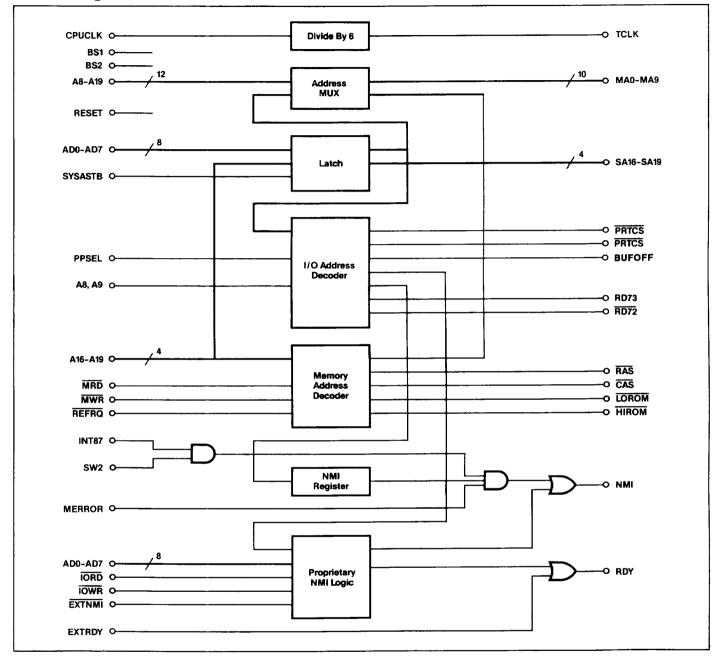

### **Block Diagram**

# **Recommended Operating Conditions**

|                                     |                                | When in             | nits<br>terfacing<br>CMOS: | When interfacing with TTL: |                 |      |

|-------------------------------------|--------------------------------|---------------------|----------------------------|----------------------------|-----------------|------|

| Parameter                           | Symbol                         | Min                 | Max                        | Min                        | Max             | Unit |

| Power supply voltage                | V <sub>CC</sub>                | 4.5                 | 5.5                        | 4.75                       | 5.25            | V    |

| Operating temperature               | Topt                           | -40                 | +85                        | 0                          | +70             | °C   |

| Low-level input voltage             | V <sub>IL</sub>                | 0                   | 0.3 V <sub>CC</sub>        | 0                          | 0.8             | ٧    |

| High-level input voltage            | V <sub>IH</sub>                | 0.7 V <sub>CC</sub> | vcc                        | 2.0                        | V <sub>CC</sub> | ٧    |

| Positive Schmitt trigger voltage    | V <sub>P</sub>                 | 2.2                 | 3.6                        | 1.3                        | 2.2             | ٧    |

| Negative Schmitt<br>trigger voltage | V <sub>N</sub>                 | 0.9                 | 2.8                        | 0.7                        | 1.7             | ٧    |

| Hysteresis                          | VΗ                             | 0.3                 | 1.5                        | 0.3                        | 1.5             | ٧    |

| Rise/fall time                      | t <sub>r</sub> /t <sub>f</sub> | 0                   | 10                         | 0                          | 10              | ns   |

### **DC** Characteristics

CMOS interface levels: V $_{CC}$  = 5.0 V  $\pm$  10%; T $_{opt}$  = - 40 to + 85 °C TTL interface levels: V $_{CC}$  = 5.0 V  $\pm$ 5%; T $_{opt}$  = 0 to +70 °C

|                                          |                 | Limits                   |      |     |          | Test                     |  |

|------------------------------------------|-----------------|--------------------------|------|-----|----------|--------------------------|--|

| Parameter                                | Symbol          | Min Typ                  |      | Max | Unit     | Conditions               |  |

| Quiescent current                        | IQ              |                          | 0.1  | 200 | μΑ       | $V_{1N} = V_{CC}$ or GND |  |

| Off-state output<br>leakage current      | lock            |                          |      | 10  | μΑ       | $V_0 = V_{CC}$ or GND    |  |

| Operating current                        | Icc             |                          | 3    |     | μΑ       | 1 MHz/cell               |  |

| Input current                            | IIN             |                          | 10-5 | 10  | μΑ       | $V_{IN} = V_{CC}$ or GND |  |

| Low-level<br>output current<br>(Note 1)  | l <sub>OL</sub> | 4<br>4.3                 | 11   |     | mA<br>mA | CMOS<br>TTL              |  |

| High-level<br>output current<br>(Note 2) | l <sub>ОН</sub> | 4<br>4.3                 | 7    |     | mA<br>mA | CMOS<br>TTL              |  |

| Low-level output voltage                 | V <sub>OL</sub> | _                        |      | 0.1 | ٧        | $I_0 = 0 \text{ mA}$     |  |

| High-level output voltage                | V <sub>OH</sub> | V <sub>CC</sub><br>- 0.1 |      |     | ٧        | $I_0 = 0 \text{ mA}$     |  |

#### Notes:

- (1)  $V_{OL} = 0.4 V$ .

- (2)  $V_{OH} = V_{CC} 0.4 V$ .

# **AC Characteristics**

CMOS interface levels:  $V_{CC} = 5.0~V \pm 10\%$ ;  $T_{opt} = -40~to +85~C$  TTL interface levels:  $V_{CC} = 5.0~V \pm 5\%$ ;  $T_{opt} = 0~to +70~C$

|                             |                  | Limits   |     |     |            | Test                   |  |

|-----------------------------|------------------|----------|-----|-----|------------|------------------------|--|

| Parameter                   | Symbol           | Min Typ  |     | Max | Unit       | Conditions             |  |

| Toggle frequency            | f <sub>clk</sub> | 70<br>75 |     |     | MHz<br>MHz | CMOS<br>TTL            |  |

| Internal gate<br>delay time | tpD              |          | 1.4 |     | ns         | F/0 = 3;<br>L = 3 mm   |  |

| Input buffer delay time     | t <sub>PD</sub>  |          | 2.0 |     | ns         | F/0 = 3;<br>L = 3 mm   |  |

| Output buffer delay time    | t <sub>PD</sub>  |          | 4.5 |     | ns         | C <sub>L</sub> = 15 pF |  |

| Output rise time            | t <sub>r</sub>   |          | 3.5 |     | ns         | $C_L = 15 pF$          |  |

| Output fall time            | t <sub>f</sub>   |          | 2.5 |     | ns         | $C_L = 15 pF$          |  |

# **Timing Characteristics**

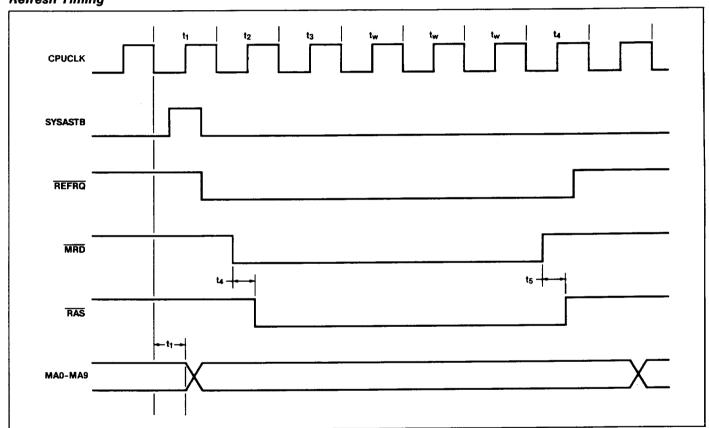

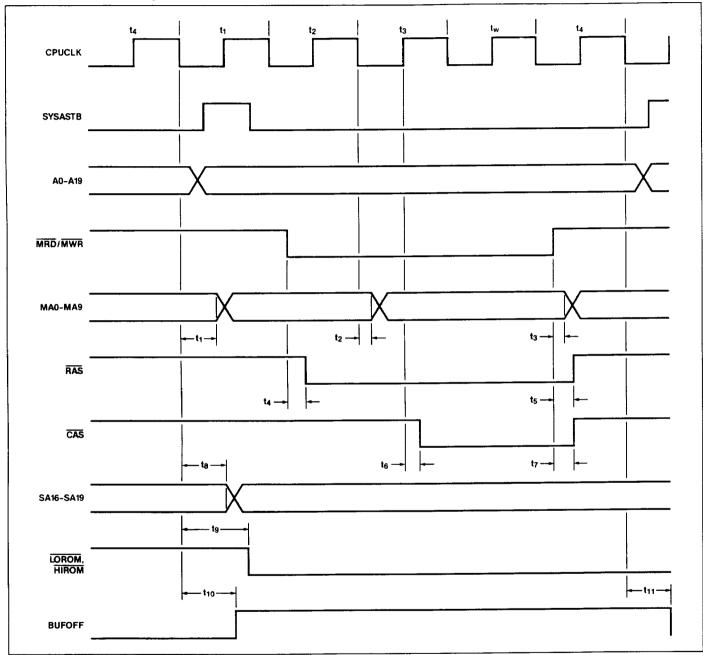

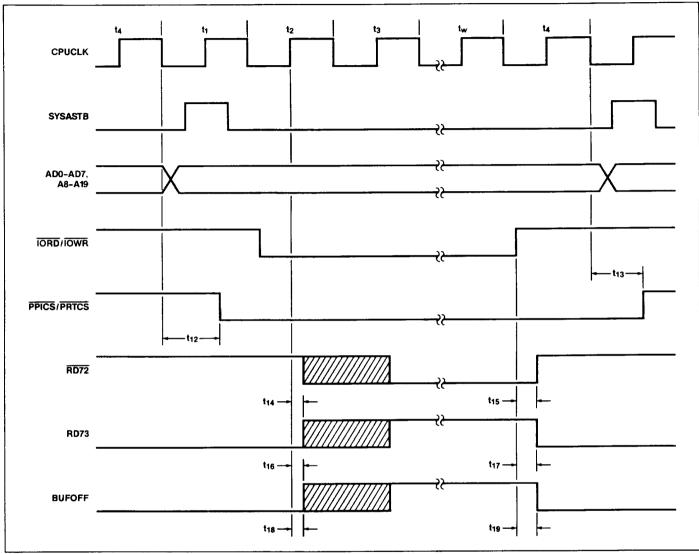

|                                     |                 | Lin |     |      |

|-------------------------------------|-----------------|-----|-----|------|

| Parameter                           | Symbol          | Min | Max | Unit |

| MA0-MA9 (RAS) from t <sub>4</sub> ↓ | t <sub>1</sub>  | 14  | 87  | ns   |

| MA0-MA9 (CAS) from t <sub>2</sub> ↓ | t <sub>2</sub>  | 7   | 34  | ns   |

| MAO-MA9 hold from MRD/MWR1          | t <sub>3</sub>  | 7   | 40  | ns   |

| RAS from MRD/MWR                    | t <sub>4</sub>  | 3   | 19  | ns   |

| RAST from MRD/MWRT                  | t <sub>5</sub>  | 3   | 19  | ns   |

| CAS↓ from t <sub>3</sub> †          | t <sub>6</sub>  | 6   | 26  | ns   |

| CAST from MRD/MWR                   | t <sub>7</sub>  | 6   | 31  | ns   |

| SA16-SA19 from t <sub>4</sub> ↓     | tg              | 17  | 84  | ns   |

| LOROM/HIROM from t <sub>4</sub> ↓   | t <sub>9</sub>  | 17  | 99  | ns   |

| BUF0FF1 from t <sub>4</sub> I       | t <sub>10</sub> | 16  | 96  | ns   |

| BUF0FF↓ from t4↓                    | t <sub>11</sub> | 16  | 96  | ns   |

| PPICS/PRTCS↓ from t4↓               | t <sub>12</sub> | 19  | 100 | ns   |

| PPICS/PRTCS1 from t <sub>4</sub> 1  | t <sub>13</sub> | 19  | 100 | ns   |

| RD72↓ from CPUCLK↑                  | t <sub>14</sub> | 9   | 43  | ns   |

| RD721 from IORD/IOWR1               | t <sub>15</sub> | 7   | 32  | ns   |

| RD731 from CPUCLK1                  | t <sub>16</sub> | 10  | 48  | ns   |

| RD73↓ from IORD/IOWR↑               | t <sub>17</sub> | 8   | 37  | ns   |

| BUFOFF† from CPUCLK†                | t <sub>18</sub> | 8   | 42  | ns   |

| BUF0FF↓ from IORD/IOWR              | t <sub>19</sub> | 7   | 31  | ns   |

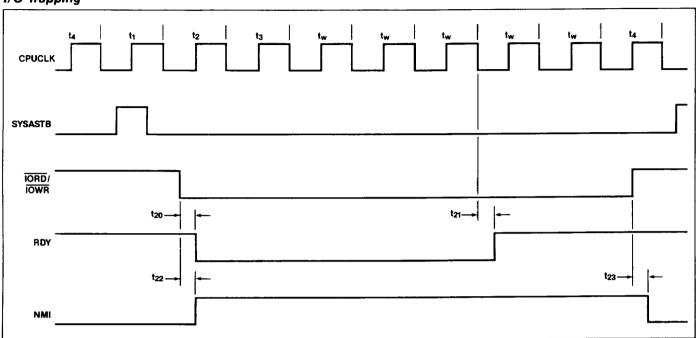

| RDY↓ from IORD/IOWR                 | t <sub>20</sub> | 5   | 29  | ns   |

| RDY1 from CPUCLK                    | t <sub>21</sub> | 7   | 35  | ns   |

| NMI1 from IORD/IOWR                 | t <sub>22</sub> | 6   | 30  | ns   |

| NMI from IORD/IOWR1                 | t <sub>23</sub> | 6   | 30  | ns   |

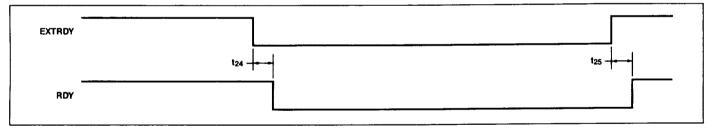

| RDY↓ from EXTRDY↓                   | t <sub>24</sub> | 5   | 25  | ns   |

| RDYT from EXTRDYT                   | t <sub>25</sub> | 5   | 25  | ns   |

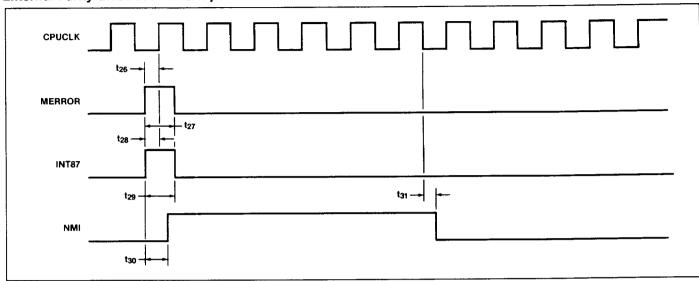

| MERROR† setup to CPUCLK†            | t <sub>26</sub> | 24  |     | ns   |

| MERROR minimum pulse width          | t <sub>27</sub> | 20  |     | ns   |

# **Timing Characteristics**

|                                      |                 | Limits |     |      |

|--------------------------------------|-----------------|--------|-----|------|

| Parameter                            | Symbol          | Min    | Max | Unit |

| INT871 setup to CPUCLK1              | t <sub>28</sub> | 28     |     | ns   |

| INT87 minimum pulse width            | t <sub>29</sub> | 20     | ,   | ns   |

| NMIT from MERROR, INT87              | t <sub>30</sub> | 6      | 29  | ns   |

| NMI↓ from CPUCLK                     | t <sub>31</sub> | 7      | 34  | ns   |

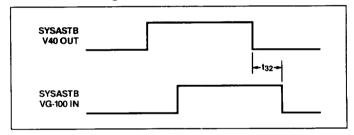

| SYSASTB delay, V40 out to VG-100A in | t <sub>32</sub> |        | 20  | ns   |

# **Timing Waveforms**

# Refresh Timing

### RAS/CAS and ROM Chip Select

# I/O Chip Selects

# I/O Trapping

### **External Ready Timing**

### External Parity Error/8087 Interrupt

### SYSASTB Timing

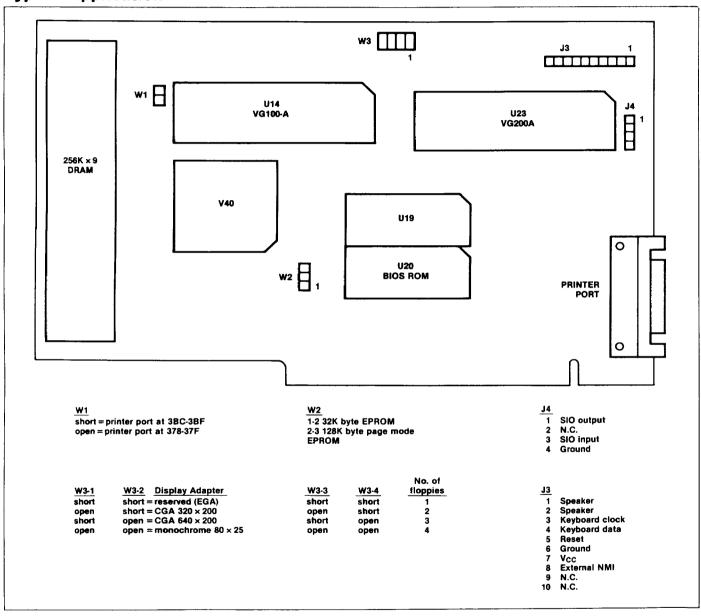

### **Applications Information**

The following figure is an actual size representation of a fully functional IBM PC-compatible computer, built using the NEC V40 microprocessor and the Vadem VG-100A and VG-200A.

### Typical Application

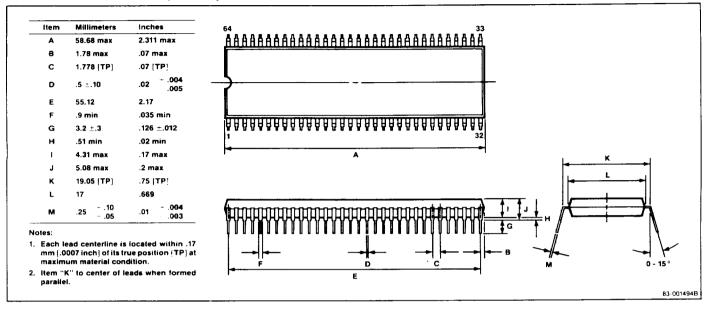

### **Physical Dimensions**

### 64-Pin Plastic Shrink DIP (750 mil)

#### VADEM

1885 Lundy Avenue, Suite 201 San Jose, CA 95131 U.S.A. Telephone (408) 943-9301 Telex: 887-591 (VADEM SNTA UD)

Fax: (408) 943-9735

© 1988 Vadem/Printed in U.S.A.

#### Notice

Vadem reserves the right to make changes in the device specifications identified in this publication without notice. Vadem advises its customers to obtain the latest version of these specifications before ordering, to verify that the information they are using is correct.

In the absence of written agreement to the contrary, Vadem assumes no liability for Vadem application assistance, customer's product design, or infringement of patents or copyrights of third parties by or arising from use of semiconductor devices described herein. Nor does Vadem warrant or represent that any license, either expressed or implied, is granted under any patent right, copyright, or any other intellectual property right of Vadem's covering or relating to any combination, machine, or process in which each semiconductor devices might be or are used.

IBM and PC are registered trademarks of International Business Machines Corporation.

NEC is a registered trademark of NEC Electronics Inc. V40 is a trademark of NEC Electronics Inc.

VG-100A and VG-200A are trademarks of Vadem Inc.

028825K

014882 1 1