## **PRELIMINARY**

# COP888CFMH Single-Chip microCMOS Microcontroller Emulator

## General Description

The COP888CFMH hybrid emulator is a member of the COPS™ microcontroller family. The device is a two chip system in a dual cavity package. Within the package is the COP888CF and a UV-erasable 8k EPROM with port recreation logic code executes of the EPROM. This device is offered in three packages: 44-pin LDCC, 40-pin DIP and 28-pin DIP. All packages contain transparent windows which allows the EPROM to be erased and re-programmed.

The COP888CFMH is a fully static part, fabricated using double-metal silicon gate microCMOS technology. Features include an 8-bit memory mapped architecture, MICRO-WIRE/PLUS™ serial I/O, two 16-bit timer/counters supporting three modes (Processor Independent PWM generation. External Event counter, and Input Capture mode capabilities), an 8-channel, 8-bit A/D converter with both differential and single ended modes, and two power savings modes (HALT and IDLE), both with a multi-sourced wakeup/interrupt capability. This multi-sourced interrupt capability may also be used independent of the HALT or IDLE modes. Each I/O pin has software selectable configurations. The COP888CFMH operates over a voltage range of 4.5V to 5.5V. High throughput is achieved with an efficient, regular instruction set operating at a maximum of 1 µs per instruction rate.

The COP888CFMH is primarily intended as a prototyping design tool. The Electrical Performance Characteristics are not tested but are included for reference only.

### **Features**

- Low cost 8-bit microcontroller

- Fully static CMOS, with low current drain

- Two power saving modes: HALT and IDLE

- 1 µs instruction cycle time

- 8192 bytes on-board EPROM

- 128 bytes on-board RAM

- Single supply operation: 4.5V-5.5V

- 8-Channel A/D converter with prescaler and both differential and single ended modes

- MICROWIRE/PLUS serial I/O

- WATCHDOG™ and Clock Monitor logic

- Idle Timer

- Multi-Input Wakeup (MIWU) with optional interrupts (8)

- Ten multi-source vectored interrupts servicing

- External Interrupt

- Idle Timer T0

- Two Timers each with 2 interrupts

- MICROWIRE/PLUS

- Multi-Input Wake Up

- Software Trap

- Default VIS

- Two 16-bit timers, each with two 16-bit registers supporting:

- Processor Independent PWM mode

- External Event counter mode

- Input Capture mode

- 8-bit Stack Pointer SP (stack in RAM)

- Two 8-bit Register Indirect Data Memory Pointers (B and X)

- Versatile instruction set wih True bit manipulation

- Memory mapped I/O

- BCD arithmetic instructions

- Package: 44 LDCC with 37 I/O pins 40 DIP with 33 I/O pins 28 DIP with 21 I/O pins

- Software selectable I/O options

- TRI-STATE® Output

- Push-Pull Output

- Weak Pull Up Input

- High Impedance Input

- Schmitt trigger inputs on ports G and L

- Form fit and function emulation device for the COP888CF

- Real time emulation and full program debug offered by National's Development Systems

# **Ordering Information**

| Hybrid Emulator | Package Type | Part Emulated with<br>Crystal Oscillator Option |

|-----------------|--------------|-------------------------------------------------|

| COP888CFMHD-x   | 40-Pin DIP   | COP888CF-XXX/N                                  |

| COP888CFMHEL-x  | 44-Pin LDCC  | COP888CF-XXX/V                                  |

| COP884CFMHD-x   | 28-Pin DIP   | COP884CF-XXX/N                                  |

x indicates crystal option; for applications requiring R/C option check with local sales representative.

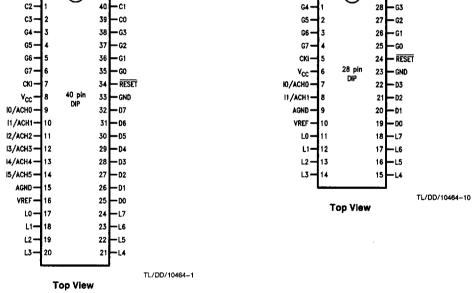

### **Connection Diagrams Plastic Chip Carrier** 288222222882 3 2 1 44 43 42 41 40 CKI V<sub>CC</sub> 38 - RESET IO/ACHO 37 - GND 11/ACH1 -36 - 07 12/ACH2 -35 **–** D6 44 pin LDCC 13/ACH3 -34 · D5 14/ACH4 -33 **–** D4 15/ACH5 -32 - D3 16/ACH6 - 15 31 - D2 17/ACH7 - 16 30 - D1 AGND -- 20 18 19 20 21 22 23 24 25 26 27 28 7 2 2 7 TL/DD/10464-2 **Top View Dual-In-Line Package Dual-In-Line Package** C2 40 28 C3 -39 27 -00 G5 -- G2 38 •G3 G6 26 -G1 G5 · 37 - GO -G2 G7 -25 G6 36 -G1 CKI-24 - RESET G7 -- GO 28 pin 35 23 Vcc-- GND CK) 34 - RESET 10/ACH0-22 D3 40 pin 33 - GND II/ACH1-21 - D2 Vcc.

FIGURE 1. COP888CFMH Connection Diagrams

# Connection Diagrams (Continued)

## **COP888CFMH Pinouts**

|                        | ,                 | COP888CFMI       | Fillouis         |               |               |                |

|------------------------|-------------------|------------------|------------------|---------------|---------------|----------------|

| Port                   | Туре              | Alternate<br>Fun | Alternate<br>Fun | 28-Pin<br>DIP | 40-Pin<br>DIP | 44-Pin<br>LDCC |

| LO                     | 1/0               | MIWU             |                  | 11            | 17            |                |

| L1                     | 1/0               | MIWU             |                  | 12            | 18            |                |

| L2                     | 1/0               | MIWU             |                  | 13            | 19            | 19             |

| L3                     | 1/0               | MIWU             |                  | 14            | 20            | 20             |

| L4                     | 1/0               | MIWU             | T2A              | 15            | 21            | 25             |

| L5                     | 1/0               | MIWU             | T2B              | 16            | 22            | 26             |

| L6                     | 1/0               | MIWU ·           |                  | 17            | 23            | 27             |

| L7                     | 1/0               | MIWU             |                  | 18            | 24            | 28             |

| G0                     | 1/0               | INT              |                  | 25            | 35            | 39             |

| G1                     | WDOUT             |                  |                  | 26            | 36            | 40             |

| G2                     | 1/0               | T1B              |                  | 27            | 37            | 41             |

| G3                     | 1/0               | T1A              |                  | 28            | 38            | 42             |

| G4                     | 1/0               | so               |                  | 1             | 3             | 3              |

| G5                     | 1/0               | SK               |                  | 2             | 4             | 4              |

| G6                     | 1                 | SI               |                  | 3             | 5             | 5              |

| G7                     | I/CKO             | HALT RESTART     |                  | 4             | 6             | 6              |

| 10                     | 1                 | ACH0             |                  | 7             | 9             | 9              |

| 11                     | 1                 | ACH1             |                  | 8             | 10            | 10             |

| 12                     | 1                 | ACH2             |                  |               | 11            | 11             |

| 13                     | 1                 | ACH3             |                  | ĺ             | 12            | 12             |

| 14                     | ļ                 | ACH4             |                  |               | 13            | 13             |

| 15                     |                   | ACH5             |                  |               | 14            | 14             |

| 16                     |                   | ACH6             |                  |               |               | 15             |

| 17                     | 1                 | ACH7             |                  |               |               | 16             |

| D0                     | 0                 |                  |                  | 19            | 25            | 29             |

| D1                     | 0                 |                  |                  | 20            | 26            | 30             |

| D2                     | 0                 |                  |                  | 21            | 27            | 31             |

| D3                     | 0                 |                  |                  | 22            | 28            | 32             |

| D4                     | 0                 |                  |                  |               | 29            | 33             |

| D5                     | 0                 |                  |                  |               | 30            | 34             |

| D6                     | 0                 |                  |                  |               | 31            | 35             |

| D7                     | 0                 |                  |                  |               | 32            | 36             |

| C0                     | 1/0               |                  |                  |               | 39            | 43             |

| C1                     | 1/0               |                  |                  |               | 40            | 44             |

| C2                     | 1/0               |                  |                  |               | 1             | 1              |

| C3                     | 1/0               |                  |                  |               | 2             | 2              |

| C4                     | 1/0               |                  |                  |               |               | 21<br>22       |

| C5                     | 1/0               |                  |                  |               |               | 22             |

| C6                     | 1/O<br>1/O        |                  |                  |               |               | 23             |

| C7                     |                   |                  |                  | 40            | 40            |                |

| V <sub>REF</sub>       | +V <sub>REF</sub> |                  |                  | 10<br>9       | 16<br>15      | 18<br>17       |

| AGND/GND               | AGND              |                  |                  | 6             | 8             | 8              |

| V <sub>CC</sub><br>GND |                   |                  |                  | 23            | 33            | 37             |

| CKI                    |                   |                  |                  | 5             | 7             | 7              |

| RESET                  |                   |                  |                  | 24            | 34            | 38             |

| HESET                  |                   | l                | i                |               |               |                |

Storage Temperature Range

## **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage (V<sub>CC</sub>) Voltage at Any Pin -0.3V to  $V_{CC} + 0.3V$ Total Current into V<sub>CC</sub> Pin (Source) 100 mA Total Current out of GND Pin (Sink) 110 mA Note: Absolute maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.

The following AC and DC Electrical Characteristics are not tested but are for reference only.

## DC Electrical Characteristics $0^{\circ}C \le T_A \le +70^{\circ}C$ unless otherwise specified

-65°C to +140°C

| Parameter                             | Conditions                                     | Min                 | Тур                  | Max                 | Units       |

|---------------------------------------|------------------------------------------------|---------------------|----------------------|---------------------|-------------|

| Operating Voltage                     |                                                | 4.5                 |                      | 5.5                 | ٧           |

| Power Supply Ripple (Note 1)          | Peak-to-Peak                                   |                     |                      | 0.1 V <sub>CC</sub> | >           |

| Supply Current (Note 2)               |                                                |                     |                      |                     |             |

| CKI = 10 MHz                          | $V_{CC} = 5.5V, t_{c} = 1 \mu s$               |                     |                      | 25                  | mA          |

| HALT Current (Note 3)                 | $V_{CC} = 5.5V$ , CKI = 0 MHz                  |                     | 250                  |                     | μΑ          |

| IDLE Current                          |                                                |                     |                      |                     |             |

| CKI = 10 MHz                          | $V_{CC} = 5.5V, t_{c} = 1 \mu s$               |                     |                      | 15                  | mA          |

| Input Levels                          |                                                |                     |                      |                     |             |

| RESET                                 |                                                |                     |                      |                     |             |

| Logic High<br>Logic Low               |                                                | 0.8 V <sub>CC</sub> |                      | 0.01/               | <b>&gt;</b> |

| CKI (External and Crystal Osc. Modes) |                                                |                     |                      | 0.2 V <sub>CC</sub> | ٧           |

| Logic High                            |                                                | 0.7 V <sub>CC</sub> |                      |                     | V           |

| Logic Low                             |                                                | • •                 |                      | 0.2 V <sub>CC</sub> | v           |

| All Other Inputs                      |                                                |                     |                      |                     | _           |

| Logic High                            |                                                | 0.7 V <sub>CC</sub> |                      |                     | ٧           |

| Logic Low                             |                                                |                     |                      | 0.2 V <sub>CC</sub> | ٧           |

| Hi-Z Input Leakage                    | V <sub>CC</sub> = 5.5V                         | -2                  |                      | +2                  | μΑ          |

| nput Pullup Current                   | $V_{CC} = 5.5V$                                | 40                  |                      | 250                 | μА          |

| G and L Port Input Hysteresis         |                                                |                     | 0.05 V <sub>CC</sub> |                     | ٧           |

| Output Current Levels                 |                                                |                     |                      |                     |             |

| D Outputs                             |                                                |                     |                      |                     |             |

| Source                                | $V_{CC} = 4.5V, V_{OH} = 3.3V$                 | 0.4                 |                      |                     | mA          |

| Sink                                  | $V_{CC} = 4.5V, V_{OL} = 1V$                   | 10                  |                      |                     | mA          |

| All Others                            |                                                |                     |                      |                     |             |

| Source (Weak Pull-Up Mode)            | $V_{CC} = 4.5V, V_{OH} = 2.7V$                 | 10                  |                      | 100                 | μΑ          |

| Source (Push-Pull Mode)               | $V_{CC} = 4.5V, V_{OH} = 3.3V$                 | 0.4                 |                      |                     | mA          |

| Sink (Push-Pull Mode)                 | V <sub>CC</sub> = 4.5V, V <sub>OL</sub> = 0.4V | 1.6                 |                      |                     | mA          |

| TRI-STATE Leakage                     | V <sub>CC</sub> = 4.5V                         | -2                  |                      | +2                  | μА          |

Note 1: Rate of voltage change must be less then 0.5 V/ms.

Note 2: Supply current is measured after running 2000 cycles with a square wave CKI input, CKO open, inputs at rails and outputs open.

Note 3: The HALT mode will stop CKI from oscillating in the RC and the Crystal configurations. Test conditions: All inputs tied to VCC, L and G ports in the TRI-STATE mode and tied to ground, all outputs low and tied to ground. If the A/D is not being used and minimum standby current is desired, VREF should be tied to AGND (effectively shorting the reference resistor). The clock monitor is disabled.

## DC Electrical Characteristics 0°C ≤ TA ≤ +70°C unless otherwise specified (Continued)

| Parameter                                                                  | Conditions                         | Min | Тур | Max     | Units    |

|----------------------------------------------------------------------------|------------------------------------|-----|-----|---------|----------|

| Allowable Sink/Source<br>Current per Pin<br>D Outputs (Sink)<br>All Others |                                    |     |     | 15<br>3 | mA<br>mA |

| Maximum Input Current without Latchup                                      | T <sub>A</sub> = 25°C              |     |     | ±100    | mA       |

| RAM Retention Voltage, V <sub>r</sub>                                      | 500 ns Rise and Fall<br>Time (Min) | 2   |     |         | ٧        |

| Input Capacitance                                                          |                                    |     |     | 7       | pF       |

| Load Capacitance on D2                                                     |                                    |     |     | 1000    | pF       |

# A/D Converter Specifications $V_{CC} = 5V \pm 10\%$ ; $(V_{SS} - 0.050V) \le Any Input \le (V_{CC} + 0.050V)$

| Parameter                        | Conditions                                                               | Min  | Тур | Max              | Units     |

|----------------------------------|--------------------------------------------------------------------------|------|-----|------------------|-----------|

| Resolution                       |                                                                          |      |     | 8                | Bits      |

| Reference Voltage Input          | AGND = 0V                                                                | 3    |     | Vcc              | V         |

| Absolute Accuracy                | $V_{REF} = V_{CC}$                                                       |      |     | ±1               | LSB       |

| Non-Linearity                    | V <sub>REF</sub> = V <sub>CC</sub> Deviation from the best straight line |      |     | ± 1/2            | LSB       |

| Differential Non-Linearity       | V <sub>REF</sub> = V <sub>CC</sub>                                       |      |     | ± 1/2            | LSB       |

| Input Reference Resistance       |                                                                          | 1.6  |     | 4.8              | kΩ        |

| Common Mode Input Range (Note 7) |                                                                          | AGND |     | V <sub>REF</sub> | V         |

| DC Common Mode Error             |                                                                          |      |     | ± 1/4            | LSB       |

| Off Channel Leakage Current      |                                                                          |      | 1   |                  | μΑ        |

| On Channel Leakage Current       |                                                                          |      | 1   |                  | μΑ        |

| A/D Clock Frequency (Note 5)     |                                                                          | 0.1  |     | 1.67             | MHz       |

| Conversion Time (Note 4)         |                                                                          |      | 12  |                  | A/D clock |

Note 4: Conversion Time includes sample and hold time.

Note 5: See Prescaler description.

Note 6: Pins G6 and RESET are designed with a high voltage input network for factory testing. These pins allow input voltages greater than V<sub>CC</sub> and the pins will have sink current to V<sub>CC</sub> when biased at voltages greater than V<sub>CC</sub> (the pins do not have source current when biased at a voltage below V<sub>CC</sub>). The effective resistance to V<sub>CC</sub> is 750Ω (typical). These two pins will not latch up. The voltage at the pins must be limited to less than 14V.

Note 7: For  $V_{IN}(-) \ge V_{IN}(+)$  the digital output code will be 0000 0000. Two on-chip diodes are tied to each analog input. The diodes will forward conduct for analog input voltages below ground or above the V<sub>CC</sub> supply. Be careful, during testing at low V<sub>CC</sub> levels (4.5V), as high level analog inputs (5V) can cause this input diode to conduct—especially at elevated temperatures, and cause errors for analog inputs near full-scale. The spec allows 50 mV forward bias of either diode. This means that as long as the analog V<sub>IN</sub> does not exceed the supply voltage by more than 50 mV, the output code will be correct. To achieve an absolute 0 V<sub>DC</sub> to 5 V<sub>DC</sub> input voltage range will therefore require a minimum supply voltage of 4.950 V<sub>DC</sub> over temperature variations, initial tolerance and loading.

| AC Electrical Characteristics o°C ≤ TA ≤ +70°C unless | otherwise specified |

|-------------------------------------------------------|---------------------|

|-------------------------------------------------------|---------------------|

| Parameter                                 | Conditions                        | Min | Тур | Max | Units          |

|-------------------------------------------|-----------------------------------|-----|-----|-----|----------------|

| Instruction Cycle Time (t <sub>c</sub> )  |                                   |     |     |     |                |

| Crystal, Resonator,                       |                                   | 1 1 |     | DC  | μs             |

| R/C Oscillator                            |                                   | 3   |     | DC  | μs             |

| CKI Clock Duty Cycle (Note 7)             | f <sub>r</sub> = Max              | 40  |     | 60  | %              |

| Rise Time (Note 7)                        | f <sub>r</sub> = 10 MHz Ext Clock |     |     | 5   | ns             |

| Fall Time (Note 7)                        | f <sub>r</sub> = 10 MHz Ext Clock |     |     | 5   | ns             |

| Inputs                                    |                                   |     |     |     |                |

| tsetup                                    |                                   | 200 |     |     | ns             |

| thold                                     |                                   | 60  |     |     | ns             |

| Output Propagation Delay                  | $R_L = 2.2k, C_1 = 100 pF$        |     |     |     |                |

| tPD1, tPD0                                |                                   |     |     |     |                |

| SO, SK                                    |                                   | 1   |     | 0.7 | μs             |

| All Others                                |                                   |     |     | 1   | μѕ             |

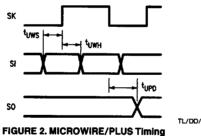

| MICROWIRE™ Setup Time (tuws)              |                                   | 20  |     |     | ns             |

| MICROWIRE Hold Time (t <sub>UWH</sub> )   |                                   | 56  |     |     | ns             |

| MICROWIRE Output Propagation Delay (tupp) |                                   |     |     | 220 | ns             |

| Input Pulse Width                         |                                   |     |     |     |                |

| Interrupt Input High Time                 |                                   | 1 1 |     |     | t <sub>c</sub> |

| Interrupt Input Low Time                  |                                   | 1 1 |     |     | tc             |

| Timer Input High Time                     |                                   | 1   |     |     | tc             |

| Timer Input Low Time                      |                                   | 1   |     |     | tc             |

| Reset Pulse Width                         |                                   | 1   |     |     | μs             |

Note 7: Parameter sampled (not 100% tested).

G JES

## Pin Descriptions

V<sub>CC</sub> and GND are the power supply pins.

$V_{\mbox{\scriptsize REF}}$  and AGND are the reference pins for the onboard A/D converter.

CKI is the clock input. This can come from an R/C generated oscillator, or a crystal oscillator (in conjunction with CKO). See Oscillator Description section.

RESET is the master reset input. See Reset Description section.

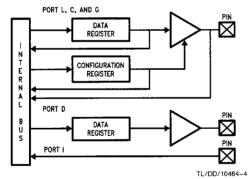

The COP888CFMH contains three bidirectional 8-bit I/O ports (C, G and L), where each individual bit may be independently configured as an input, output or TRI-STATE under program control. Three data memory address locations are allocated for each of these I/O ports. Each I/O port has two associated 8-bit memory mapped registers, the CONFIGURATION register and the output DATA register. A memory mapped address is also reserved for the input pins of each I/O port. Figure 3 shows the I/O port configurations. The DATA and CONFIGURATION registers allow for each port bit to be individually configured under software control as shown below:

| CONFIGURATION<br>Register | DATA<br>Register | Port Set-Up             |

|---------------------------|------------------|-------------------------|

| 0                         | 0                | Hi-Z Input              |

|                           |                  | (TRI-STATE Output)      |

| 0 .                       | 1                | Input with Weak Pull-Up |

| 1                         | 0                | Push-Pull Zero Output   |

| 1                         | 1                | Push-Pull One Output    |

FIGURE 3. I/O Port Configurations

Port L is an 8-bit I/O port. All L-pins have Schmitt triggers on the inputs.

The Port L supports Multi-Input Wake Up. L4 and L5 are used for the timer input functions T2A and T2B.

The Port L has the following alternate features:

LO MIWU (28- and 40-pin only)

L1 MIWU (28- and 40-pin only)

L2 MIWU

L3 MIWU

L4 MIWU or T2A

L5 MIWU or T2B

L6 MIWU

L7 MIWU

Port G is an 8-bit port with 5 I/O pins (G0, G2-G5), an input pin (G6), and two dedicated output pins (G1 and G7). Pins G0 and G2-G6 all have Schmitt Triggers on their inputs. Pin G1 serves as the dedicated WDOUT WATCHDOG output, while pin G7 is either input or output depending on the oscillator mask option selected. With the crystal oscillator option selected, G7 serves as the dedicated output pin for the CKO clock output. With the single-pin R/C oscillator mask option selected, G7 serves as a general purpose input pin but is also used to bring the device out of HALT mode with a low to high transition. There are two registers associated with the G Port, a data register and a configuration register. Therefore, each of the 5 I/O bits (G0, G2-G5) can be individually configured under software control.

Since G6 is an input only pin and G7 is the dedicated CKO clock output pin (crystal clock option) or general purpose input (R/C clock option), the associated bits in the data and configuration registers for G6 and G7 are used for special purpose functions as outlined below. Reading the G6 and G7 data bits will return zeros.

Note that the chip will be placed in the HALT mode by writing a "1" to bit 7 of the Port G Data Register. Similarly the chip will be placed in the IDLE mode by writing a "1" to bit 6 of the Port G Data Register.

Writing a "1" to bit 6 of the Port G Configuration Register enables the MICROWIRE/PLUS to operate with the alternate phase of the SK clock. The G7 configuration bit, if set high, enables the clock start up delay after HALT when the R/C clock configuration is used.

|    | Config Reg.  | Data Reg. |

|----|--------------|-----------|

| G7 | CLKDLY       | HALT      |

| G6 | Alternate SK | IDLE      |

Port G has the following alternate features:

G0 INTR (External Interrupt Input)

G2 T1B (Timer T1 Capture Input)

G3 T1A (Timer T1 I/O)

G4 SO (MICROWIRE Serial Data Output)

G5 SK (MICROWIRE Serial Clock)

G6 SI (MICROWIRE Serial Data Input)

Port G has the following dedicated functions:

- G1 WDOUT (WATCHDOG and/or Clock Monitor dedicated output)

- cated output)

G7 CKO (Oscillator dedicated output or general purpose input)

Port I is an eight-bit Hi-Z input port and also provides the analog inputs to the A/D Converter.

Port D is an 8-bit output port that is preset high when RESET goes low. The user can tie two or more D port outputs together in order to get a higher drive.

Port C is an 8-bit I/O port.

## **Oscillator Circuits**

The chip can be driven by a clock input on the CKI input pin which can be between DC and 10 MHz. The CKO output clock is on pin G7 (crystal configuration). The CKI input frequency is divided down by 10 to produce the instruction cycle clock  $(1/t_c)$ .

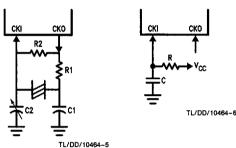

Figure 4 shows the Crystal and R/C diagrams.

### CRYSTAL OSCILLATOR

CKI and CKO can be connected to make a closed loop crystal (or resonator) controlled oscillator.

Table I shows the component values required for various standard crystal values.

### R/C OSCILLATOR (Special Order from Factory)

By selecting CKI as a single pin oscillator input, a single pin R/C oscillator circuit can be connected to it. CKO is available as a general purpose input, and/or HALT restart input.

Table II shows the variation in the oscillator frequencies as functions of the component (R and C) values.

FIGURE 4. Crystal and R/C Oscillator Diagrams

**TABLE I. Crystal Oscillator Configuration,** TA = 25°C, Vcc = 5V

| 1A 20 0, VCC 01 |            |            |            |                   |  |  |

|-----------------|------------|------------|------------|-------------------|--|--|

| R1<br>(kΩ)      | R2<br>(MΩ) | C1<br>(pF) | C2<br>(pF) | CKI Freq<br>(MHz) |  |  |

| 0               | 1          | 30         | 30-36      | 10                |  |  |

| 0               | 1          | 30         | 30-36      | 4                 |  |  |

| 0               | 1          | 200        | 100-150    | 0.455             |  |  |

TABLE II. RC Oscillator Configuration, TA = 25°C, Vcc = 5V

| R<br>(kΩ) | C<br>(pF) | CKI Freq<br>(MHz) | instr. Cycle<br>(μs) |

|-----------|-----------|-------------------|----------------------|

| 3.3       | 82        | 2.8 to 2.2        | 3.6 to 4.5           |

| 5.6       | 100       | 1.5 to 1.1        | 6.7 to 9             |

| 6.8       | 100       | 1.1 to 0.8        | 9 to 12.5            |

## Programming the COP888CFMH

Programming the COP888CFMH hybrid emulators is accomplished with the duplicator board which is a stand alone programmer capable of supporting different package types. It works in conjunction with a pre-programmed EPROM (either via the development system or a standard programmer) holding the application program. The duplicator board essentially copies the information in the EPROM into the hybrid emulator.

The last byte of program memory (EPROM location 01FFF Hex) must contain the value specified in the following table.

### TABLE III

| Package | HALT<br>Mode | Contents of Last Byte (Address 01FFF) |

|---------|--------------|---------------------------------------|

| 28      | Enabled      | 6F                                    |

| 28      | Disabled     | EF                                    |

| 40/44   | Enabled      | 7F                                    |

| 40/44   | Disabled     | FF                                    |

The following product codes are used by the customer order to order the duplicator board.

| NSID<br>COP8-PRGM-PCC | <b>Description</b> Duplicator Board for 44-Pin LDCC | Documentation<br>User Instruction<br>Manual |

|-----------------------|-----------------------------------------------------|---------------------------------------------|

| COP8-PRGM-DIP         | 40-Pin DIP                                          | User Instruction<br>Manual                  |

| COP8-PRGM-28D         | 28-Pin DIP                                          | User Instruction<br>Manual                  |

The device will also program on a Data I/O Programmer. The following table provides the programming information on a Data I/O Programmer.

| COPs Part<br>Number | Package<br>Type | Family<br>Code | Pin | Software<br>Rev | Adapter |

|---------------------|-----------------|----------------|-----|-----------------|---------|

| COP884CFMHD         | 28 DIP          | 16F            | 19E | V3.3            | SITE 48 |

| COP888CFMHD         | 40 DiP          | 16F            | 19F | V3.3            | SITE 48 |

| COP888CFMHEL        | 44 LDCC         | 16F            | 175 | V3.2            | PINSITE |

## **ERASING THE PROGRAM MEMORY**

Erasure of the program memory is achieved by removing the device from its socket and exposing the transparent window to an ultra-violet light source.

The erasure characteristics of the device are such that erasure begins to occur when exposed to light with wavelengths shorter than approximately 4000Å. It should be noted that sunlight and certain types of fluorescent lamps have wavelengths in the 3000Å to 4000Å range.

After programming, opaque labels should be placed over the window of the device to prevent temporary functional failure due to the generation of photo currents, erasure, and excessive HALT current. Note that the device will also draw more current than normal (especially in HALT mode) when the window of the device is not covered with an opaque lable.

The recommended erasure procedure for the device is exposure to short wave ultraviolet light which has a wavelength of 2537Å. The integrated dose (UV intensity X exposure time) for erasure should be a minimum of 15 W-sec/ cm<sup>2</sup>.

The device should be placed within one inch of the lamp tubes during erasure. Some lamps have a filter on their tubes which should be removed before erasure. The following table shows the minimum erasure time for various light intensities.

TARLE IV Minimum CORRECEMU Esseure Time

| TABLE 17: Millingill COT COOCT MITT Exabate Time |                           |  |  |  |

|--------------------------------------------------|---------------------------|--|--|--|

| Light Intensity<br>(Micro-Watts/cm²)             | Erasure Time<br>(Minutes) |  |  |  |

| 15,000                                           | 20                        |  |  |  |

| 10,000                                           | 25                        |  |  |  |

| 5,000                                            | 50                        |  |  |  |

# **Development Support**

**Development Tools Selection Table**

| Microcontroller                    | Order<br>Part Number       | Description                                                                                         | Includes                                 | Manual<br>Number |

|------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------|------------------|

|                                    | MOLE-BRAIN                 | Brain Board                                                                                         | Brain Board Users Manual                 | 420408188-001    |

|                                    | MOLE-COP8-PB2              | Personality Board                                                                                   | COP888 Personality Board<br>Users Manual | 420420084-001    |

| COP888 MOLE-COP8-IBM 420411060-001 | Assembler Software for IBM | COP800 Software Users Manual<br>and Software Disk<br>PC-DOS Communications<br>Software Users Manual | 424410527-00°<br>420040416-00°           |                  |

|                                    | Programmer's Manual        |                                                                                                     | 420411060-01                             |                  |

An erasure system should be calibrated periodically. The distance from lamp to device should be maintained at one inch. The erasure time increases as the square of the distance. Lamps lose intensity as they age. When a lamp has aged, the system should be checked to make certain that adequate UV dosages are being applied for full erasure.

### **DEVELOPMENT SYSTEM**

The NSC Development System is a low cost development system and emulator for all microcontroller products. These include COPs microcontrollers and the HPC family of products. The development system consists of a BRAIN Board, Personality Board and optional host software.

The purpose of the development system is to provide the user with a tool to write and assemble code, emulate code for the target microcontroller and assist in both software and hardware debugging of the system.

It is a self contained computer with its own firmware which provides for all system operation, emulation control, communication, PROM programming and diagnostic operations.

It contains three serial ports to optionally connect to a terminal, a host system, a printer or a modem, or to connect to other development systems in a multi-development system environment

Development system can be used in either a stand alone mode or in conjunction with a selected host system using PC-DOS communicating via a RS-232 port.

### **How to Order**

To order a complete development package, select the section for the microcontroller to be developed and order the parts listed.

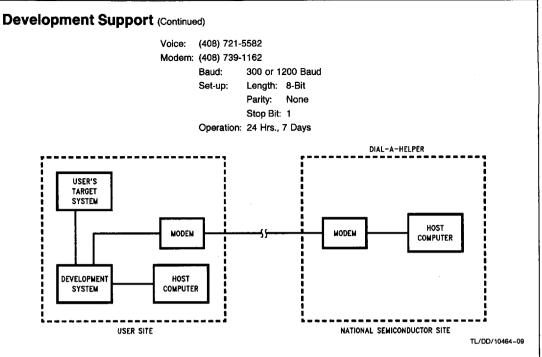

## DIAL-A-HELPER

Dial-A-Helper is a service provided by the Microcontroller Applications group. The Dial-A-Helper is an Electronic Bulletin Board Information system and additionally, provides the capability of remotely accessing the development system at a customer site.

### INFORMATION SYSTEM

The Dial-A-Helper system provides access to an automated information storage and retrieval system that may be accessed over standard dial-up telephone lines 24 hours a day. The system capabilities include a MESSAGE SECTION (electronic mail) for communications to and from the Microcontroller Applications Group and a FILE SECTION which consists of several file areas where valuable application software and utilities could be found. The minimum requirement for accessing the Dial-A-Helper is a Hayes compatible modem.

If the user has a PC with a communications package then files from the FILE SECTION can be down loaded to disk for later use.

### ORDER P/N: MOLE-DIAL-A-HLP

Information System Package contains:

Dial-A-Helper Users Manual

Public Domain Communications Software

## **FACTORY APPLICATIONS SUPPORT**

Dial-A-Helper also provides immediate factor applications support. If a user is having difficulty in operating the development system, he can leave messages on our electronic bulletin board, which we will respond to, or under extraordinary circumstances he can arrange for us to actually take control of his system via modem for debugging purposes.