# 82385SX HIGH PERFORMANCE CACHE CONTROLLER

- Improves 386™ SX System Performance

- Reduces Average CPU Wait States to Nearly Zero

- Zero Wait State Read Hit

- Zero Wait State Posted Memory Writes

- Allows Other Masters to Access the System Bus More Readily

- Hit Rates up to 99%

- Optimized as 386 SX Companion

- Simple 386 SX Interface

- Part of Intel386™-Based Compute Engine Including 387™ SX Math Coprocessor and 82370 Integrated System Peripheral

- 16 MHz and 20 MHz Operation

- **■** Software Transparent

- Synchronous Dual Bus Architecture

Bus Watching Maintains Cache

- Coherency

- Maps Full 386 SX Address Space

- **■** Flexible Cache Mapping Policies

- Direct Mapped or 2-Way Set Associative Cache Organization

- Supports Non-Cacheable Memory Space

- Unified Cache for Code and Data

- Integrates Cache Directory and Cache Management Logic

- High Speed CHMOS Technology — 132-Pin PGA and 132-Lead PQFP

The 82385SX Cache Controller is a high performance peripheral for Intel's 386TM SX Microprocessor. It stores a copy of frequently accessed code and data from main memory in a zero wait state local cache memory. The 82385SX allows the 386 SX Microprocessor to run near its full potential by reducing the average number of CPU wait states to nearly zero. The dual bus architecture of the 82385SX allows other masters to access system resources while the 386 SX CPU operates locally out of its cache. In this situation, the 82385SX's "bus watching" mechanism preserves cache coherency by monitoring the system bus address lines at no cost to system or local throughput.

The 82385SX is completely software transparent, protecting the integrity of system software. High performance and board space savings are achieved because the 82385SX integrates a cache directory and all cache management logic on one chip.

Intel386™, 386™, 386™ SX, and 387™ SX are trademarks of Intel Corporation.

November 1991 Order Number: 290222-003

# 82385SX

# intel.

| CONTENTS                                                                                                              | PAGE  |

|-----------------------------------------------------------------------------------------------------------------------|-------|

| 1.0 82385SX FUNCTIONAL OVERVIEW                                                                                       | 5-706 |

| 1.1 82385SX Overview                                                                                                  | 5-706 |

| 1.2 System Overview I: Bus Structure                                                                                  | 5-706 |

| 1.2.1 386TM SX Local Bus/82358SX Local Bus/System Bus                                                                 | 5-706 |

| 1.2.2 Bus Arbitration                                                                                                 | 5-706 |

| 1.2.3 Master/Slave Operation                                                                                          | 5-709 |

| 1.2.4 Cache Coherency                                                                                                 | 5-709 |

| 1.3 System Overview II: Basic Operation                                                                               | 5-710 |

| 1.3.1 386 SX Memory Code and Data Read Cycles                                                                         | 5-710 |

| 1.3.1.1 Read Hits                                                                                                     | 5-710 |

| 1.3.1.2 Read Misses                                                                                                   | 5-710 |

| 1.3.2 386 SX Memory Write Cycles                                                                                      | 5-710 |

| 1.3.3 Non-Cacheable Cycles                                                                                            | 5-710 |

| 1.3.4 386 SX Local Bus Cycles                                                                                         | 5-711 |

| 1.3.5 Summary of 82385SX Response to All 386 SX Cycles                                                                | 5-711 |

| 1.3.6 Bus Watching                                                                                                    | 5-711 |

| 1.3.7 Cache Flush                                                                                                     | 5-711 |

| 2.0 82385SX CACHE ORGANIZATION                                                                                        | 5-713 |

| 2.1 Direct Mapped Cache                                                                                               | 5-713 |

| 2.1.1 Direct Mapped Cache Structure and Terminology                                                                   | 5-713 |

| 2.1.2 Direct Mapped Cache Operation                                                                                   | 5-714 |

| 2.1.2.1 Read Hits                                                                                                     | 5-714 |

| 2.1.2.2 Read Misses                                                                                                   | 5-714 |

| 2.1.2.3 Other Operations That Affect the Cache and Cache Directory                                                    | 5-714 |

| 2.2 Two Way Set Associative Cache                                                                                     | 5-715 |

| 2.2.1 Two Way Set Associative Cache Structure and Terminology                                                         | 5-715 |

| 2.2.2 LRU Replacement Algorithm                                                                                       | 5-715 |

| 2.2.3 Two Way Set Associative Cache Operation                                                                         | 5-715 |

| 2.2.3.1 Read Hits                                                                                                     | 5-715 |

| 2.2.3.2 Read Misses                                                                                                   | 5-715 |

| 2.2.3.3 Other Operations That Affect the Cache and Cache Directory                                                    | 5-715 |

| 3.0 82835SX PIN DESCRIPTION                                                                                           | 5-715 |

| 3.1 386 SX Interface Signals                                                                                          | 5-717 |

| 3.1.1 386 SX Clock (CLK2)                                                                                             | 5-717 |

| 3.1.2 386 SX RESET (RESET)                                                                                            | 5-717 |

| 3.1.3 386 SX Address Bus (A1-A23), Byte Enables (BHE#, BLE#), and Cycle Definition Signals (M/IO#, D/C#, W/R#, LOCK#) | 5-718 |

| 3.1.4 386 SX Address Status (ADS#) and Ready Input (READYI#)                                                          |       |

| 3.1.5 386 SX Next Address Request (NA#)                                                                               |       |

| 3.1.6 Ready Output (READYO#) and Bus Ready Enable (BRDYFN#)                                                           | 5-718 |

| )( | JN. | TENTS                                                                                        | PAGE  |

|----|-----|----------------------------------------------------------------------------------------------|-------|

|    | 3.2 | Cache Control Signals                                                                        | 5-718 |

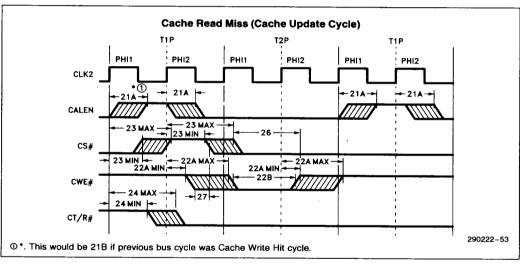

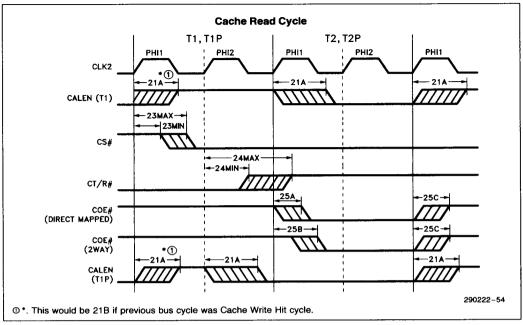

|    |     | 3.2.1 Cache Address Latch Enable (CALEN)                                                     |       |

|    |     | 3.2.2 Cache Transmit/Receive (CT/R#)                                                         | 5-718 |

|    |     | 3.2.3 Cache Chip Selects (CS0 # -CS1 #)                                                      | 5-719 |

|    |     | 3.2.4 Cache Output Enables (COEA#, COEB#) and Write Enables                                  |       |

|    |     | (CWEA#, CWEB#)                                                                               | 5-719 |

|    | 3.3 | 386 SX Local Bus Decode Inputs                                                               | 5-719 |

|    |     | 3.3.1 386 SX Local Bus Access (LBA#)                                                         |       |

|    |     | 3.3.2 Non-Cacheable Access (NCA#)                                                            |       |

|    | 3.4 | 82385SX Bus Interface Signals                                                                | 5-719 |

|    |     | 3.4.1 82385SX Bus Byte Enables (BBHE#, BBLE#)                                                |       |

|    |     | 3.4.2 82385SX Bus Lock (BLOCK#)                                                              | 5-720 |

|    |     | 3.4.3 82385SX Bus Address Status (BADS#)                                                     | 5-720 |

|    |     | 3.4.4 82385SX Bus Ready Input (BREADY#)                                                      | 5-720 |

|    |     | 3.4.5 82385SX Bus Next Address Request (BNA#)                                                | 5-720 |

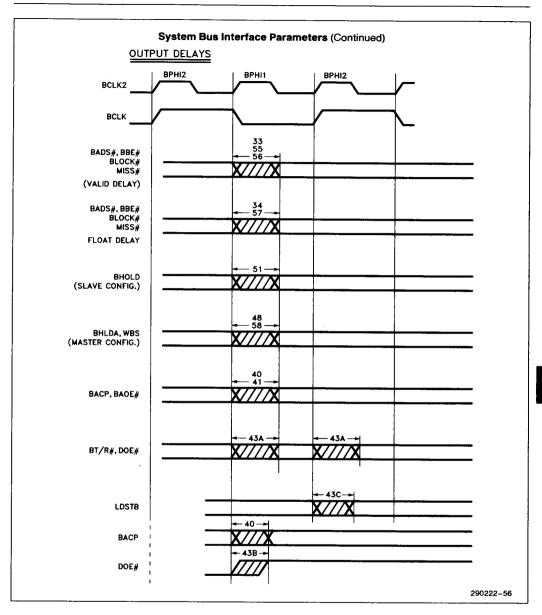

|    | 3.5 | 82385SX Bus Data Transceiver and Address Latch Control                                       | 5-720 |

|    |     | 3.5.1 Local Data Strobe (LDSTB), Data Output Enable (DOE#), and Bus Transmit/Receive (BT/R#) | 5-720 |

|    |     | 3.5.2 Bus Address Clock Pulse (BACP) and Bus Address Output Enable (BAOE#).                  | 5-720 |

|    | 3.6 | Status and Control Signals                                                                   | 5-720 |

|    |     | 3.6.1 Cache Miss Indication (MISS#)                                                          | 5-720 |

|    |     | 3.6.2 Write Buffer Status (WBS)                                                              | 5-721 |

|    |     | 3.6.3 Cache Flush (FLUSH)                                                                    | 5-721 |

|    | 3.7 | Bus Arbitration Signals (BHOLD and BHLDA)                                                    | 5-721 |

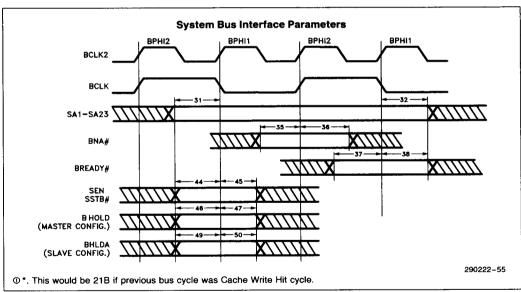

|    | 3.8 | Coherency (Bus Watching) Support Signals (SA1-SA23, SSTB#, SEN)                              | 5-721 |

|    | 3.9 | Configuration Inputs (2W/D#, M/S#, DEFOE#)                                                   | 5-721 |

|    | 3.1 | 0 Reserved Pins (RES)                                                                        | 5-721 |

| .0 | 386 | SX LOCAL BUS INTERFACE                                                                       | 5-722 |

|    | 4.1 | Processor Interface                                                                          | 5-722 |

|    |     | 4.1.1 Hardware Interface                                                                     | 5-722 |

|    |     | 4.1.2 Ready Generation                                                                       | 5-724 |

|    |     | 4.1.3 NA# and 386 SX Local Bus Pipelining                                                    |       |

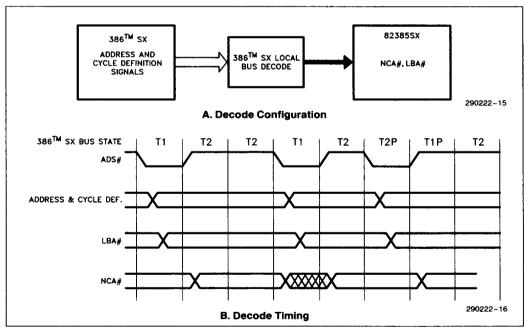

|    |     | 4.1.4 LBA# and NCA# Generation                                                               |       |

|    | 4.2 | Cache Interface                                                                              | 5-727 |

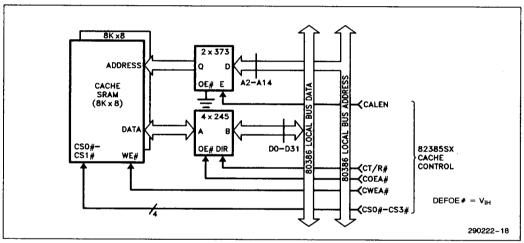

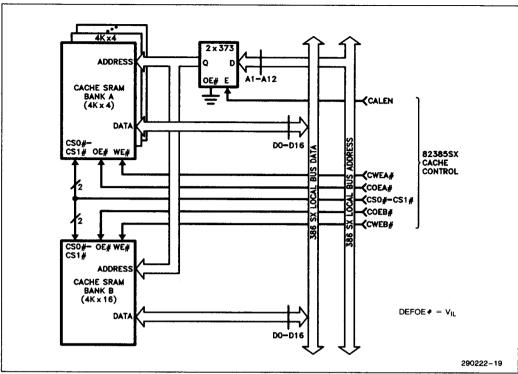

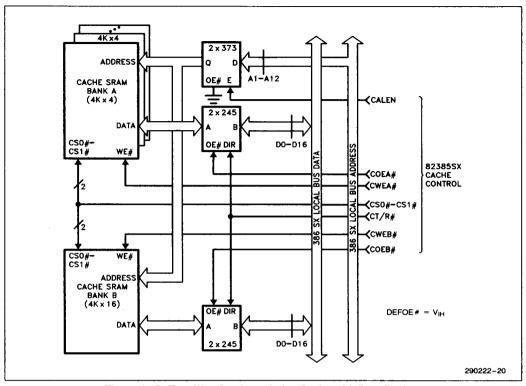

|    |     | 4.2.1 Cache Configurations                                                                   |       |

|    |     | 4.2.2 Cache Control Direct Mapped                                                            |       |

|    |     | 4.2.3 Cache Control Two Way Set Associative                                                  |       |

|    |     |                                                                                              |       |

# 82385SX

# intel.

| CC  | )N  | TENTS                                                                              | PAGE  |

|-----|-----|------------------------------------------------------------------------------------|-------|

| 5.0 | 823 | 385SX LOCAL BUS AND SYSTEM INTERFACE                                               | 5-733 |

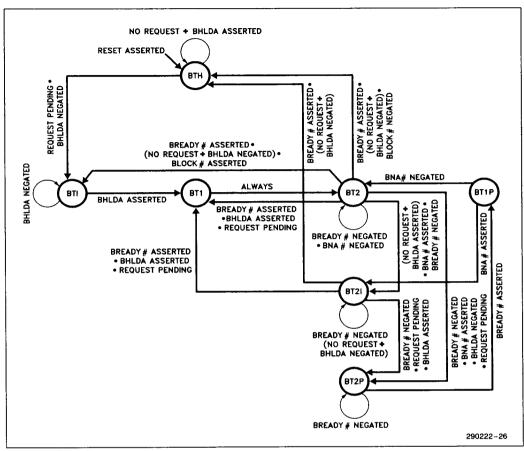

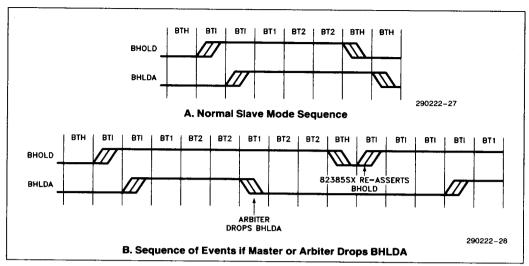

|     | 5.1 | The 823885SX Bus State Machine                                                     | 5-733 |

|     |     | 5.1.1 Master Mode                                                                  | 5-733 |

|     |     | 5.1.2 Slave Mode                                                                   | 5-733 |

|     | 5.2 | ? The 82385SX Local Bus                                                            | 5-738 |

|     |     | 5.2.1 82385SX Bus Counterparts to 386 SX Signals                                   | 5-746 |

|     |     | 5.2.1.1 Address Bus (BA1-BA23) and Cycle Definition Signals (BM/IO#, BD/C#, BW/R#) | 5-746 |

|     |     | 5.2.1.2 Data Bus (BD0-BD15)                                                        |       |

|     |     | 5.2.1.3 Byte Enables (BBHE#, BBLE#)                                                |       |

|     |     | 5.2.1.4 Address Status (BADS#)                                                     |       |

|     |     | 5.2.1.5 Ready (BREADY#)                                                            |       |

|     |     | 5.2.1.6 Next Address Request (BNA#)                                                | 5-747 |

|     |     | 5.2.1.7 Bus Lock (BLOCK#)                                                          | 5-747 |

|     |     | 5.2.2 Additional 82385SX Bus Signals                                               | 5-748 |

|     |     | 5.2.2.1 Cache Read/Write Miss Indication (MISS#)                                   | 5-748 |

|     |     | 5.2.2.2 Write Buffer Status (WBS)                                                  | 5-749 |

|     |     | 5.2.2.3 Cache Flush (FLUSH)                                                        | 5-749 |

|     | 5.3 | Bus Watching (Snoop) Interface                                                     | 5-749 |

|     | 5.4 | Reset Definition                                                                   | 5-750 |

| 6.0 | SY  | STEM DESIGN GUIDELINES                                                             | 5-751 |

|     |     | Introduction                                                                       | 5-751 |

|     |     | Power and Grounding                                                                | 5-751 |

|     |     | 6.2.1 Power Connections                                                            | 5-751 |

|     |     | 6.2.2 Power Decoupling                                                             | 5-751 |

|     |     | 6.2.3 Resistor Recommendations                                                     | 5-751 |

|     |     | 6.2.3.1 386 SX Local Bus                                                           | 5-751 |

|     |     | 6.2.3.2 82385SX Local Bus.                                                         | 5-751 |

|     | 6.3 | 82385SX Signal Connections                                                         | 5-751 |

|     |     | 6.3.1 Configuration Inputs                                                         | 5-751 |

|     |     | 6.3.2 CLK2 and RESET                                                               | 5-752 |

|     | 6.4 | Unused Pin Requirements                                                            | 5-752 |

|     |     | Cache SRAM Requirements                                                            | 5-752 |

|     |     | 6.5.1 Cache Memory without Transceivers                                            | 5-752 |

|     |     | 6.5.2 Cache Memory with Transceivers                                               |       |

| ł | ı |   | ı |

|---|---|---|---|

| Ĺ | į |   | ١ |

| r | ١ | ı | ı |

|   |   | _ |   |

| CONTENTS                                          | PAGE  |

|---------------------------------------------------|-------|

| 7.0 SYSTEM TEST CONSIDERATIONS                    | 5-753 |

| 7.1 Introduction                                  | 5-753 |

| 7.2 Main Memory (DRAM) Testing                    | 5-753 |

| 7.2.1 Memory Testing Routine                      | 5-753 |

| 7.3 82385SX Cache Memory Testing                  | 5-753 |

| 7.3.1 Test Routine in the NCA# or LBA# Memory Map | 5-754 |

| 7.3.2 Test Routine in Cacheable Memory            | 5-754 |

| 7.4 82385SX Cache Directory Testing               | 5-754 |

| 7.5 Special Function Pins                         | 5-754 |

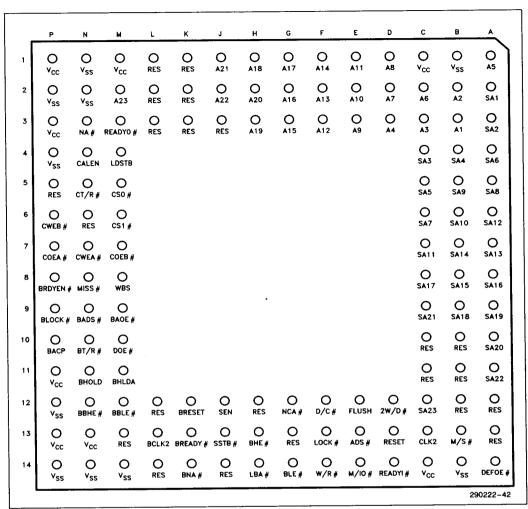

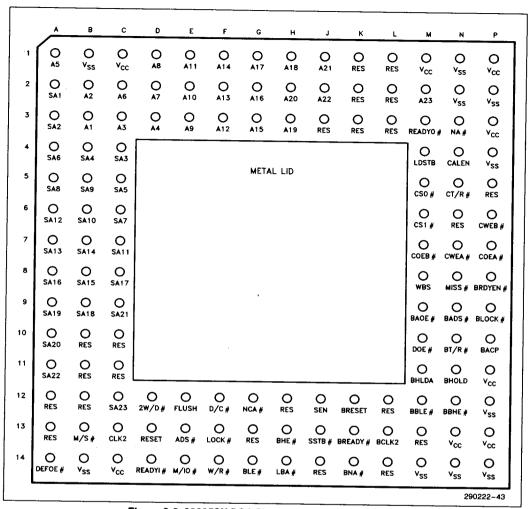

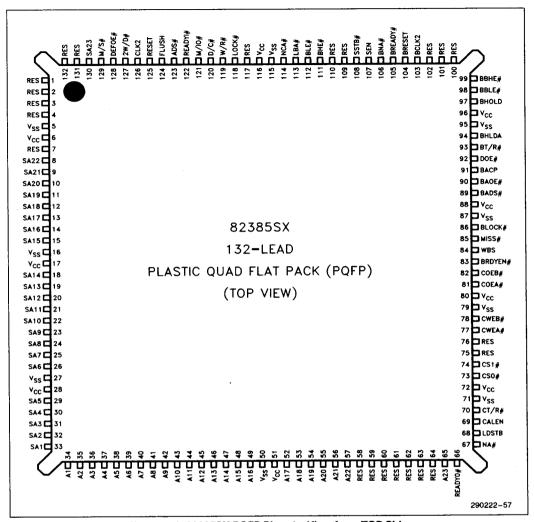

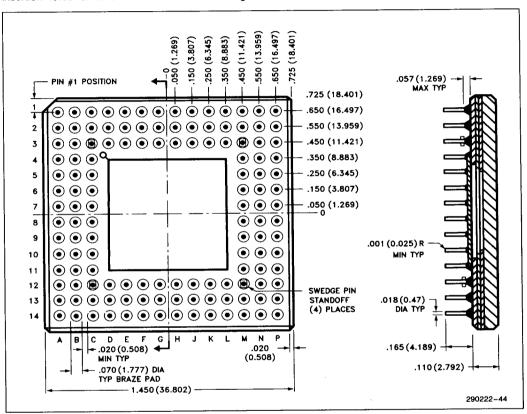

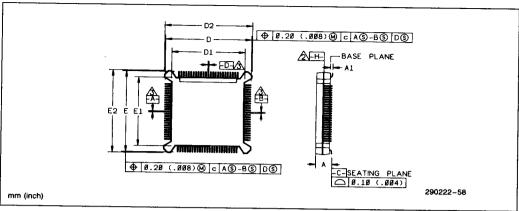

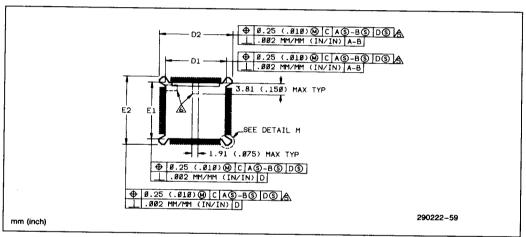

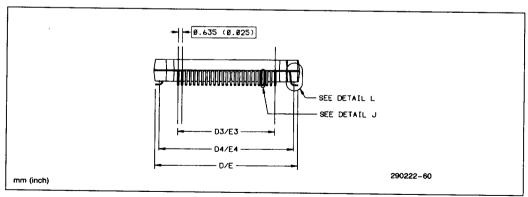

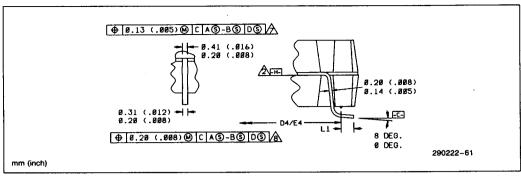

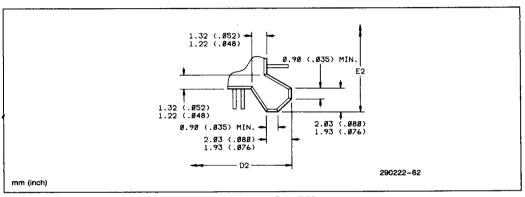

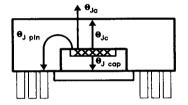

| 8.0 MECHANICAL DATA                               | 5-754 |

| 8.1 Introduction                                  | 5-754 |

| 8.2 Pin Assignment                                | 5-754 |

| 8.3 Package Dimensions and Mounting               | 5-759 |

| 8.4 Package Thermal Specification                 |       |

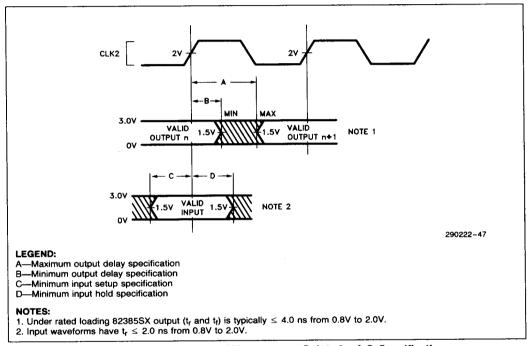

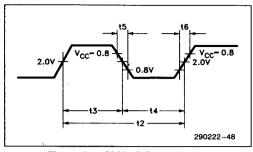

| 9.0 ELECTRICAL DATA                               | 5-764 |

| 9.1 Introduction                                  | 5-764 |

| 9.2 Maximum Ratings                               | 5-764 |

| 9.3 D.C. Specifications                           | 5-764 |

| 9.4 A.C. Specifications                           |       |

| 9.4.1 Frequency Dependent Signals                 |       |

# 1.0 82385SX FUNCTIONAL OVERVIEW

The 82385SX Cache Controller is a high performance peripheral for Intel's 386™ SX microprocessor. This chapter provides an overview of the 82385SX, and of the basic architecture and operation of a 386 SX CPU/82385SX system.

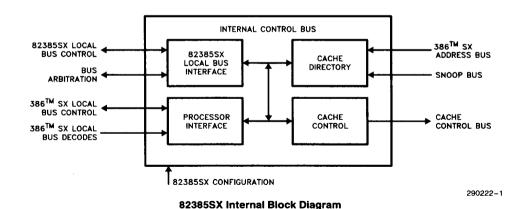

#### 1.1 82385SX Overview

The main function of a cache memory system is to provide fast local storage for frequently accessed code and data. The cache system intercepts 386 SX memory references to see if the required data resides in the cache. If the data resides in the cache (a hit), it is returned to the 386 SX without incurring wait states. If the data is not cached (a miss), the reference is forwarded to the system and the data retrieved from main memory. An efficient cache will yield a high "hit rate" (the ratio of cache hits to total 386 SX accesses), such that the majority of accesses are serviced with zero wait states. The net effect is that the wait states incurred in a relatively infrequent miss are averaged over a large number of accesses, resulting in an average of nearly zero wait states per access. Since cache hits are serviced locally, a processor operating out of its local cache has a much lower "bus utilization" which reduces system bus bandwidth requirements, making more bandwidth available to other bus masters.

The 82385SX Cache Controller integrates a cache directory and all cache management logic required to support an external 16 kbyte cache. The cache directory structure is such that the entire physical address range of the 386 SX is mapped into the cache. Provision is made to allow areas of memory to be set aside as non-cacheable. The user has two cache organization options: direct mapped and 2-way set associative. Both provide the high hit rates necessary to make a large, relatively slow main memory array look like fast, zero wait state memory to the 386 SX.

A good hit rate is an essential ingredient of a successful cache implementation. Hit rate is the measure of how efficient a cache is in maintaining a copy of the most frequently requested code and data. However, efficiency is not the only factor for performance consideration. Just as essential are sound cache management policies. These policies refer to the handling of 386 SX writes, preservation of cache coherency, and ease of system design. The 82385SX's "posted write" capability allows the majority of 386 SX writes, including most non-cacheable cycles, to run with zero wait states, and the 82385SX's "bus watching" mechanism preserves

cache coherency with no impact on system performance. Physically, the 82385SX ties directly to the 386 SX with virtually no external logic.

# 1.2 System Overview I: Bus Structure

A good grasp of bus structure of a 386 SX CPU/82385SX system is essential in understanding both the 82385SX and its role in a 386 SX system. The following is a description of this structure.

# 1.2.1 386TM SX LOCAL BUS/82385SX LOCAL BUS/SYSTEM BUS

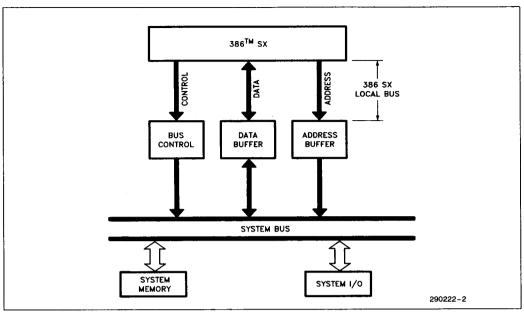

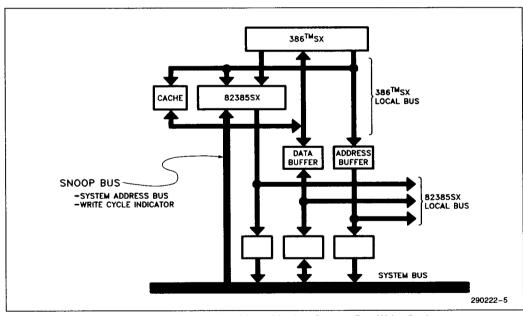

Figure 1-1 depicts the bus structure of a typical 386 SX system. The "386 SX Local Bus" consists of the physical 386 SX address, data, and control busses. The local address and data busses are buffered and/or latched to become the "system" address and data busses. The local control bus is decoded by bus control logic to generate the various system bus read and write commands.

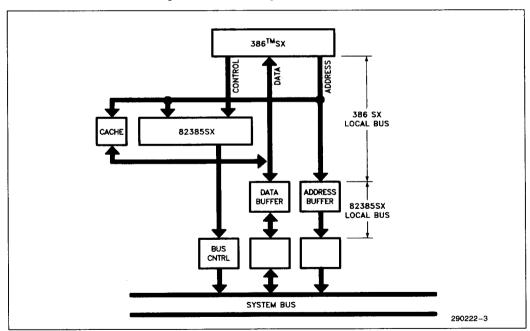

The addition of an 82385SX Cache Controller causes a separation of the 386 SX bus into two distinct busses: the actual 386 SX local bus and the "82385SX Local Bus" (Figure 1-2). The 82385SX local bus is designed to look like the front end of a 386 SX by providing 82385SX local bus equivalents to all appropriate 386 SX signals. The system ties to this "386 SX-like" front end just as it would to an actual 386 SX. The 386 SX simply sees a fast system bus, and the system sees a 386 SX front end with low bus bandwidth requirements. The cache subsystem is transparent to both. Note that the 82385SX local bus is not simply a buffered version of the 386 SX bus, but rather is distinct from, and able to operate in parallel with the 386 SX bus. Other masters residing on either the 82385SX local bus or system bus are free to manage system resources while the 386 SX operates out of its cache.

### 1.2.2 BUS ARBITRATION

The 82385SX presents the "386 SX-like" interface which is called the 82385SX local bus. Whereas the 386 SX provides a Hold Request/ Hold Acknowledge bus arbitration mechanism via its HOLD and HLDA pins, the 82385SX provides an equivalent mechanism via its BHOLD and BHLDA pins. (These signals are described in Section 3.7.) When another master requests the 82385SX local bus, it issues the request to the 82385SX via BHOLD. Typically, at the end of the current 82385SX local bus cycle, the 82385SX will release the 82385SX local bus and acknowledge the request via BHLDA. The 386 SX is of course free to continue operating on the 386 SX local bus while another master owns the 82385SX local bus.

Figure 1-1. 386™ SX System Bus Structure

Figure 1-2. 386™ SX and 82385SX System Bus Structure

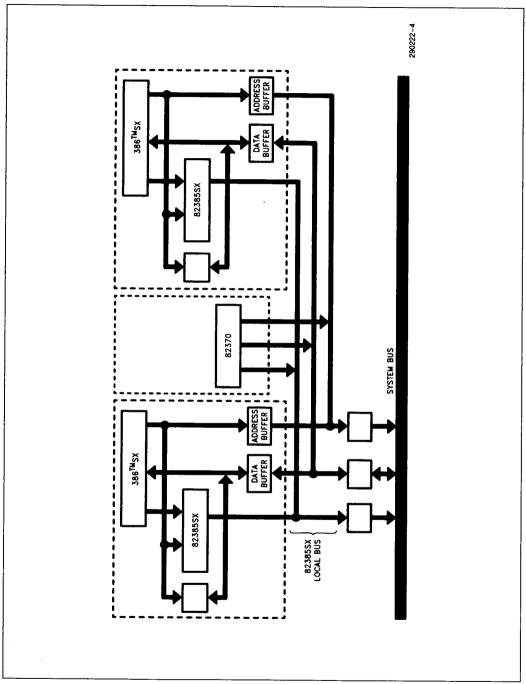

Figure 1-3. Multi-Master/Multi-Cache Environment 5-708

#### 1.2.3 MASTER/SLAVE OPERATION

The above 82385SX local bus arbitration discussion is true when the 82385SX is programmed for "Master" mode operation. The user can, however, configure the 82385SX for "Slave" mode operation. (Programming is done via a hardware strap option.) The roles of BHOLD and BHLDA are reversed for an 82385SX in slave mode; BHOLD becomes an output indicating a request to control the bus, and BHLDA becomes an input indicating that a request has been granted. An 82385SX programmed in slave mode drives the 82385SX local bus only when it has requested and subsequently been granted bus control. This allows multiple 386 SX CPU/82385SX subsystems to reside on the same 82385SX local bus (Figure 1-3).

#### 1.2.4 CACHE COHERENCY

Ideally, a cache contains a copy of the most heavily used portions of main memory. To maintain cache "coherency" is to make sure that this local copy is identical to main memory. In a system where multiple masters can access the same memory, there is

always a risk that one master will alter the contents of a memory location that is duplicated in the local cache of another master. (The cache is said to contain "stale" data.) One rather restrictive solution is to not allow cache subsystems to cache shared memory. Another simple solution is to flush the cache anytime another master writes to system memory. However, this can seriously degrade system performance as excessive cache flushing will reduce the hit rate of what may otherwise be a highly efficient cache.

The 82385SX preserves cache coherency via "bus watching" (also called snooping), a technique that neither impacts performance nor restricts memory mapping. An 82385SX that is not currently bus master monitors system bus cycles, and when a write cycle by another master is detected (a snoop), the system address is sampled and used to see if the referenced location is duplicated in the cache. If so (a snoop hit), the corresponding cache entry is invalidated, which will force the 386 SX to fetch the upto-date data from main memory the next time it accesses this modified location. Figure 1-4 depicts the general form of bus watching.

Figure 1-4. 82385SX Bus Watching—Monitor System Bus Write Cycles

# 1.3 System Overview II: Basic Operation

This discussion is an overview of the basic operation of a 386 SX CPU/82385SX system. Items discussed include the 82385SX's response to all 386 SX cycles, including interrupt acknowledges, halts, and shutdowns. Also discussed are non-cacheable and local accesses.

# 1.3.1 386TM SX MEMORY CODE AND DATA READ CYCLES

#### 1.3.1.1 Read Hits

When the 386 SX initiates a memory code or data read cycle, the 82385SX compares the high order bits of the 386 SX address bus with the appropriate addresses (tags) stored in its on-chip directory. (The directory structure is described in Section 2.1.1) If the 82385SX determines that the requested data is in the cache, it issues the appropriate control signals that direct the cache to drive the requested data onto the 386 SX data bus, where it is read by the 386 SX. The 82385SX terminates the 386 SX cycle without inserting any wait states.

#### 1.3.1.2 Read Misses

If the 82385SX determines that the requested data is not in the cache, the request is forwarded to the 82385SX local bus and the data retrieved from main memory. As the data returns from main memory, it is directed to the 386 SX and also written into the cache. Concurrently, the 82385SX updates the cache directory such that the next time this particular piece of information is requested by the 386 SX, the 82385SX will find it in the cache and return it with zero wait states.

The basic unit of transfer between main memory and cache memory in a cache subsystem is called the line size. In an 82385SX system, the line size is one 16-bit word. During a read miss, both 82385SX local bus byte enables are active. This insures that the 16-bit entry is written into the cache. (The 386 SX simply ignores what it did not request.) In any other type of 386 SX cycle that is forwarded to the 82385SX local bus, the logic levels of the 386 SX byte enables are duplicated on the 82385SX local bus.

The 82385SX does not actively fetch main memory data independently of the 386 SX. The 82385SX is essentially a passive device which only monitors the address bus and activates control signals. The read miss is the only mechanism by which main memory data is copied into the cache and validated in the cache directory.

In an isolated read miss, the number of wait states seen by the 386 SX is that required by the system memory to respond with data plus the cache comparison cycle (hit/miss decision). The cache system must determine that the cycle is a miss before it can begin the system memory access. However, since misses most often occur consecutively, the 82385SX will begin 386 SX address pipelined cycles to effectively "hide" the comparison cycle beyond the first miss (refer to Section 4.1.3).

The 82385SX can execute a memory access on the 82385SX local bus only if it currently owns the bus. If not, an 82385SX in master mode will run the cycle after the current master releases the bus. An 82385SX in slave mode will issue a hold request, and will run the cycle as soon as the request is acknowledged. (This is true for any read or write cycle that needs to run on the 82385SX local bus.)

#### 1.3.2 386TM SX MEMORY WRITE CYCLES

The 82385SX's "posted write" capability allows the majority of 386 SX memory write cycles to run with zero wait states. The primary memory update policy implemented in a posted write is the traditional cache "write through" technique, which implies that main memory is always updated in any memory write cycle. If the referenced location also happens to reside in the cache (a write hit), the cache is updated as well.

Beyond this, a posted write latches the 386 SX address, data, and cycle definition signals, and the 386 SX local bus is terminated without any wait states, even though the corresponding 82385SX local bus cycle is not yet completed, or perhaps not even started. A posted write is possible because the 82385SX's bus state machine, which is almost identical to the 386 SX bus state machine, is able to run 82385SX local bus cycles independently of the 386 SX. The only time the 386 SX sees write cycle wait states is when a previously latched (posted) write has not yet been completed on the 82385SX local bus or during an I/O write (which is not posted). An 386 SX write can be posted even if the 82385SX does not currently own the 82385SX local bus. In this case, an 82385SX in master mode will run the cycle as soon as the current master releases the bus, and an 82385SX in slave mode will request the bus and run the cycle when the request is acknowledged. The 386 SX is free to continue operating out of its cache (on the 386 SX local bus) during this time.

#### 1.3.3 NON-CACHEABLE CYCLES

Non-cacheable cycles fall into one of two categories: cycles decoded as non-cacheable, and cycles

that are by default non-cacheable according to the 82385SX's design. All non-cacheable cycles are forwarded to the 82385SX local bus. Non-cacheable cycles have no effect on the cache or cache directory.

The 82385SX allows the system designer to define areas of main memory as non-cacheable. The 386 SX address bus is decoded and the decode output is connected to the 82385SX's non-cacheable access (NCA#) input. This decoding is done in the first 386 SX bus state in which the non-cacheable cycle address becomes available. Non-cacheable read cycles resemble cacheable read miss cycles, except that the cache and cache directory are unaffected. NCA# defined non-cacheable writes, like most writes, are posted.

The 82385SX defines certain cycles as non-cacheable without using its non-cacheable access input. These include I/O cycles, interrupt acknowledge cycles, and halt/shutdown cycles. I/O reads and interrupt acknowledge cycles execute as any other non-cacheable read. I/O write cycles are not posted. The 386 SX is not allowed to continue until a ready signal is returned from the system. Halt/Shutdown cycles are posted. During a halt/shutdown condition, the 82385SX local bus duplicates the behavior of the 386 SX, including the ability to recognize and respond to a BHOLD request. (The 82385SX's bus watching mechanism is functional in this condition.)

#### 1.3.4 386TM SX LOCAL BUS CYCLES

386 SX Local Bus Cycles are accesses to resources on the 386 SX local bus other than to the 82385SX itself. The 82385SX simply ignores these accesses: they are neither forwarded to the system nor do they affect the cache. The designer sets aside memory and/or I/O space for local resources by decoding the 386 SX address bus and feeding the decode to the 82385SX's local bus access (LBA#) input. The designer can also decode the 386 SX cycle definition signals to keep specific 386 SX cycles from being forwarded to the system. For example, a multiprocessor design may wish to capture and remedy a 386 SX shutdown locally without having it detected by the rest of the system. Note that in such a design, the local shutdown cycle must be terminated by local bus control logic. The 387 SX Math Coprocessor is considered a 386 SX local bus resource, but it need not be decoded as such by the user since the 82385SX is able to internally recognize 387 SX accesses via the M/IO# and A23 pins.

# 1.3.5 SUMMARY OF 82385SX RESPONSE TO ALL 386TM SX CYCLES

Table 1-1 summarizes the 82385SX response to all 386 SX bus cycles, as conditioned by whether or not the cycle is decoded as local or non-cacheable. The table describes the impact of each cycle on the cache and on the cache directory, and whether or not the cycle is forwarded to the 82385SX local bus. Whenever the 82385SX local bus is marked "IDLE", it implies that this bus is available to other masters.

#### 1.3.6 BUS WATCHING

As previously discussed, the 82385SX "qualifies" a 386 SX bus cycle in the first bus state in which the address and cycle definition signals of the cycle become available. The cycle is qualified as read or write, cacheable or non-cacheable, etc. Cacheable cycles are further classified as hit or miss according to the results of the cache comparison, which accesses the 82385SX directory and compares the appropriate directory location (tag) to the current 386 SX address. If the cycle turns out to be non-cacheable or a 386 SX local bus access, the hit/miss decision is ignored. The cycle qualification requires one 386 SX state. Since the fastest 386 SX access is two states, the second state can be used for bus watching.

When the 82385SX does not own the system bus, it monitors system bus cycles. If another master writes into main memory, the 82385SX latches the system address and executes a cache look-up to see if the altered main memory location resides in the cache. If so (a snoop hit), the cache entry is marked invalid in the cache directory. Since the directory is at most only being used every other state to qualify 386 SX accesses, snoop look-ups are interleaved between 386 SX local bus look-ups. The cache directory is time multiplexed between the 386 SX address and the latched system address. The result is that all snoops are caught and serviced without slowing down the 386 SX, even when running zero wait state hits on the 386 SX local bus.

#### 1.3.7 CACHE FLUSH

The 82385SX offers a cache flush input. When activated, this signal causes the 82385SX to invalidate all data which had previously been cached. Specifically, all tag valid bits are cleared. (Refer to the 82385SX directory structure in Section 2.1.1.) There-

Table 1-1, 82385SX Response to 386™ SX Cycles

|                                     |                      |                | L              | I             |            |                                            |                      |       |                                                |                          |             |                                                          |                      |

|-------------------------------------|----------------------|----------------|----------------|---------------|------------|--------------------------------------------|----------------------|-------|------------------------------------------------|--------------------------|-------------|----------------------------------------------------------|----------------------|

| 386 SX Bus Cycle 823  Definition 8  | us Cycle<br>Ition    |                | 853            | 823           | 823<br>× × | 82385SX Response when Decoded as Cacheable | oonse<br>ded<br>ded  | Φ 10  | 82385SX Response when Decoded as Non-Cacheable | sponse<br>oded<br>neable | 82386<br>De | 82385X Response when Decoded as a 386SX Local Bus Access | 386SX                |

| D/C# W/R# 386 SX Cache              | R# 386 SX<br>Cycle   |                | Cache          | Cache         |            | Cache<br>Directory                         | 82385SX<br>Local Bus | Cache | Cache<br>Directory                             | 82385SX<br>Local Bus     | Cache       | Cache<br>Directory                                       | 82385SX<br>Local Bus |

| 0 0 INT ACK N/A —                   | N/A                  | N/A            |                | -             |            | 1                                          | INT ACK              | _     |                                                | INT ACK                  | 1           | 1                                                        | DLE                  |

| 0 1 UNDEFINED N/A                   | _                    | _              | N/A            |               |            |                                            | UNDEFINED            |       |                                                | UNDEFINED                |             |                                                          | DLE                  |

| 1 0 I/OREAD N/A —                   | N/A                  | N/A            |                | ı             |            | 1                                          | I/O READ             |       | _                                              | I/O READ                 |             | 1                                                        | IDLE                 |

| 1 1/OWRITE N/A —                    | N/A                  | N/A            |                | 1             |            | -                                          | I/O WRITE            | ı     | 1                                              | I/O WRITE                | _           | J                                                        | IDLE                 |

| 0 0 MEM CODE HIT CACHE<br>READ READ | Ħ                    | Ħ              |                | CACHE         |            | 1                                          | IDLE                 | 1     | I                                              | MEM                      | -           |                                                          | IDLE                 |

| MISS CACHE WRITE                    | CACHE<br>WRITE       | CACHE<br>WRITE | CACHE<br>WRITE |               |            | DATA<br>VALIDATION                         | MEM CODE<br>READ     |       |                                                | READ                     |             |                                                          |                      |

| 0 1 HALT/ N/A — SHUTDOWN            | N/A                  | N/A            |                | 1             |            | I                                          | HALT/<br>SHUTDOWN    | -     | Ι                                              | HALT/<br>SHUTDOWN        | ı           | ı                                                        | IDLE                 |

| 1 0 MEM DATA HIT CACHE<br>READ READ | MEM DATA HIT<br>READ | 片              |                | CACHE<br>READ |            | 1                                          | וסרב                 | -     | ı                                              | MEM<br>DATA              | ı           | ı                                                        | IDLE                 |

| MISS CACHE WRITE                    | _                    | _              | _              | _             |            | DATA<br>VALIDATION                         | MEM DATA<br>READ     |       |                                                | READ                     |             |                                                          |                      |

| 1 1 MEM DATA HIT CACHE WRITE WRITE  | 토                    | 토              |                | CACHE         |            | l                                          | MEM DATA<br>WRITE    | 1     | I                                              | MEM<br>DATA              | 1           | ı                                                        | IDLE                 |

| - WISS                              |                      |                |                | ı             |            | 1                                          | MEM DATA<br>WRITE    |       |                                                | WRITE                    |             |                                                          |                      |

• A dash (—) indicates that the cache and cache directory are unaffected. This table does not reflect how an access affects the LRU bit.

The 82385SX's response to 387<sup>TM</sup> SX accesses is the same as when decoded as a 386 SX Local Bus Access. An "IDLE" 82385SX Local Bus implies that this bus is available to other masters.

The only other operations that affect the cache directory are:

1. RESET or Cache Flush—all tag valid bits cleared.

2. Snoop Hit—corresponding line valid bit cleared.

fore, the cache is empty and subsequent cycles are misses until the 386 SX begins repeating the new accesses (hits). The primary use of the FLUSH input is for diagnostics and multi-processor support.

#### NOTE:

The use of this pin as a coherency mechanism may impact software transparency.

# 2.0 82385SX CACHE ORGANIZATION

The 82385SX supports two cache organizations: a simple direct mapped organization and a slightly more complex, higher performance two way set associative organization. The choice is made by strapping an 82385SX input (2W/D#) either high or low. This chapter describes the structure and operation of both organizations.

### 2.1 Direct Mapped Cache

### 2.1.1 DIRECT MAPPED CACHE STRUCTURE AND TERMINOLOGY

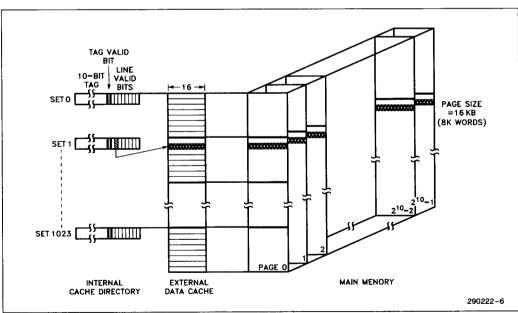

Figure 2-1 depicts the relationship between the 82385SX's internal cache directory, the external cache memory, and the 386 SX's physical address space. The 386 SX address space can conceptually be thought of as cache "pages" each being 8K words (16 Kbytes) deep. The page size matches the cache size. The cache can be further divided into 1024 (0 thru 1023) sets of eight words (8 x 16 bits). Each 16-bit word is called a "line". The unit of transfer between the main memory and cache is one line.

Each block in the external cache has an associated 19-bit entry in the 82385SX's internal cache directory. This entry has three components: a 10-bit "tag", a "tag valid" bit, and eight "line valid" bits. The tag acts as a main memory page number (10 tag bits support 210 pages). For example, if line 9 of page 2 currently resides in the cache, then a binary 2 is stored in the Set 1 tag field. (For any 82385SX direct mapped cache page in main memory. Set 0 consists of lines 0-7, Set 1 consists of lines 8-15, etc. Line 9 is shaded in Figure 2-1.) An important characteristic of a direct mapped cache is that line 9 of any page can only reside in line 9 of the cache. All identical page offsets map to a single cache location.

The data in a cache set is considered valid or invalid depending on the status of its tag valid bit. If clear, the entire set is considered invalid. If true, an individual line within the set is considered valid or invalid depending on the status of its line valid bit.

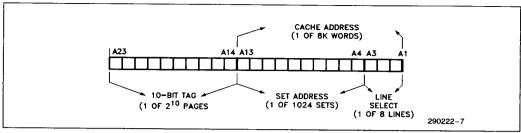

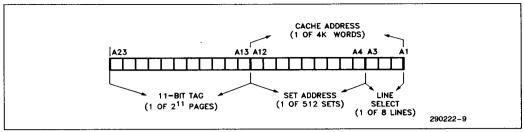

The 82385SX sees the 386 SX address bus (A1-A23) as partitioned into three fields: a 10-bit "taq"

Figure 2-1, Direct Mapped Cache Organiztion

5-713

Figure 2-2. 386™ SX Address Bus Bit Fields—Direct Mapped Organization

field (A14-A23), a 10-bit "set address" field (A4-A13), and a 3-bit "line select" field (A1-A3). (See Figure 2-2.) The lower 13 address bits (A1-A13) also serve as the "cache address" which directly selects one of 8K words in the external cache.

### 2.1.2 DIRECT MAPPED CACHE OPERATION

The following is a description of the interaction between the 386 SX, cache, and cache directory.

#### 2.1.2.1 Read Hits

When the 386 SX initiates a memory read cycle, the 82385SX uses the 10-bit set address to select one of 1024 directory entries, and the 3-bit line select field to select one of eight line valid bits within the entry. The 13-bit cache address selects the corresponding word in the cache. The 82385SX compares the 10-bit tag field (A14-A23 of the 386 SX access) with the tag stored in the selected directory entry. If the tag and upper address bits match, and if both the tag and appropriate line valid bits are set, the result is a hit, and the 82385SX directs the cache to drive the selected word onto the 386 SX data bus. A read hit does not alter the contents of the cache or directory.

### 2.1.2.2 Read Misses

A read miss can occur in two ways. The first is known as a "line" miss, and occurs when the tag and upper address bits match and the tag valid bit is set, but the line valid bit is clear. The second is called a "tag" miss, and occurs when either the tag and upper address bits do not match, or the tag valid bit is clear. (The line valid bit is a "don't care" in a tag miss.) In both cases, the 823855X forwards the 386 SX reference to the system, and as the returning data is fed to the 386 SX, it is written into the cache and validated in the cache directory.

In a line miss, the incoming data is validated simply by setting the previously clear line valid bit. In a tag miss, the upper address bits overwrite the previously stored tag, the tag valid bit is set, the appropriate line valid bit is set, and the other seven line valid bits are cleared. Subsequent tag hits with line misses will only set the appropriate line valid bit. (Any data associated with the previous tag is no longer considered resident in the cache.)

# 2.1.2.3 Other Operations That Affect the Cache and Cache Directory

The other operations that affect the cache and/or directory are write hits, snoop hits, cache flushes, and 82385SX resets. In a write hit, the cache is updated along with main memory, but the directory is unaffected. In a snoop hit, the cache is unaffected, but the affected line is invalidated by clearing its line valid bit in the directory. Both an 82385SX reset and cache flush clear all tag valid bits.

When a 386 SX CPU/82385SX system "wakes up" upon reset, all tag valid bits are clear. At this point, a read miss is the only mechanism by which main memory data is copied into the cache and validated in the cache directory. Assume an early 386 SX code access seeks (for the first time) line 9 of page 2. Since the tag valid bit is clear, the access is a tag miss, and the data is fetched from main memory. Upon return, the data is fed to the 386 SX and simultaneously written into line 9 of the cache. The set directory entry is updated to show this line as valid. Specifically, the tag and appropriate line valid bits are set, the remaining seven line valid bits cleared, and binary 2 written into the tag. Since code is sequential in nature, the 386 SX will likely next want line 10 of page 2, then line 11, and so on. If the 386 SX sequentially fetches the next six lines, these fetches will be line misses, and as each is fetched from main memory and written into the cache, its corresponding line valid bit is set. This is the basic flow of events that fills the cache with valid data. Only after a piece of data has been copied into the cache and validated can it be accessed in a zero wait state read hit. Also, a cache entry must have been validated before it can be subsequently altered by a write hit, or invalidated by a snoop hit.

An extreme example of "trashing" is if line 9 of page two is an instruction to jump to line 9 of page one, which is an instruction to jump back to line 9 of page two. Trashing results from the direct mapped cache characteristic that all identical page offsets map to a single cache location. In this example, the page one access overwrites the cached page two data, and the page two access overwrites the cached page one data. As long as the code jumps back and forth the hit rate is zero. This is of course an extreme case. The effect of trashing is that a direct mapped cache exhibits a slightly reduced overall hit rate as compared to a set associative cache of the same size.

## 2.2 Two Way Set Associative Cache

# 2.2.1 TWO WAY SET ASSOCIATIVE CACHE STRUCTURE AND TERMINOLOGY

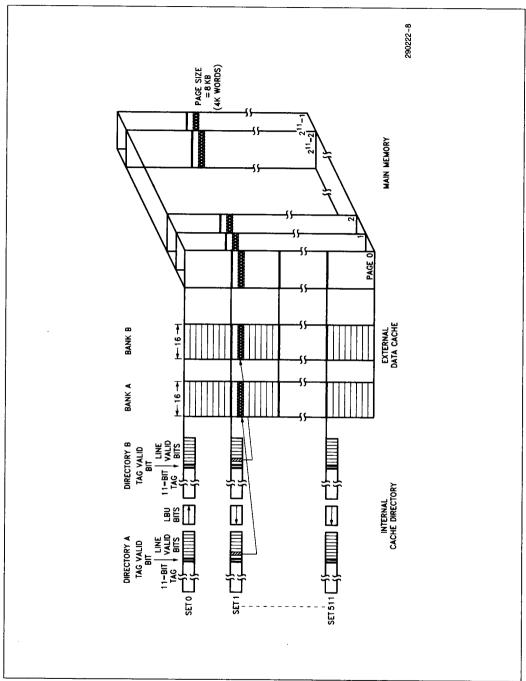

Figure 2-3 illustrates the relationship between the directory, cache, and 386 SX address space. Whereas the direct mapped cache is organized as one bank of 8K words, the two way set associative cache is organized as two banks (A and B) of 4K words each. The page size is halved, and the number of pages doubled. (Note the extra tag bit.) The cache now has 512 sets in each bank. (Two banks times 512 sets gives a total of 1024. The structure can be thought of as two half-sized direct mapped caches in parallel.) The performance advantage over a direct mapped cache is that all identical page offsets map to two cache locations instead of one. reducing the potential for thrashing. The 82385SX's partitioning of the 386 SX address bus is depicted in Figure 2-4.

### 2.2.2 LRU REPLACEMENT ALGORITHM

The two way set associative directory has an additional feature: the "least recently used" or LRU bit. In the event of a read miss, either bank A or bank B will be updated with new data. The LRU bit flags the candidate for replacement. Statistically, of two blocks of data, the block most recently used is the block most likely to be needed again in the near future. By flagging the least recently used block, the 82385SX ensures that the cache block replaced is the least likely to have data needed by the CPU.

# 2.2.3 TWO WAY SET ASSOCIATIVE CACHE OPERATION

#### 2.2.3.1 Read Hits

When the 386 SX initiates a memory read cycle, the 82385SX uses the 9-bit set address to select one of

512 sets. The two tags of this set are simultaneously compared with A13–A23, both tag valid bits checked, and both appropriate line valid bits checked. If either comparison produces a hit, the corresponding cache bank is directed to drive the selected word onto the 386 SX data bus. (Note that both banks will never concurrently cache the same main memory location.) If the requested data resides in bank A, the LRU bit is pointed toward B. If B produces the hit, the LRU bit is pointed toward A.

#### 2.2.3.2 Read Misses

As in direct mapped operation, a read miss can be either a line or tag miss. Let's start with a tag miss example. Assume the 386 SX seeks line 9 of page 2, and that neither the A or B directory produces a tag match. Assume also, as indicated in Figure 2-3, that the LRU bit points to A. As the data returns from main memory, it is loaded into offset 9 of bank A. Concurrently, this data is validated by updating the set 1 directory entry for bank A. Specifically, the upper address bits overwite the previous tag, the tag valid bit is set, the appropriate line valid bit is set, and the other seven line valid bits cleared. Since this data is the most recently used, the LRU bit is turned toward B. No change to bank B occurs.

If the next 386 SX request is line 10 of page two, the result will be a line miss. As the data returns from main memory, it will be written into offset 10 of bank A (tag hit/line miss in bank A), and the appropriate line valid bit will be set. A line miss in one bank will cause the LRU bit to point to the other bank. In this example, however, the LRU bit has already been turned toward B.

# 2.2.3.3 Other Operations That Affect the Cache and Cache Directory

Other operations that affect the cache and cache directory are write hits, snoop hits, cache flushes, and 82385SX resets. A write hit updates the cache along with main memory. If directory A detects the hit, bank A is updated. If directory B detects the hit, bank B is updated. If one bank is updated, the LRU bit is pointed towards the other.

If a snoop hit invalidates an entry, for example, in cache bank A, the corresponding LRU bit is pointed toward A. This insures that invalid data is the prime candidate for replacement in a read miss. Finally, resets and flushes behave just as they do in a direct mapped cache, clearing all tag valid bits.

### 3.0 82385SX PIN DESCRIPTION

The 82385SX creates the 82385SX local bus, which is a functional 386 SX interface. To facilitate under-

Figure 2-3. Two-Way Set Associative Cache Organization

5-716

Figure 2-4. 386™ SX Address Bus Bit Fields—Two-Way Set Associative Organization

standing, 82385SX local bus signals go by the same name as their 386 SX equivalents, except that they are preceded by the letter "B". The 82385SX local bus equivalent to ADS# is BADS#, the equivalent to NA# is BNA#, etc. This convention applies to bus states as well. For example, BT1P is the 82385SX local bus state equivalent to the 386 SX T1P state.

# 3.1 386™ SX CPU/82385SX Interface Signals

These signals form the direct interface between the 386 SX and the 82385SX.

### 3.1.1 386TM SX CPU/82385SX Clock (CLK2)

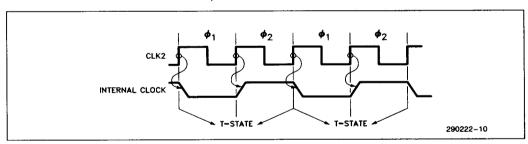

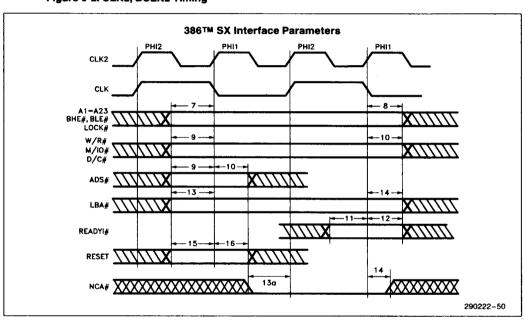

CLK2 provides the fundamental timing for a 386 SX CPU/82385SX system, and is driven by the same source that drives the 386 SX CLK2 input. The

82385SX, like the 386 SX, divides CLK2 by two to generate an internal "phase indication" clock. (See Figure 3-1.) The CLK2 period whose rising edge drives the internal clock low is called PHI1, and the CLK2 period that drives the internal clock high is called PHI2. A PHI1-PHI2 combination (in that order) is known as a "T" state, and is the basis for 386 SX bus cycles.

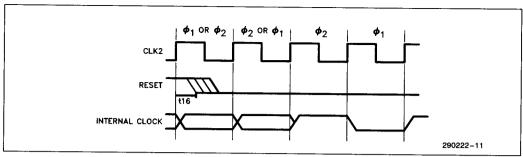

### 3.1.2 386TM SX CPU/82385SX RESET (RESET)

This input resets the 82385SX, bringing it to an initial known state, and is driven by the same source that drives the 386 SX RESET input. A reset effectively flushes the cache by clearing all cache directory tag valid bits. The falling edge of RESET is synchronized to CLK2, and used by the 82385SX to properly establish the phase of its internal clock. (See Figure 3-2.) Specifically, the second internal phase following the falling edge of RESET is PHI2.

Figure 3-1. CLK2 and Internal Clock

Figure 3-2. Reset/Internal Phase Relationship

# 3.1.3 386<sup>TM</sup> SX CPU/82385SX ADDRESS BUS (A1-A23), BYTE ENABLES (BHE#, BLE#), AND CYCLE DEFINITION SIGNALS (M/IO#, D/C#, W/R#, LOCK#)

The 82385SX directly connects to these 386 SX outputs. The 386 SX address bus is used in the cache directory comparison to see if data referenced by 386 SX resides in the cache, and the byte enables inform the 82385SX as to which portions of the data bus are involved in a 386 SX cycle. The cycle definition signals are decoded by the 82385SX to determine the type of cycle the 386 SX is executing.

### 3.1.4 386TM SX CPU/82385SX ADDRESS STATUS (ADS#) AND READY INPUT (READYI#)

ADS#, a 386 SX output, tells the 82385SX that new address and cycle definition information is available. READYI#, an input to both the 386 SX (via the 386 SX READY# input pin) and 82385SX, indicates the completion of a 386 SX bus cycle. ADS# and READYI# are used to track the 386 SX bus state.

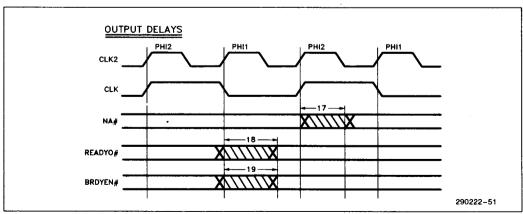

# 3.1.5 386™ SX NEXT ADDRESS REQUEST (NA#)

This 82385SX output controls 386 SX pipelining. It can be tied directly to the 386 SX NA# input, or it can be logically "AND"ed with other 386 SX local bus next address requests.

# 3.1.6 READY OUTPUT (READYO#) AND BUS READY ENABLE (BRDYEN#)

The 82385SX directly terminates all but two types of 386 SX bus cycles with its READYO# output. 386 SX local bus cycles must be terminated by the local device being accessed. This includes devices decoded using the 82385SX LBA# signal and 387 accesses. The other cycles not directly terminated by the 82385SX are 82385SX local bus reads, spe-

cifically cache read misses and non-cacheable reads. (Recall that the 82385SX forwards and runs such cycles on the 82385SX bus.) In these cycles the signal that terminates the 82385SX local bus access is BREADY# which is gated through to the 386 SX local bus such that the 386 SX and 82385SX local bus cycles are concurrently terminated. BRDYEN# is used to gate the BREADY# signal to the 386 SX.

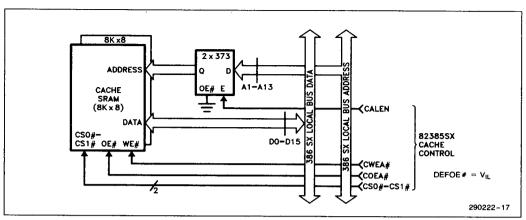

### 3.2 Cache Control Signals

These 82385SX outputs control the external 16 KB cache data memory.

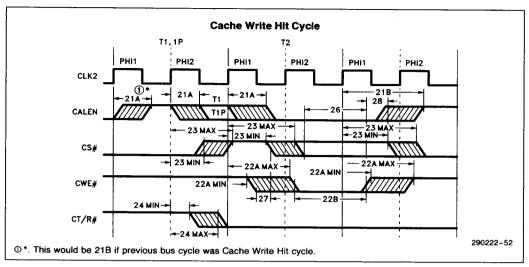

# 3.2.1 CACHE ADDRESS LATCH ENABLE (CALEN)

This signal controls the latch (typically an F or AS series 74373) that resides between the low order 386 SX address bits and the cache SRAM address inputs. (The outputs of this latch are the "cache address" described in the previous chapter.) When CALEN is high the latch is transparent. The falling edge of CALEN latches the current inputs which remain applied to the cache data memory until CALEN returns to an active high state.

# 3.2.2 CACHE TRANSMIT/RECEIVE (CT/R#)

This signal defines the direction of an optional data transceiver (typically an F or AS series 74245) between the cache and 386 SX data bus. When high, the transceiver is pointed towards the 386 SX local data bus (the SRAMs are output enabled). When low, the transceiver points towards the cache data memory. A transceiver is required if the cache is designed with SRAMs that lack an output enable control. A transceiver may also be desirable in a system that has a heavily loaded 386 SX local data bus. These devices are not necessary when using SRAMs which incorporate an output enable.

### 3.2.3 CACHE CHIP SELECTS (CS0#, CS1#)

These active low signals tie to the cache SRAM chip selects, and individually enable both bytes of the 16-bit wide cache. CSO# enables D0-D7 and CS1# enables D8-D15. During read hits, both bytes are enabled regardless of whether or not the 386 SX byte enables are active. (The 386 SX ignores what it did not request.) Also, both cache bytes are enabled in a read miss so as to update the cache with a complete line (word). In a write hit, only the cache bytes that correspond to active byte enables are selected. This prevents cache data from being corrupted in a partial word write.

### 3.2.4 CACHE OUTPUT ENABLES (COEA#, COEB#) AND WRITE ENABLES (CWEA#, CWEB#)

COEA# and COEB# are active low signals which tie to the cache SRAM or Transceiver output enables and respectively enable cache bank A or B. The state of DEFOE# (define cache output enable), an 82385SX configuration input, determines the functional definition of COEA# and COEB#.

If DEFOE# =  $V_{IL}$ , in a two-way set associative cache, either COEA# or COEB# is active during read hit cycles only, depending on which bank is selected. In a direct mapped cache, both are activated during read hits, so the designer is free to use either one. This COEx# definition best suits cache SRAMs with output enables.

If DEFOE# = V<sub>IH</sub>, COEx# is active during a read hit, read miss (cache update) and write hit cycles only. This COEx# definition best suits cache SRAMs without output enables. In such systems, transceivers are needed and their output enables must be active for writing, as well as reading, the cache SRAMs.

CWEA# and CWEB# are active low signals which tie to the cache SRAM write enables, and respectively enable cache bank A or B to receive data from the 386 SX data bus (386 SX write hit or read miss update). In a two-way set associative cache, one or the other is enabled in a read miss or write hit. In a direct mapped cache, both are activated, so the designer is free to use either one.

The various cache configurations supported by the 82385SX are described in Section 4.2.1.

# 3.3 386TM SX Local Bus Decode Inputs

These 82385SX inputs are generated by decoding the 386 SX address and cycle definition lines. These

active low inputs are sampled at the end of the first state in which the address of a new 386 SX cycle becomes available. (T1 or first T2P.)

### 3.3.1 386TM SX LOCAL BUS ACCESS (LBA#)

This input identifies a 386 SX access as directed to a resource (other than the cache) on the 386 SX local bus. (The 387 SX Math Coprocessor is considered a 386 SX local bus resource, but LBA# need not be generated as the 82385SX internally decodes 387 SX accesses.) The 82385SX simply ignores these cycles. They are neither forwarded to the system nor do they affect the cache or cache directory. Note that LBA# has priority over all other types of cycles. If LBA# is asserted, the cycle is interpreted as a 386 SX local bus access, regardless of the cycle type or status of NCA#. This allows any 386 SX cycle (memory, I/O, interrupt acknowledge, etc.) to be kept on the 386 SX local bus if desired.

### 3.3.2 NON-CACHEABLE ACCESS (NCA#)

This active low input identifies a 386 SX cycle as non-cacheable. The 82385SX forwards non-cacheable cycles to the 82385SX local bus and runs them. The cache and cache directory are unaffected.

NCA# allows a designer to set aside a portion of main memory as non-cacheable. Potential applications include memory-mapped I/O and systems where multiple masters access dual ported memory via different busses. Another possibility makes use of the 386 SX D/C# output. The 82385SX by default implements a unified code and data cache, but driving NCA# directly by D/C# creates a data only cache. If D/C# is inverted first, the result is a code only cache.

# 3.4 82385SX Local Bus Interface Signals

The 82385SX presents an "386 SX-like" front end to the system, and the signals discussed in this section are 82385SX local bus equivalents to actual 386 SX signals. These signals are named with respect to their 386 SX counterparts, but with the letter "B" appended to the front.

Note that the 82385SX itself does not have equivalent output signals to the 386 SX data bus (D0-D15) address bus (A1-A23), and cycle definition signals (M/IO\*, D/C\*, W/R\*). The 82385SX data bus (BD0-BD15) is actually the system side of a latching transceiver, and the 82385SX address bus and cycle definition signals (BA1-BA23, BM/IO\*, BD/C\*,

BW/R#) are the outputs of an edge-triggered latch. The signals that control this data transceiver and address latch are discussed in Section 3.5.

# 3.4.1 82385SX BUS BYTE ENABLES (BBHE#, BBLE#)

BBHE# and BBLE# are the 82385SX local bus equivalents to the 386 SX byte enables. In a cache read miss, the 82385SX drives both signals low, regardless of whether or not the 386 SX byte enables are active. This insures that a complete line (word) is fetched from main memory for the cache update. In all other 82385SX local bus cycles, the 82385SX duplicates the logic levels of the 386 SX byte enables. The 82385SX tri-states these outputs when it is not the current bus master.

### 3.4.2 82385SX BUS LOCK (BLOCK #)

BLOCK# is the 82385SX local bus equivalent to the 386 SX LOCK# output, and distinguishes between locked and unlocked cycles. When the 386 SX runs a locked sequence of cycles (and LBA# is negated), the 82385SX forwards and runs the sequence on the 82385SX local bus, regardless of whether any locations referenced in the sequence reside in the cache. A read hit will be run as if it is a read miss, but a write hit will update the cache as well as being completed to system memory. In keeping with 386 SX behavior, the 82385SX does not allow another master to interrupt the sequence. BLOCK# is tri-stated when the 82385SX is not the current bus master.

# 3.4.3 82385SX BUS ADDRESS STATUS (BADS#)

BADS# is the 82385SSX local bus equivalent of ADS#, and indicates that a valid address (BA1-BA23, BBHE#, BBLE#) and cycle definition (BM/IO#, BW/R#, BD/C#) are available. It is asserted in BT1 and BT2P states, and is tri-stated when the 82385SX does not own the bus.

### 3.4.4 82385SX BUS READY INPUT (BREADY #)

82385SX local bus cycles are terminated by BREADY#, just as 386 SX cycles are terminated by the 386 SX READY# input. In 82385SX local bus read cycles, BREADY# is gated by BRDYEN# onto the 386 SX local bus, such that it terminates both the 386 SX and 82385SX local bus cycles.

# 3.4.5 82385SX BUS NEXT ADDRESS REQUEST (BNA#)

BNA# is the 82385SX local bus equivalent to the 386 SX NA# input, and indicates that the system is

prepared to accept a pipelined address and cycle definition. If BNA# is asserted and the new cycle information is available, the 82385SX begins a pipelined cycle on the 82385SX local bus.

# 3.5 82385SX Bus Data Transceiver and Address Latch Control Signals

The 82385SX data bus is the system side of a latching transceiver (typically for F or AS series 74646), and the 82385SX address bus and cycle definition signals are the outputs of an edge-triggered latch (F or AS series 74374). The following is a discussion of the 82385SX outputs that control these devices. An important characteristic of these signals and the devices they control is that they ensure that BD0-BD15, BA1-BA23, BM/IO#, BD/C# and BW/R# reproduce the functionality and timing behavior of their 386 SX equivalents.

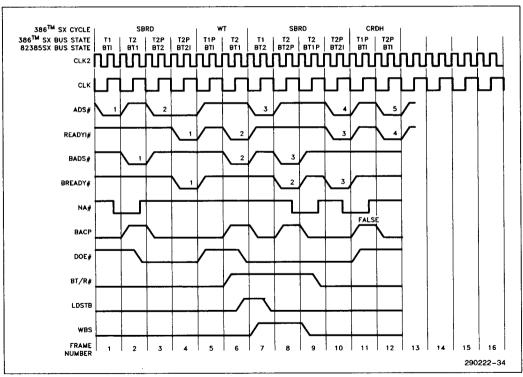

# 3.5.1 LOCAL DATA STROBE (LDSTB), DATA OUTPUT ENABLE (DOE#), AND BUS TRANSMIT/RECEIVE (BT/R#)

These signals control the latching data transceiver. BT/R# defines the transceiver direction. When high, the transceiver drives the 82385SX data bus in write cycles. When low, the transceiver drives the 386 SX data bus in 82385SX local bus read cycles. DOE# enables the transceiver outputs.

The rising edge of LDSTB latches the 386 SX data bus in all write cycles. The interaction of this signal and the latching transceiver is used to perform the 82385SX's posted write capability.

# 3.5.2 BUS ADDRESS CLOCK PULSE (BACP) AND BUS ADDRESS OUTPUT ENABLE (BAOE #)

These signals control the latch that drives BA1-BA23, BM/IO#, BW/R#, and BD/C#. In any 386 SX cycle that is forwarded to the 82385SX local bus, the rising edge of BACP latches the 386 SX address and cycle definition signals. BAOE# enables the latch outputs when the 82385SX is the current bus master and disables them otherwise

### 3.6 Status and Control Signals

# 3.6.1 CACHE MISS INDICATION (MISS#)

This output accompanies cacheable read and write miss cycles. This signal transitions to its active low state when the 82385SX determines that a cacheable 386 SX access is a miss. Its timing behavior

follows that of the 82385SX local bus cycle definition signals (BM/IO#, BD/C#, BW/R#) so that it becomes available with BADS# in BT1 or the first BT2P. MISS# is floated when the 82385SX does not own the bus, such that multiple 82385SX's can share the same node in multi-cache systems. (As discussed in Chapter 7, this signal also serves a reserved function in testing the 82385SX.)

#### 3.6.2 WRITE BUFFER STATUS (WBS)

The latching data transceiver is also known as the "posted write buffer". WBS indicates that this buffer contains data that has not yet been written to the system even though the 386 SX may have begun its next cycle. It is activated when 386 SX data is latched, and deactivated when the corresponding 82385SX local bus write cycle is completed (BREADY#). (As discussed in Chapter 7, this signal also serves a reserved function in testing the 82385SX.)

WBS can serve several functions. In multi-processor applications, it can act as a coherency mechanism by informing a bus arbiter that it should let a write cycle run on the system bus so that main memory has the latest data. If any other 82385SX cache subsystems are on the bus, they will monitor the cycle via their bus watching mechanisms. Any 82385SX that detects a snoop hit will invalidate the corresponding entry in its local cache.

#### 3.6.3 CACHE FLUSH (FLUSH)

When activated, this signal causes the 82385SX to clear all of its directory tag valid bits, effectively flushing the cache. (As discussed in Chapter 7, this signal also serves a reserved function in testing the 82385SX.) The primary use of the FLUSH input is for diagnostics and multi-processor support. The use of this pin as a coherency mechanism may impact software transparency.

The FLUSH input must be held active for at least 4 CLK (8 CLK2) cycles to complete the flush sequence. If FLUSH is still active after 4 CLK cycles, any accesses to the cache will be misses and the cache will not be updated (since FLUSH is active).

# 3.7 Bus Arbitration Signals (BHOLD and BHLDA)

In master mode, BHOLD is an input that indicates a request by a slave device for bus ownership. The

82385SX acknowledges this request via its BHLDA output. (These signals function identically to the 386 SX HOLD and HLDA signals.)

The roles of BHOLD and BHLDA are reversed for an 82385SX in slave mode. BHOLD is now an output indicating a request for bus ownership, and BHLDA an input indicating that the request has been granted.

## 3.8 Coherency (Bus Watching) Support Signals (SA1-SA23, SSTB#, SEN)

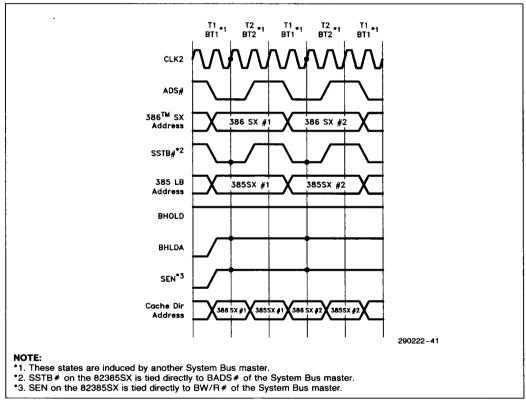

These signals form the 82385SX's bus watching interface. The Snoop Address Bus (SA1-SA23) connects to the system address lines if masters reside at both the system and 82385SX local bus levels, or the 82385SX local bus address lines if masters reside only at the 82385SX local bus level. Snoop Strobe (SSTB#) indicates that a valid address is on the snoop address inputs. Snoop Enable (SEN) indicates that the cycle is a write. In a system with masters only at the 82385SX local bus level, SA1-SA23, SSTB#, and SEN can be driven respectively by BA1-BA23, BADS#, and BW/R# without any support circuitry.

# 3.9 Configuration Inputs (2W/D#, M/S#, DEFOE#)

These signals select the configurations supported by the 82385SX. They are hardware strap options and must not be changed dynamically. 2W/D# (2-Way/Direct Mapped Select) selects a two-way set associative cache when tied high, or a direct mapped cache when tied low. M/S# (Master/Slave Select) chooses between master mode (M/S# high) and slave mode (M/S# low). DEFOE# defines the functionality of the 82385SX cache output enables (COEA# and COEB#). DEFOE# allows the 82385SX to interface to SRAMs with output enables (DEFOE# low) or to SRAMs requiring transceivers (DEFOE# high).

### 3.10 Reserved Pins (RES)

Some pins on the 82385SX are reserved for internal testing and future cache features. To assure compatibility and functionality, these reserved pins must be configured as shown in Table 3.10.1.

Table 3.10.1. Reserved Pin Connections

| PGA<br>Pin Location | PQFP<br>Pin Location | Logic Level |

|---------------------|----------------------|-------------|

| A12                 | 1                    | High        |

| A13                 | 131                  | High        |

| B10                 | 7                    | High        |

| B11                 | 3                    | High        |

| B12                 | 132                  | High        |

| C10                 | 4                    | High        |

| C11                 | 2                    | High        |

| G13                 | 117                  | High        |

| H12                 | 110                  | High        |

| J3                  | 60                   | High        |

| J14                 | 109                  | High        |

| K1                  | 58                   | High        |

| K2                  | 59                   | High        |

| K3                  | 62                   | High        |

| L1                  | 61                   | High        |

| L2                  | 63                   | High        |

| L3                  | 64                   | High        |

| L12                 | 100                  | No Connect  |

| L14                 | 102                  | High        |

| M13                 | 101                  | No Connect  |

| N6                  | 75                   | No Connect  |

| P5                  | 76                   | No Connect  |

### 4.0 386 SX LOCAL BUS INTERFACE

The following is a detailed description of how the 82385SX interfaces to the 386 SX and to 386 SX local bus resources. Items specifically addressed are the interfaces to the 386 SX, the cache SRAMs, and the 387 SX Math Coprocessor.

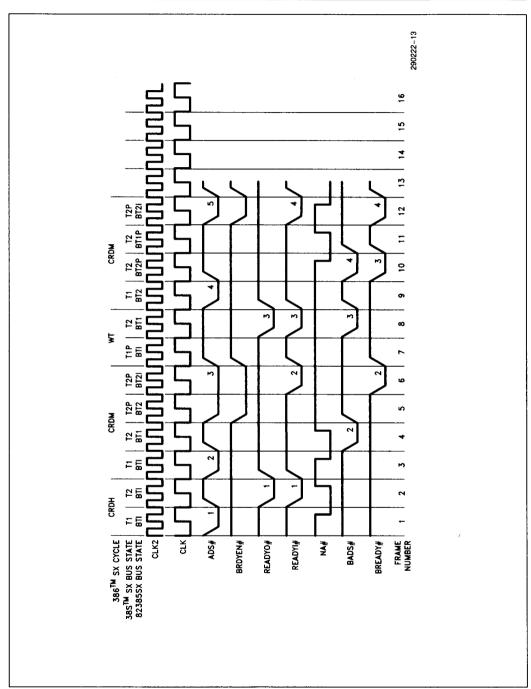

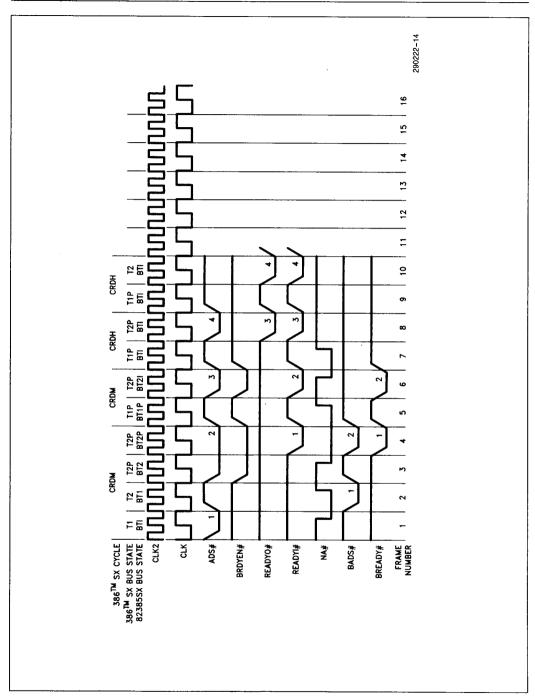

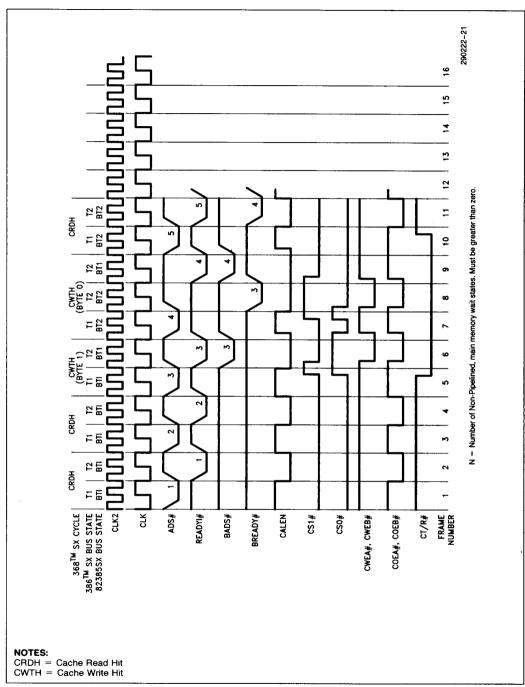

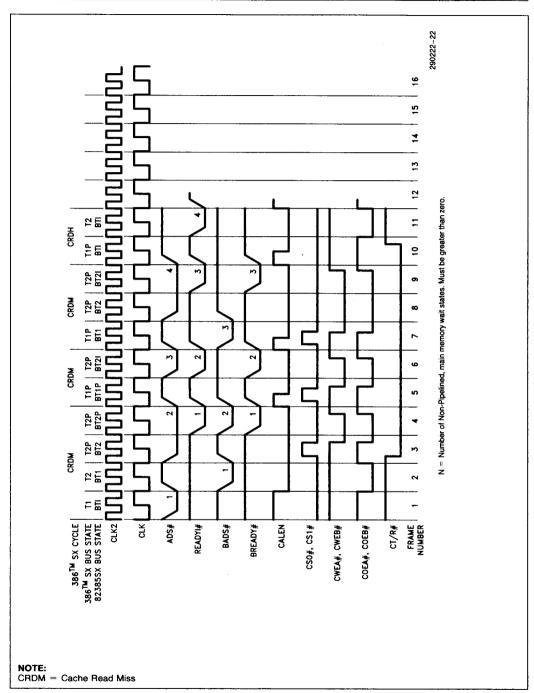

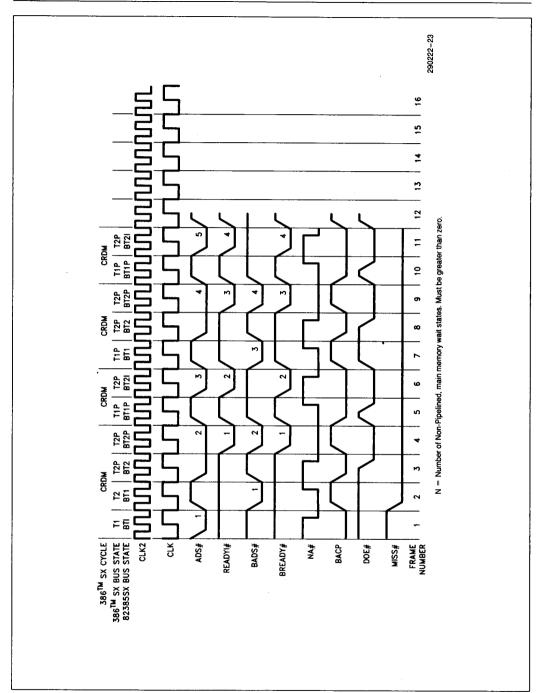

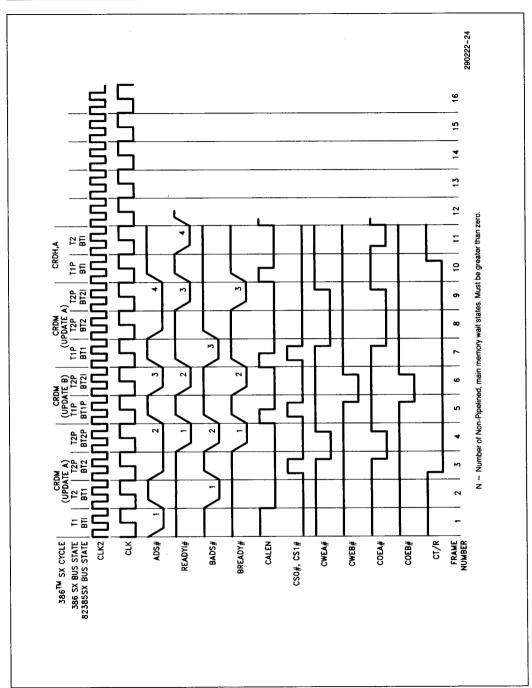

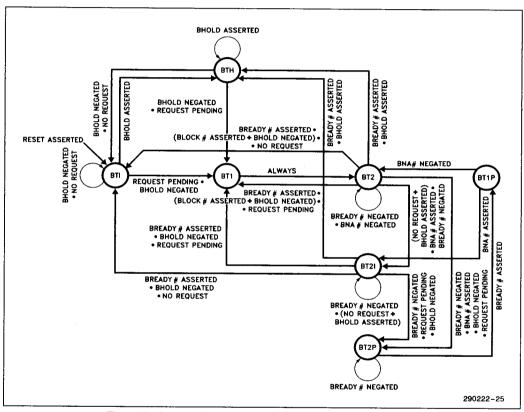

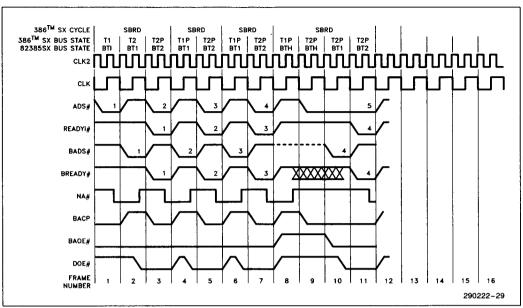

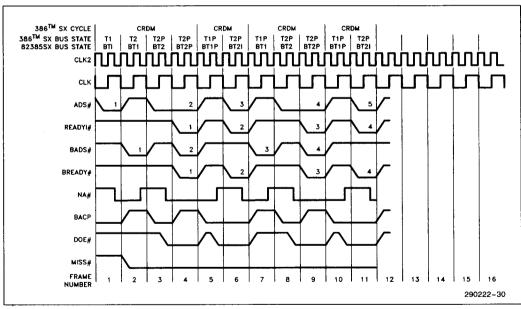

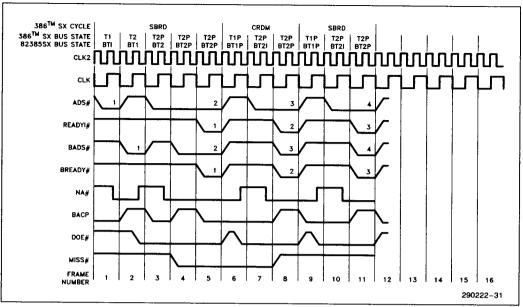

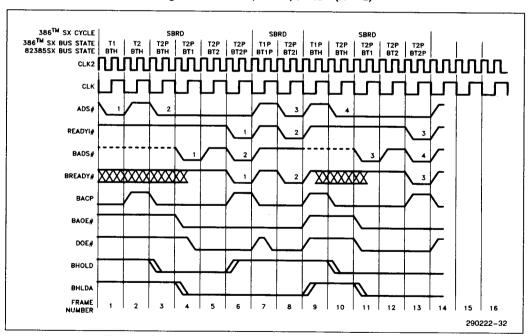

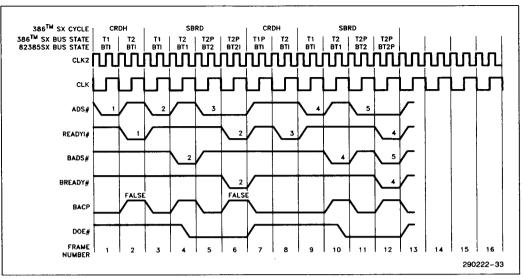

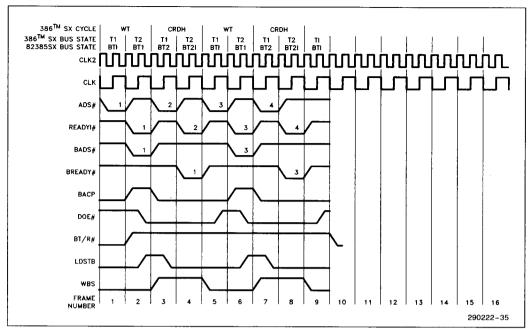

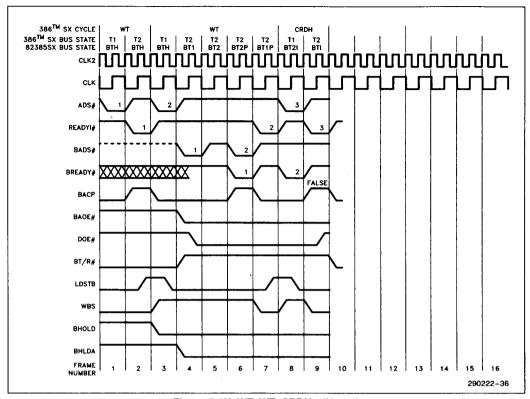

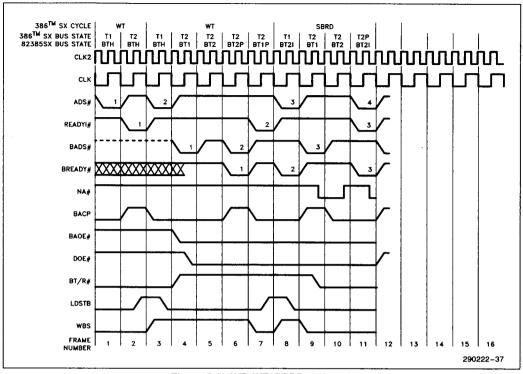

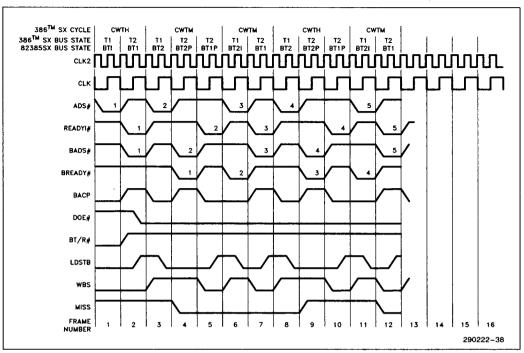

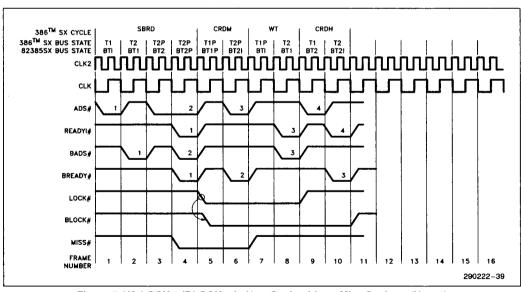

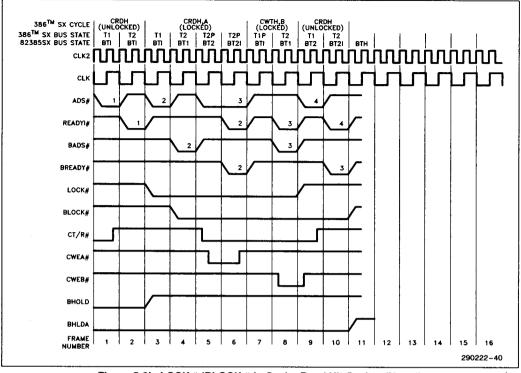

The many timing diagrams in this and the next chapter provide insight into the dual pipelined bus structure of a 386 SX CPU/82385SX system. It's important to realize, however, that one need not know every possible cycle combination to use the 82385SX. The interface is simple, and the dual bus operation invisible to the 386 SX and system. To facilitate discussion of the timing diagrams, several conventions have been adopted. Refer to Figure 4-2A, and note that 386 SX bus cycles, 386 SX bus states, and 82385SX bus states are identified along the top. All states can be identified by the "frame numbers" along the bottom. The cycles in Figure 4-2A include a cache read hit (CRDH), a cache read miss (CRDM), and a write (WT). WT represents any write, cacheable or not. When necessary to distinguish cacheable writes, a write hit goes by CWTH and a write miss by CWTM. Non-cacheable system reads go by SBRD. Also, it is assumed that system bus pipelining occurs even though the BNA# signal is not shown. When the system pipeline begins is a function of the system bus controller.

386 SX bus cycles can be tracked by ADS# and READYI#, and 82385SX cycles by BADS# and BREADY#. These four signals are thus a natural choice to help track parallel bus activity. Note in the timing diagrams that 386 SX cycles are numbered using ADS# and READYI#, and 82385SX cycles using BADS# and BREADY#. For example, when the address of the first 386 SX cycle becomes available, the corresponding assertion of ADS# is marked "1", and the READYI# pulse that terminates the cycle is marked "1" as well. Whenever a 386 SX cycle is forwarded to the system, its number is forwarded as well so that the corresponding 82385SX bus cycle can be tracked by BADS# and BREADY#.

The "N" value in the timing diagrams is the assumed number of main memory wait states inserted in a non-pipelined 82385SX bus cycle. For example, a non-pipelined access to N = 2 memory requires a total of four bus states, while a pipelined access requires three. (The pipeline advantage effectively hides one main memory wait state.)

### 4.1 Processor Interface

This section presents the 386 SX CPU/82385SX hardware interface and discusses the interaction and timing of this interface. Also addressed is how to decode the 386 SX address bus to generate the 82385SX inputs LBA# and NCA#. (Recall that LBA# allows memory and/or I/O space to be set aside for 386 SX local bus resources; and NCA# allows system memory to be set aside as non-cacheable.)

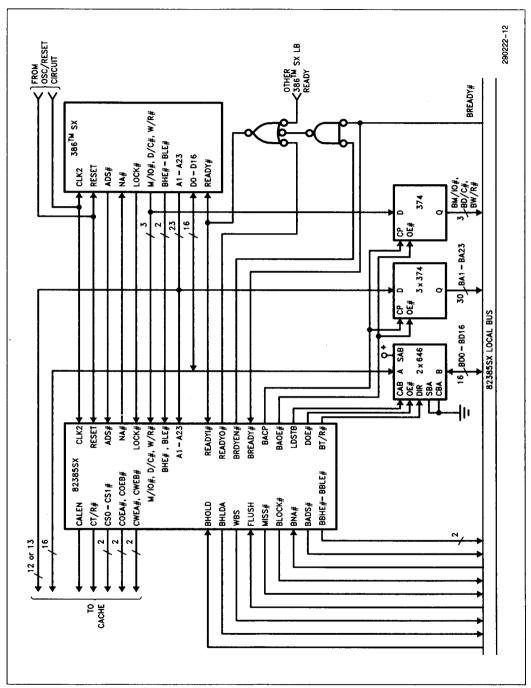

### 4.1.1 HARDWARE INTERFACE

Figure 4-1 is a diagram of a 386 SX CPU/82385SX system, which can be thought of as three distinct interfaces. The first is the 386 SX CPU/82385SX interface (including the Ready Logic). The second is the cache interface, as depicted by the cache control bus in the upper left corner of Figure 4-1. The third is the 82385SX bus interface, which includes both direct connects and signals that control the 74374 address/cycle definition latch and 74646 latching data transceiver. (The 82385SX bus interface is the subject of the next chapter.)

As seen in Figure 4-1, the 386 SX CPU/82385SX interface is a straightforward connection. The only necessary support logic is that required to sum all ready sources.

5-722

Figure 4-1. 386TM SX CPU/82385SX Interface

5-723

#### 4.1.2 READY GENERATION

Note in Figure 4-1 that the ready logic consists of two gates. The upper three-input AND gate (shown as a negative logic OR) sums all 386 SX local bus ready sources. One such source is the 82385SX READYO# output, which terminates read hits and posted writes. The output of this gate drives the 386 SX READY# input and is monitored by the 82385SX (via READYI#) to track the 386 SX bus state.

When the 82385SX forwards a 386 SX read cycle to the 82385SX bus (cache read miss or non-cacheable read), it does not directly terminate the cycle via READYO#. Instead, the 386 SX and 82385SX bus cycles are concurrently terminated by a system ready source. This is the purpose of the additional two-input OR gate (negative logic AND) in Figure 4-1. When the 82385SX forwards a read to the 82385SX bus, it asserts BRDYEN# which enables the system ready signal (BREADY#) to directly terminate the 386 SX bus cycle.

Figure 4-2A and 4-2B illustrate the behavior of the signals involved in ready generation. Note in cycle 1 of Figure 4-2A that the 82385SX READYO# directly terminates the hit cycle. In cycle 2, READYO# is not activated. Instead the 82385SX BRDYEN# is activated in BT2, BT2P, or BT2I states such that BREADY# can concurrently terminate the 386 SX and 82385SX bus cycles (frame 6). Cycle 3 is a posted write. The write data becomes available in T1P (frame 7), and the address, data, and cycle definition of the write are latched in T2 (frame 8). The 386 SX cycle is terminated by READYO# in frame 8 with no wait states. The 82385SX, however, sees the write cycle through to completion on the 82385SX bus where it is terminated in frame 10 by BREADY#. In this case, the BREADY # signal is not gated through to the 386 SX. Refer to Figures 4-2A and 4-2B for clarification.

# 4.1.3 NA# AND 386 SX LOCAL BUS PIPELINING

Cycle 1 of Figure 4-2A is a typical cache read hit. The 386 SX address becomes available in T1, and the 82385SX uses this address to determine if the referenced data resides in the cache. The cache look-up is completed and the cycle qualified as a hit or miss in T1. If the data resides in the cache, the cache is directed to drive the 386 SX data bus, and the 82385SX drives its READYO# output so the cycle can be terminated at the end of the first T2 with no wait states.

Although cycle 2 starts out like cycle 1, at the end of T1 (frame 3), it is qualified as a miss and forwarded to the 82385SX bus. The 82385SX bus cycle begins

one state after the 386 SX bus cycle, implying a one wait state overhead associated with cycle 2 due to the look-up. When the 82385SX encounters the miss, it immediately asserts NA#, which puts the 386 SX into pipelined mode. Once in pipelined mode, the 82385SX is able to qualify a 386 SX cycle using the 386 SX pipelined address and control signals. The result is that the cache look-up state is hidden in all but the first of a contiguous sequence of read misses. This is shown in the first two cycles, both read misses, of Figure 4-2B. The CPU sees the look-up state in the first cycle, but not in the second. In fact, the second miss requires a total of only two states, as not only does 386 SX pipelining hide the look-up state, but system pipelining hides one of the main memory wait states. (System level pipelining via BNA# is discussed in the next chapter.) Several characteristics of the 82385SX's pipelining of the 386 SX are as follows:

- The above discussion applies to all system reads, not just cache read misses.