# 82961KA PAGE PRINTER CONTROLLER

- High Integration i960® Page Printer Controller<sup>(1)</sup>

- Direct Interface to 32-bit 80960KA or KB<sup>(2)</sup> Embedded Processors

- Direct Non-Impact Printer Video Interface

- Automatic DMA Burst DRAM Access to Transmit Video Image

- Internal Phase Lock Loop

- Top and Left Margin, Page Height and Width

- Direct Generic Printer Engine Interface to TEC, Canon, Ricoh and Okidata Printer Engines

- Programmable ROM/EPROM Interface

- Direct Interface to Two Banks

- Expandable to Eight Banks

- Programmable ROM Size and Wait States

- Programmable System Timer

- **Programmable DRAM interface**

- Direct Interface to Four Banks

- Programmable DRAM Size and Wait States

- Page Mode Cache to Reduce Wait States on First Access

- Transparent Refresh of DRAM Banks

- Interfaces to 16- and 32-bit DRAM Systems

- Programmable I/O Control

- Chip-Select, Access Time, Recovery Time

- Wait State Control for Eight External Devices

- Burst Interface Support for i960 KA/KB Bus

- Automatic Data Conversion from 16-bit Font Cartridge to 32-bit i960 Embedded Processor Format

- Low-Cost 132-Lead Plastic Quad Flat Pack (PQFP)

Intel's 82961KA page printer controller is the first member of a new family of page printer companion peripherals that address the need for high integration and cost reduction. It is designed to interface Intel's 80960K-series of embedded processors to a variety of non-impact or laser printer mechanisms. The 82961KA controller contains complete DRAM, ROM and I/O controllers, the associated logic required to control virtually all non-impact printer mechanisms, a programmable wait state generator and programmable chip select generation logic. The 82961KA controller—coupled with an 80960Kx plus DRAM, ROM and the appropriate I/O—forms the nucleus for a cost-effective non-impact printer controller.

Designs that employ the 82961KA controller provide substantial system performance improvements. The 82961KA device decouples DRAM and video output subsystems from the synchronous 80960KA/KB bus to achieve increased performance. The 82961KA device's unique programmable video output controller manages virtually every aspect of memory address generation, timing and control once the device begins to produce the video output signal.

February 1993 Order Number: 272134-003

<sup>1.</sup> The 82961KA i960 Page Printer Controller is based on the single-chip controller architecture created by Peerless Systems Corp.

<sup>2.</sup> Throughout this data sheet, 80960Kx refers to the 80960KA and KB processors.

# 82961KA Page Printer Controller

| CONTENTS PA                                                     | GE   | CONTENTS PAGE                                        |

|-----------------------------------------------------------------|------|------------------------------------------------------|

| 1.0 PURPOSE 3-                                                  | -331 | 5.0 ABSOLUTE MAXIMUM RATINGS                         |

| 2.0 82961KA FUNCTIONAL OVERVIEW3                                | -331 | 6.0 TARGETED DC CHARACTERISTICS                      |

| 3.0 PACKAGE INFORMATION 3-<br>3.1 Package Introduction 3-       | -332 | 7.0 TARGETED AC CHARACTERISTICS                      |

| 3.2 Pin Descriptions 3. 3.3 82961KA PQFP Pinout 3.              |      | 7.1 Targeted L-Bus Timing Specifications             |

| 3.4 Mechanical Data3                                            | -339 | 7.2 L-Bus Operational Waveforms 3-352                |

| 3.5 Package Thermal Specification 3. 3.6 Package Dimensions and | -339 | 7.3 Targeted DRAM Controller Timing Specifications   |

| Mounting3                                                       | -340 | 7.4 DRAM Controller Operational Waveforms            |

| <b>4.0 ELECTRICAL SPECIFICATIONS</b> 3                          | -341 | 7.5 ROM and I/O Controller                           |

| 4.1 Power and Grounding 3                                       | -341 | Operational Waveforms 3-362                          |

| 4.2 Power Decoupling Recommendations                            | -341 | 7.6 Targeted Printer Video and Communications Timing |

| 4.3 Connection Recommendations 3                                | -341 | Specifications 3-368                                 |

| CONTE                  | ENTS PAI                                                                            | GE   | CONTE          | ENTS                                                 | PAGE           |

|------------------------|-------------------------------------------------------------------------------------|------|----------------|------------------------------------------------------|----------------|

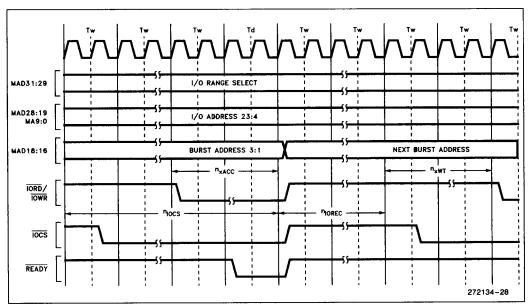

| FIGURES                |                                                                                     |      | Figure 30      | I/O Address Transition in<br>Burst Mode              | 3-367          |

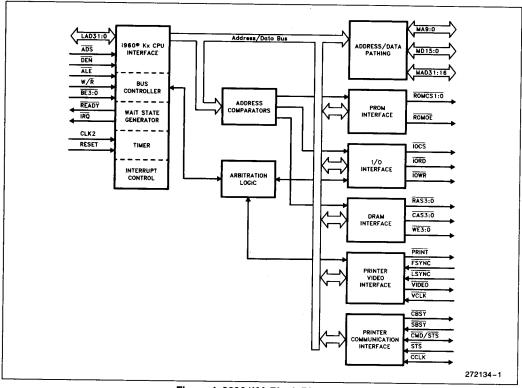

| Figure 1               | 82961KA Block Diagram 3-3                                                           | 332  | Figure 31      |                                                      |                |

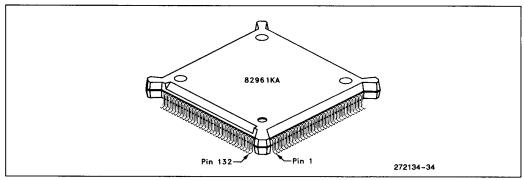

| Figure 2               | 82961KA 132-Lead Plastic<br>Quad Flat Pack (PQFP)<br>Package3-3                     |      | J              | Printer Video Interface Timing                       |                |

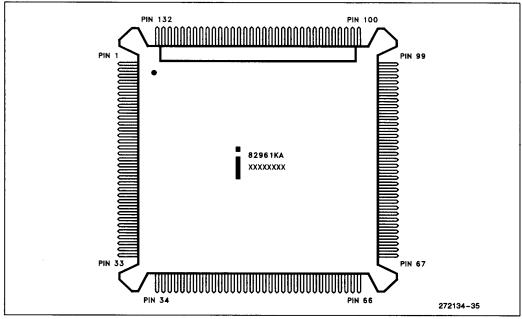

| Figure 3               | 82961KA PQFP Package<br>(Top View)3-3                                               |      | Figure 33      | Printer Communications<br>Interface Timing (82961KA  |                |

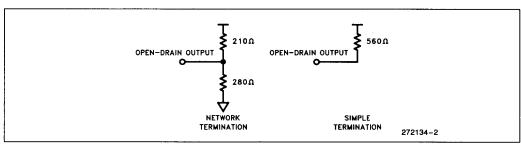

| Figure 4               | Network and Simple Termination Examples 3-3                                         | 841  | Figure 34      |                                                      | . 3-3/1        |

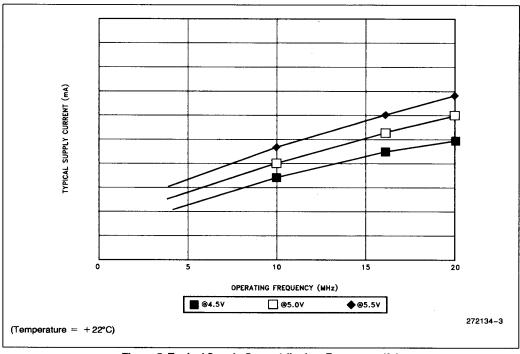

| Figure 5               | Typical Supply Current (I <sub>CC</sub> ) vs. Frequency (f <sub>C</sub> ) 3-3       |      |                | Interface Timing (CCLK Supplied Externally)          | . 3-371        |

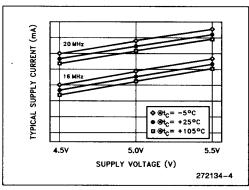

| Figure 6               | Typical Supply Current (I <sub>CC</sub> ) vs. Supply Voltage (V <sub>CC</sub> ) 3-3 |      | TABLES Table 1 | Din Danadatia                                        |                |

| Figure 7               | AC Test Loads                                                                       | 45   | i abie i       | Pin Description Nomenclature                         | 3-333          |

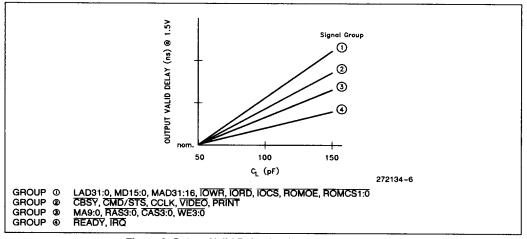

| Figure 8               | Output Valid Delay (t <sub>OV</sub> ) vs.                                           |      | Table 2        | L-Bus Interface Signals                              | 3-332<br>3-332 |

|                        | Load Capacitance 3-3                                                                | 45   | Table 3        | Memory Interface Signals                             | 3-334          |

| Figure 9               | Clock Input Waveforms 3-3                                                           | 46   | Table 4        | ROM Signals                                          |                |

| Figure 10              | Synchronous Input/Output                                                            | •    | Table 5        | I/O Interface Signals                                |                |

|                        | Waveforms3-3                                                                        |      | Table 6        | Printer Video Interface                              |                |

| Figure 11              | Reset Timing 3-3                                                                    | 49   |                | Signals                                              | . 3-335        |

| Figure 12              | L-Bus Relative Timings 3-3                                                          |      | Table 7        | Printer Communications                               |                |

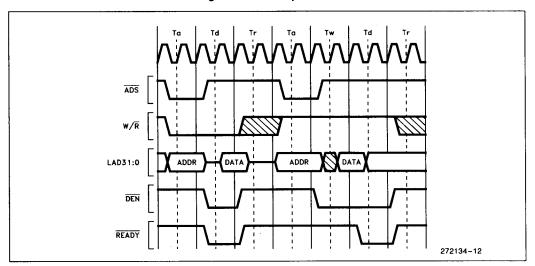

| Figure 13              | L-Bus Operation 3-3                                                                 | 52 . | Table 8        | Interface Signals                                    |                |

| Figure 14              | Read/Write 3-3                                                                      | 52   | Table 9        | Processor Control Signals PQFP Pin Name with Package | )              |

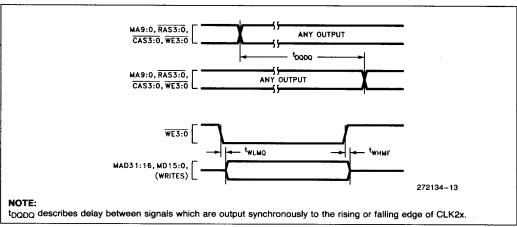

| Figure 15              | DRAM Relative Timings 3-3                                                           | 53 - | Table 10       | Location (Signal Order)                              | 3-337          |

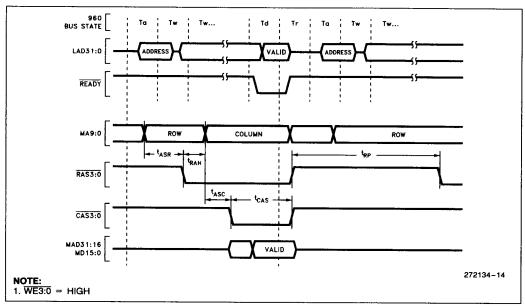

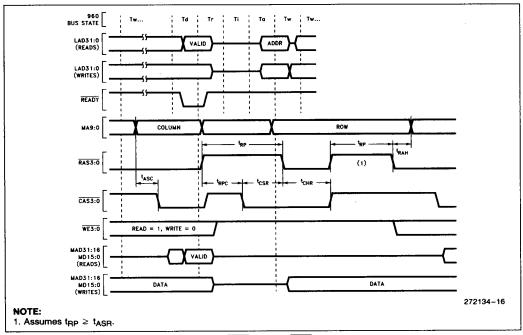

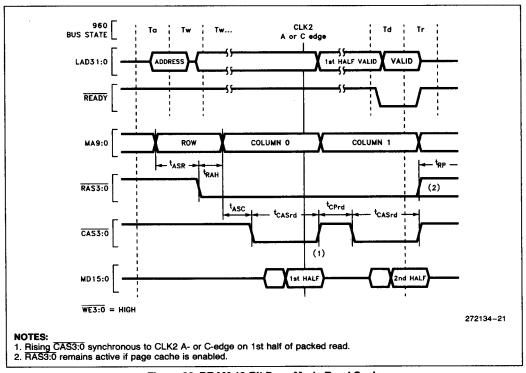

| Figure 16              | DRAM Non-Page Read<br>Cycle3-3:                                                     | 55   |                | PQFP Pin Name with Package Location (Pin Order)      | :<br>3-338     |

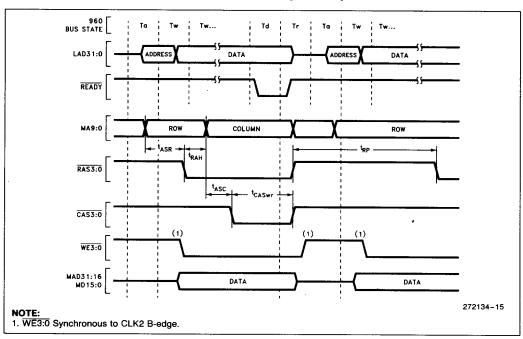

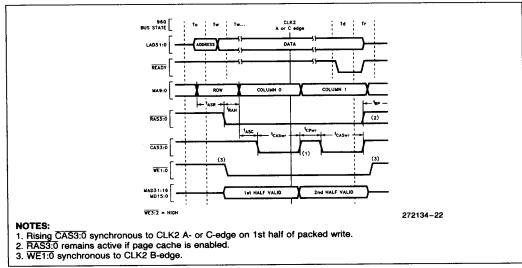

| Figure 17              | DRAM Non-Page Write                                                                 |      |                | 82961KA PQFP Package Thermal Characteristics         | 3-339          |

| Figure 18              | Cycle                                                                               |      | Γable 12       | Absolute Ratings                                     | 3-342          |

|                        | Refresh Cycle 3-39                                                                  | 56   | Γable 13       | Targeted Operating Conditions                        | 3-342          |

| Figure 19<br>Figure 20 |                                                                                     |      | Γable 14       | Targeted DC Characteristics                          |                |

|                        | Cycle 3-38                                                                          |      |                | Input Clock Specifications                           |                |

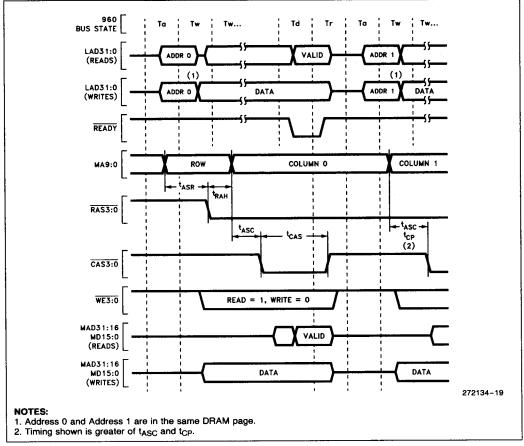

| Figure 21              | DRAM Page Hit 3-38                                                                  |      | Table 16       | Synchronous Input and Output                         | •              |

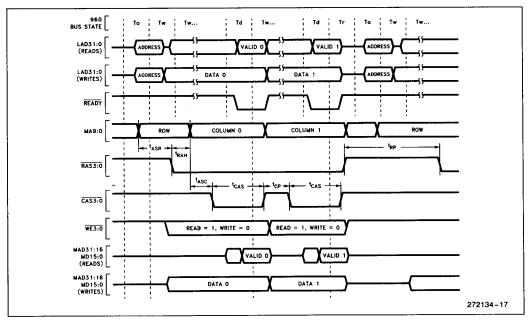

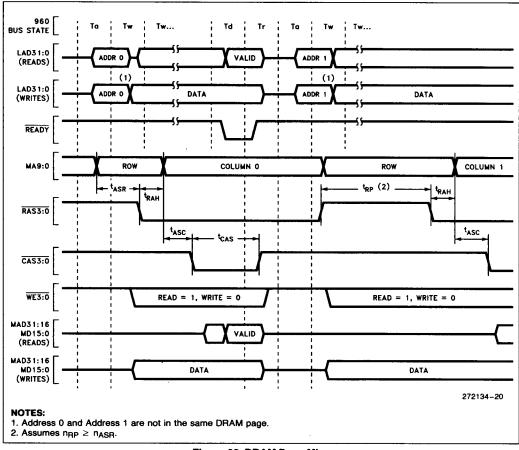

| Figure 22              | DRAM Page Miss 3-38                                                                 | 59   |                | Specifications                                       | 3-347          |

| Figure 23              | DRAM 16-Bit Page Mode<br>Read Cycle                                                 |      | able 17        | L-Bus Relative Timing Specifications                 | 3-350          |

| Figure 24              | DRAM Aligned 16-Bit Page<br>Mode Write Cycle 3-36                                   |      | able 18        | DRAM Controller Relative<br>Timings                  |                |

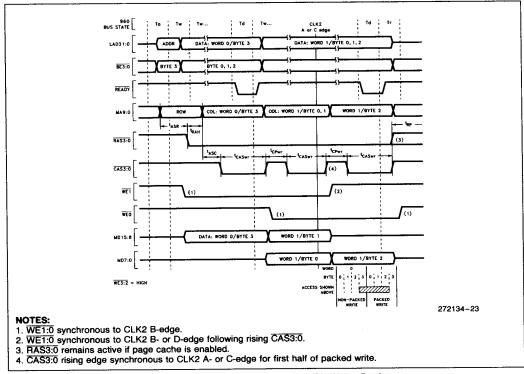

| Figure 25              | DRAM Non-Aligned 16-Bit<br>Write Cycle 3-36                                         | 7    | able 19        | DRAM Controller<br>Programmable Timings              |                |

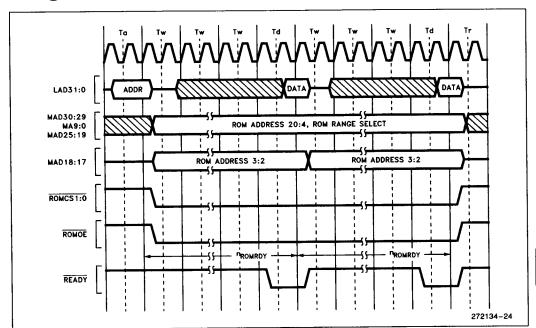

| Figure 26              | ROM Burst Read 3-36                                                                 | 33 T | able 20        | ROM and I/O Controller                               |                |

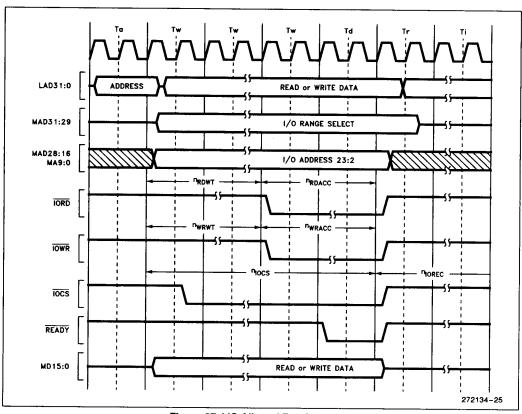

| Figure 27              | I/O Aligned Read or Write 3-36                                                      | 3.4  |                | Programmable Timings                                 | 3-362          |

| -                      | I/O Packed Read 3-36                                                                |      | able 21        | Printer Video Interface<br>Timings                   | 2 200          |

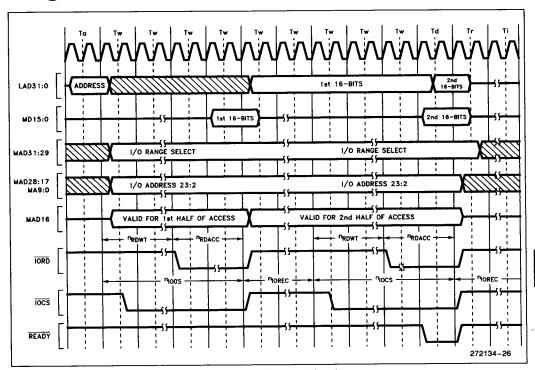

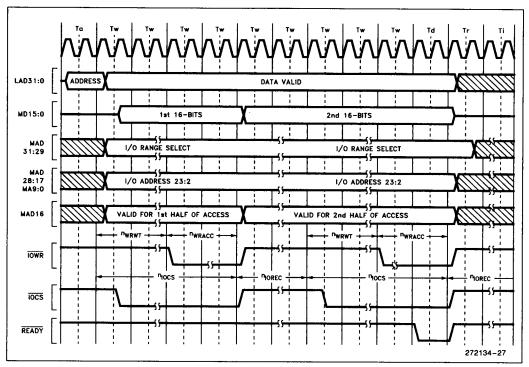

|                        | I/O Packed Write 3-36                                                               |      | able 22        | Printer Communications                               | 3-368          |

#### 1.0 PURPOSE

This data sheet describes the 82961KA page printer controller. It provides the information required to begin designing with the 82961KA printer controller. It contains functional and physical descriptions, electrical characteristics and specifications, absolute maximum ratings and package and pin definitions.

# 2.0 82961KA FUNCTIONAL OVERVIEW

The 82961KA integrates onto a single chip all the "glue" or support logic required in a 80960Kx processor design with a high performance interface to non-impact printers. 82961KA functional blocks are:

- · 80960K-Series L-Bus Interface

- ROM Interface

- DRAM interface

- I/O Interface

- Printer Video Interface

- Printer Communication Interface

- System Timer

The 82961KA is the first member of a new family of page printer companion peripherals. It is intended to

operate in the non-impact printer environment. However, many of its features make it extremely wellsuited for other applications. The 82961KA provides a direct interface between the Intel 80960Kx microprocessor and system memory, communication channels and printer engine.

The 82961KA is designed for flexibility, ease of use and optimum performance while employing a minimal number of external components. A page printer's host communication environment can range from a simple serial or parallel port to a complete Ethernet implementation. To support this vast range, the 82961KA is not limited to any specific communication mechanism. Instead, the 82961KA generates chip-selects and control signals that allow the user to easily connect standard communication devices to the 80960Kx. Additionally, the 82961KA can be used in other operating environments to enhance Intel 80960Kx microprocessors by providing memory interfaces and peripheral timing controls.

In the most simplistic implementations, the system consists of clock and reset generation, an 80960Kx microprocessor, peripheral communications with interface devices, the 82961KA, ROM devices, DRAM devices with series damping resistors, minimal printer interface logic, along with the usual oscillators, connectors and PC board.

Figure 1. 82961KA Block Diagram

## 3.0 PACKAGE INFORMATION

# 3.1 Package Introduction

This section describes the 82961KA pins, pinouts, and thermal characteristics in the 132-pin Plastic Quad Flat Pack (PQFP). For complete package specifications and information, refer to the Intel Packaging Specification (Order No. 231369).

# 3.2 Pin Descriptions

82961KA pins are described in this section. Table 1 presents the legend for interpreting pin descriptions contained in the following tables. Table 2 defines pins associated with the L-Bus. Tables 3, 4 and 5 define pins associated with memory and I/O interface signals. Table 6 defines pins associated with the printer video interface. Table 7 defines printer communications interface signals. Table 8 defines pins associated with basic processor configuration and control.

**Table 1. Pin Description Nomenclature**

| Symbol <sup>(1)</sup> | Description                                                 |

|-----------------------|-------------------------------------------------------------|

| ı                     | Pin is input only                                           |

| 0                     | Pin is output only                                          |

| 1/0                   | Pin can be either an input or output                        |

| L                     | Signal is active LOW                                        |

| L(P)                  | Signal is active LOW and the signal's sense is programmable |

| Н                     | Signal is active HIGH                                       |

| TS                    | Signal is tristate                                          |

| OD                    | Signal is open-drain output                                 |

| ST                    | Signal is Schmitt trigger input                             |

#### NOTE:

1. Bold indicates a pin; non-bold indicates a signal.

3-332

PRODUCT PREVIEW

**Table 2. L-Bus Interface Signals**

| Name    | Туре           | Description                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|---------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

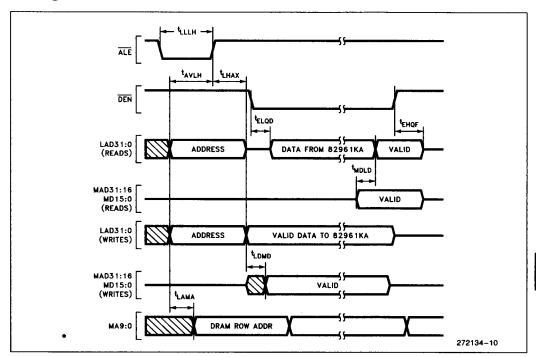

| LAD31:0 | I/O<br>H<br>TS | LOCAL ADDRESS/DATA BUS carries 32-bit physical address and data to and from memory, I/O devices or internal registers. During an address cycle, bits 31:2 contain a physical word address and bits 1:0 contain a burst size. During a data cycle, bits 31:0 contain read or write data. Burst size is an encoded number where 00 represents one word and 11 represents four words.                                 |  |

| ALE     | l<br>L         | ADDRESS LATCH ENABLE indicates the transfer of a physical address. ALE is asserted during an address cycle and deasserted before a data cycle begins.                                                                                                                                                                                                                                                              |  |

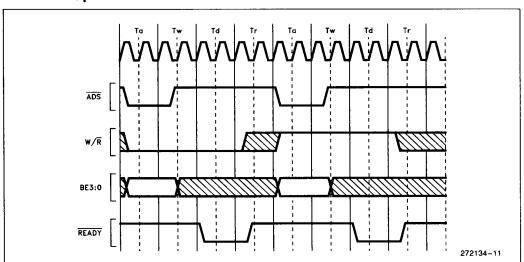

| ADS     | L              | ADDRESS/DATA STATUS indicates an address state. It is asserted during an address cycle and deasserted during a following data cycle. For a burst transaction, ADS is asserted again every data cycle where READY was asserted in the previous cycle.                                                                                                                                                               |  |

| W/R     | 1              | WRITE/READ specifies, during an address cycle, whether the operation is a write or a read. Valid during entire memory, register or I/O operation.                                                                                                                                                                                                                                                                  |  |

| DEN     | i<br>L         | DATA ENABLE indicates a transfer on the LAD lines. Asserted during all data cycles.                                                                                                                                                                                                                                                                                                                                |  |

| READY   | <b>O</b><br>OD | <b>READY</b> indicates data on the LAD signals can be sampled or removed. If <b>READY</b> is not asserted during a data transfer, the data cycle is extended to next cycle by inserting a wait state and ADS is not asserted in the next cycle.                                                                                                                                                                    |  |

| BE3:0   | l<br>L         | BYTE ENABLE: BE signals specify data bytes on the bus which take part in the current data cycle. BEO corresponds to LAD7:0. BE3 corresponds to LAD31:24. BE signals are pipelined. BE signals corresponding to the first data transfer of a burst are asserted during address cycle. BE signals corresponding to subsequent data transfers of a burst are asserted in the data cycle of the current data transfer. |  |

| IRQ     | O<br>L<br>OD   | INTERRUPT REQUEST indicates an interrupt to the 80960Kx processor. When the 82961KA interrupt is cleared, the signal goes inactive for two bus cycles before it can be reasserted.                                                                                                                                                                                                                                 |  |

**Table 3. Memory Interface Signals**

| Name     | Туре          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|----------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|          | I/O           | MEMORY DATA signals contain the two least significant data bytes for I/O and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| MD15:0   | H<br>TS       | DRAM memory operations. MD7:0 contain the least significant byte; MD15:8 contain the second most significant byte. If DRAM is configured as 16 bits wide, or the I/O channel being accessed is packed, MD7:0 also contain the third most significant byte and MD15:8 also contain the most significant byte. During a DRAM write operation, only those bytes with a corresponding write enable signal asserted are driven by the 82961KA.                                                                                                                                                                                                                                                                                                                                                                                           |  |

| MAD31:29 | 1/0           | MEMORY ADDRESS/DATA signals are multi-purpose depending on the device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|          | H<br>TS       | that is selected:  ROM MAD31 is not used. MAD30:39 signals output an encoded address range select and are driven high or low.  I/O Signals output an encoded address range selected.  DRAM Signals contain data bits 29–31 when DRAM is in 32-bit configuration. When DRAM is in 16-bit configuration, these signals are unused and are floated.  During a DRAM write operation, only those bytes with a corresponding write enable signal asserted are driven by the 82961KA.                                                                                                                                                                                                                                                                                                                                                      |  |

| MAD28:16 | 1/0           | MEMORY ADDRESS/DATA signals are multi-purpose depending on the device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|          | H<br>TS       | selected:  ROM MAD16 is not used. MAD25:17 output address bits 02–08, 17, 19.  MAD28:26 are not used and are driven high or low.  I/O Signals output address bits 01–08, 17, 19, 21–23.  DRAM Signals contain data bits 16–28 with DRAM in 32-bit configuration. When DRAM is in 16-bit configuration, signals are unused and are floated.  During a DRAM write operation, only those bytes with a corresponding write enable signal asserted are driven by the 82961KA.                                                                                                                                                                                                                                                                                                                                                            |  |

| MA9:0    | ОН            | MEMORY ADDRESS signals are multi-purpose depending on the device selected:  ROM Signals output address bits 09–16, 18, 20.  I/O Signals output address bits 09–16, 18, 20.  Signals output multiplexed address bits 00-09. The number of address bits actually multiplexed on these signals depends on the DRAM bank accessed and the programmed size for that bank. Use MA7:0 for 64 Kbit x 16/32 DRAM; use MA8:0 for 256 Kbit x 16/32 DRAM; use MA9:0 for 1 Mbit x 16/32 DRAM.                                                                                                                                                                                                                                                                                                                                                    |  |

| RAS3:0   | O<br>L        | ROW ADDRESS STROBE signals, used for DRAM accesses, are asserted when MA9:0 signals contain a valid row address. RAS0 corresponds to the first DRAM bank; RAS3 corresponds to the fourth DRAM bank. In page mode the RAS signal of the accessed bank remains asserted after completion of the memory operation, and is deasserted for a bank when a page miss occurs.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| CAS3:0   | <b>O</b><br>L | COLUMN ADDRESS STROBE signals, used for DRAM accesses, are asserted when MA9:0 signals contain a valid column address. CASO corresponds to the first DRAM bank; CASO corresponds to the fourt DRAM bank. Only one of the four CAS signals is asserted during a memory operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| WE3:0    | O<br>L        | WRITE ENABLE signals, used for DRAM accesses, are asserted during write operations.  For 32-bit wide DRAM, WE0 corresponds to the least significant byte MD7:0 and WE3 corresponds to the most significant byte MD31:24. WE0 also corresponds to the 80960Kx BE0 signals and WE3 corresponds to the BE3 signal. Only those WE signals with a corresponding asserted BE signal are asserted.  For 16-bit wide DRAM, WE0 corresponds to both the least significant byte, and the third most significant byte, which uses MD7:0. WE1 corresponds to both the second most significant byte and the most significant byte, which uses MD15:8.  WE0 also corresponds to BE0 and BE2; WE1 corresponds to BE1 and BE3. For 16-bit wide DRAM, DRAM accesses are performed in two 16-bit accesses; WE2 and WE3 are unused and are deasserted. |  |

## **Table 4. ROM Signals**

| Name     | Туре    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

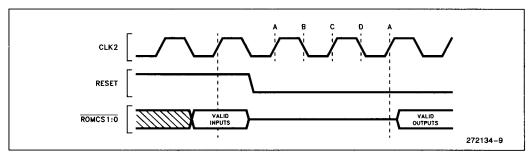

| ROMCS1:0 | L<br>TS | <b>ROM CHIP SELECT</b> signals indicate an access to one of the eight ROM banks. ROMCS0 is used for ROM banks 0–3; ROMCS1 for ROM banks 4–7. While ROMCS0 or ROMCS1 is asserted, the encoded address range select signals MAD30:29 determine the particular ROM bank to be accessed. MAD30:29 signals are guaranteed to be valid during the entire time that ROMCS1:0 is asserted. ROMCS0 and ROMCS1 are never asserted at the same time. These signals are valid during the entire memory operation. During reset, ROMCS0 is used as an input to indicate DRAM bus width. If this pin is low during reset, DRAM is configured as a 16-bit bus. If this pin is high, DRAM is configured as a 32-bit bus. This pin is either pulled up (for a 32-bit bus) or pulled down (for a 16-bit bus) through a 10 KΩ resistor. During reset, ROMCS1 is used as an input to clear ROM bank 0 size field to zero, disabling it. This allows external ROM and control circuit at address zero. If pin is low during reset, ROM bank 0 is disabled. If pin is high, ROM bank 0 is enabled as normal. This pin is either pulled up (enabled) or pulled down (disabled) through a 10 KΩ resistor. |

| ROMOE    | O<br>L  | <b>ROM OUTPUT ENABLE</b> corresponds to the DEN signal and is asserted during all data cycles to any of the eight ROM banks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## Table 5. I/O Interface Signals

| Name | Туре          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

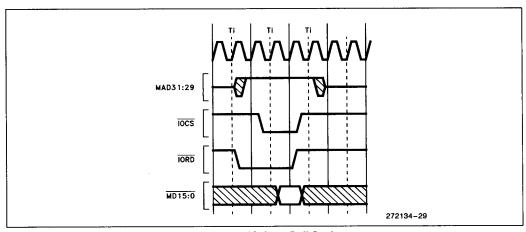

| ĪOCS | <b>O</b><br>L | I/O CHIP SELECT indicates an access to one of the eight I/O device address ranges in an auto-poll cycle. It is asserted at the beginning of an I/O operation and remains asserted for a programmed duration of I/O device select. While IOCS is asserted, encoded address range select signals MAD31:29 determine the particular I/O channel to be accessed. MAD31:29 signals are guaranteed to be valid during the entire time that IOCS is asserted. |  |

| IOWR | O<br>L        | I/O WRITE indicates a write operation to one of the eight I/O device address ranges. It is asserted a programmed duration after IOCS is asserted and remains asserted for a programmed duration. It is asserted for I/O write operations only.                                                                                                                                                                                                         |  |

| IORD | O<br>L        | I/O READ indicates a read operation to one of the eight I/O device address ranges in an auto-poll cycle. It is asserted a programmed duration after IOCS is asserted and remains asserted for a programmed duration. It is asserted for I/O read operations only.                                                                                                                                                                                      |  |

#### **Table 6. Printer Video Interface Signals**

| Name  | Туре            | Description                                                                                                                                                                                                                                                      |  |

|-------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PRINT | O<br>L(P)       |                                                                                                                                                                                                                                                                  |  |

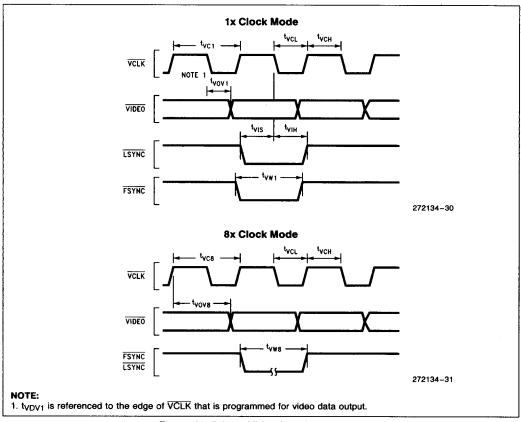

| FSYNC | L(P)<br>ST      | FRAME SYNC indicates printer engine began to print and medium is positioned at top of page. When signal is asserted, the 82961KA controller begins sampling LSYNC signal.                                                                                        |  |

| LSYNC | I<br>L(P)<br>ST | LINE SYNC indicates printer engine began to move the medium and imaging circuitry is positioned at left page position. Each time this signal is asserted, the 82961KA controller counts down the top margin size or initiates a scanline transfer of video data. |  |

Table 6. Printer Video Interface Signals (Continued)

| Name  | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VIDEO | O<br>L(P) | VIDEO is the digital serial video data stream. It is driven after each assertion of LSYNC signal after any top margin size is counted. By default, a high on this signal indicates "white space" and low indicates "black space".                                                                                                                                                                                                                                                                                                                           |

| VCLK  | I<br>L(P) | VIDEO CLOCK is the video shift rate clock. If the printer engine supplies a video shift rate clock, it is presented on this pin. If the printer engine does not supply a video shift rate clock, an 8x video shift rate clock must be presented on this pin and the 82961KA must be programmed for phase locked loop operation. In phase locked loop operation, the internal video shift rate clock is locked to LSYNC signal active edge. By default, when programmed for 1x operation the video shift rate clock falling edge shifts a bit of video data. |

# **Table 7. Printer Communications Interface Signals**

| Name    | Туре                | Description                                                                                                                                                                                                                                                                                                                                                                                  |  |

|---------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

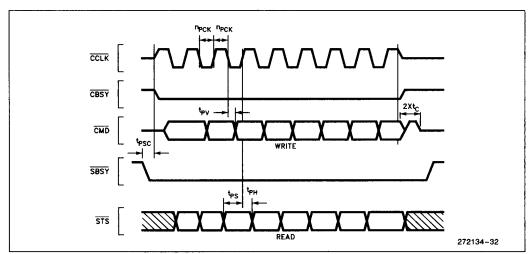

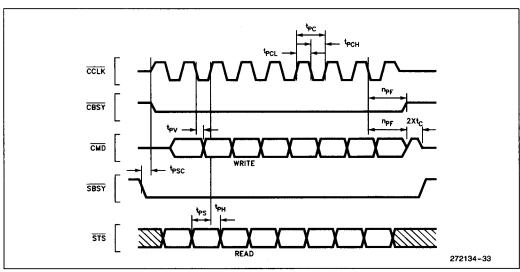

| CBSY    | <b>O</b><br>L<br>OD | COMMAND BUSY indicates 82961KA has command to transmit to the printer engine. CBSY is asserted when 82961KA's printer command register is written; it remains asserted until all command data is sent.                                                                                                                                                                                       |  |

| SBSY    | l<br>L<br>ST        | STATUS BUSY indicates the printer engine has status to transmit to the 82961KA. When signal is asserted, 82961KA assembles a printer engine status byte in the 82961KA's printer status register using eight transitions of CCLK. Note that CCLK may come from the 82961KA or the printer engine, depending on programmed CCLK mode.                                                         |  |

| CMD/STS | I/O<br>L<br>TS      | COMMAND/STATUS DATA is programmable to be either command data output to printer engine or bidirectional command/status data to/from the printer. Command data is an 8-bit serial command stream to a printer engine. After CBSY is asserted by writing the 82961KA's printer command register, each command bit is presented on this signal, accompanied by a transition of the CCLK signal. |  |

| STS     | l<br>L<br>ST        | STATUS DATA is an 8-bit serial status from the printer engine. After SBSY is asserted, the printer engine presents each status bit on this signal with each CCLK transition from the 82961KA controller. SBSY must be deasserted and reasserted to begin a second 8-bit status message.                                                                                                      |  |

| CCLK    | I/O<br>L<br>TS      | COMMAND CLOCK is programmable to be either an input clock from the printer engine or an output clock to the printer engine. It causes the printer engine to assemble an 8-bit command or transmit an 8-bit status one bit at a time with each transition of this signal. Each command bit is shifted on a falling edge of CCLK and each status bit is sampled on a rising edge of CCLK.      |  |

#### **Table 8. Processor Control Signals**

| Name            | ne Type Description |                                                                                                                                           |  |

|-----------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

|                 |                     | <b>SYSTEM CLOCK</b> provides the fundamental timing for the 82961KA. It is twice the frequency of an 80960Kx address or data cycle.       |  |

| RESET           | ST                  | RESET clears 82961KA internal logic and initializes all internal registers.                                                               |  |

| V <sub>CC</sub> | ı                   | SYSTEM POWER connections consist of eight pins; it is strongly recommended that these are connected externally to a $V_{CC}$ board plane. |  |

| V <sub>SS</sub> | ı                   | SYSTEM GROUND consists of 10 pins; it is strongly recommended that these are connected externally to a V <sub>SS</sub> board plane.       |  |

#### 3.3 82961KA PQFP Pinout

Tables 9 and 10 list 82961KA pin names and package location. See Section 4, Electrical Specifications for specifications and recommended connections.

Table 9. PQFP Pin Name with Package Location (Signal Order)

| L-Bus |          |  |  |  |

|-------|----------|--|--|--|

| Name  | Location |  |  |  |

| LAD31 | 128      |  |  |  |

| LAD30 | 129      |  |  |  |

| LAD29 | 130      |  |  |  |

| LAD28 | 131      |  |  |  |

| LAD27 | 132      |  |  |  |

| LAD26 | 1        |  |  |  |

| LAD25 | 2        |  |  |  |

| LAD24 | 4        |  |  |  |

| LAD23 | 5        |  |  |  |

| LAD22 | 6        |  |  |  |

| LAD21 | 7        |  |  |  |

| LAD20 | 8        |  |  |  |

| LAD19 | 9        |  |  |  |

| LAD18 | 11       |  |  |  |

| LAD17 | 12       |  |  |  |

| LAD16 | 13       |  |  |  |

| LAD15 | 15       |  |  |  |

| LAD14 | 16       |  |  |  |

| LAD13 | 17       |  |  |  |

| LAD12 | 18       |  |  |  |

| LAD11 | 19       |  |  |  |

| LAD10 | 20       |  |  |  |

| LAD9  | 21       |  |  |  |

| LAD8  | 23       |  |  |  |

| LAD7  | 24       |  |  |  |

| LAD6  | 25       |  |  |  |

| LAD5  | 27       |  |  |  |

| LAD4  | 28       |  |  |  |

| LAD3  | 29       |  |  |  |

| LAD2  | 30       |  |  |  |

| LAD1  | 31       |  |  |  |

| LAD0  | 32       |  |  |  |

| ALE   | 119      |  |  |  |

| ADS   | 118      |  |  |  |

| W/R   | 120      |  |  |  |

| 3. FOR FEIR MAINE WILLI |          |

|-------------------------|----------|

| L-Bus (Continued)       |          |

| Name                    | Location |

| DEN                     | 117      |

| READY                   | 126      |

| BE3                     | 121      |

| BE2                     | 122      |

| BE1                     | 123      |

| BE0                     | 124      |

| ĪRQ                     | 125      |

|                         |          |

| 1/0         |          |

|-------------|----------|

| Name        | Location |

| IOCS        | 96       |

| <b>IOWR</b> | 97       |

| IORD        | 98       |

|             | L        |

| Printer Video |          |

|---------------|----------|

| Name          | Location |

| VIDEO         | 109      |

| PRINT         | 110      |

| VCLK          | 111      |

| LSYNC         | 112      |

| FSYNC         | 113      |

|               |          |

| Printer Comm |          |

|--------------|----------|

| Name         | Location |

| STS          | 102      |

| SBSY         | 104      |

| CCLK         | 105      |

| CMD/STS      | 107      |

| CBSY         | 108      |

| Memory |          |

|--------|----------|

| Name   | Location |

| CAS0   | 46       |

| MD0    | 47       |

| MD1    | 48       |

| MD2    | 50       |

| (Continued) |                                        |

|-------------|----------------------------------------|

| Location    |                                        |

| 51          |                                        |

| 52          |                                        |

| 53          |                                        |

| 54          |                                        |

| 56          |                                        |

| 57          |                                        |

| 59          |                                        |

| 60          |                                        |

| 61          |                                        |

| 62          |                                        |

| 63          |                                        |

| 64          |                                        |

| 65          |                                        |

| 66          |                                        |

|             | 51 52 53 54 56 57 59 60 61 62 63 64 65 |

67

68

69

89

90

91

| MA4   | 70 |

|-------|----|

| MA5   | 71 |

| MA6   | 73 |

| MA7   | 74 |

| MA8   | 75 |

| MA9   | 76 |

| MAD16 | 77 |

| MAD17 | 78 |

| MAD18 | 80 |

| MAD19 | 81 |

| MAD20 | 82 |

| MAD21 | 84 |

| MAD22 | 85 |

| MAD23 | 86 |

| MAD24 | 88 |

MAD25

MAD26

MAD27

MA1

MA2

MA3

| Memory (Continued) |          |

|--------------------|----------|

| Name               | Location |

| MAD28              | 92       |

| MAD29              | 93       |

| MAD30              | 94       |

| MAD31              | 95       |

| DRAM |          |

|------|----------|

| Name | Location |

| WE3  | 33       |

| WE2  | 34       |

| WE1  | 35       |

| WE0  | 36       |

| RAS3 | 37       |

| CAS3 | 38       |

| RAS2 | 40       |

| CAS2 | 41       |

| RAS1 | 43       |

| CAS1 | 44       |

| RAS0 | 45       |

| ROM     |          |

|---------|----------|

| Name    | Location |

| ROMOE   | 99       |

| ROMC\$1 | 100      |

| ROMCS0  | 101      |

| Control |          |

|---------|----------|

| Name    | Location |

| CLK2    | 114      |

| RESET   | 116      |

| V <sub>CC</sub>     |  |

|---------------------|--|

| 14, 26, 49, 58, 72, |  |

| 103, 115, 127       |  |

| V <sub>SS</sub>        |

|------------------------|

| 3, 10, 22, 39, 42, 55, |

| 79, 83, 87, 106        |

Table 10. PQFP Pin Name with Package Location (Pin Order)

|     | 18              |

|-----|-----------------|

| Pin | Signal          |

| 1   | LAD26           |

| 2   | LAD25           |

| 3   | V <sub>SS</sub> |

| 4   | LAD24           |

| 5   | LAD23           |

| 6   | LAD22           |

| 7   | LAD21           |

| 8   | LAD20           |

| 9   | LAD19           |

| 10  | V <sub>SS</sub> |

| 11  | LAD18           |

| 12  | LAD17           |

| 13  | LAD16           |

| 14  | V <sub>CC</sub> |

| 15  | LAD15           |

| 16  | LAD14           |

| 17  | LAD13           |

| 18  | LAD12           |

| 19  | LAD11           |

| 20  | LAD10           |

| 21  | LAD9            |

| 22  | V <sub>SS</sub> |

| 23  | LAD8            |

| 24  | LAD7            |

| 25  | LAD6            |

| 26  | Vcc             |

| 27  | LAD5            |

| 28  | LAD4            |

| 29  | LAD3            |

| 30  | LAD2            |

| 31  | LAD1            |

| 32  | LAD0            |

| 33  | WE3             |

|     |                 |

| Pin | Signal          |

|-----|-----------------|

| 34  | WE2             |

| 35  | WE1             |

| 36  | WEO             |

| 37  | RAS3            |

| 38  | CAS3            |

| 39  | V <sub>SS</sub> |

| 40  | RAS2            |

| 41  | CAS2            |

| 42  | V <sub>SS</sub> |

| 43  | RAS1            |

| 44  | CAS1            |

| 45  | RAS0            |

| 46  | CAS0            |

| 47  | MD0             |

| 48  | MD1             |

| 49  | Vcc             |

| 50  | MD2             |

| 51  | MD3             |

| 52  | MD4             |

| 53  | MD5             |

| 54  | MD6             |

| 55  | Vss             |

| 56  | MD7             |

| 57  | MD8             |

| 58  | Vcc             |

| 59  | MD9             |

| 60  | MD10            |

| 61  | MD11            |

| 62  | MD12            |

| 63  | MD13            |

| 64  | MD14            |

| 65  | MD15            |

| 66  | MAO             |

| Package Location (Pi |                 |  |  |  |

|----------------------|-----------------|--|--|--|

| Pin                  | Signal          |  |  |  |

| 67                   | MA1             |  |  |  |

| 68                   | MA2             |  |  |  |

| 69                   | МАЗ             |  |  |  |

| 70                   | MA4             |  |  |  |

| 71                   | MA5             |  |  |  |

| 72                   | V <sub>CC</sub> |  |  |  |

| 73                   | MA6             |  |  |  |

| 74                   | MA7             |  |  |  |

| · 75                 | MA8             |  |  |  |

| 76                   | MA9             |  |  |  |

| 77                   | MAD16           |  |  |  |

| 78                   | MAD17           |  |  |  |

| 79                   | V <sub>SS</sub> |  |  |  |

| 80                   | MAD18           |  |  |  |

| 81                   | MAD19           |  |  |  |

| 82                   | MAD20           |  |  |  |

| 83                   | V <sub>SS</sub> |  |  |  |

| 84                   | MAD21           |  |  |  |

| 85                   | MAD22           |  |  |  |

| 86                   | MAD23           |  |  |  |

| 87                   | V <sub>SS</sub> |  |  |  |

| 88                   | MAD24           |  |  |  |

| 89                   | MAD25           |  |  |  |

| 90                   | MAD26           |  |  |  |

| 91                   | MAD27           |  |  |  |

| 92                   | MAD28           |  |  |  |

| 93                   | MAD29           |  |  |  |

| 94                   | MAD30           |  |  |  |

| 95                   | MAD31           |  |  |  |

| 96                   | IOCS            |  |  |  |

| 97                   | IOWR            |  |  |  |

| 98                   | IORD            |  |  |  |

| 99                   | ROMOE           |  |  |  |

| er) |                 |  |  |  |  |

|-----|-----------------|--|--|--|--|

| Pin | Signal          |  |  |  |  |

| 100 | ROMCS1          |  |  |  |  |

| 101 | ROMCS0          |  |  |  |  |

| 102 | STS             |  |  |  |  |

| 103 | V <sub>CC</sub> |  |  |  |  |

| 104 | SBSY            |  |  |  |  |

| 105 | CCLK            |  |  |  |  |

| 106 | V <sub>SS</sub> |  |  |  |  |

| 107 | CMD/STS         |  |  |  |  |

| 108 | CBSY            |  |  |  |  |

| 109 | VIDEO           |  |  |  |  |

| 110 | PRINT           |  |  |  |  |

| 111 | VCLK            |  |  |  |  |

| 112 | LŠYNC           |  |  |  |  |

| 113 | FSYNC           |  |  |  |  |

| 114 | CLK2            |  |  |  |  |

| 115 | V <sub>CC</sub> |  |  |  |  |

| 116 | RESET           |  |  |  |  |

| 117 | DEN             |  |  |  |  |

| 118 | ADS             |  |  |  |  |

| 119 | ALE             |  |  |  |  |

| 120 | W/R             |  |  |  |  |

| 121 | BE3             |  |  |  |  |

| 122 | BE2             |  |  |  |  |

| 123 | BE1             |  |  |  |  |

| 124 | BE0             |  |  |  |  |

| 125 | ĪRŌ             |  |  |  |  |

| 126 | READY           |  |  |  |  |

| 127 | V <sub>CC</sub> |  |  |  |  |

| 128 | LAD31           |  |  |  |  |

| 129 | LAD30           |  |  |  |  |

| 130 | LAD29           |  |  |  |  |

| 131 | LAD28           |  |  |  |  |

| 132 | LAD27           |  |  |  |  |

#### 3.4 Mechanical Data

## **Package Dimensions and Mounting**

The 82961KA is available in a 132-lead plastic quad flat pack (PQFP). The plastic package uses finepitch gull wing leads arranged in a single row along the perimeter of the package with 0.025 inch (0.64 mm) spacing.

The PQFP is normally surface mounted to take best advantage of the plastic package's small footprint and low cost. In some applications, however, designers may prefer to use a socket, either to improve heat dissipation or reduce repair costs.

## Pin Assignment

Figures 2 and 3 show the top view of the PQFP; notice that the pins are numbered in order from 1 to 132 around the package's perimeter. Tables 9 and 10 list the function of each pin in the PQFP.

It is strongly recommended that V<sub>CC</sub> and GND connections be made to multiple V<sub>CC</sub> and GND pins. Each V<sub>CC</sub> and GND pin should be connected to the appropriate voltage or ground and externally strapped close to the package. We recommend that you include separate power and ground planes in your circuit board for power distribution.

# 3.5 Package Thermal Specification

The 82961KA is specified for operation when case temperature is within the range 0°C to +85°C (PQFP). The case temperature should be measured at the top center of the package as shown in Table

The ambient temperature can be calculated from  $\theta_{ic}$ and  $\theta_{ia}$  by using the following equations:

$$\begin{split} T_J &= T_C + P^*\theta_{jc} \\ T_A &= T_J - P^*\theta_{ja} \\ T_C &= T_A + P^*[\theta_{ja} - \theta_{jc}] \end{split}$$

Table 11. 82961KA PQFP Package Thermal Characteristics

| Parameter   O   50   100   200   400   600   800   (0)   (0.25)   (0.50)   (1.01)   (2.03)   (3.04)   (4.06)                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   0   0.25   0.50   (1.01)   (2.03)   (3.04)   (4.06)                                                                                                                                                    |

| Case-to-Ambient No Heatsink)  22 19 18 16 11 9 8  DTES: This table applies to 82961KA 3. $\theta_{JL} = 18^{\circ}\text{C/Watt}$ DEP soldered directly into board. $\theta_{JB} = 18^{\circ}\text{C/Watt}$ |

| No Heatsink) 22 19 18 16 11 9 8  OTES:  This table applies to 82961KA 3. $\theta_{JL} = 18^{\circ}\text{C/Watt}$ OFP soldered directly into board. $\theta_{JB} = 18^{\circ}\text{C/Watt}$                 |

| This table applies to 82961KA 3. $\theta_{JL} = 18^{\circ}\text{C/Watt}$ QFP soldered directly into board. $\theta_{JB} = 18^{\circ}\text{C/Watt}$                                                         |

|                                                                                                                                                                                                            |

| √— Θ <sub>JC</sub>                                                                                                                                                                                         |

|                                                                                                                                                                                                            |

Values for  $\theta_{ja}$  and  $\theta_{jc}$  are given in Table 11 for the PQFP for various airflows. Note that the  $\theta_{ja}$  for the PGA package can be reduced by adding a heatsink, while a heatsink is not generally used with the plastic package since it is intended to be surface mounted. The maximum allowable ambient temperature

$(T_A)$  permitted without exceeding  $T_C$  is shown by the charts in Figure 6.

The curves assume the maximum permitted supply current (I<sub>CC</sub>) at each speed, V<sub>CC</sub> of 5.0V, and a T<sub>CASE</sub> of  $+85^{\circ}$ C (PQFP).

#### 3.6 Package Dimensions and Mounting

Figure 2. 82961KA 132-Lead Plastic Quad Flat Pack (PQFP) Package

Figure 3. 82961KA PQFP Package (Top View)

#### 4.0 ELECTRICAL SPECIFICATIONS

# 4.1 Power and Grounding

Power and ground capacitors must be made to all 82961KA power and ground pins. On the circuit board, all V<sub>CC</sub> pins must be strapped closely together. Similarly, all V<sub>SS</sub> pins should be strapped closely together. It is strongly recommended that V<sub>CC</sub> pins are connected to a common power plane and V<sub>SS</sub> pins are connected to a common ground plane in the PC board.

# 4.2 Power Decoupling Recommendations

Decoupling capacitors should be placed near the 82961KA. The 82961KA can cause transient power surges when multiple, loaded outputs switch simultaneously. Proper power decoupling is required to avoid "ground lift" or "ground bounce" induced by these power surges.

#### 4.3 Connection Recommendations

Low inductance capacitors and interconnects are recommended for best high frequency electrical performance. Inductance can be reduced by shortening the PC board traces between the processor and decoupling capacitors as much as possible.

For reliable operation, always connect unused inputs to an appropriate signal level. **No unused input pin should be left floating**. Connect unused pins directly to V<sub>SS</sub> or to V<sub>CC</sub> through a pull-up resistor.

Recommended value of the pull-up resistor is approximately 20  $K\Omega$  for each pin tied high.

Output drivers for RAS3:0, CAS3:0, WE3:0 and MA9:0 are designed to directly drive the heavy capacitive loads of DRAM arrays. To prevent outputs from ringing in the system, it is necessary to match the output driver's output impedance to that of the DRAM array. This is accomplished by placing a resistor in series with each signal. Place the series resistor near the 82961KA. Resistor value is dependent on DRAM loading and is best determined by experimentation at the prototype level.

All open-drain outputs require a pull-up termination connected to the output pin. Signals READY, IRQ and CBSY are open-drain outputs on the 82961KA.

While in most cases a simple pull-up resistor is adequate, a network consisting of pull-up and pull-down resistors may be necessary for the READY pin, since timing on this signal is critical.

Figure 4 shows recommendations for low and high current drive network which assumes the circuit board has a characteristic impedance of  $100\Omega$ . The resistor network should bias the output to a valid HIGH level ( $V_{|H|} \geq 2.0V$ ). To minimize signal reflection, termination should be placed close to the end of the PC board trace. Pull-up and pull-down resistor value should be chosen such that network impedance closely matches the characteristic impedance of the PC board trace.

Figure 4 also shows a simple pull-up termination which can be used to terminate the open-drain outputs.

Figure 4. Network and Simple Termination Examples

#### 5.0 ABSOLUTE MAXIMUM RATINGS

NOTICE: This document contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product is available.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

**Table 12. Absolute Ratings**

| KU82961KA-20, -16 (20, 16 MHz Specification)          |                    |                       |           |  |  |  |  |

|-------------------------------------------------------|--------------------|-----------------------|-----------|--|--|--|--|

| Daniel Maria                                          |                    | Absolut               | e Ratings |  |  |  |  |

| Parameter/Description                                 | Min Max Units Cond |                       |           |  |  |  |  |

| Storage Temperature                                   | -65                | 150                   | °C        |  |  |  |  |

| Case Temperature Under Bias                           | -65                | 110                   | °C        |  |  |  |  |

| Supply Voltage with Respect to V <sub>SS</sub>        | -0.5               | 6.5                   | ٧         |  |  |  |  |

| Voltage on Other Pins with Respect to V <sub>SS</sub> | -0.5               | V <sub>CC</sub> + 0.5 | ٧         |  |  |  |  |

**Table 13. Targeted Operating Conditions**

| KU82961KA-20, -16 (20, 16 MHz Specification) |                                                              |             |             |       |                      |  |

|----------------------------------------------|--------------------------------------------------------------|-------------|-------------|-------|----------------------|--|

| Symbol                                       | Parameter/Description                                        | Min         | Max         | Units | Conditions           |  |

| V <sub>CC</sub> ,                            | Supply Voltage<br>KU82961KA-20<br>KU82961KA-16               | 4.75<br>4.5 | 5.25<br>5.5 | ٧     | (Note 1)<br>(Note 2) |  |

| fc                                           | Input Clock (CLK2) Frequency<br>KU82961KA-20<br>KU82961KA-16 | 1           | 40<br>32    | MHz   | (Note 1)<br>(Note 2) |  |

| T <sub>C</sub>                               | Case Temperature Under Bias<br>KU82961KA-20<br>KU82961KA-16  | 0           | 85<br>85    | °C    | (Note 1)<br>(Note 2) |  |

#### NOTES:

- 1. 82961KA-20 is tested with voltage supplies set to  $\pm 5\%$ .

- 2. 82961KA-16 is tested with voltage supplies set to  $\pm 10\%$ .

#### 6.0 TARGETED DC CHARACTERISTICS

**Table 14. Targeted DC Characteristics**

|                 | 82961KA-20, -16 (20, 16 MHz Specification)       |      |                       |          |                                       |  |  |  |

|-----------------|--------------------------------------------------|------|-----------------------|----------|---------------------------------------|--|--|--|

| Symbol          | Parameter/Description                            | Min  | Max                   | Units    | Conditions                            |  |  |  |

| V <sub>IL</sub> | Input Low Voltage                                | -0.3 | 0.8                   | V        | (Note 1)                              |  |  |  |

| V <sub>IH</sub> | Input High Voltage                               | 2.0  | V <sub>CC</sub> + 0.3 | V        | (Note 1)                              |  |  |  |

| V <sub>OL</sub> | Output Low Voltage                               | *    | 0.45                  | V        | (Note 2)                              |  |  |  |

| V <sub>OH</sub> | Output High Voltage                              | 2.4  |                       | ٧        | (Note 3)                              |  |  |  |

| Icc             | Power Supply Current<br>82961KA-20<br>82961KA-16 |      | 250<br>200            | mA<br>mA | (Note 4)                              |  |  |  |

| ILI             | Input Leakage Current                            |      | ±10                   | μΑ       | $0 \le V_{IN} \le V_{CC}$             |  |  |  |

| llo             | Output Leakage Current                           |      | ± 10                  | μΑ       | $0.45 \le V_O \le V_{CC}$             |  |  |  |

| CIN             | Input Capacitance                                |      | 8                     | pF       | f <sub>C</sub> = 1 MHz <sup>(5)</sup> |  |  |  |

| C <sub>IO</sub> | I/O or Output Capacitance                        |      | 10                    | pF       | f <sub>C</sub> = 1 MHz <sup>(5)</sup> |  |  |  |

#### NOTES:

2. VOL is measured under the following conditions:

I<sub>OL</sub> = 6 mA LAD31:0, MAD31:16, MD15:0, IOCS, IORD, IOWR, ROMOE, ROMCS1:0,

RAS3:0, CAS3:0, WE3:0, MA9:0

I<sub>OL</sub> = 12 mA CCLK, CMD/STS, CBSY, VIDEO, PRINT

I<sub>OL</sub> = 24 mA READY, IRQ

3. V<sub>OH</sub> is measured under the following conditions:

I<sub>OH</sub> = 6 mA LAD31:0, MAD31:16, MD15:0, IOCS, IORD, IOWR, ROMOE, ROMCS1:0,

I<sub>OH</sub> = 12 mA RAS3:0, CAS3:0, WE3:0, MA9:0

VOH is not measured for open-drain outputs, IRQ, READY, and CBSY

5. Capacitance values are not tested.

<sup>1.</sup> RESET, FSYNC, LSYNC, SBSY, and STS are Schmitt trigger inputs. Hysteresis on these pins is approximately 200 mV, but is not tested for each device.

<sup>4.</sup> Measured at worst case frequency, V<sub>CC</sub>, and temperature, with device operating and outputs loaded to the test conditions shown in Figure 5.

Figure 5. Typical Supply Current (I<sub>CC</sub>) vs Frequency (f<sub>C</sub>)

Figure 6. Typical Supply Current (I<sub>CC</sub>) vs Supply Voltage (V<sub>CC</sub>)

# 7.0 TARGETED AC CHARACTERISTICS

AC Specifications presented in this document are tested with loading on output pins as shown in Figure 7. Output test load ( $C_L$ ) is never less than 50 pF unless specifically stated in the AC Specifications.

Figure 8 shows output valid delay as a function of load capacitance. Output valid delays given in the AC Specifications must be adjusted using data in Figure 8 when pin loading in the system exceeds test load, C<sub>L</sub>. Derating information is verified at all operating conditions using a sampling of components which represent process extremes. Derating information is not tested for each device.

AC Specifications relating to outputs are measured at the 1.5V crossing point of the output signal unless otherwise indicated. Input signals are driven during test with a rise and fall time of  $\leq 2$  ns. AC Specifications relating to inputs are measured from the 1.5V crossing point of the input waveform.

Figure 7. AC Test Loads

Figure 8. Output Valid Delay (tov) vs Load Capacitance

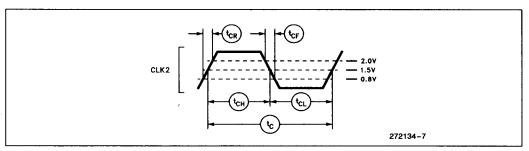

**Table 15. Input Clock Specifications**

| Symbol          | Parameter/Description    | Min   | Max  | Units | Conditions |

|-----------------|--------------------------|-------|------|-------|------------|

| 82961KA-2       | 0 (20 MHz Specification) |       |      |       |            |

| fc              | CLK2 Frequency           | 1     | 40   | MHz   | (Note 1)   |

| t <sub>C</sub>  | CLK2 Period              | 25    | 1000 | ns    | (Note 1)   |

| t <sub>CH</sub> | CLK2 High Time           | 10    |      | ns    | (Note 1)   |

| t <sub>CL</sub> | CLK2 Low Time            | 10    |      | ns    | (Note 1)   |

| t <sub>CR</sub> | CLK2 Rise Time           |       | 6    | ns    | (Note 1)   |

| t <sub>CF</sub> | CLK2 Fall Time           |       | 6    | ns    | (Note 1)   |

| 82961KA-1       | 6 (16 MHz Specification) |       |      |       |            |

| fc              | CLK2 Frequency           | 1     | 32   | MHz   | (Note 1)   |

| tc              | CLK2 Period              | 31.25 | 1000 | ns    | (Note 1)   |

| t <sub>CH</sub> | CLK2 High Time           | 12.5  |      | ns    | (Note 1)   |

| t <sub>CL</sub> | CLK2 Low Time            | 12.5  |      | ns    | (Note 1)   |

| t <sub>CR</sub> | CLK2 Rise Time           |       | 6    | ns    | (Note 1)   |

| t <sub>CF</sub> | CLK2 Fall Time           |       | 6    | ns    | (Note 1)   |

#### NOTE:

<sup>1.</sup> See Figure 7 for waveforms and specifications.

Figure 9. Clock Input Waveforms

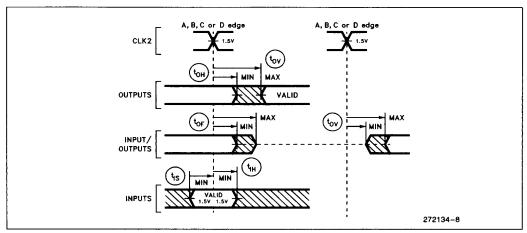

Table 16. Synchronous Input and Output Specifications

| Symbol          | Parameter/Description                                             | Min | Max | Unit | Conditions     |

|-----------------|-------------------------------------------------------------------|-----|-----|------|----------------|

| 82961KA-        | 20 (20 MHz Specification)                                         |     |     |      |                |

| tov             | Output Valid Delay (Maximum Value)                                |     |     |      |                |

| ŧон             | Output Hold Delay (Minimum Value)                                 |     |     |      |                |

|                 | t <sub>OV1</sub> , t <sub>OH1</sub> LAD31:0                       | 5   | 37  | ns   | Notes 1, 3, 7  |

|                 | t <sub>OV2</sub> , t <sub>OH2</sub> LAD31:0 (register read only)  | 5   | 59  | ns   | Notes 1, 2, 7  |

|                 | t <sub>OV3</sub> , t <sub>OH3</sub> IRQ                           | 5   | 37  | ns   | Notes 1, 2     |

|                 | t <sub>OV4</sub> , t <sub>OH4</sub> READY                         | 5   | 37  | ns   | Notes 1, 2     |

|                 | t <sub>OV5</sub> , t <sub>OH5</sub> MD15:0                        | 5   | 33  | ns   | Notes 1, 3, 10 |

|                 | t <sub>OV6</sub> , t <sub>OH6</sub> MAD31:16 (I/O cycles only)    | 5   | 34  | ns   | Notes 1, 3, 9  |

|                 | t <sub>OV7</sub> , t <sub>OH7</sub> MAD31:16 (ROM cycles only)    | 5   | 31  | ns   | Notes 1, 2, 9  |

|                 | t <sub>OV8</sub> , t <sub>OH8</sub> MAD31:29 (auto-poll only)     | 5   | 37  | ns   | Notes 1, 6, 9  |

|                 | t <sub>OV9</sub> , t <sub>OH9</sub> MA9:0                         | 5   | 32  | ns   | Notes 1, 4, 8  |

|                 | t <sub>OV10</sub> , t <sub>OH10</sub> RAS3:0, CAS3:0              | 5   | 26  | ns   | Notes 1, 4     |

|                 | t <sub>OV11</sub> , t <sub>OH11</sub> WE3:0                       | 5   | 34  | ns   | Notes 1, 5     |

|                 | t <sub>OV12</sub> , t <sub>OH12</sub> ROMCS1:0, ROMOE             | 5   | 24  | ns   | Notes 1, 2     |

|                 | t <sub>OV13</sub> , t <sub>OH13</sub> IOCS, IORD, IOWR            | 5   | 27  | ns   | Notes 1, 3     |

|                 | t <sub>OV14</sub> , t <sub>OH14</sub> IOCS, IORD (auto-poll only) | 5   | 31  | ns   | Notes 1, 3     |

|                 | t <sub>OV15</sub> , t <sub>OH15</sub> PRINT                       |     | 28  | ns   | Notes 1, 2     |

| tOF             | Output Float Delay                                                |     |     |      |                |

|                 | t <sub>OF1</sub> MD15:0                                           |     | 33  | ns   | Notes 1, 11    |

|                 | t <sub>OF2</sub> MAD31:16                                         |     | 37  | ns   | Notes 1, 11    |

| tis             | Input Setup Time                                                  |     |     |      |                |

|                 | t <sub>IS1</sub> ADS, W/R, BE3:0, DEN                             | 42  |     | ns   | Notes 1, 2     |

|                 | t <sub>IS2</sub> LAD31:0                                          | 10  |     | ns   | Notes 1, 2, 12 |

|                 | t <sub>IS3</sub> MD15:0                                           | 8   |     | ns   | Notes 1, 3, 13 |

|                 | t <sub>IS4</sub> MAD31:16                                         | 8   |     | ns   | Notes 1, 3, 14 |

|                 | t <sub>IS5</sub> RESET                                            | 0   |     | ns   | Notes 1, 3     |

|                 | t <sub>IS6</sub> ROMCS1:0 (on RESET)                              | 0   |     | ns   | Notes 1, 3     |

| t <sub>IH</sub> | Input Hold Time                                                   |     |     |      |                |

|                 | t <sub>lH1</sub> ADS, W/R, BE3:0, DEN                             | 2   |     | ns   | Notes 1, 2     |

|                 | t <sub>lH2</sub> LAD31:0                                          | 2   |     | ns   | Notes 1, 2, 12 |

|                 | t <sub>IH3</sub> MD15:0                                           | 8   |     | กร   | Notes 1, 3, 13 |

|                 | t <sub>lH4</sub> MAD31:16                                         | 10  |     | ns   | Notes 1, 3, 14 |

|                 | t <sub>IH5</sub> RESET                                            | 5   |     | ns   | Notes 1, 3     |

|                 | t <sub>IH6</sub> ROMCS1:0 (on RESET)                              | 8   |     | ns   | Notes 1, 3     |

| 82961KA-        | 16 (16 MHz Specification)                                         |     |     |      |                |

|                 | TBD                                                               |     | ,   |      |                |

#### NOTES:

- 1. See Figure 8 for waveforms and specifications.

- 2. Signal is synchronous to the CLK2 A edge.

- 3. Signal is synchronous to the CLK2 A or C edge.

- 4. Signal is synchronous to any rising or falling edge of CLK2 (CLK2 A, B, C or D edge).

- 5. Signal is synchronous to the CLK2 B edge.

- 6. Signal is synchronous to the CLK2 C edge.