L64381 4-Port Ethernet Controller Device Technical Manual This document is preliminary. As such, it contains data derived from functional simulations and performance estimates. LSI Logic has not verified either the functional descriptions, or the electrical and mechanical specifications using production parts.

Document DB14-000002-01, Second Edition (August 1996)

This document describes revision B of LSI Logic Corporation's L64381 4-Port Ethernet Controller (Quad CASCADE®) Device and will remain the official reference source for all revisions/releases of this product until rescinded by an update.

To receive product literature, call us at 1.800.574.4286 (U.S. and Canada); +32.11.300.531 (Europe); 408.433.7700 (outside U.S., Canada, and Europe) and ask for Department JDS; or visit us at http://www.lsilogic.com.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 1995, 1996 by LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

LSI Logic logo design and CASCADE are registered trademarks of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

# **Preface**

This book is the primary reference and technical manual for the L64381 4-Port Ethernet Controller (Quad CASCADE) Device. It contains a complete functional description for the L64381 and includes complete physical and electrical specifications for the L64381.

#### **Audience**

This document assumes that you have some familiarity with networking, microprocessors, and related support devices. The people who benefit from this book are:

- ◆ Engineers and managers who are evaluating the L64381 for possible use in a networking system

- ♦ Engineers who are designing the L64381 into a system

#### **Organization**

This document has the following chapters and appendixes:

- ◆ Chapter 1, Introduction, describes the general characteristics and capabilities of the L64381 product.

- Chapter 2, Registers, defines the on-chip registers.

- ◆ Chapter 3, **Signal Descriptions**, describes the input, output, and bidirectional signals of the L64381 chip.

- ◆ Chapter 4, L64381 Operation, provides a detailed description of the functional blocks and interfaces within the L64381 chip.

- Chapter 5, Statistics Counters, lists the purpose and contents of the 32-bit Statistics Counters.

- Chapter 6, Instruction Set, defines the L64381 instruction set and provides each instruction's valid modes.

- ◆ Chapter 7, Specifications, provides the AC and DC specifications and packaging information for the L64381 chip.

Preface iii

◆ Appendix A, Customer Feedback, includes a form that you may use to fax us your comments about this document.

# Related Publications

Compacted and Scalable Dedicated Ethernet (CASCADE) Core Technical Manual, Order No. C14015

# Conventions Used in This Manual

The first time a word or phrase is defined in this manual, it is italicized.

The following signal naming conventions are used throughout this manual:

- ♦ A level-significant signal that is true or valid when the signal is LOW always has an overbar ( ) over its name.

- ◆ An edge-significant signal that initiates actions on a HIGH-to-LOW transition always has an overbar ( ) over its name.

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive.

Hexadecimal numbers are indicated by the prefix "0x" before the number—for example, 0x32CF. Binary numbers are indicated by a subscripted "2" following the number—for example, 0011.0010.1100.1111<sub>2</sub>.

A word is 32-bits long. A halfword is 16-bits long. A byte is 8-bits long.

# **Contents**

| Chapter 1 | Intro               | duction  |                                        |      |

|-----------|---------------------|----------|----------------------------------------|------|

| •         | 1.1                 | Overvi   | ew                                     | 1-1  |

|           | 1.2                 | Key Fe   | eatures                                | 1-3  |

|           |                     | 1.2.1    | Ethernet Core                          | 1-3  |

|           |                     | 1.2.2    | Internal Architecture                  | 1-4  |

|           |                     | 1.2.3    | Bus Interface                          | 1-4  |

|           |                     | 1.2.4    | Processor Interface                    | 1-5  |

|           |                     | 1.2.5    | Key Programmable Features              | 1-5  |

| Chapter 2 | Regi                | sters    |                                        |      |

|           | 2.1                 | Registe  | er Addresses                           | 2-2  |

|           | 2.2                 | Config   | uration Registers                      | 2-3  |

|           |                     | 2.2.1    | Configuration Register 0               | 2-3  |

|           |                     | 2.2.2    | Configuration Register 1               | 2-4  |

|           |                     | 2.2.3    | Packet Configuration Register          | 2-9  |

|           | 2.3                 | Ethern   | et Address Registers                   | 2-10 |

|           | 2.4 Error Registers |          | 2-11                                   |      |

|           |                     | 2.4.1    | Error Register 0                       | 2-11 |

|           |                     | 2.4.2    | Error Register 1                       | 2-12 |

|           | 2.5                 | Error N  | /lask Registers                        | 2-13 |

|           |                     | 2.5.1    | Error Mask Register 0                  | 2-13 |

|           |                     | 2.5.2    | Error Mask Register 1                  | 2-14 |

|           | 2.6                 | Statisti | cs Counters Registers                  | 2-15 |

|           |                     | 2.6.1    | Statistics Counters Address Register   | 2-15 |

|           |                     | 2.6.2    | Statistics Counters Data-In Registers  | 2-16 |

|           |                     | 2.6.3    | Statistics Counters Data-Out Registers | 2-16 |

|           | 2.7                 | Data F   | IFO Registers                          | 2-17 |

|           |                     | 2.7.1    | Data FIFO Address Register             | 2-17 |

|           |                     | 2.7.2    | Data FIFO Data-In Registers            | 2-19 |

Contents

|           |       | 2.7.3      | Data FIFO Data-Out Registers                | 2-19 |

|-----------|-------|------------|---------------------------------------------|------|

|           | 2.8   | Receive    | FIFO Head Pointer Registers                 | 2-20 |

|           | 2.9   | Receive    | FIFO Tail Pointer Registers                 | 2-20 |

|           | 2.10  | Transmit   | FIFO Head Pointer Registers                 | 2-21 |

|           | 2.11  | Transmit   | : FIFO Tail Pointer Registers               | 2-22 |

|           | 2.12  | Receive    | EOP Counters                                | 2-22 |

|           | 2.13  | Transmit   | EOP Counters                                | 2-23 |

| Chapter 3 | Signa | al Descrip | otions                                      |      |

|           | 3.1   | Network    | Interface Signals                           | 3-3  |

|           | 3.2   | Bus Inte   | rface Signals                               | 3-5  |

|           | 3.3   | Process    | or Interface Signals                        | 3-12 |

|           | 3.4   | Status S   | iignals                                     | 3-13 |

|           | 3.5   | Clock Si   | gnals                                       | 3-15 |

|           | 3.6   | Test Sig   | nals                                        | 3-15 |

|           | 3.7   | Miscella   | neous Signals                               | 3-16 |

| Chapter 4 | L643  | 81 Opera   | tion                                        |      |

|           | 4.1   | Ethernet   | : Cores                                     | 4-2  |

|           | 4.2   | On-chip    | FIFOs                                       | 4-3  |

|           |       | 4.2.1      | Transmit FIFO                               | 4-4  |

|           |       | 4.2.2      | Receive FIFO                                | 4-5  |

|           | 4.3   | Bus Inte   | rface                                       | 4-6  |

|           |       | 4.3.1      | Bus-Out State Machine                       | 4-6  |

|           |       | 4.3.2      | Bus-In State Machine                        | 4-10 |

|           | 4.4   | Process    | or Interface                                | 4-15 |

|           |       | 4.4.1      | Reading the L64381 Internal Registers       | 4-15 |

|           |       | 4.4.2      | Writing the L64381 Internal Registers       | 4-16 |

|           |       | 4.4.3      | Burst Mode Reads of the Statistics Counters | 4-17 |

|           | 4.5   | PLL Cor    | nnections                                   | 4-17 |

|           | 4.6   | Twisted-   | Pair Interface                              | 4-18 |

|           | 4.7   | AUI Inte   | rface                                       | 4-19 |

|           | 4.8   | JTAG In    | itialization                                | 4-19 |

|           |       |            |                                             |      |

# Chapter 5 Statistics Counters

vi

| Chapter 6  | Instru                                                                              | ıction Set                                                                                                                                                                                                                                                                                                                      |                                                                                 |

|------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

|            | 6.1                                                                                 | Instruction Set Summary                                                                                                                                                                                                                                                                                                         | 6-1                                                                             |

|            | 6.2                                                                                 | Accessing the Data FIFO                                                                                                                                                                                                                                                                                                         | 6-4                                                                             |

|            |                                                                                     | 6.2.1 Reading the Data FIFO                                                                                                                                                                                                                                                                                                     | 6-4                                                                             |

|            |                                                                                     | 6.2.2 Writing to the Data FIFO                                                                                                                                                                                                                                                                                                  | 6-4                                                                             |

|            | 6.3                                                                                 | Accessing the Statistics Counters                                                                                                                                                                                                                                                                                               | 6-5                                                                             |

|            |                                                                                     | 6.3.1 Reading the Statistics Counters                                                                                                                                                                                                                                                                                           | 6-5                                                                             |

|            |                                                                                     | 6.3.2 Writing the Statistics Counters                                                                                                                                                                                                                                                                                           | 6-5                                                                             |

|            |                                                                                     | 6.3.3 Burst Read of the Statistics Counters                                                                                                                                                                                                                                                                                     | 6-6                                                                             |

| Chapter 7  | Speci                                                                               | ifications                                                                                                                                                                                                                                                                                                                      |                                                                                 |

|            | 7.1                                                                                 | AC Timing                                                                                                                                                                                                                                                                                                                       | 7-1                                                                             |

|            | 7.2                                                                                 | Electrical Requirements                                                                                                                                                                                                                                                                                                         | 7-8                                                                             |

|            | 7.3                                                                                 | Special VDD and VSS Connections                                                                                                                                                                                                                                                                                                 | 7-12                                                                            |

|            | 7.4                                                                                 | Packaging                                                                                                                                                                                                                                                                                                                       | 7-12                                                                            |

|            |                                                                                     | 7.4.1 Ordering Information                                                                                                                                                                                                                                                                                                      | 7-13                                                                            |

|            |                                                                                     | 7.4.2 Package Information                                                                                                                                                                                                                                                                                                       | 7-13                                                                            |

| Appendix A | Custo                                                                               | omer Feedback                                                                                                                                                                                                                                                                                                                   |                                                                                 |

|            |                                                                                     | L64381 Block Diagram                                                                                                                                                                                                                                                                                                            | 1-2                                                                             |

| Figures    | 1.1                                                                                 | E0-001 Block Blagram                                                                                                                                                                                                                                                                                                            | . –                                                                             |

| Figures    | 1.1<br>2.1                                                                          | Configuration Register 0                                                                                                                                                                                                                                                                                                        | 2-3                                                                             |

| Figures    |                                                                                     | _                                                                                                                                                                                                                                                                                                                               |                                                                                 |

| Figures    | 2.1                                                                                 | Configuration Register 0                                                                                                                                                                                                                                                                                                        | 2-3                                                                             |

| Figures    | 2.1<br>2.2                                                                          | Configuration Register 0 Configuration Register 1                                                                                                                                                                                                                                                                               | 2-3<br>2-4                                                                      |

| Figures    | 2.1<br>2.2<br>2.3                                                                   | Configuration Register 0 Configuration Register 1 Big-Endian Addressing                                                                                                                                                                                                                                                         | 2-3<br>2-4<br>2-7                                                               |

| Figures    | 2.1<br>2.2<br>2.3<br>2.4                                                            | Configuration Register 0 Configuration Register 1 Big-Endian Addressing Little-Endian Addressing                                                                                                                                                                                                                                | 2-3<br>2-4<br>2-7<br>2-7                                                        |

| Figures    | 2.1<br>2.2<br>2.3<br>2.4<br>2.5                                                     | Configuration Register 0 Configuration Register 1 Big-Endian Addressing Little-Endian Addressing Packet Configuration Register                                                                                                                                                                                                  | 2-3<br>2-4<br>2-7<br>2-7<br>2-9                                                 |

| Figures    | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6                                              | Configuration Register 0 Configuration Register 1 Big-Endian Addressing Little-Endian Addressing Packet Configuration Register Error Register 0                                                                                                                                                                                 | 2-3<br>2-4<br>2-7<br>2-7<br>2-9<br>2-11                                         |

| Figures    | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7                                       | Configuration Register 0 Configuration Register 1 Big-Endian Addressing Little-Endian Addressing Packet Configuration Register Error Register 0 Error Register 1                                                                                                                                                                | 2-3<br>2-4<br>2-7<br>2-7<br>2-9<br>2-11<br>2-12                                 |

| Figures    | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8                                | Configuration Register 0 Configuration Register 1 Big-Endian Addressing Little-Endian Addressing Packet Configuration Register Error Register 0 Error Register 1 Error Mask Register 0                                                                                                                                          | 2-3<br>2-4<br>2-7<br>2-7<br>2-9<br>2-11<br>2-12                                 |

| Figures    | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9                         | Configuration Register 0 Configuration Register 1 Big-Endian Addressing Little-Endian Addressing Packet Configuration Register Error Register 0 Error Register 1 Error Mask Register 0 Error Mask Register 1                                                                                                                    | 2-3<br>2-4<br>2-7<br>2-7<br>2-9<br>2-11<br>2-12<br>2-13                         |

| Figures    | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10                 | Configuration Register 0 Configuration Register 1 Big-Endian Addressing Little-Endian Addressing Packet Configuration Register Error Register 0 Error Register 1 Error Mask Register 0 Error Mask Register 1 Statistics Counters Address Register                                                                               | 2-3<br>2-4<br>2-7<br>2-7<br>2-9<br>2-11<br>2-12<br>2-13<br>2-14                 |

| Figures    | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11         | Configuration Register 0 Configuration Register 1 Big-Endian Addressing Little-Endian Addressing Packet Configuration Register Error Register 0 Error Register 1 Error Mask Register 0 Error Mask Register 1 Statistics Counters Address Register Statistics Counters Data In-Register 0                                        | 2-3<br>2-4<br>2-7<br>2-7<br>2-9<br>2-11<br>2-12<br>2-13<br>2-14<br>2-15         |

| Figures    | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11<br>2.12 | Configuration Register 0 Configuration Register 1 Big-Endian Addressing Little-Endian Addressing Packet Configuration Register Error Register 0 Error Register 1 Error Mask Register 0 Error Mask Register 1 Statistics Counters Address Register Statistics Counters Data In-Register 0 Statistics Counters Data In-Register 1 | 2-3<br>2-4<br>2-7<br>2-7<br>2-9<br>2-11<br>2-12<br>2-13<br>2-14<br>2-15<br>2-16 |

Contents

| 2.16 | Data FIFO Data In Register 0                        | 2-19 |

|------|-----------------------------------------------------|------|

| 2.17 | Data FIFO Data In Register 1                        | 2-19 |

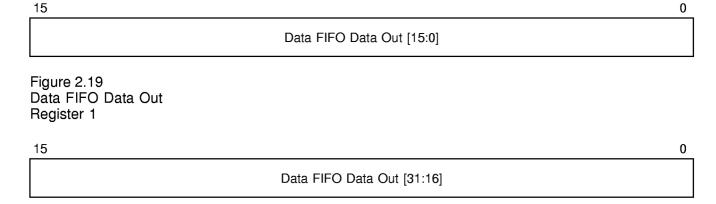

| 2.18 | Data FIFO Data Out Register 0                       | 2-19 |

| 2.19 | Data FIFO Data Out Register 1                       | 2-19 |

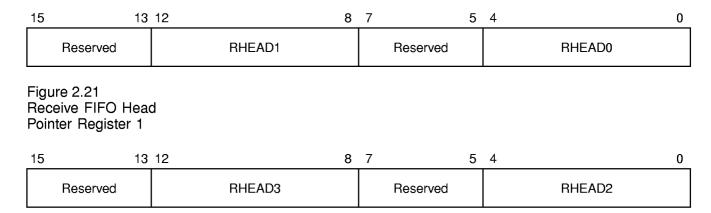

| 2.20 | Receive FIFO Head Pointer Register 0                | 2-20 |

| 2.21 | Receive FIFO Head Pointer Register 1                | 2-20 |

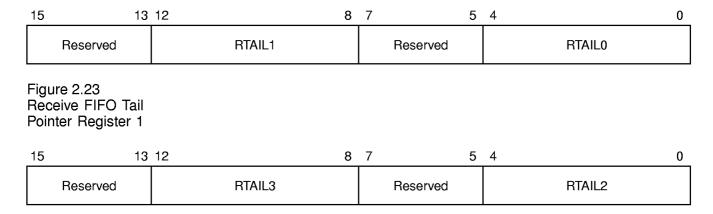

| 2.22 | Receive FIFO Tail Pointer Register 0                | 2-21 |

| 2.23 | Receive FIFO Tail Pointer Register 1                | 2-21 |

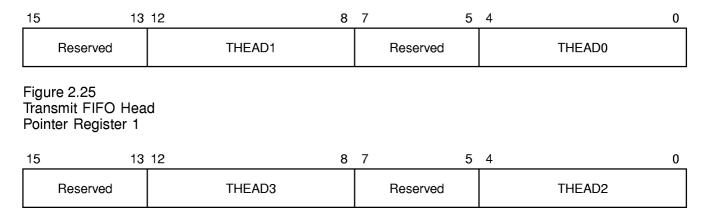

| 2.24 | Transmit FIFO Head Pointer Register 0               | 2-21 |

| 2.25 | Transmit FIFO Head Pointer Register 1               | 2-21 |

| 2.26 | Transmit FIFO Tail Pointer Register 0               | 2-22 |

| 2.27 | Transmit FIFO Tail Pointer Register 1               | 2-22 |

| 2.28 | Receive EOP Counter 0                               | 2-23 |

| 2.29 | Receive EOP Counter 1                               | 2-23 |

| 2.30 | Transmit EOP Counter 0                              | 2-23 |

| 2.31 | Transmit EOP Counter 1                              | 2-23 |

| 3.1  | L64381 Logic Diagram                                | 3-2  |

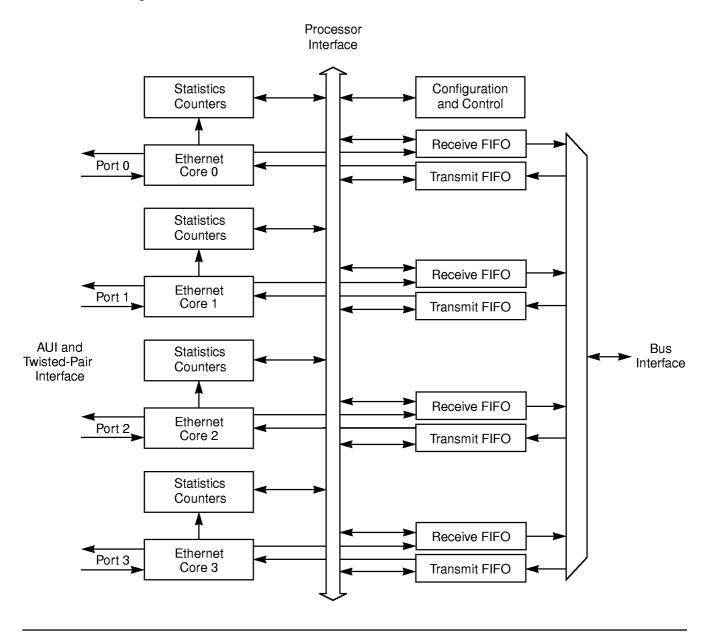

| 4.1  | L64381 Block Diagram                                | 4-2  |

| 4.2  | Data FIFO Block Diagram                             | 4-4  |

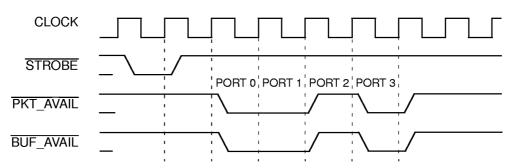

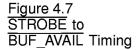

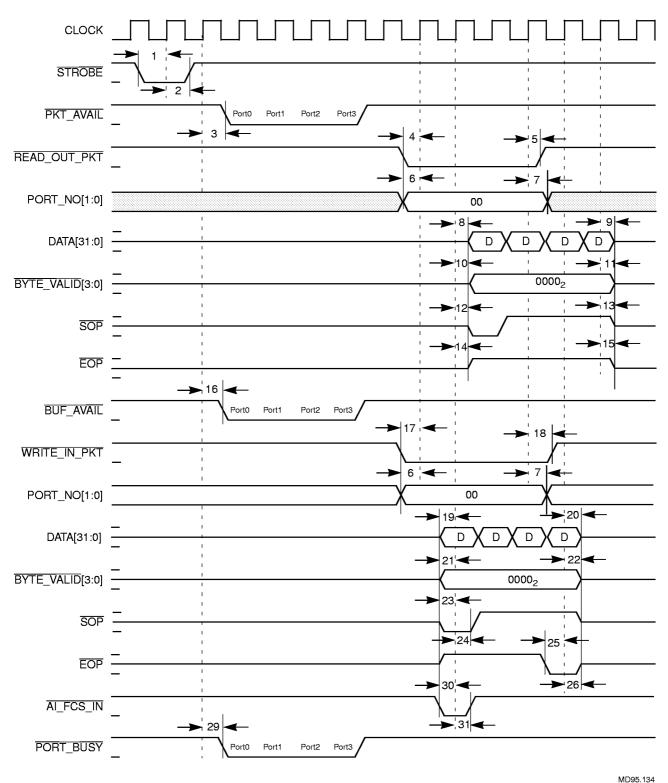

| 4.3  | STROBE to PKT_AVAIL Timing Relationship             | 4-6  |

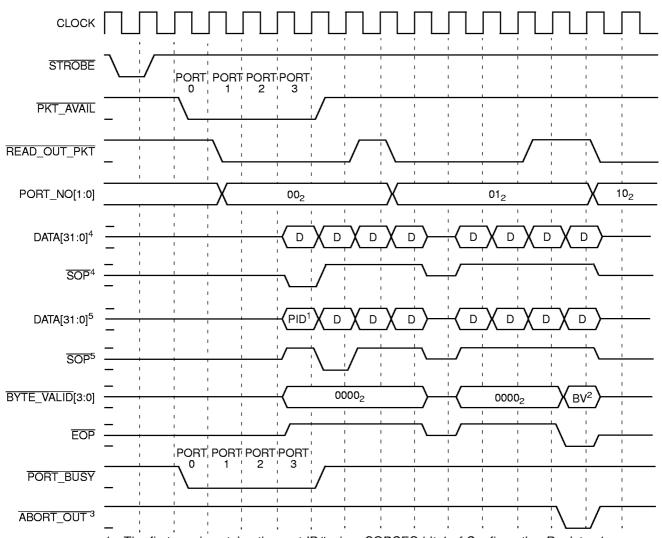

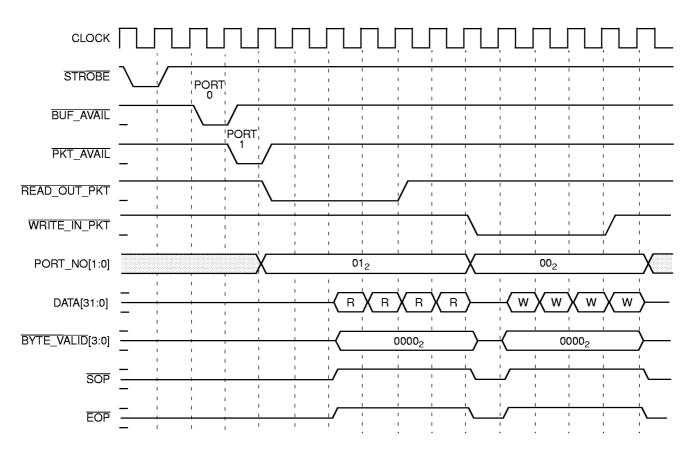

| 4.4  | Reading Packets from the L64381                     | 4-7  |

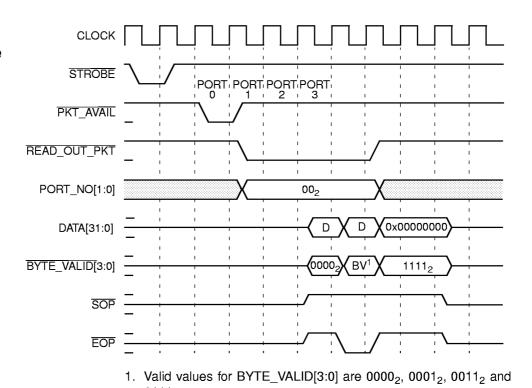

| 4.5  | Read Packet with EOP in the Middle of a Transfer    | 4-8  |

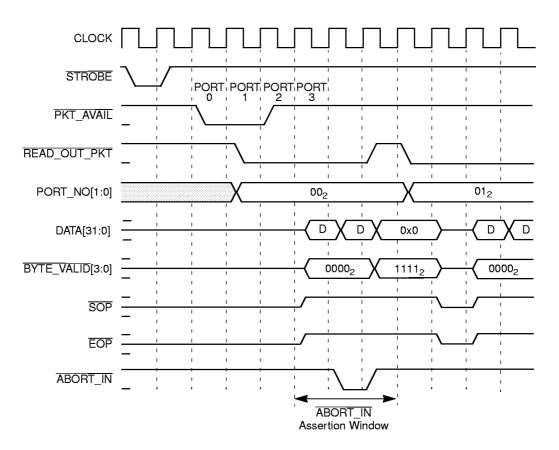

| 4.6  | Read Data with ABORT_IN Assertion                   | 4-10 |

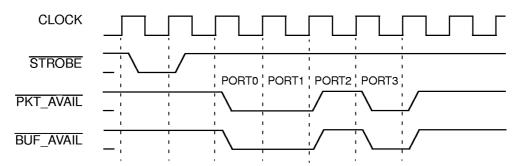

| 4.7  | STROBE to BUF_AVAIL Timing                          | 4-11 |

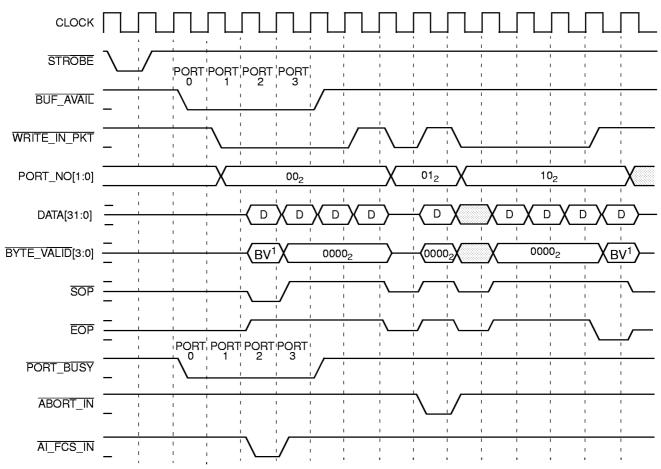

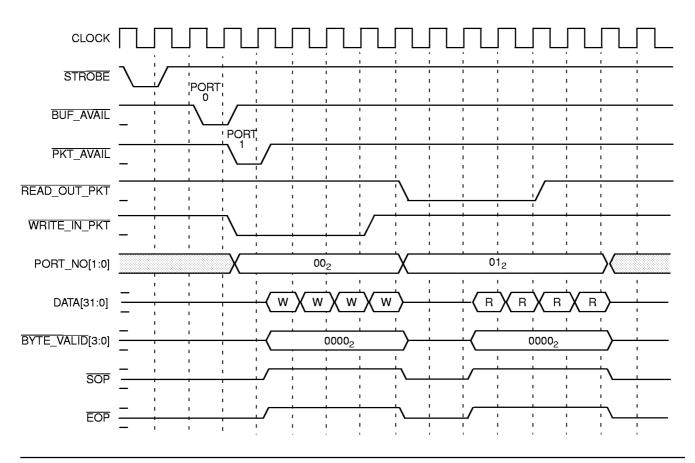

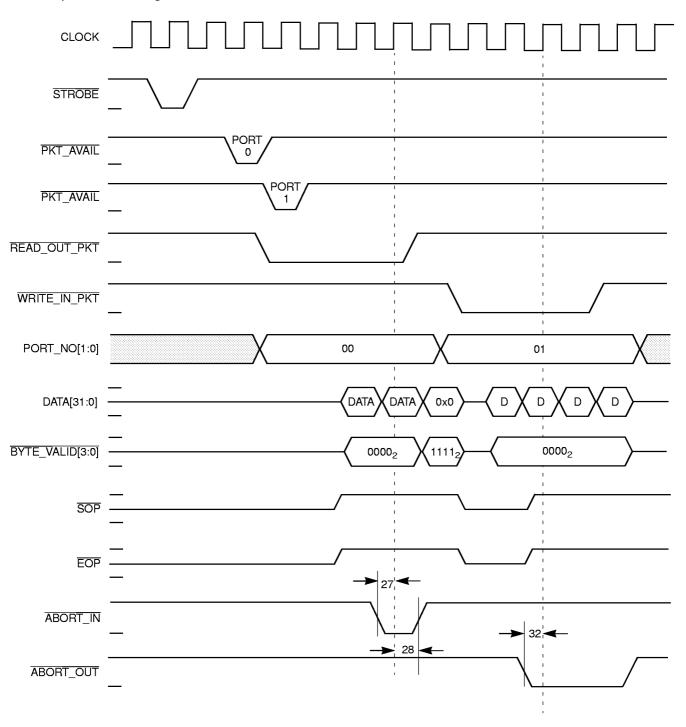

| 4.8  | Writing Packets to the L64381 with Port 1 Operation |      |

|      | Aborted                                             | 4-12 |

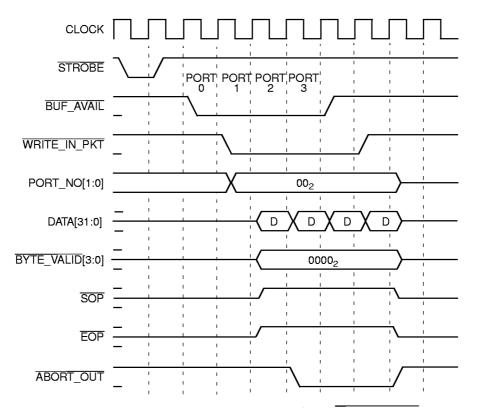

| 4.9  | Writing Packets to the L64381 with ABORT_OUT        |      |

|      | Asserted                                            | 4-13 |

| 4.10 | Read-then-Write Operations                          | 4-14 |

| 4.11 | Write-then-Read Operations                          | 4-15 |

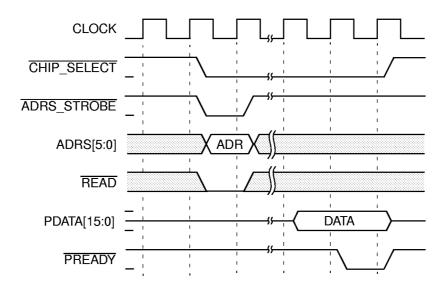

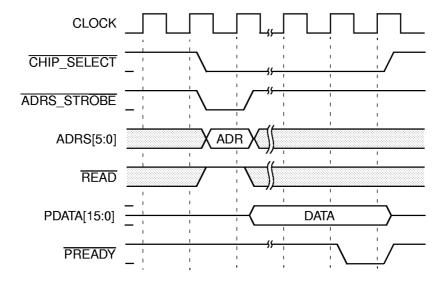

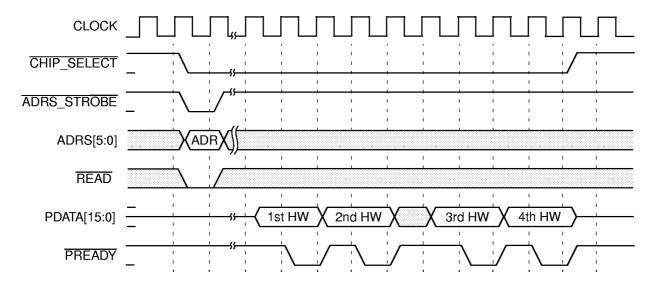

| 4.12 | Processor Read Timing                               | 4-16 |

| 4.13 | Processor Write Timing                              | 4-16 |

| 4.14 | Burst Read Access Timing to the L64381              | 4-17 |

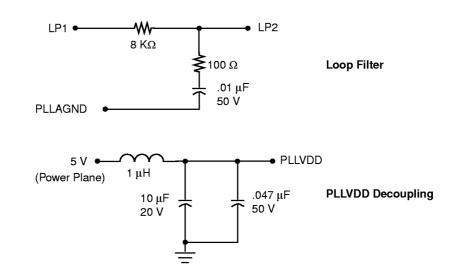

| 4.15 | Loop Filter and PLLVDD Decoupling                   | 4-18 |

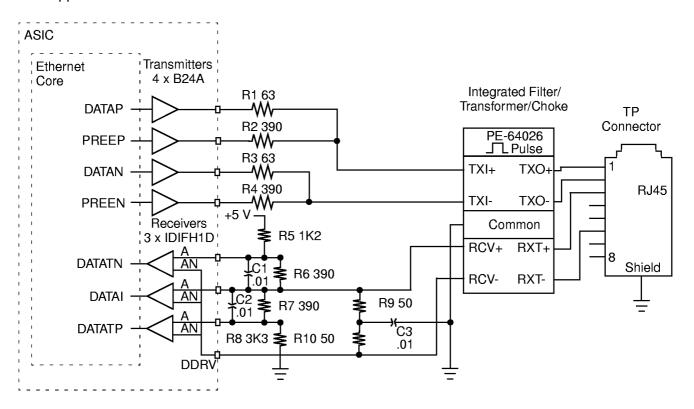

| 4.16 | Typical L64381 Twisted-Pair Application             | 4-18 |

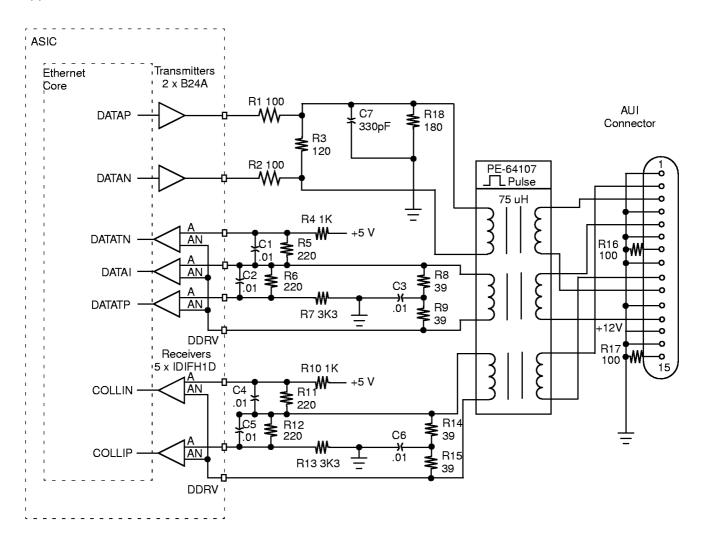

| 4.17 | Typical L64381 AUI Application                      | 4-19 |

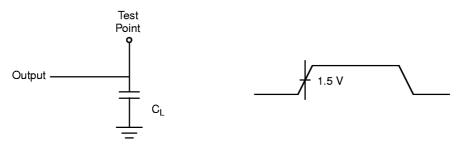

| 7.1  | AC Test Load and Waveform for Standard Outputs      | 7-1  |

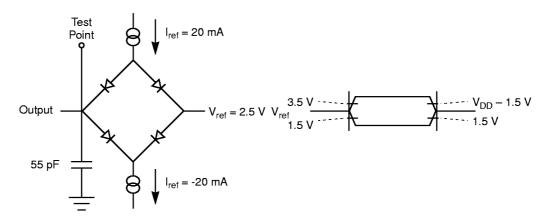

| 7.2  | AC Test Load and Waveform for 3-State Outputs       | 7-2  |

viii Contents

|        | 7.3  | Bus Interface Read and Write Timing        | 7-5  |

|--------|------|--------------------------------------------|------|

|        | 7.4  | Abort Operation Timing                     | 7-6  |

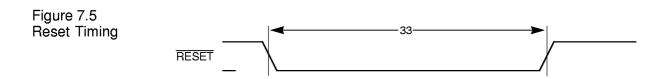

|        | 7.5  | Reset Timing                               | 7-7  |

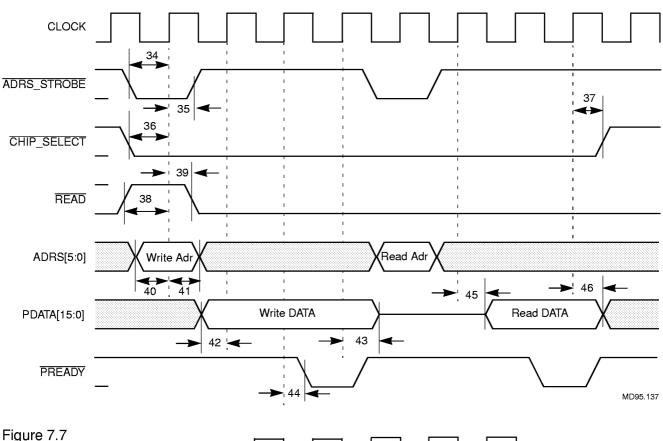

|        | 7.6  | Processor Interface Timing                 | 7-7  |

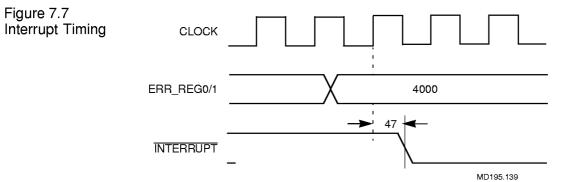

|        | 7.7  | Interrupt Timing                           | 7-7  |

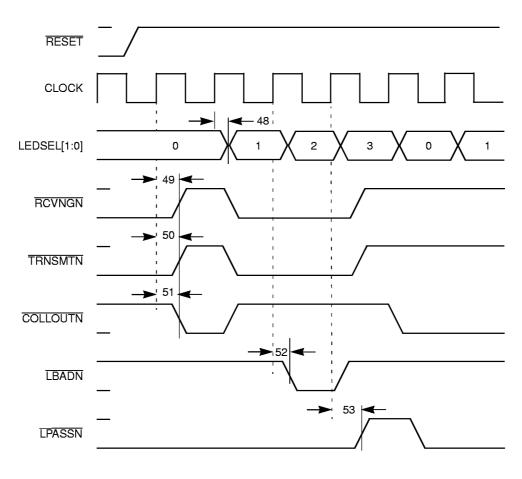

|        | 7.8  | Status Timing                              | 7-8  |

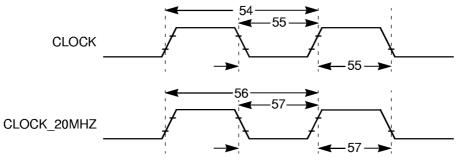

|        | 7.9  | Clock Timing                               | 7-8  |

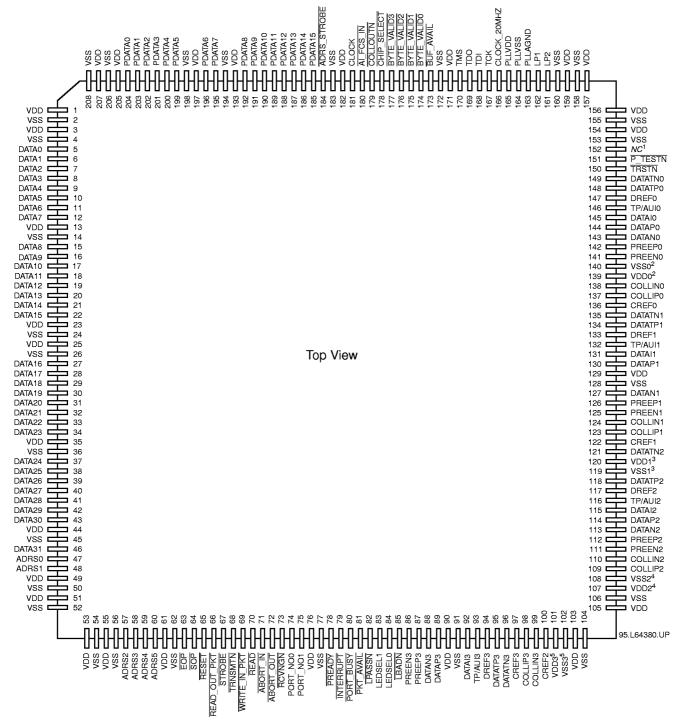

|        | 7.10 | 208-Pin PQFP Pinout                        | 7-15 |

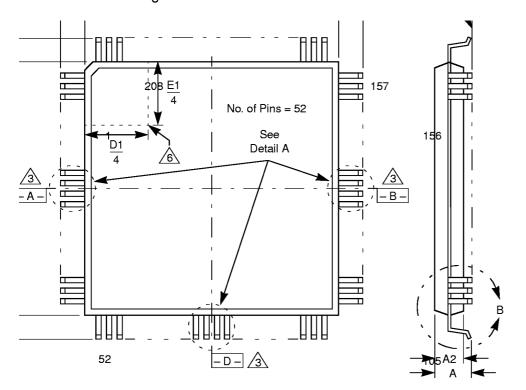

|        | 7.11 | 208-Pin PQFP Mechanical Drawing            | 7-16 |

| Tables | 2.1  | L64381 Register Summary                    | 2-2  |

|        | 5.1  | Descriptions of Statistics Counters        | 5-2  |

|        | 6.1  | L64381 Instructions                        | 6-1  |

|        | 7.1  | AC Timing Values                           | 7-3  |

|        | 7.2  | Absolute Maximum Ratings                   | 7-9  |

|        | 7.3  | Recommended Operating Conditions           | 7-9  |

|        | 7.4  | Capacitance                                | 7-9  |

|        | 7.5  | DC Characteristics                         | 7-10 |

|        | 7.6  | Pin Description Summary                    | 7-11 |

|        | 7.7  | VDD/VSS Pin Numbers Per Port               | 7-12 |

|        | 7.8  | L64381 Ordering Information                | 7-13 |

|        | 7.9  | Alphabetical Pin List for the 208-Pin PQFP | 7-14 |

Contents ix

# Chapter 1 Introduction

This document describes the L64381 (Quad CASCADE) 4-Port Ethernet Controller device, a highly integrated CMOS solution for Local Area Network (LAN) applications. The L64381 is derived from the 10-Mbps Ethernet Controller core. This multiport solution allows system designers to build cost-effective switched Ethernet hub or router products.

The L64381 consists of four ports, each with separate 128-byte Transmit and Receive FIFOs. The device architecture includes a high-performance 1-Gbps bus interface designed for fast packet transfers, and a processor interface for control and status checking purposes. The L64381 can be programmed for full-duplex or half-duplex operation, has individual, and promiscuous addressing modes, and supports both twisted-pair and AUI (Attachment Unit Interface) interfaces.

The L64381 has met all IEEE 802.3 signal conformance and interoperability tests.

Chapter 1 provides an overview of the L64381. It contains two sections:

- ♦ Section 1.1, "Overview"

- ♦ Section 1.2, "Key Features"

### 1.1 Overview

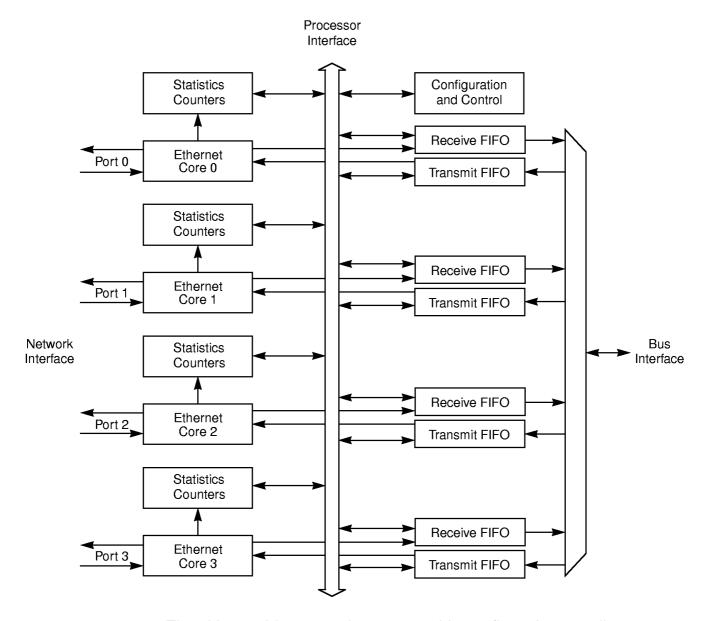

Figure 1.1 shows a block diagram of the L64381 device. The four Ethernet controllers are fully independent. Each L64381 port has its own MAC (Medium Access Control), Manchester Encoder/Decoder, and twisted-pair/AUI transceivers. The device is fully synchronous. It operates on a 16-MHz to 33-MHz host clock and a 20-MHz network clock. The 128-byte FIFOs are configurable for optimizing latency and throughput.

Each port has 23 Statistical Counters, which provide on-chip maintenance. These counters meet the statistics requirements of the Simple Network Management Protocol (SNMP).

Figure 1.1 L64381 Block Diagram

The chip provides several programmable configurations to allow customer product differentiation, such as source address insertion, FCS insertion, immediate retransmission on collision, bus transfer size, and transmit buffer threshold size.

The L64381 can be configured using the 6-bit Address bus and the 16-bit PData bus. All the internal registers can be read, and most also can be written. Special test modes are provided that make functional and in system testing simpler.

The Bus Interface is designed to allow efficient transfers of packet data to and from the L64381. Four bytes of data can be transferred per cycle on the bus with a burst size of 4, 8, or 16 words. One dead cycle is required between each burst cycle.

The scan interface allows for board-level testing using the JTAG (IEEE 1149.1) standard.

LSI Logic fabricates the L64381 in the CMOS cell-based process. The L64381 is available in a 208-pin Plastic Quad Flat Pack (PQFP) package.

## 1.2 Key Features

This section lists the general features of the L64381.

# 1.2.1 Ethernet Core

The Ethernet core features are categorized into four subsections: MAC, Encoder/Decoder, twisted-pair transceivers, and AUI transceivers.

#### 1.2.1.1 MAC Features

- ♦ IEEE 802.3 Ethernet Standards support

- ♦ Complete CSMA/CD Medium Access Control functions

- ◆ Twisted-pair, full-duplex mode for 20 Mbit/s throughput

- Individual address filter (individual and promiscuous addressing modes)

- ♦ Internal FCS generator and checker

#### 1.2.1.2 Encoder/Decoder

- ♦ 10 Mbit/s Manchester encoding/decoding

- ♦ Digital PLL with synchronous data recovery

- Manchester data decoded with 18-ns jitter

- ♦ PLL with fast-lock time

- ♦ Elasticity:

- Maximum time: 600 ns

- Maximum clock error @ 1518 byte frame: 0.05%

- Maximum clock error @ 4500 byte frame: 0.016%

Key Features 1-3

#### 1.2.1.3 Twisted-Pair (10BASE-T) Transceivers

- ♦ Integrated transceiver interface

- ♦ Collision detect

- Link integrity test

- ♦ Loopback test capabilities

- Autopolarity detection and correction

#### 1.2.1.4 Attachment Unit Interface (AUI) Transceivers

- ♦ Signal Quality Error test (Heartbeat)

- ♦ Smart receive squelch for receive data

- ♦ Smart SQE squelch for collision detection

- ◆ 10BASE-2, 10BASE-5, or 10BASE-F interface

### 1.2.2 Internal Architecture

This subsection highlights the features of the internal architecture:

- Independent 128-Byte Transmit and Receive FIFOs per Ethernet port

- ◆ Autotransmit on collision feature. First 64 transmit bytes buffered on chip to allow retransmission on collision without requiring bus transactions for first 64 bytes of packet

- Ability to generate or suppress FCS

- Next packet to transmit is queued while previous packet is still being transmitted, thus providing multiple back-to-back packet transmissions without wasted bandwidth

- Statistics per Ethernet core maintained on chip

- ♦ All registers are fully observable, most are controllable

# 1.2.3 Bus Interface

This subsection summarizes the key features of the L64381 bus interface:

- ♦ 32-bit data bus width

- Up to 48 ports (12 devices) at 20 Mbit/s can be connected based on approximately 1-Gbit bandwidth

- ◆ PKT\_AVAIL signal informs system when the Receive FIFO has more data than the programmable bus transfer size, or that an End-of-Packet (EOP) signal is present in the Receive FIFO, so that the FIFO data can be read by the system

- ♦ BUF\_AVAIL signal informs system when the Transmit FIFO has more space than the programmable bus transfer size, so that the system can write transmit data to the FIFO

- ♦ Four BYTE\_VALID signals specify which bytes are valid in the current data word (significant only for the first and last transfer in a packet when either the start-of-packet signal SOP or the end-of-packet signal EOP is asserted)

- ♦ SOP and EOP signals delimit start of packet and end of packet, respectively

- ♦ PORT\_BUSY signal per Ethernet core when operating in full-duplex or half-duplex mode

# 1.2.4 Processor Interface

This subsection highlights the features of the L64381 processor interface:

- ♦ 6-bit Address and 16-bit PData buses

- Slave mode device

- ♦ Chip Control and Status information can be read from Control and Status Registers

- Burst mode reads of Ethernet Statistics

- ♦ Interrupt signal to inform the processor if an error condition occurs

## 1.2.5 Key Programmable Features

The L64381 has several key programmable features:

- ♦ Individual twisted-pair or AUI assignment per port

- Automatic source address insertion

- ♦ Automatic FCS insertion

- ♦ Bus transfer size is configurable to 4, 8, or 16 words

- Addressing modes (individual, promiscuous, or multicast)

- ◆ Auto padding of packets less than 64 bytes in length

- Programmable little-endian and big-endian addressing modes

Key Features 1-5

# Chapter 2 Registers

The L64381 has a number of on-chip registers that configure and control it. In addition, all the FIFO pointers, FIFO Address and Data registers, and Statistics Counters are decoded as register addresses, so that the Processor Interface can read and write their values. This chapter describes the function of the registers with their associated bit fields.

This chapter has the following sections:

- ♦ Section 2.1, "Register Addresses"

- Section 2.2, "Configuration Registers"

- Section 2.3, "Ethernet Address Registers"

- ♦ Section 2.4, "Error Registers"

- Section 2.5, "Error Mask Registers"

- Section 2.6, "Statistics Counters Registers"

- ♦ Section 2.7, "Data FIFO Registers"

- Section 2.8, "Receive FIFO Head Pointer Registers"

- Section 2.9, "Receive FIFO Tail Pointer Registers"

- Section 2.10, "Transmit FIFO Head Pointer Registers"

- Section 2.11, "Transmit FIFO Tail Pointer Registers"

- Section 2.12, "Receive EOP Counters"

- ♦ Section 2.13, "Transmit EOP Counters"

# 2.1 Register Addresses

Table 2.1 summarizes the addresses of the L64381 registers. The ADRS[5:0] inputs determine which register is being accessed.

Table 2.1 L64381 Register Summary

| ADRS[5:0] | Accessibility    | Register                                |

|-----------|------------------|-----------------------------------------|

| 000010    | R/W <sup>1</sup> | Configuration Register 0                |

| 000011    | R/W              | Configuration Register 1                |

| 000100    | R/W              | Ethernet Address Register 0             |

| 000101    | R/W              | Ethernet Address Register 1             |

| 000110    | R/W              | Ethernet Address Register 2             |

| 000111    | R/W              | Packet Configuration Register           |

| 001000    | R/W              | Error Register 0                        |

| 001010    | R/W              | Error Register 1                        |

| 001001    | R/W              | Error Mask Register 0                   |

| 001011    | R/W              | Error Mask Register 1                   |

| 010000    | R/W              | Statistics Counters Data In Register 0  |

| 010001    | R/W              | Statistics Counters Data In Register 1  |

| 010010    | R/O <sup>2</sup> | Statistics Counters Data Out Register 0 |

| 010011    | R/O              | Statistics Counters Data Out Register 1 |

| 010110    | R/W              | Statistics Counters Address Register    |

| 011000    | R/W              | Data FIFO Data In Register 0            |

| 011001    | R/W              | Data FIFO Data In Register 1            |

| 011010    | R/O              | Data FIFO Data Out Register 0           |

| 011011    | R/O              | Data FIFO Data Out Register 1           |

| 011110    | R/W              | Data FIFO Address Register              |

| 100000    | R/W              | Receive FIFO Head Pointer Register 0    |

| 100001    | R/W              | Receive FIFO Head Pointer Register 1    |

| 100010    | R/W              | Receive FIFO Tail Pointer Register 0    |

| 100011    | R/W              | Receive FIFO Tail Pointer Register 1    |

| 100100    | R/W              | Transmit FIFO Head Pointer Register 0   |

| 100101    | R/W              | Transmit FIFO Head Pointer Register 1   |

| 100110    | R/W              | Transmit FIFO Tail Pointer Register 0   |

| 100111    | R/W              | Transmit FIFO Tail Pointer Register 1   |

| 101000    | R/W              | Receive EOP Counter 0                   |

| 101001    | R/W              | Receive EOP Counter 1                   |

| 101010    | R/W              | Transmit EOP Counter 0                  |

| 101011    | R/W              | Transmit EOP Counter 1                  |

- 1. Read/Write.

- 2. Read Only.

## 2.2 Configuration Registers

There are three configuration registers: Configuration Register 0, Configuration Register 1, and the Packet Configuration Register. These registers initialize the overall L64381. In the following subsections, the letter 'x' is used to imply any one of the four ports. Bit assignments are made in ascending order—Port 0 is assigned the lowest bit, and Port 3 is assigned the highest bit.

# 2.2.1 Configuration Register 0

Figure 2.1 shows the bit assignments for Configuration Register 0. This 16-bit register is read/write.

Figure 2.1 Configuration Register 0

| 15 | 14  | 13 8  | 7 4    | 3 0    |

|----|-----|-------|--------|--------|

|    | RES | PRTID | PRTMDE | DUPLEX |

RES Reserved [15:14]

These bits are reserved and read as zeroes.

# PRTID PORT ID [13:8]

These six bits assign unique, sequential ID numbers to the ports. This field is useful for applications with multiple L64381 devices. PORT 0 is assigned an eight-bit number, which is the PORT ID field appended with  $00_2$ , PORT 1 is assigned the value {PORT ID ||  $01_2$ }, PORT 2 is assigned the number {PORT ID ||  $10_2$ }, and PORT 3 is assigned the number {PORT ID ||  $11_2$ }.

The SOPCFG bit must be set to one for this field to be meaningful. Refer to the description of SOPCFG in Section 2.2.2, "Configuration Register 1."

#### PRTMDE PORT x Mode

These four bits configure the corresponding port to receive all packets that are sent on the Ethernet. (Bit 4 corresponds to Port 0, Bit 5 corresponds to Port 1, etc.) If one of these bits is reset to zero (Port Mode is OFF), then the corresponding port receives only the packets that exactly match the Ethernet address specified in the

[7:4]

Ethernet Address Registers. No broadcast or multicast packets are accepted in the OFF mode.

If one of these bits is set to one (Port Mode is ON), then the corresponding port receives all packets that are sent on the Ethernet, regardless of the address specified in the Ethernet Address Registers. The ports also receive all broadcast and multicast packets in the ON mode.

#### DUPLEX PORT x Duplex Mode

[3:0]

These four bits configure the corresponding Ethernet ports to half-duplex or full-duplex mode (0 = Half Duplex; 1 = Full Duplex). Bit 0 configures Port 0, Bit 1 configures Port 1, etc.

# 2.2.2 Configuration Register 1

Figure 2.2 shows the bit assignments for Configuration Register 1. This 16-bit register is read/write. To modify any of these bits, the processor should perform a read-modify-write operation in order to retain the values of the non-affected bits in this register.

Figure 2.2 Configuration Register 1

| 15  | 14 13 | 12     | 98 7   | 6 5 | 4      | 3    | 2 1   | 0   |

|-----|-------|--------|--------|-----|--------|------|-------|-----|

| WEP | DIAG  | LOOPBK | THRESH | BUS | SOPCFG | ENDN | BURST | WEN |

WEP Write Enable Port 15

Setting this bit to one enables writing to the four bits in the ENPORTx field in the Packet Configuration Register. The ENPORTx field enables/disables the four ports.

#### DIAG Diagnostic Modes [14:13]

These bits determine the type of mode in which the L64381 operates.

| DIAG | Mode                        | Description                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0, 2 | Normal                      | The L64381 is in normal operating mode (active) as described in this document.                                                                                                                                                                                                                                                                                                                                    |

| 1    | R/W<br>Register             | In this mode, the L64381 is halted. This mode is used for reading and writing values into the FIFO Pointer Registers, the Data FIFO, and the Statistics Counters. This mode is provided for testing the Transmit and Receive FIFO Pointer registers and the Data FIFO and Counters. In normal mode, it is not possible for the processor to directly write data into the FIFO Pointer registers or the Data FIFO. |

| 3    | FIFO and<br>Counter<br>Test | This mode puts the FIFO address register and the Statistics Counter address counter into an increment mode. An initial value is loaded into the address register, and then the address increments itself on every read and write operation to the FIFO or counter. This mode is useful for testing the Data FIFO and Statistics Counters, as well as initializing them.                                           |

#### LOOPBK

### Per Port Loopback Mode

[12:9]

When one of these bits is set to one, its corresponding port operates in local loopback mode. In this mode, the transmitter output is fed back into the receiver input, thus allowing local testing without requiring an external loopback connector. The following table shows the relationship between the LOOPBK register bits and their corresponding ports. This mode applies to full-duplex configuration only.

| LOOPBK Bit | Port |

|------------|------|

| 12         | 3    |

| 11         | 2    |

| 10         | 1    |

| 9          | 0    |

These two bits determine the number of words that need to be stored in the Transmit FIFO before it initiates a packet transmit on the Ethernet.

| П  | # of Stored Words |

|----|-------------------|

| 00 | 4 words           |

| 01 | 8 words           |

| 10 | 16 words          |

| 11 | 16 words          |

#### BUS Bus Transfer Size

[6:5]

These bits specify the maximum number of words that the L64381 transfers across the Bus Interface whenever the L64381 asserts either <a href="https://pexpeculiar.nlm.nih.gov/PKT\_AVAIL">PKT\_AVAIL</a> or <a href="https://pubm.nih.gov/BUF\_AVAIL">BUF\_AVAIL</a> in response to the assertion of <a href="https://pexpeculiar.nlm.nih.gov/STROBE">STROBE</a>.

| BUS | Transfer Size |

|-----|---------------|

| 00  | 4 words       |

| 01  | 8 words       |

| 10  | 16 words      |

| 11  | 16 words      |

that to externally control the length of the trans-Note: fer, the system could deassert either READ OUT PKT or WRITE IN PKT before the BUS amount of words is transferred across the Bus Interface. However, READ OUT PKT or WRITE IN PKT should not be kept asserted after the BUS amount of words has been transferred, because the L64381 does not guarantee the response. If an EOP signal is asserted in the middle of a transfer, the L64381 drives idle data (zeros) until it detects the deassertion of READ OUT PKT. If the L64381 detects an EOP while WRITE IN PKT is asserted, then it stops writing data into the Transmit FIFO after that cycle.

#### SOPCFG Start

#### **Start of Packet Configuration**

4

When this bit is set to one, the L64381 assumes that the first word in any packet that the host writes into its Transmit FIFO contains Packet Configuration Information. In this case, the least-significant four bits in the Packet Configuration Register are ignored and are replaced with the four least-significant bits from the first word in the packet. Therefore, each port is configured on a perpacket basis. In addition, when the L64381 receives packets from the Ethernet, it appends one extra word containing the PORT ID number in front of the packet so that the host knows which port the packet is coming from, and can insert the Packet Configuration Information into this space later. (The PORT ID number is placed at the least-significant byte of the first word.)

If SOPCFG is not set, then the Packet Configuration Information bits of the Packet Configuration Register are used as the Packet Configuration Information for all packets that are transmitted by the L64381. In this case, the PORT ID number is not used. Refer to Figure 4.4 for SOP timing.

#### **ENDN**

#### **Endian Addressing**

3

When this bit is set to zero, the L64381 addressing mode on the Processor Interface is big endian (see Figure 2.3). When this bit is set to one, the addressing mode is little endian (see Figure 2.4). Because the L64381 is not byte addressable, this bit only affects the Burst Read instruction.

Figure 2.3 Big-Endian Addressing

PDATA15 PDATA0

Most-Significant 16 bits

Least-Significant 16 bits

second read

first read

Figure 2.4 Little-Endian Addressing

Least-Significant 16 bits

first read

Most-Significant 16 bits

second read

When accessing statistics from the Statistics Counters in big-endian and burst modes, the two most-significant bytes of the counter are placed on the PDATA bus before the two least-significant bytes. In little-endian and burst modes, the two least-significant bytes are placed on the PDATA bus before the two most-significant bytes.

The ENDN bit setting affects only the Processor Interface and has no effect on the little-endian Bus Interface. During a Bus Interface write transaction, the L64381 looks for the first valid byte from either DATA[7:0], DATA[15:8], DATA[23:16] or DATA[31:24]. This choice depends on the value of BYTE\_VALID[3:0]. The L64381 then sends the valid byte to the network. In the first example below, DATA[7:0] goes to the network first, then DATA[15:8], and finally DATA[23:16]. The second example has only two valid bytes, so DATA[23:16] is passed to the network first, and DATA[31:24] follows.

| BYTE_VALID[3:0] | 1000 <sub>2</sub> | 00112        |

|-----------------|-------------------|--------------|

| Blts[31:24]     | Invalid Byte      | Second Byte  |

| Bits [23:16]    | Third Byte        | First Byte   |

| Bits [15:8]     | Second Byte       | Invalid Byte |

| Bits [7:0]      | First Byte        | Invalid Byte |

#### **BURST**

#### **Burst Mode Size**

[2:1]

These bits define the number of burst transfers that the L64381 can perform on the Processor Interface in response to a burst mode instruction. The Burst Mode allows the processor to quickly read all the statistics collected by the L64381 per Ethernet port without having to execute individual read instructions per statistic.

| BURST[2:1] | Transfer Size       |

|------------|---------------------|

| 00         | 2 16-bit transfers  |

| 01         | 4 16-bit transfers  |

| 10         | 8 16-bit transfers  |

| 11         | 16 16-bit transfers |

Note: These bits refer only to the Processor Interface; the Bus Transfer Size (BUS) bits define the transfer size on the Bus Interface.

Setting this bit to one enables writing to the six-byte Ethernet address of the ports. The user should reset this bit as soon as the address has been assigned in order to reduce the chances of an accidental overwrite of the address.

2.2.3

Packet

Configuration

Register

Figure 2.5 shows the Packet Configuration Register. This 16-bit read/write register contains programming information for packets and control bits that enable and disable the ports. The information stored in the least-significant four bits of this register are applied to all four ports on the L64381. To override the information in these four bits with packet specific information, set the SOPCFG bit in Configuration Register 1 to one. The most-significant four bits of this register enable the individual ports (1 = Enabled). In the disabled state, the ports will not respond to any internal or external stimuli.

Figure 2.5 Packet Configuration Register

| 15 | 12      |              | 87         | 4 | 3   | 2   | 1 | 0    |

|----|---------|--------------|------------|---|-----|-----|---|------|

|    | ENPORTx | LFORCEPPORTx | LCORPPORTx | S | S64 | PAD | R | AUTO |

#### **ENPORTX** Enable Port x

[15:12]

When one of these bits is set, the associated port is enabled and it functions as specified in Configuration Registers 0 and 1. When one of these bits is reset, the associated port is reset (disabled), the associated port's outputs are negated, and the Head and Tail Pointers and EOP counters are reset to zeros. This field can only be written if the WEP bit in Configuration Register 1 is set to one.

#### **LFORCEPPORTX**

#### Link Force Port x

[11:8]

When one of these bits is set, the associated port allows a transmit even if the link integrity fails. Refer to Chapter 2, "Signal Descriptions," in the *Compacted and Scalable Dedicated Ethernet (CASCADE) Core Technical Manual* for a description of the LFORCEP signal.

### **LCORPPORT** Link Correct Polarity Port x

[7:4]

When one of these bits is set, the associated port corrects for inverted polarity on the twisted-pair interface, if an inverted polarity condition exists on that port. Refer to Chapter 2, "Signal Descriptions," in the *Compacted and Scalable Dedicated Ethernet (CASCADE) Core Technical Manual* for a description of the LCORPP signal.

#### S64 Store First 64 Bytes

3

When this bit is set, each port's Transmit FIFO stores the first 64 bytes of a packet until all bytes have been transmitted without collisions on the Network Interface. Once the first 64 bytes are transmitted, the FIFO releases the locations that were used to store these bytes, thereby allowing new data to be fetched into the FIFO. This feature allows the port to retransmit the packet without requiring extra transfers on the Bus Interface. This bit is valid only when the SOPCFG bit is zero.

#### PAD Automatic Packet Padding

2

When this bit is set, the ports automatically pad a runt packet to a length of 64 bytes. This feature allows better utilization of the Transmit FIFO space, because all runt packets do not need to be pre-padded to the minimum Ethernet packet size. This bit has effect only when AI\_FCS\_IN is asserted and the SOPCFG bit is zero, or else the L64381 ignores this bit.

#### R Reserved

1

This bit is reserved and reads as zero.

#### AUTO Auto Insert Source Address

0

When this bit is set, the ports automatically insert the address stored in the Ethernet Address Registers into the source address field of the Ethernet packet. This bit is valid only when the SOPCFG bit is zero.

## 2.3 Ethernet Address Registers

The three Ethernet Address Registers (0 through 2) contain the 48-bit Ethernet address assigned to the L64381. Ethernet Address Register 0 contains the least-significant bytes of the Ethernet port address, and Ethernet Register 2 contains the most-significant bytes of the Ethernet address. These registers can be written only when the WEN bit in Configuration Register 1 is set to one.

Note:

The user should immediately reset the write enable bits after the address has been written. This action reduces the likelihood of an inadvertent change of the address due to a software bug. When the Port Mode is ON, the ports accept all packets received on the Ethernet regardless of the value in these registers. When the Port Mode is OFF, only those packets that exactly match the address in these registers are accepted.

# 2.4 Error Registers

The L64381 has two Error Registers, Error Register 0 and Error Register 1. The fields within these registers indicate the status of all errors the L64381 can detect. Upon detection of an error, the L64381 asserts the INTERRUPT output. To clear the interrupt, take the one's complement of the Error Register that caused the interrupt and write the value back into that register.

# 2.4.1 Error Register 0

Figure 2.6 shows Error Register 0. Error Register 0 is a 16-bit read-write register. Upon power-up or when RESET is asserted, all bits in this register are cleared to zeros (all interrupts are disabled).

Figure 2.6 Error Register 0

| 15 | 14   | 13 | 12   | 11 8  | 7 4    | 0      |

|----|------|----|------|-------|--------|--------|

| R  | PINT | R  | BINT | LATEC | RCFIFO | TRFIFO |

R Reserved 15, 13

These bits are reserved and read as zeros.

PINT Processor Interface Error 14

A one on this bit indicates that a Processor Interface error occurred (for example, a write to an unwritable location).

BINT Bus Interface Error 12

A one on this bit indicates that a Bus Interface error occurred. This error occurs when WRITE\_IN\_PKT and READ\_OUT\_PKT are both asserted at the same time.

Error Registers 2-11

#### LATEC PORT x Late Collision Error

[11:8]

A one on any of the bits in this field indicates that a Late Collision error occurred for the specific port. Each bit in this field corresponds to one of the four ports. The least-significant bit corresponds to Port 0; the most-significant bit corresponds to Port 3.

#### RCFIFO PORT x Receive FIFO Overrun Error [7:4]

A one on any of the bits in this field indicates that a Receive FIFO Overrun error occurred for the specific port. Each bit in this field corresponds to one of the four ports. The least-significant bit corresponds to Port 0; the most-significant bit corresponds to Port 3.

#### TRFIFO PORT x Transmit FIFO Underrun Error [3:0]

A one on any of the bits in this field indicates that a Transmit FIFO Underrun error occurred for the specific port. Each bit in this field corresponds to one of the four ports. The least-significant bit corresponds to Port 0; the most-significant bit corresponds to Port 3.

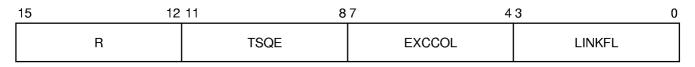

# 2.4.2 Error Register 1

Figure 2.7 shows Error Register 1. Error Register 1 is a 16-bit read/write register. Upon power-up or when RESET is asserted, all bits in this register will be zeros (all interrupts are disabled). Each active field in Error Register 1 contains four bits. Each bit corresponds to one of the four ports. The least-significant bit corresponds to Port 0; the most-significant bit corresponds to Port 3.

Figure 2.7 Error Register 1

R Reserved [15:12]

These bits are reserved and read as zeros.

TSQE Transmit SQE Error Port x [11:8]

A one on any of these bits indicates that an SQE error occurred for the specific port.

#### **EXCCOL** Excessive Collision Port x Error [7:4]

A one on any of the bits in this field indicates that the frame could not be transmitted after 16 attempts for the specific port. The L64381 aborts the transmission with no further retries.

#### LINKFL Link Failure Port x Error

[3:0]

A one on any of the bits in this field indicates that a Link Failure error (either no data or link integrity pulses were received for 100 ms) occurred for the specific port.

## 2.5 Error Mask Registers

The two Error Mask Registers contain the mask bits for the error fields in the corresponding Error Registers. When a bit is set to one in the Mask Register, the corresponding error is masked and the L64381 does not assert the INTERRUPT signal for that error condition.

# 2.5.1 Error Mask Register 0

Figure 2.8 shows Error Mask Register 0. This register contains the mask bits for the error fields in Error Register 0. Upon power-up or when RESET is asserted, all bits in this register are zeros.

Figure 2.8 Error Mask Register 0

| 15  | 14    | 13 | 12    | 11 8   | 7 4     | 3 0     |

|-----|-------|----|-------|--------|---------|---------|

| INT | PINTM | R  | BINTM | LATECM | RCFIFOM | TRFIFOM |

INT Enable Interrupts 15

When this bit is a one, the L64381 generates an interrupt whenever a bit in the Error Register is written to a one, provided that the bit's corresponding mask bit is not set in the Error Mask Register.

PINTM Processor Interface Error Mask 14

A one on this bit masks the Processor Interface error.

R Reserved 13

This bit is reserved and reads as zero.

BINTM Bus Interface Error Mask 12

A one on this bit masks the Bus Interface error.

#### LATECM PORT x Late Collision Error Mask [11:8]

A one on any of the bits in this field masks the corresponding port's late collision error. Each bit in this field corresponds to one of the four ports. The least-significant bit corresponds to Port 0; the most-significant bit corresponds to Port 3.

#### RCFIFOM PORT x Receive FIFO Overrun Error Mask [7:4]

A one on any of the bits in this field masks the corresponding port's Receive FIFO overrun error. Each bit in this field corresponds to one of the four ports. The least-significant bit corresponds to Port 0; the most-significant bit corresponds to Port 3.

#### TRFIFOM PORT x Transmit FIFO Underrun Error Mask [3:0]

A one on any of the bits in this field masks the corresponding port's Transmit FIFO underrun error. Each bit in this field corresponds to one of the four ports. The least-significant bit corresponds to Port 0; the most-significant bit corresponds to Port 3.

## 2.5.2 Error Mask Register 1

Figure 2.9 shows Error Mask Register 1. This register contains the mask bits for the error fields in Error Register 1. Upon power-up or when RESET is asserted, all bits in this register are cleared to zeros.

Figure 2.9 Error Mask Register 1

| 15 12 | 11 8  | 7 4     | 3 0     |

|-------|-------|---------|---------|

| R     | TSQEM | EXCCOLM | LINKFLM |

R Reserved [15:12]

These bits are reserved and read as zeros.

#### TSQEM Transmit SQE Error Port x Mask [11:8]

A one on any of the bits in this field masks the corresponding port's transmit SQE error. Each bit in this field corresponds to one of the four ports. The least-significant bit corresponds to Port 0; the most-significant bit corresponds to Port 3.

#### **EXCCOLM** Excessive Collision Port x Error Mask [7:4]

A one on any of the bits in this field masks the corresponding port's excessive collision error. Each bit in this field corresponds to one of the four ports. The least-significant bit corresponds to Port 0; the most-significant bit corresponds to Port 3.

#### LINKFLM Link Failure Port x Error Mask

A one on any of the bits in this field masks the corresponding port's link failure error. Each bit in this field corresponds to one of the four ports. The least-significant bit corresponds to Port 0; the most-significant bit corresponds to Port 3.

# 2.6 Statistics Counters Registers

This section describes the five registers that are used to access the Statistics Counters: the Statistics Counters Address Register, the two Statistics Counters Data-In Registers, and the two Statistics Counters Data-Out Registers.

# 2.6.1 Statistics Counters Address Register

Figure 2.10 shows the Statistics Counters Address Register. This read/write register stores a pointer to the Statistics Counters. This pointer is used to either read a counter value or write a value to the specified counter. When a burst read instruction is performed, the L64381 increments the counter value automatically, but the port number remains unaffected. Similarly in the autoincrement diagnostics mode, the L64381 does not increment the port number.

Figure 2.10 Statistics Counters Address Register

| 15 | 7 6  | 2 1 0 |

|----|------|-------|

| R  | STAT | PORT  |

R Reserved [15:7]

These bits are reserved and read as zeros.

STAT Statistics Counter [6:2]

These bits determine to which counter the read/write access pertains.

[3:0]

#### PORT Port Number

[1:0]

These bits select the port number of the selected counter in the STAT field.

# 2.6.2 Statistics Counters Data-In Registers

Figures 2.11 and 2.12 show the Statistics Counters Data-In Registers. The values in these two 16-bit registers are written into the Statistics Counters.

Note:

The write statistical counter operation may occur in any mode. Because the L64381 internally uses a big-endian addressing scheme, the lower 16 bits of the 32-bit data are written to Statistics Counters Data-In Register 0, and the upper 16 bits are written to Statistics Counters Data-In Register 1.

Figure 2.11 Statistics Counters Data In-Register 0

Statistics Counters Data In [15:0]

Figure 2.12 Statistics Counters Data In-Register 1

15 0

Statistics Counters Data In [31:16]

# 2.6.3 Statistics Counters Data-Out Registers

Figures 2.13 and 2.14 show the Statistics Counters Data-Out Registers. Values read from the Statistics Counters are placed in these two 16-bit, read-only registers. Because the L64381 internally uses a big-endian addressing scheme, the lower 16 bits of the 32-bit data are read out of Statistics Counters Data-Out Register 0, and the upper 16 bits are read out of Statistics Counters Data-Out Register 1.

Figure 2.13 Statistics Counters Data Out Register 0

15

Statistics Counters Data Out [15:0]

Figure 2.14

Statistics Counters

Data Out Register 1

15 0

Statistics Counters Data Out [31:16]

## 2.7 Data FIFO Registers

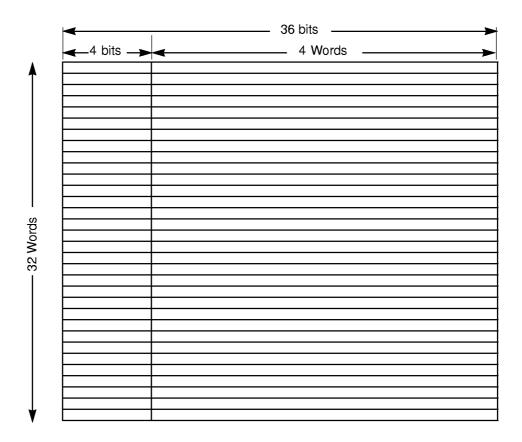

This section describes the five registers that are used to access the Data FIFO: the Data FIFO Address Register, the two Data FIFO Data In Registers, and the two Data FIFO Data Out Registers. The Transmit and Receive FIFOs contain 128 bytes in a 32 x 36 bit array. Refer to Section 4.2, "On-chip FIFOs," for more information on the configuration of the FIFOs.

# 2.7.1 Data FIFO Address Register

Figure 2.15 shows the Data FIFO Address Register. This 16-bit register contains the address for either a Data FIFO read or a Data FIFO write. Note that transfers between the Data FIFO Address Register and the Data FIFO occur only in Diagnostic Modes 1 and 3.

In Diagnostic Modes 1 and 3, the entire 36-bit wide FIFO can be tested. To write to a 36-bit location in the Data FIFO, the lower 32 bits are placed in the Data FIFO Data In Registers. The upper four bits are written to the Data FIFO from the WRAM field of the Data FIFO Address Register. To read back a Data FIFO location, the lower 32 bits are read into the Data FIFO Data Out Registers. The upper four bits are placed in the RRAM field of the Data FIFO Address Register.

Figure 2.15 Data FIFO Address Register

| 15 | 12   | 11   | 8 | 7     | 6     | 5  | 4 |          | 0 |

|----|------|------|---|-------|-------|----|---|----------|---|

|    | RRAM | WRAM |   | FIFOS | PORTI | NO |   | WORDADDR |   |

#### RRAM Read Data FIFO

[15:12]

During a Data FIFO read, the L64381 writes the value of the four most-significant bits in the selected Data FIFO location into these four bits. This value is the user-encoded value of BYTE\_VALID[3:0], SOP, EOP, and AI\_FCS\_IN. The addition of this field allows reading of all 36 bits of the selected Data FIFO without requiring an additional register decode.

#### WRAM Write Data FIFO

[11:8]

These bits contain the value to be written into the upper four bits of one of the 32 words in the selected Data FIFO. When a bus interface transaction occurs, this value is a user-encoded value for BYTE\_VALID[3:0], SOP, EOP, and AI\_FCS\_IN. The addition of this field allows writing of all 36 bits of the Data FIFO without requiring an additional register decode.

#### FIFOS FIFO Select

7

This bit selects either the Transmit FIFO (FIFOS = 0) or the Receive FIFO (FIFOS = 1) for the read or write operation.

#### PORTNO Port Number

[6:5]

This field selects the port number (3:0) for the read or the write operation.

#### WORDADDR Word Address

[4:0]

This field selects one of the words within the 128-byte FIFO.

When the processor writes to the Data FIFO Address Register, all 16 bits of the register are written, allowing for testing of the register. If the processor executes a Read Data FIFO instruction, the highest four bits are overwritten with the encoded value field of the Data FIFO. Therefore, when testing the Data FIFO Address Register, the user should execute a Read Data FIFO Address Register instruction before executing a Read Data FIFO instruction.

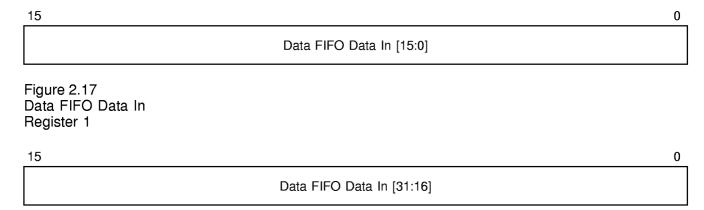

# 2.7.2 Data FIFO Data-In Registers

Figures 2.16 and 2.17 show the Data FIFO Data-In Registers. Values stored in these registers can be written into the Data FIFO in Diagnostic Modes 1 and 3 (refer to the DIAG field in Configuration Register 1). Because the L64381 uses a big-endian addressing scheme, it places the lower 16 bits of the 32-bit data in Data FIFO Data-In Register 0, and places the upper 16 bits in Data FIFO Data-In Register 1.

Figure 2.16 Data FIFO Data In Register 0

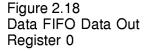

# 2.7.3 Data FIFO Data-Out Registers

Figures 2.18 and 2.19 show the Data FIFO Data-Out Registers. Values read from the Data FIFO are written into these read-only registers. Because the L64381 uses a big-endian addressing scheme, the lower 16 bits of the 32-bit data are read out of Data FIFO Data-Out Register 0, and the upper 16 bits are read out of Data FIFO Data-Out Register 1.

# 2.8 Receive FIFO Head Pointer Registers

Figures 2.20 and 2.21 show the Receive FIFO Head Pointer Registers. These registers are used to read and write the Receive FIFO head pointers. The head pointers point to the first location in the Receive FIFO with valid data to read. Register 0 contains the head pointers for Ports 0 and 1, and register 1 contains the head pointers for Ports 2 and 3. The FIFO pointers are each five bits in length. The most-significant bits of both bytes (bits [15:13] and [7:5]) are ignored on a write instruction, and a read of these registers returns a zero in bits [15:13] and [7:5].

Figure 2.20 Receive FIFO Head Pointer Register 0

# 2.9 Receive FIFO Tail Pointer Registers

Figures 2.22 and 2.23 show the Receive FIFO Tail Pointer Registers. These registers are used to read and write the Receive FIFO tail pointers. The tail pointers point to the first empty location in the Receive FIFO for writing data. Register 0 contains the tail pointers for Ports 0 and 1, and register 1 contains the tail pointers for Ports 2 and 3. The FIFO pointers are each five bits in length. The most-significant bits of both bytes (bits [15:13] and [7:5]) are ignored on a write instruction, and a read of these registers returns a zero in bits [15:13] and [7:5].

Figure 2.22 Receive FIFO Tail Pointer Register 0

# 2.10 Transmit FIFO Head Pointer Registers

Figures 2.24 and 2.25 show the Transmit FIFO Head Pointer Registers. These registers are used to read and write the Transmit FIFO head pointers. The head pointers point to the first location in the Transmit FIFO with valid data to read. Register 0 contains the head pointers for Ports 0 and 1, and Register 1 contains the head pointers for Ports 2 and 3. The FIFO pointers are each five bits in length. The most-significant bits of both bytes (bits [15:13] and [7:5]) are ignored on a write instruction, and a read of these registers returns a zero in bits [15:13] and [7:5].

Figure 2.24 Transmit FIFO Head Pointer Register 0

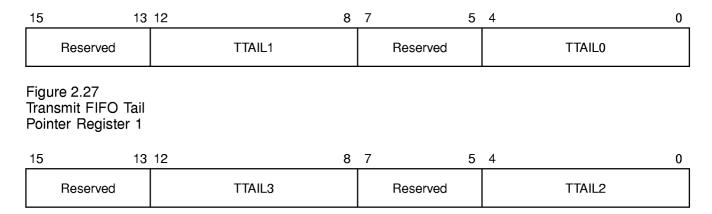

# 2.11 Transmit FIFO Tail Pointer Registers

Figures 2.26 and 2.27 show the Transmit FIFO Tail Pointer Registers. These registers are used to read and write the Transmit FIFO tail pointers. The tail pointers point to the first empty location in the Transmit FIFO for writing data. Register 0 contains the tail pointers for Ports 0 and 1, and register 1 contains the tail pointers for Ports 2 and 3. The FIFO pointers are each five bits in length. The most-significant bits of both bytes (bits [15:13] and [7:5]) are ignored on a write instruction, and a read of these registers returns a zero in bits [15:13] and [7:5].

Figure 2.26 Transmit FIFO Tail Pointer Register 0

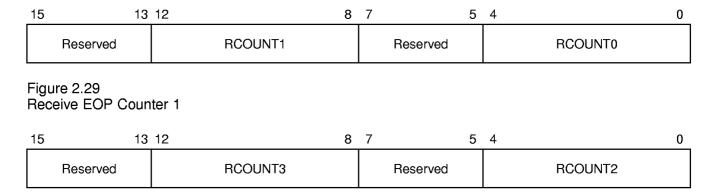

# 2.12 Receive EOP Counters

Figures 2.28 and 2.29 show the Receive EOP Counters. These counters count the number of end of packets (EOPs) that are in the Receive FIFO. The port increments the counter when it receives the end of a packet, and decrements the counter when the Bus Interface asserts EOP on the bus. If the counter value is greater than or equal to one, there is at least one EOP in the Receive FIFO. Even if the number of bytes left in the FIFO is less than the programmed bus transfer size (BUS field), the L64381 still asserts PKT\_AVAIL to allow the host to drain the Receive FIFO. This scheme permits better use of the Receive FIFO, because no padding of data is needed to align it with the Bus Transfer Size, hence FIFO space is not wasted with pad data. Counter 0 contains the counter values for Ports 0 and 1, and Counter 1 contains the counter values for Ports 2 and 3.

Figure 2.28 Receive EOP Counter 0

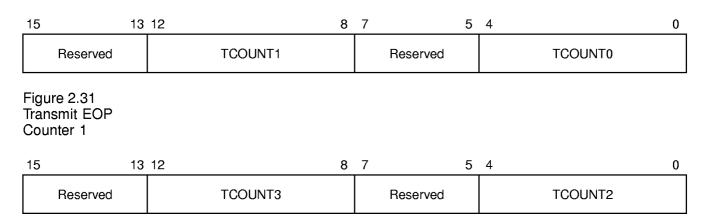

# 2.13 Transmit EOP Counters

Figures 2.30 and 2.31 show the Transmit EOP Counters. These counters count the number of EOPs that are present in the Transmit FIFO. The port increments the counter when the Bus Interface receives an end of a packet from the bus (EOP is asserted), and decrements the counter when the end of packet is sent to the port for transmission. Similar to the Receive EOP Counter, this scheme guarantees that a packet is transmitted when the packet size is smaller than the Transmit Threshold field. Note that this transmit can occur because the L64381 allows automatic padding of packets. This scheme permits better use of the Transmit FIFO, since no padding of data is needed to align it with the Transmit Threshold, hence FIFO space is not wasted with pad data. Register 0 contains the counter values for Ports 0 and 1, and Register 1 contains the counter values for Ports 2 and 3.

Figure 2.30 Transmit EOP Counter 0

# Chapter 3 Signal Descriptions

This chapter describes the signals that comprise the L64381's bit-level interface to other devices. This description is intended for hardware designers who are connecting the product to other components.

This chapter is divided into seven sections:

- ♦ Section 3.1, "Network Interface Signals"

- ♦ Section 3.2, "Bus Interface Signals"

- ♦ Section 3.3, "Processor Interface Signals"

- Section 3.4, "Status Signals"

- ♦ Section 3.5, "Clock Signals"

- ♦ Section 3.6, "Test Signals"

- ♦ Section 3.7, "Miscellaneous Signals"

The product's interface signals are described in alphabetical order by mnemonic. Each signal definition contains the mnemonic and the full signal name. The mnemonics for signals that are active LOW are marked with an overbar; all others are active HIGH. For example,  $\overline{\text{WE}}$  is active LOW, and RD is active HIGH.

In the descriptions that follow, the verb *assert* means to drive TRUE or active. The verb *deassert* means to drive FALSE or inactive.

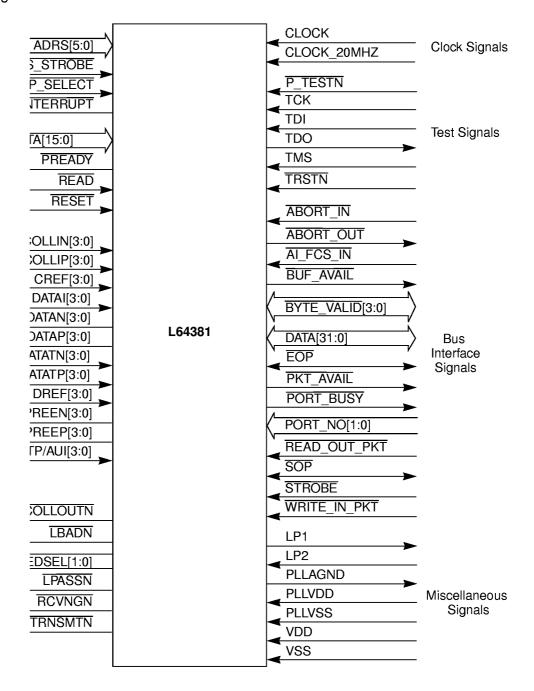

Figure 3.1 shows the logic diagram for the L64381.

Figure 3.1 L64381 Logic Diagram

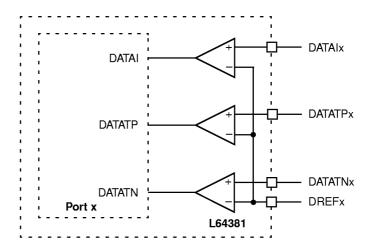

# 3.1 Network Interface Signals

This section describes the signals that comprise the L64381 Network Interface.

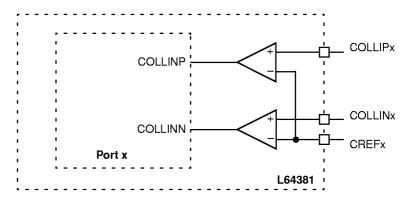

# COLLIN[3:0] Negative Collision Threshold

Input

COLLIN[3:0] and COLLIP[3:0] are used to detect collisions. COLLIN[3:0] are valid only in AUI mode (TP/AUI signal is LOW), and should be connected to the outputs of the negative collision threshold differential receivers. COLLIN[3:0] correspond to Ports [3:0], respectively.

#### COLLIP[3:0] Positive Collision Threshold

Input