## L64853A

Enhanced SBus DMA Gontroller Technical Manual

Second Edition

Document Number MS71-000104-99 B

This document applies to revision A of the L64853A Enhanced SBus DMA Controller and to all subsequent versions unless otherwise indicated in a subsequent edition or an update to this edition of the document.

Publications are stocked at the address given below. Requests should be addressed to:

LSI Logic Corporation Literature Distribution, M/S D-102 1551 McCarthy Boulevard Milpitas, CA 95035 Fax: 408.433.8989

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

© 1991, 1993 LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

LSI Logic logo design is a registered trademark of LSI Logic Corporation. SPARC is a registered trademark of SPARC International, Inc. Products bearing the SPARC trademarks are based on an architecture developed by Sun Microsystems, Inc. All other brand and product names may be trademarks of their respective companies.

### **Preface**

This book is the primary reference and technical manual for the L64853A Enhanced SBus DMA Controller. It contains a complete functional description for the L64853A and includes complete physical and electrical specifications for the L64853A.

#### Audience

This book assumes that you have some familiarity with microprocessors and related support devices. It also assumes readers have access to additional information about the SPARC workstation—in particular, the SBus specification, which can be obtained from Sun Microsystems, Inc. This book provides information for both system-level programmers and hardware designers as follows:

- System-Level Programmers For the system-level programmer, this manual briefly describes the SPARC workstation architecture, then fully describes the function of the chip with respect to the architecture.

- Chapter 1 describes the basic features and operation of the L64853A Enhanced DMA Controller and the chip's relationship to the other SPARC chips. Chapter 2 describes the internal, programmable registers of the L64853A, and it describes how to access both internal and external registers. Chapter 3 covers the two modes of operation and describes the internal cache memory. Chapters 4 and 5 further describe the operation of the D and E channels. To aid in implementation of the chip in a typical environment, Chapter 8 shows how to access the Emulex SCSI Processor (ESP-100) and the AMD Am7990 Local Area Network Controller for Ethernet (LANCE) internal registers.

- Hardware Designers For the hardware designer, this manual provides the electrical, logical, and mechanical data necessary to integrate the L64853A DMA Controller into the SPARC workstation.

Chapter 1 describes the architecture and operation of the L64853A. Chapters 4 and 5 provide detailed information on the D and E channels, respectively. Chapter 6 describes the data transfer cycles for the D and E channels and the signals used by the L64853A DMA Controller during read and write operations. Chapter 7 provides the AC, DC, environmental, and mechanical specifications for the L64853A. Chapter 8 discusses how to interface the L64853A to the ESP-100 and the LANCE.

#### Organization

This book has the following chapters:

- Chapter 1, Introduction, describes the basic features and operation of the L64853A Enhanced DMA Controller, showing its relationship to the other SPARC system elements.

- Chapter 2, Registers, describes the types of registers available on the L64853A and how to access internal and external registers.

- Chapter 3, L64853A Operation, describes the modes of operation on the SBus, which is used for data transfers between the peripheral subsystems and main memory. This chapter also discusses the internal cache memory, which provides data buffering between the peripheral subsystems and main memory.

- Chapter 4, **D-Channel Operation**, describes the DMA Controller's D channel, an eight-bit DMA control channel.

- Chapter 5, E-Channel Operation, describes the DMA Controller's E channel, a 16-bit DMA control channel.

- Chapter 6, Interface Description, describes the input and output signals used by the L64853A.

- Chapter 7, Specifications, provides the AC, DC, environmental, and mechanical specifications for the L64853A.

- Chapter 8, Applications, describes the types of SPARC workstation applications that the L64853A Enhanced DMA Controller fits into and provides interface examples to Emulex SCSI Processor (ESP-100) and to an AMD Local Area Network Controller (AM7990).

- Appendix A, L64853 and L64853A Differences, lists the major differences between the L64853 and L64853A SBus DMA Controllers.

- Appendix B, Customer Feedback, is a form for you to fill out with your comments on the content and quality of this document.

#### Related Publications

Building a Low-Cost SPARC-Based Multimedia Workstation White Paper, Order No. M22004.A

Designing with the SparKIT Chipset White Paper, Order No. M22001.A

SBus Solutions for Graphics, DMA, and All Other Applications White Paper, Order No. M22002.A

The SBus Specification available from Sun Microsystems, Inc., 2550 Garcia Avenue, Mountain View, CA 94042

## Conventions Used in this Manual

The first time a word or phrase is defined in this manual, it is italicized.

The following signal naming conventions are used throughout this manual:

- A level-significant signal that is true or valid when the signal is LOW always has an overbar (\_\_\_\_) over its name.

- An edge-significant signal that initiates actions on a HIGH-to-LOW transition always has an overbar ( ) over its name.

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive.

Hexadecimal numbers are indicated by the prefix "0x" before the number—for example, 0x32CF. Binary numbers are indicated by a subscripted "2" following the number—for example, 0011.0010.1100.1111<sub>2</sub>.

## **Contents**

| Chapter 1 | Introduction        |                                                |      |  |  |  |

|-----------|---------------------|------------------------------------------------|------|--|--|--|

|           | 1.1                 | General Description                            | 1-1  |  |  |  |

|           |                     | Architecture                                   | 1-2  |  |  |  |

|           |                     | Channel Operations                             | 1-3  |  |  |  |

|           | 1.2                 | Key Features                                   | 1-4  |  |  |  |

|           | 1.3                 | Enhancements                                   | 1-4  |  |  |  |

| Chapter 2 | Regi                | isters                                         |      |  |  |  |

|           | 2.1                 | Internal Programmable Registers                | 2-1  |  |  |  |

|           |                     | DMA Control/Status Register (CSR)              | 2-2  |  |  |  |

|           |                     | DMA Address Counter and Next Address Registers | 2-6  |  |  |  |

|           |                     | DMA Byte and Next Byte Counters                | 2-7  |  |  |  |

|           | 2.2                 | Internal and External ID Registers             | 2-7  |  |  |  |

|           | 2.3                 | Addressing Internal and External Registers     | 2-8  |  |  |  |

|           | 2.4                 | Internal Register Reads and Writes             | 2-10 |  |  |  |

| Chapter 3 | L64853A Operation   |                                                |      |  |  |  |

|           | 3.1                 | Modes of Operation                             | 3-1  |  |  |  |

|           |                     | Master Mode                                    | 3-1  |  |  |  |

|           |                     | Slave Mode                                     | 3-2  |  |  |  |

|           | 3.2                 | Internal Cache Memory                          | 3-3  |  |  |  |

|           |                     | Memory Reads                                   | 3-4  |  |  |  |

|           |                     | Memory Writes                                  | 3-4  |  |  |  |

| Chapter 4 | D-Channel Operation |                                                |      |  |  |  |

|           | 4.1                 | General Description                            | 4-1  |  |  |  |

|           | 4.2                 | Register Operation                             | 4-2  |  |  |  |

|           |                     | Operation without Data Block Chaining          | 4-2  |  |  |  |

|           |                     | Operation with Data Block Chaining             | 4-3  |  |  |  |

|           | 4.3                 | D-Channel Cache Operation                      | 44   |  |  |  |

Contents

## ■ 5304804 0012280 7T6 ■LLC

|           |       | Memory Reads                                   | 4-4  |

|-----------|-------|------------------------------------------------|------|

|           |       | Memory Writes                                  | 4-5  |

|           | 4.4   | Memory Errors and Interrupts                   | 4-5  |

|           | 4.5   | Read/Write Transactions                        | 4-6  |

|           |       | DMA Reads and Writes (Master Mode)             | 4-6  |

|           |       | Register Reads and Writes (Slave Mode)         | 4-10 |

|           | 4.6   | Programming Notes                              | 4-13 |

|           |       | Setting Up, Suspending, and Stopping Transfers | 4-13 |

|           |       | Using the Byte Counter with EN_NEXT = 0        | 4-14 |

|           |       | Using the Byte Counter with EN_NEXT = 1        | 4-15 |

| Chapter 5 | E-Ch  | annel Operation                                |      |

|           | 5.1   | General Description                            | 5-1  |

|           | 5.2   | E-Channel Cache Operation                      | 5-2  |

|           |       | Memory Reads                                   | 5-2  |

|           |       | Memory Writes                                  | 5-3  |

|           | 5.3   | Memory Errors                                  | 5-4  |

|           |       | Read Operations                                | 5-5  |

|           |       | Write Operations                               | 5-5  |

|           | 5.4   | Read/Write Transactions                        | 5-5  |

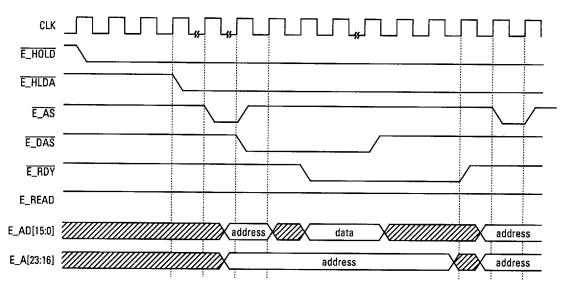

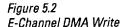

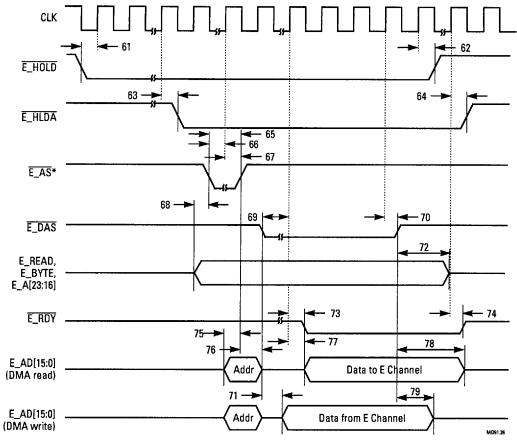

|           |       | DMA Reads and Writes (Master Mode)             | 5-5  |

|           |       | Register Reads and Writes (Slave Mode)         | 5-9  |

| Chapter 6 | Inter | face Description                               |      |

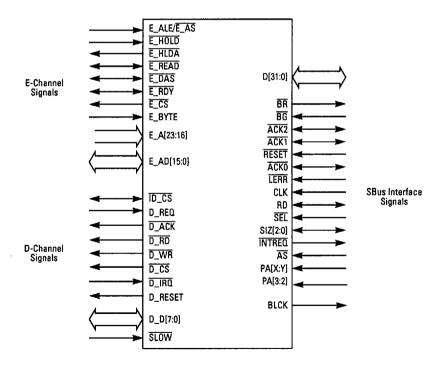

|           | 6.1   | D-Channel Signals                              | 6-2  |

|           | 6.2   | E-Channel Signals                              | 6-3  |

|           | 6.3   | SBus Interface Signals                         | 6-5  |

|           | 6.4   | Miscellaneous Signals                          | 6-7  |

| Chapter 7 | Spe   | cifications                                    |      |

|           | 7.1   | AC Characteristics                             | 7-1  |

|           | 7.2   | Electrical Specifications                      | 7-10 |

|           | 7.3   | Mechanical Specifications                      | 7-13 |

| Chapter 8 | Арр   | lications                                      |      |

|           | 8.1   | The SBus and the SPARC Workstation             | 8-1  |

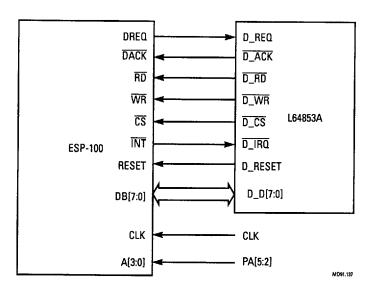

|           | 8.2   | Using the EMULEX SCSI Processor                | 8-3  |

|           |       | L64853A to ESP-100 Interconnection             | 8-3  |

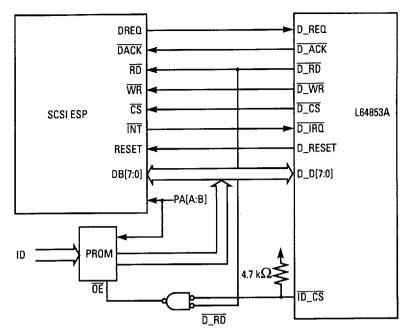

|           |       | Accessing ESP Internal Registers               | 8-4  |

### 5304804 0012281 632 MLLC

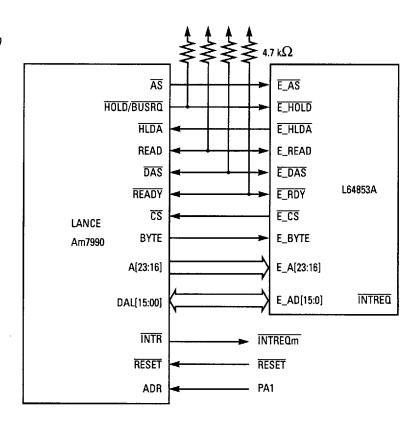

|            | 8.3         | Using the AMD LANCE Ethernet Controller                             | 8-5         |

|------------|-------------|---------------------------------------------------------------------|-------------|

|            |             | L64853A to LANCE Interconnection                                    | 8-5         |

|            |             | Accessing LANCE Internal Registers                                  | 8-6         |

| Appendix A | L648!       | 53 and L64853A Differences                                          |             |

|            | <b>A.</b> 1 | Line Buffers                                                        | <b>A-</b> 1 |

|            | A.2         | Pin Changes                                                         | A-1         |

|            | A.3         | Internal Register Changes                                           | A-1         |

| Appendix B | Custo       | omer Feedback                                                       |             |

| Figures    | 1.1         | L64853A Internal Block Diagram                                      | 1-2         |

|            | 2.1         | DMA Control/Status Register (CSR)                                   | 2-2         |

|            | 2.2         | DMA Address Counter and Next Address Registers                      | 2-6         |

|            | 2.3         | DMA Byte and Next Byte Counters                                     | 2-7         |

|            | 2.4         | L64853A Register Read/Write Cycles                                  | 2-10        |

|            | 3.1         | SBus DMA Burst Read                                                 | 3-2         |

|            | 3.2         | L64853A Block Diagram                                               | 3-3         |

|            | 3.3         | Cache Line Configuration                                            | 3-4         |

|            | 4.1         | DMA Read with FASTER = $x$ , $\overline{SLOW} = 0$                  | 4-8         |

|            | 4.2         | DMA Read with FASTER = $0$ , $\overline{SLOW} = 1$                  | 4-8         |

|            | 4.3         | DMA Read with FASTER = 1, $\overline{\text{SLOW}}$ = 1              | 4-8         |

|            | 4.4         | DMA Write with FASTER = $x$ , $\overline{SLOW} = 0$                 | 4-10        |

|            | 4.5         | DMA Write with FASTER = $0$ , $\overline{SLOW} = 1$                 | 4-10        |

|            | 4.6         | DMA Write with FASTER = 1, $\overline{\text{SLOW}}$ = 1             | 4-10        |

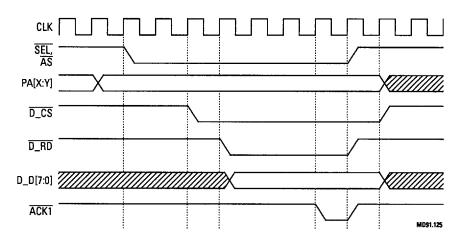

|            | 4.7         | Fast Mode D-Channel Register Read ( $\overline{\text{SLOW}} = 1$ )  | 4-11        |

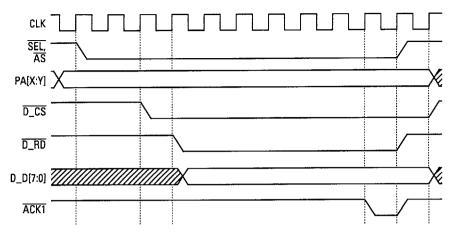

|            | 4.8         | Slow Mode D-Channel Register Read ( $\overline{\text{SLOW}} = 0$ )  | 4-12        |

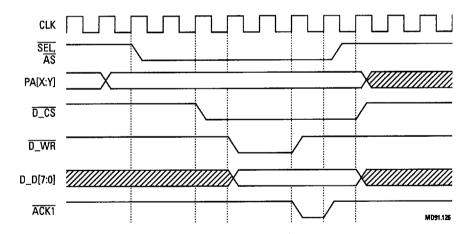

|            | 4.9         | Fast-Mode D-Channel Register Write ( $\overline{\text{SLOW}} = 1$ ) | 4-12        |

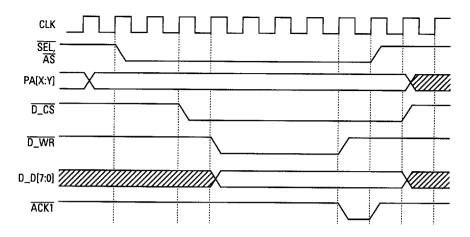

|            | 4.10        | Slow-Mode D-Channel Register Write ( $\overline{\text{SLOW}} = 0$ ) | 4-13        |

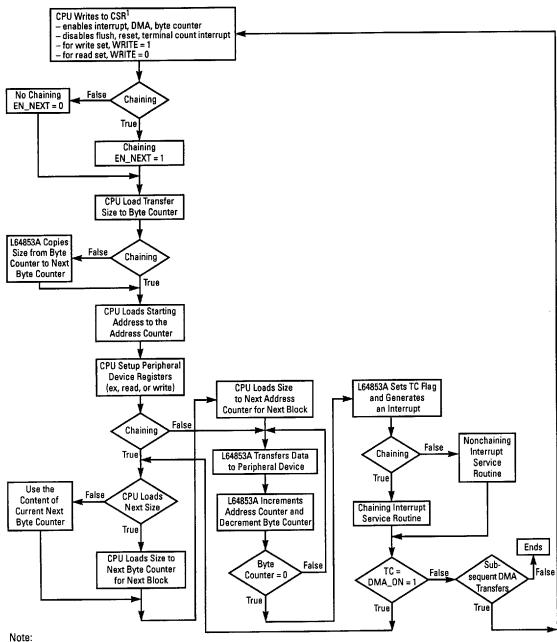

|            | 4.11        | Flow of DMA Transfers on the D Channel                              | 4-18        |

|            | 5.1         | E-Channel DMA Read with Cache Hit                                   | 5-7         |

|            | 5.2         | E-Channel DMA Write                                                 | 5-8         |

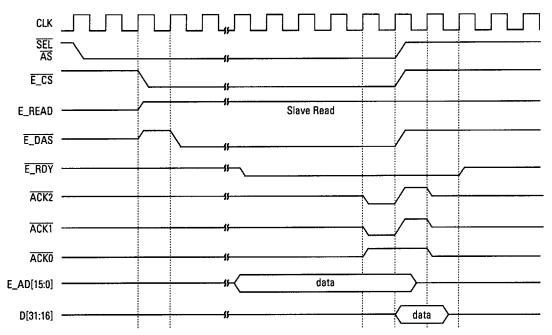

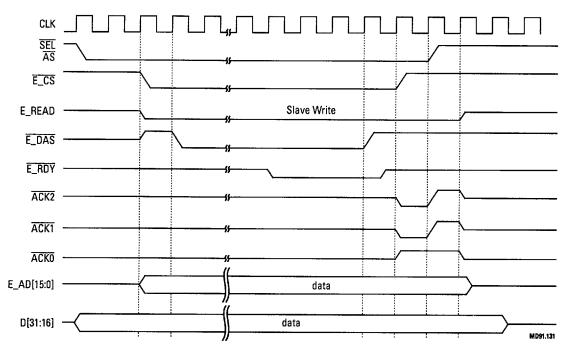

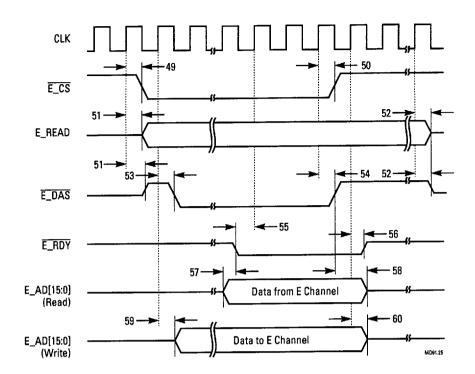

|            | 5.3         | E-Channel Register Read Cycle                                       | 5-10        |

|            | 5.4         | E-Channel Register Write Cycle                                      | 5-11        |

|            | 6.1         | L64853A Logic Symbol                                                | 6-1         |

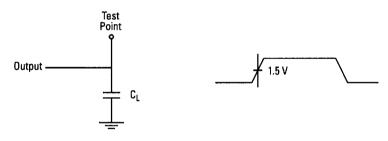

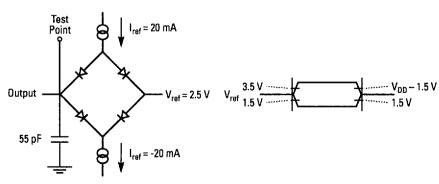

|            | 7.1         | AC Test Load and Waveform for Standard Outputs                      | 7-1         |

|            | 7.2         | AC Test Load and Waveform for 3-State Outputs                       | 7-1         |

|            | 7.3         | SBus Input Signals                                                  | 7-5         |

Contents ix

|        | 7.4         | SBus Output Signals                            | 7-5         |

|--------|-------------|------------------------------------------------|-------------|

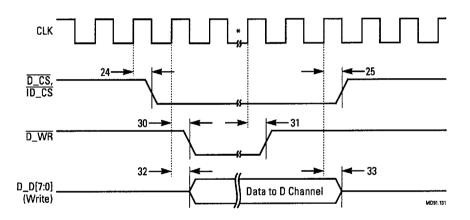

|        | 7.5         | D-Channel Register Read Timing                 | 7-6         |

|        | 7.6         | D-Channel Register Write Timing                | 7-6         |

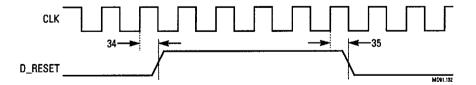

|        | 7.7         | D-Channel Reset Timing                         | 7-6         |

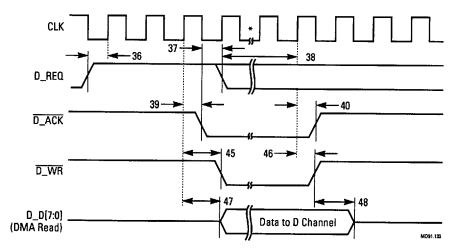

|        | 7.8         | D-Channel DMA Write Timing                     | 7-7         |

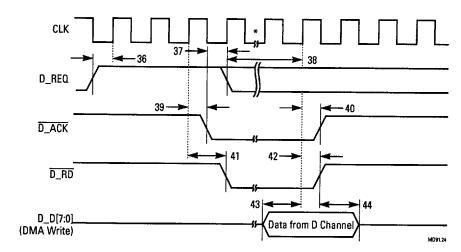

|        | 7.9         | D-Channel DMA Read Timing                      | 7-7         |

|        | 7.10        | E-Channel Register Access Timing               | 7-8         |

|        | 7.11        | E-Channel DMA Cycle Timing                     | 7-9         |

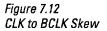

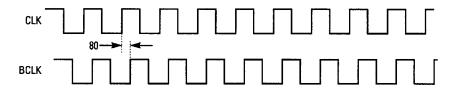

|        | 7.12        | CLK to BCLK Skew                               | 7-9         |

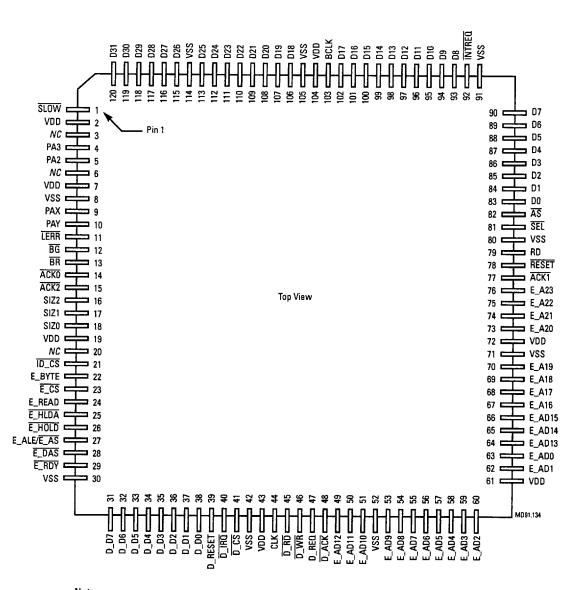

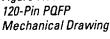

|        | 7.13        | 120-Pin PQFP Pinout Diagram                    | 7-15        |

|        | 7.14        | 120-Pin PQFP Mechanical Drawing                | 7-16        |

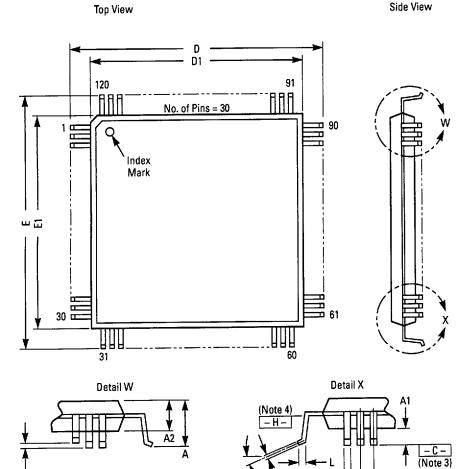

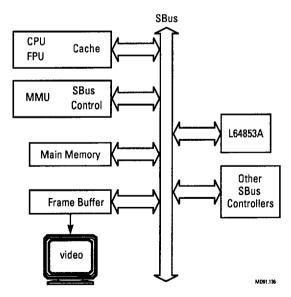

|        | 8.1         | Host-Based System: SPARCstation 1              | 8-2         |

|        | 8.2         | Symmetric Configuration                        | 8-2         |

|        | 8.3         | L64853A to ESP-100 Interface                   | 8-3         |

|        | 8.4         | ESP Interface Example Using External Boot PROM | 8-4         |

|        | 8.5         | L64853A to Am7990 LANCE Interface              | 8-5         |

| Tables | 2.1         | Accesses by Register Type                      | 2-9         |

|        | 2.2         | Internal Programmable Registers                | 2-9         |

|        | 4.1         | DMA Read Operation Settings                    | 4-7         |

|        | 4.2         | DMA Write Operation Settings                   | 4-9         |

|        | 7.1         | AC Characteristics                             | 7-2         |

|        | 7.2         | Absolute Maximum Ratings                       | 7-10        |

|        | 7.3         | Recommended Operating Conditions               | 7-10        |

|        | 7.4         | Capacitance                                    | 7-10        |

|        | 7.5         | DC Characteristics                             | 7-11        |

|        | 7.6         | Alphabetical Pin Description Summary           | 7-12        |

|        | 7.7         | L64853A Ordering Information                   | 7-13        |

|        | 7.8         | Alphabetical Pin List for the 120-Pin PQFP     | 7-14        |

|        | 8.1         | Selecting External Registers on ESP SCSI Chip  | 8-4         |

|        | 8.2         | Addressing Registers on LANCE                  | 8-6         |

|        | <b>A</b> .1 | Pin Differences                                | <b>A-</b> 1 |

|        | A.2         | CSR Differences                                | A-2         |

# Chapter 1 Introduction

This chapter describes the basic capabilities and operation of the L64853A Enhanced SBus DMA Controller. This chapter is particularly important for system-level programmers and hardware designers.

#### 1.1 General Description

The L64853A Enhanced SBus DMA Controller provides a complete SBus interface for SBus peripheral subsystems. The L64853A, implemented in a 1.5-micron CMOS process and manufactured by LSI Logic Corporation, is packaged in an inexpensive, 120-pin, plastic quad flat package (PQFP).

The L64853A contains two independent DMA channels, a 16-bit channel and an 8-bit channel. The two channels support DMA for use in applications that require operation as an SBus Master. Such applications include:

- Ethernet controllers

- Eight-bit controllers

The L64853A's two channels can also be used for applications that rely on programmed I/O and thus use only the L64853A's SBus slave capability. These applications include:

- Serial ports

- Analog-to-Digital converters

The 8-bit channel is called the *D channel*, and the 16-bit channel is called the *E channel*. The L64853A generates, upon request from a device attached to either channel, sequences of SBus data transfers (that is, reads or writes) between the peripheral controller and main memory. To perform this function, the L64853A can become an SBus Master through the use of the SBus Request and Grant signals. In SBus terminology, the L64853A is a *Direct Virtual Memory Access (DVMA) Master*, that is, it generates virtual addresses on the SBus data lines and employs the SBus controller's Memory Management Unit (MMU) to translate these virtual addresses

into physical addresses. (See *The SBus Specification* from Sun Microsystems for more details.)

The L64853A is programmable. Programs running on the system CPU may set parameters that both govern the transfers to and from the peripheral controllers performed by the L64853A and also read the current status of the chip. Software writes and reads the internal registers on the L64853A and also on the two peripheral controllers. To permit this writing and reading, the L64853A becomes an *SBus Slave* when the CPU asserts the Slave Select signal specific to the L64853A. While the L64853A acts as an SBus Slave, the CPU can use the L64853A as a conduit to the two peripheral controller chips, thus allowing the CPU to program them.

#### Architecture

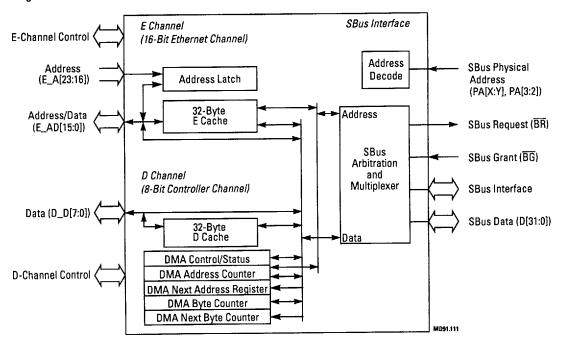

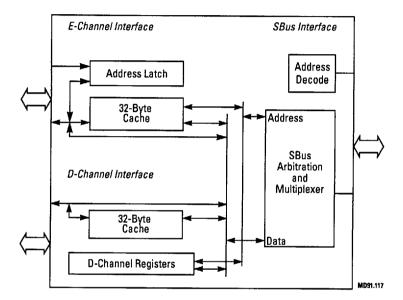

The principal components of the L64853A are its two functionally distinct DMA channels and its SBus interface with associated bus arbitration logic. Figure 1.1 shows the chip's internal architecture. Refer to Chapter 6 for a detailed description of the L64853A DMA Controller's signals.

Figure 1.1 L64853A Internal Block Diagram

The *E Channel* (16-bit Ethernet Channel) has the following functional blocks:

- An Address Latch temporarily stores memory addresses from the E-channel controller

- A 32-byte *E Cache* buffers data between the 16-bit interface and the SBus

The *D Channel* (eight-bit I/O Controller Channel) has the following functional blocks:

- A 32-byte *D Cache* buffers data between the 8-bit interface and the SBus

- A Control/Status Register contains programmable parameters and status fields

- An Address Counter Register holds the memory address of the next byte the D channel accesses

- A Next Address Register holds the memory address for the next data block transfer on the SBus

- A Byte Counter Register counts down the number of bytes transferred during a transfer of a block of data

- A Next Byte Counter Register holds the number of bytes to be transferred during the next data block transfer

#### Channel Operations

When the L64853A is an SBus Master, it performs high-speed data transfers between peripheral controllers and main memory. When the L64853A is an SBus Slave, a Bus Master performs register reads and writes to the L64853A, and also performs register reads and writes to the D-channel and E-channel controllers through the L64853A. All channel operations are ultimately governed by the SPARC environment in which the L64853A is implemented.

Chapter 3 describes the features of the L64853A common to both the D and E channels. Chapters 4 and 5 provide detailed information on the D and E channels, respectively.

1-3

#### 1.2 Key Features

This section summarizes the key features of the L64853A. These features are described in more detail in subsequent chapters.

- Operates at speeds up to 25 MHz

- Performs DMA transfers, assuming an SBus latency of up to 40 clock cycles, at a maximum 8.3 Mbytes/second at 25 MHz for both the D and E channels

- Supports 8- or 16-bit peripherals

- Packs/unpacks SBus words into bytes or halfwords for use by the peripheral controllers

- Supports for byte, halfword, word, or four-word burst transfers on the SBus

- Operates in virtual address space with the SPARC MMU providing virtual-to-physical address translations

- Supports rerun acknowledgments

- Includes 24-bit address and data counters

- Uses a single clock input

- Performs data block chaining on the D-channel interface

- Packaged in a low-cost, 120-pin plastic quad flat package

### 1.3 Enhancements

The L64853A Enhanced SBus DMA Controller is an enhanced version of the L64853 SBus DMA Controller. The features added to the L64853A are:

- Larger internal data buffer to support four-word data burst transfers.

- Two additional D-channel registers (Next Address Register and Next Byte Counter) that allow data transfer setups to be pipelined, thus reducing the overhead between data transfers.

- Programmable E\_ALE/E\_AS pin on the E channel for compatibility with various 16-bit controllers.

- FASTER option that increases the speed of D-channel read and write operations.

# **Chapter 2 Registers**

This chapter discusses the L64853A's registers and tells how to access both internal and external registers. This chapter is intended primarily for system programmers.

The L64853A has two types of internal registers:

■ Programmable registers

The L64853A's five *programmable registers* control the operation of the chip and contain status information.

ID Register

The *ID Register* is pre-programmed with a unique, read-only value for the L64853A chip.

The following sections discuss the programmable and ID registers in more detail. Chapter 3 provides additional details about the fields and bits in these registers while the D and E channels are operating.

#### 2.1 Internal Programmable Registers

This section describes the five programmable L64853A registers:

- DMA Control/Status Register (CSR)

- DMA Address Counter and Next Address Registers

- DMA Byte and Next Byte Counters

The DMA Control/Status Register (CSR) contains control and status information for both the D and E channels. The remaining programmable registers control only the D channel and the SBus. The E channel is controlled entirely by external registers on the E-channel peripheral controller itself.

The following subsections define the fields within the L64853A registers in detail. In these definitions, the set state = 1 and the clear state = 0. This convention applies to all bits in the L64853A internal registers.

DMA Control/ Status Register (CSR) The 32-bit Control/Status Register (shown in Figure 2.1 below) controls the operation of the D channel and reports the status of the D and E channels. The following description provides the functions of the individual fields in the CSR.

Figure 2.1 DMA Control/Status Register (CSR)

| Bit | 31       | 28 | 27         | 26       | 25         | 24      | 23    |               | 22     | 21           | 20      | 19           | 16           |

|-----|----------|----|------------|----------|------------|---------|-------|---------------|--------|--------------|---------|--------------|--------------|

|     | DEV_II   | )  | NA_LOADED  | A_LOADED | DMA_ON     | EN_NEXT | TC1_D | IS FAS        | STER L | ANCE_<br>ERR | ALE/AS  | Unu          | sed          |

| Bit | 15       | 14 | 13         | 12 10    | 9          | 8       | 7     | 6             | 5      | 4            | 3 2     | 1            | 0            |

|     | Reserved | TC | EN_<br>CNT | Unused   | EN_<br>DMA | WRITE   | RESET | SLAVE_<br>ERR | FLUSH  | INT_EN       | DRAININ | ERR_<br>PEND | INT_<br>PEND |

#### INT\_PEND

#### Interrupt Pending (Read Only)

0

The L64853A automatically sets INT\_PEND to indicate a pending interrupt. Asserting  $\overline{D_{-}IRQ}$  or setting TC (when not disabled by TCI\_DIS) sets INT\_PEND. If no interrupts are pending, this bit is clear.

#### ERR\_PEND

#### Error Pending (Read Only)

1

ERR\_PEND is set when an error condition occurs during a D-channel memory access (for example, a parity error, protection violation, or time-out). Setting ERR\_PEND causes an interrupt (INTREQ asserted) if INT\_EN is set. DMA transfers are stopped when ERR\_PEND is asserted. ERR\_PEND is reset when either the FLUSH bit is set, the RESET bit is set, or RESET is asserted.

#### DRAINING

#### Draining (Read Only)

[3:2]

Dirty data are data in the D cache that are pending a write to the SBus. Draining is the process of writing the dirty data to the SBus. If one of the D channel's cache lines is draining dirty data, the DRAINING bits (bits [3:2]) read as 11<sub>2</sub>. While these bits are ones, do not set the RESET or FLUSH bits or write to the DMA Address Counter Register. The DRAINING bits are not valid while ERR\_PEND is set or during D-channel read operations and should be ignored. Note that these two bits are backward-compatible with the PACK\_CNT bits, which occupy the same bit positions in the L64853 CSR.

#### INT\_EN Interrupt Enable (Read/Write)

When set, INT\_EN enables the SBus INTREQ signal when INT\_PEND or ERR\_PEND is set.

#### FLUSH Flush Buffer (Write Only)

Setting FLUSH marks all bytes in the D-channel cache as invalid and resets ERR\_PEND and TC. If EN\_NEXT = 1, A\_LOADED and NA\_LOADED are also reset. Note that the FLUSH bit also resets itself, hence it always reads as zero. Note also that software should never set this bit while the EN\_DMA or DRAINING bits are set.

#### SLAVE\_ERR Slave Error (Read/Write)

The L64853A sets the SLAVE\_ERR bit when an SBus Master tries to access the L64853A with an unsupported SBus size. In this situation, the L64853A responds with an SBus Error Acknowledgement and sets this bit. Write a one to this bit to reset it.

#### RESET Reset DMA (Read/Write)

When set, RESET acts as a hardware reset. The L64853A is initialized into the following state: ERR\_PEND, INT\_EN, FLUSH, EN\_NEXT, DRAINING, SLAVE\_ERR, WRITE, EN\_DMA, EN\_CNT, TC, DMA\_ON, and FASTER are set to zero, and RESET is set to one. All valid/dirty bits in the cache are cleared. An SBus reset (RESET = 0) sets all CSR bits to zero except for the DEV\_ID field. The D\_RESET signal remains asserted for as long as the RESET bit of the CSR or the RESET signal is active. Note that software should never set this bit while the EN\_DMA or DRAINING bits are set.

#### WRITE Memory Read/Write (Read/Write)

WRITE determines the direction of the D-channel DMA transfer. When HIGH, the flow is to memory (memory write); when LOW, the flow is from memory (memory read).

#### EN\_DMA Enable DMA (Read/Write)

When set, EN\_DMA allows the L64853A to respond to DMA requests by the D-channel controller, as long as DMA activity is not stopped due to an interrupt, etc. When this bit is one, do not set the RESET or FLUSH bits or write to the DMA Address Counter Register. See the description of the DMA\_ON bit for more information.

4

5

6

7

8

9

#### Not Used (Read Only) Unused

[19:16], [12:10]

These bits are unused; they always read as zeros.

#### EN CNT Enable Counter (Read/Write)

13

As long as EN\_CNT is set, the internal Byte Counter is enabled. The Byte Counter decrements on byte transfers between the D channel and the L64853A. The set state also enables the operation of the TC bit. EN\_CNT and EN\_NEXT control the operating modes of the D-channel programmable registers. Refer to the table in the EN NEXT description on page 2-5 for these modes.

#### TC Terminal Count (Read Only)

14

When set, TC indicates that the Byte Counter has expired. That is, TC is set when a byte count makes a transition from 0x00.0001 to 0x00.0000. When the L64853A sets the TC bit, an interrupt is generated on the INTREQ pin, as long as interrupts are enabled by INT\_EN and not disabled by TCI\_DIS. Also, if the operation was a DMA write, the L64853A queues all dirty bytes in the cache for draining. When  $EN_NEXT = 0$ , TC is cleared only by the FLUSH bit, the RESET bit, or the RESET pin. When EN\_NEXT = 1, TC can also be cleared by writing a one to it.

#### Reserved

#### Reserved (Read/Write)

15

20

Bit 15 is reserved for future enhancements. For correct operation, always write a zero to this bit.

#### ALE/AS

Address Latch Enable/Address Strobe (Read/Write)

$ALE/\overline{AS}$  defines pin 27 as either ALE (active HIGH signal) or  $\overline{AS}$  (active LOW signal). If this bit = 1, pin 27 is ALE. If this bit = 0, pin 27 is  $\overline{AS}$ . The default value for this bit is zero.

#### LANCE\_ERR LANCE Error (Read Only)

21

LANCE ERR is set when a memory error occurs on a transfer to or from the E channel. The L64853A does not generate an interrupt in response to LANCE\_ERR being set. The L64853A does not respond to any subsequent E-channel transfers until LANCE ERR is cleared. A slave write to the E channel clears this bit.

#### Fast Speed (Read/Write) **FASTER**

22

The FASTER bit is set when a faster access time is required for the D channel. Refer to the timing diagrams in Section 4.5, "Read/Write Transactions," for specific details.

#### TCI\_DIS TC Interrupt Disable (Read/Write)

When TCI\_DIS is set, interrupts and auto-draining are disabled from TC. The default value for this bit is zero.

#### **EN\_NEXT** Enable Next (Read/Write)

24

23

As long as EN\_NEXT is set, the next address auto-load mechanism is enabled. The default value for this bit is zero. EN\_NEXT and EN\_CNT control the operating modes of the DMA Address Counter Register, Next Address Register, Byte Counter, and Next Byte Counter as shown in the following table.

#### EN\_CNT EN\_NEXT Mode

| 0 | x <sup>1</sup> | Backward-compatible with the L64853                                                                                                                                                                         |

|---|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | 0              | Backward-compatible with the L64853 using the Byte Counter. FLUSH clears the TC flag.                                                                                                                       |

| 1 | 1              | Next Address and Next Byte Count values loaded into the Address Counter and Byte Counter Registers on byte count expiration. DMA stops on byte count expiration if the Next Address Register is not loaded. |

1. x = don't care.

#### DMA\_ON DMA On (Read Only)

25

When DMA\_ON is set, the L64853A responds to DMA requests from the D channel. This bit reads as one when ((A\_LOADED OR NA\_LOADED) & EN\_DMA & NOT ERR\_PEND) is true. When this bit is clear, the L64853A ignores DMA requests from the D channel.

#### A\_LOADED Address Loaded (Read Only)

26

When either software writes to the Address Counter Register or the L64853A copies the contents of the Next Address Register into the Address Counter Register, the A\_LOADED bit is set. This bit is cleared by RESET assertion or Byte Counter expiration. A\_LOADED is also reset by FLUSH when EN\_NEXT = 1.

#### NA\_LOADED Next Address Loaded (Read Only)

27

Writing to the Next Address Register while EN\_NEXT = 1 sets NA\_LOADED. This bit is cleared when RESET is set, EN\_NEXT is cleared, EN\_CNT is cleared, or when the Next Address Register is copied to the Address Counter Register. The latter case occurs when both NA\_LOADED = 1 and A\_LOADED = 0. NA\_LOADED is also reset by FLUSH when EN\_NEXT = 1.

DEV\_ID Device ID (Read Only)

For the current implementation, this field is set to 1001<sub>2</sub>.

[31:28]

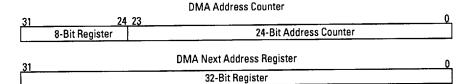

DMA Address Counter and Next Address Registers The DMA Address Counter Register and the DMA Next Address Register, shown in Figure 2.2, contain the virtual addresses for the current and next memory transfers, respectively. The Next Address Register is a 32-bit register. The Address Counter Register is divided into a 24-bit counter and an 8-bit register.

Figure 2.2 DMA Address Counter and Next Address Registers

The eight-bit register in the Address Counter Register contains the high-order byte of the virtual address; the upper eight bits are fixed since DMA transfers are limited to 16 Mbytes. The 24-bit counter contains the lower three bytes of the virtual address. The Address Counter Register always points to the next byte to be accessed by the D-channel controller, independent of which bytes in memory have been accessed by the L64853A.

The Next Address Register, in conjunction with the Next Byte Counter Register, allows data transfer setups to be pipelined, thus reducing the amount of overhead between block transfers. The virtual address for the next data transfer is preloaded into the Next Address Register. When NA\_LOADED = 1 and A\_LOADED = 0, the L64853A automatically copies the contents of the Next Address Register into the Address Counter Register.

If data block chaining is enabled (EN\_NEXT = 1), both the Address Counter Register and the Next Address Register are used in the DMA operation. If data block chaining is disabled (EN\_NEXT = 0), only the Address Counter Register is used.

After a RESET, the Address Counter Register and Next Address Register both contain indeterminate values.

Note that software should never write to the Address Counter Register while the EN\_DMA or DRAINING bits are set. If the Address Counter

Register is written to, the L64853A marks all bytes in the D cache as invalid.

See Section 4.2, "Register Operation," for more information on the DMA Address Counter Register and the DMA Next Address Register.

#### DMA Byte and Next Byte Counters

The Byte Counter and the Next Byte Counter are 32-bit registers that hold the number of bytes in a D-channel DMA transfer. The Byte Counter contains the byte count for the current memory transfer. The Next Byte Counter contains the byte count for the next memory transfer. These registers are shown in Figure 2.3.

Figure 2.3 DMA Byte and Next Byte Counters

| 31 |          | 24 23 | DMA Byte Counter      | 0          |

|----|----------|-------|-----------------------|------------|

|    | 00000000 |       | Byte Count            |            |

| 31 |          | 24 23 | DMA Next Byte Counter | 0          |

|    | 00000000 |       | Next Byte Count       | · <u> </u> |

The upper byte of these registers always reads as zero. If data block chaining is enabled (EN\_NEXT = 1), both the Byte Counter and the Next Byte Counter are used during DMA transfers (provided that EN\_CNT = 1). If data block chaining is disabled (EN\_NEXT = 0), only the Byte Counter is used.

Loading the Byte Counter with 0 allows the transfer of  $2^{24}$  bytes (16 Mbytes) before it expires.

The Next Byte Counter Register, in conjunction with the Next Address Register, allows data transfer setups to be pipelined, thus reducing the amount of overhead between block transfers.

After a RESET, the Byte Counter and Next Byte Counter both contain indeterminate values.

See Section 4.2, "Register Operation," for more information on these registers.

#### 2.2 Internal and External ID Registers

The SBus DMA contains a 32-bit internal identification (ID) register and a facility for accessing an external ID register or PROM. The external ID register or PROM supports the automatic configuration feature of *The SBus Specification*. Upon power-up, the CPU reads certain memory locations or slots to determine the system configuration. When the CPU

accesses the L64853A slot with physical address 0, the DMA controller either outputs the value in the internal ID register or begins an access similar to a slave access to the D channel to read the external ID register or PROM. The access uses  $\overline{\text{ID}\_\text{CS}}$  as the chip select instead of  $\overline{\text{D}\_\text{CS}}$ .

The L64853A determines whether to use an internal or external ID by the state of the  $\overline{\text{ID}\_\text{CS}}$  signal. If the bidirectional  $\overline{\text{ID}\_\text{CS}}$  signal is tied LOW, then the DMA controller uses the internal ID register value. If  $\overline{\text{ID}\_\text{CS}}$  is pulled HIGH through a 4.7-k $\Omega$  resistor, then the L64853A uses an external ID register or PROM. The  $\overline{\text{ID}\_\text{CS}}$  pin then becomes a chip select output. The L64853A pulls the  $\overline{\text{ID}\_\text{CS}}$  pin LOW to indicate an external ID access.

The L64853A internal ID register is hardwired to 0xFE81.0102. The internal ID register should be used mainly for system testing purposes. Actual system implementations should use an external ID register or PROM to avoid ID conflicts with multiple DMA devices on a single system. The information programmed in the ID PROM can range from a manufacturer's name and model number to a device driver. Note that if a slot does not respond with that information during the ID access, that slot is subsequently ignored.

#### 2.3 Addressing Internal and External Registers

Any SBus peripheral device that is built using the L64853A contains two types of configuration and control registers: the internal L64853A registers, described in Section 2.1, and the external registers in the peripheral controllers that are attached to the L64853A's two channels. Examples of external registers are listed in Chapter 8.

The implementation of the SBus controller and the way that the hardware designer connects the physical address signals determine the system addresses that specify the internal or external registers.

With regard to the SBus controller implementation, the SBus uses a geographical addressing scheme that assigns ranges of addresses to each SBus connector. When the SBus controller detects access to a particular range, it asserts the SEL signal dedicated to the related connector.

When the SBus controller asserts the L64853A's  $\overline{SEL}$  input, the L64853A uses four address inputs to further decode the address present on SBus signals PA[27:0]: PA[X:Y] and PA[3:2]. The PA[X:Y] signals are connected to two of the SBus's 28 physical address lines, PA[27:0]; for example on the L64853A in the SPARCstation 2, PA[X:Y] = PA[23:22]. The L64853A

uses PA[X:Y] to select the category of registers for access according to Table 2.1. The size of the data item that must be transferred over the SBus, specified by SIZ[2:0], is also shown for each category of register.

Table 2.1 Accesses by Register Type

| PA[X:Y] | Addressed Register Type                                                       | Size                                            |

|---------|-------------------------------------------------------------------------------|-------------------------------------------------|

| 0 0     | Internal ID Register (or external if $\overline{ID}_{\overline{CS}} = HIGH$ ) | Byte, Halfword <sup>1</sup> , Word <sup>1</sup> |

| 0 1     | Internal Programmable Registers                                               | Word                                            |

| 1 0     | D-channel Registers (External)                                                | Byte, Halfword <sup>1</sup> , Word <sup>1</sup> |

| 11      | E-channel Registers (External)                                                | Halfword, Word <sup>1</sup>                     |

<sup>1.</sup> Allowed due to SBus bus-sizing protocol.

Table 2.2 lists the addresses of the programmable registers. These registers are selected when  $PA[X:Y] = 01_2$ ,  $\overline{SEL} = \overline{AS} = 0$ .

Table 2.2 Internal Programmable Registers

| PA[3:2] | EN_NEXT <sup>1</sup> | A_LOADEI | O <sup>1</sup> Type | Register                              |

|---------|----------------------|----------|---------------------|---------------------------------------|

| 0 0     | x                    | х        | R/W                 | Control/Status Register (CSR)         |

| 0 1     | 0                    | x        | R/W                 | Address Counter Register              |

| 0 1     | 1                    | 0        | R/W                 | Address Counter Register              |

| 0 1     | 1                    | 1        | R                   | Address Counter Register              |

| 0 1     | 1                    | 1        | $\mathbf{w}$        | Next Address Register                 |

| 10      | 0                    | x        | R/W                 | Byte Count Register <sup>2</sup>      |

| 10      | 1                    | 0        | R/W                 | Byte Count Register <sup>2</sup>      |

| 1 0     | 1                    | 1        | R                   | Byte Count Register <sup>2</sup>      |

| 10      | 1                    | 1        | W                   | Next Byte Count Register <sup>2</sup> |

| 1 1     | X                    | x        | R                   | Reserved for Testing                  |

<sup>1.</sup> EN\_NEXT and A\_LOADED are bits within the CSR.

Other physical address lines are wired directly to the two peripheral controllers and are used in an implementation-dependent manner to select specific registers on these two chips.

<sup>2.</sup> The Byte Counter Registers are used only when the EN\_CNT bit in the Control/ Status Register equals 1.

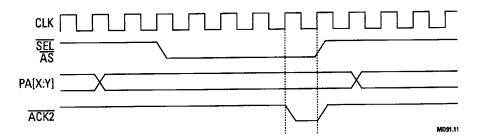

#### 2.4 Internal Register Reads and Writes

The accessible registers in the L64853A include the Control/Status Register, Address Counter Register, and Byte Counter. The Next Address Register and the Next Byte Counter are write-only registers. The following steps describe how to read or write one of these internal L64853A registers:

- 1. The CPU executes a LOAD or STORE instruction and asserts the L64853A's Slave Select signal (SEL). The physical address is also driven onto PA[27:0] at this time along with RD, SIZ[2:0], and AS.

- 2. Because the L64853A recognizes that the read or write access is intended for itself (SEL is asserted), the L64853A interprets the two-bit value (00<sub>2</sub> or 01<sub>2</sub>) on the physical address lines PA[X:Y]. This two-bit value indicates that an internal L64853A register is the target of the read or write. Refer to Table 2.2 for the assignment of physical addresses to L64853A internal registers.

- 3. If the target register is internal to the L64853A, the data are either read from the intended register to the data lines D[31:0] or written from the data lines to the intended register.

- 4. Finally, the L64853A asserts ACK2 to inform the SBus controller that the slave-mode operation is complete.

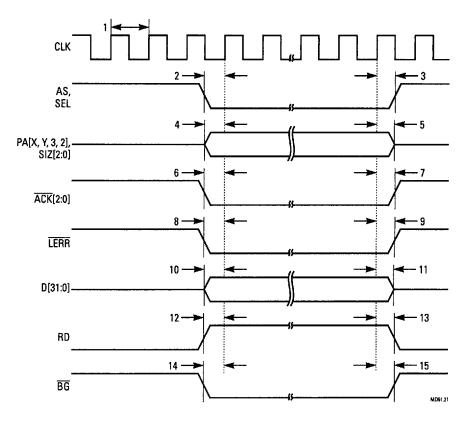

Figure 2.4 illustrates both a register read and a register write operation for the L64853A. See *The SBus Specification* for further details on SBus signals not shown here.

Figure 2.4 L64853A Register Read/Write Cycles

# **Chapter 3 L64853A Operation**

This chapter describes the operational modes of the L64853A and the internal cache organization. These descriptions apply to both the D and E channels. Details specific to the individual channels are provided in Chapter 4, "D-Channel Operation," and Chapter 5, "E-Channel Operation."

### 3.1 Modes of Operation

The L64853A supports two basic modes of operation: Master and Slave. The basic operations of both the D and E channels are DMA Reads and Writes, executed when the L64853A is in Master mode, and Register Reads and Writes, executed when the L64853A is an SBus Slave.

DMA transfers are accomplished by the coordinated activity of all chips in the system: the peripheral controller, the L64853A, the CPU, the SBus controller, and the memory controller.

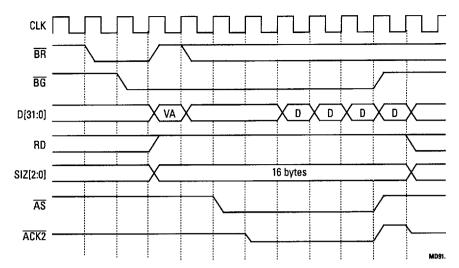

#### Master Mode

In Master mode, the L64853A is an SBus DVMA Master and performs DMA reads and writes. The L64853A generates virtual addresses on the SBus data lines. These addresses are translated into physical addresses by the SBus controller's MMU. Data is then transferred between the internal cache of the L64853A and either memory or another SBus Slave.

All DMA reads from memory are in four-word bursts (see Figure 3.1). DMA writes to memory can be any size: byte, halfword, word, or four-word burst. The L64853A SBus interface always uses the largest size possible when writing to memory. The largest possible size is determined by the total number of bytes written to the internal cache by the I/O device. Note that because the L64853A uses four-word bursts, the slave device that it is accessing must also support four-word bursts.

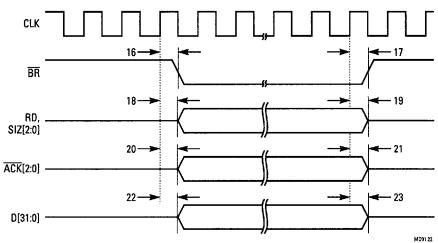

Figure 3.1 SBus DMA Burst Read

The L64853A SBus interface supports rerun acknowledgments from slaves. The requested DMA transfer repeats until either it completes or an error indicator, for example,  $\overline{ACKO}$ , is received, whereupon the transfer aborts. When the L64853A receives a rerun acknowledgment, it deasserts  $\overline{BR}$  for one clock to give the CPU and other DMA Masters a chance to win SBus arbitration. The L64853A then reasserts  $\overline{BR}$  to retry the cycle. After the L64853A asserts  $\overline{BR}$ , it does not deassert it until  $\overline{BG}$  or  $\overline{RESET}$  is asserted.

#### Slave Mode

In Slave mode, the CPU is the SBus Master, and it performs register reads and writes of the L64853A as an SBus Slave. The SBus physical address lines access the L64853A's internal registers and those of the two peripheral controllers, using a register addressing scheme that is implementation-dependent. The L64853A's internal cache is bypassed in the Slave mode.

If the SBus Master attempts a slave access to the D or E channel while the channel is currently active with a DMA transfer to/from the L64853A, the L64853A forces the Master to rerun the slave access. This rerun acknowledgment ensures that a deadlock does not occur between the peripheral controllers and the SBus Master.

The L64853A allows the SBus Master to access internal L64853A registers while the L64853A is active with a DMA transfer to/from one of the peripheral controllers.

### 3.2 Internal Cache Memory

This section discusses the L64853A's internal cache configuration. The internal cache is used only during DMA transfers. The D and E channels each include a 32-byte cache memory, as shown in Figure 3.2. The caches are the data buffers between the SBus and the peripheral controllers. Data are packed or unpacked in the appropriate cache memory. Packing and unpacking the data in the cache allows for a four-word burst and reduces the impact on the SBus bandwidth.

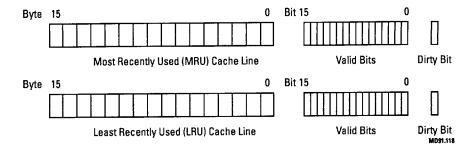

Figure 3.2 L64853A Block Diagram

Each cache is divided into two lines of 16 bytes (four words) each. The cache lines are referred to as Most Recently Used (MRU) and Least Recently Used (LRU), depending on when each line was last accessed, where an access is either a read or a write. The line most recently accessed by the peripheral controller is marked as MRU, and the other as LRU. Once the last byte of the MRU cache line is accessed (the least significant address bits of the last byte = 0xF), that cache line is then marked LRU and the other cache line is marked as MRU.

Each 16-byte cache line has a dirty bit and 16 valid bits associated with it, where each valid bit corresponds to a byte in the cache line. When set, the valid bit indicates that its corresponding byte contains valid data for a memory read or write. The dirty bit refers to the entire cache line. When set, the dirty bit indicates that the cache line contains data for a memory

write. When the dirty bit is reset, the cache line does not contain data for a write. Figure 3.3 illustrates the cache lines with their associated bits.

Figure 3.3 Cache Line Configuration

#### Memory Reads

For memory reads, a cache miss occurs when the data requested by the peripheral device are not in the cache line. When a cache miss occurs, the L64853A loads the cache with a four-word burst from memory. The data from the four-word aligned, four-word burst are loaded into the LRU cache line. As each byte is read into the cache, the L64853A sets the byte's corresponding valid bit. When the data are transferred to the peripheral device, the valid bit for the corresponding byte or bytes is cleared. Once the valid bit is cleared, data at that particular cache address cannot be read again. This step ensures consistency between the internal cache and memory.

The L64853A performs read-ahead operations in order to maximize the number of cache hits. Read-ahead operations fill an entire cache line with a line from memory. These operations occur when the least significant address bits of the requested data are  $0100_2$  for a D-channel read and  $0110_2$  for an E-channel read. Refer to Section 4.3, "D-Channel Cache Operation," and Section 5.2, "E-Channel Cache Operation," for more details on read-ahead operations.

### **Memory Writes**

For memory writes, the peripheral device first writes the data to the cache. Writing the first byte to the cache sets the dirty bit for that cache line. The valid bit that corresponds to each byte written to the cache is also set. The data are packed into the cache until either the line is full or another draining condition is met. The cache line is marked LRU, and the valid data in the line are scheduled for draining to memory. The other cache line is marked MRU, and transfers between the peripheral device and the L64853A can continue simultaneously with the SBus transfer.

## 5304804 0012301 250 MLLC

Draining conditions are different for the D and E channels. Refer to Section 4.3, "D-Channel Cache Operation," and Section 5.2, "E-Channel Cache Operation," for more information on draining in the D and E caches.

# Chapter 4 D-Channel Operation

Chapter 4 describes the organization and operation of the D channel, for both programmers and hardware designers. This chapter is divided into the following sections:

- General Description: This section presents the D channel in general terms.

- Register Operation: This section describes the register and counter operation during memory transfers between the D channel and the L64853A.

- D-Channel Cache Operation: This section explains the D-cache data transfer for both memory read and write operations.

- Memory Errors and Interrupts: This section discusses the detection and resolution of memory errors and interrupts.

- Read/Write Transactions: This section describes the signal sequences required for DMA and slave register read/write operations.

- Programming Notes: This section provides programming tips on data transfers and register operation.

#### 4.1 General Description

The D channel is an eight-bit DMA control channel. The L64853A D-channel interface supports DMA memory reads and writes (Master mode) and register read and write operations (Slave mode).

A DMA transfer from the D channel to memory consists of two separate transfers: one or more eight-bit transfers from the D channel to the D cache, then a byte, halfword, or word transfer from the D cache to memory. Similarly, a transfer from memory to the D channel consists of two transfers: a four-word burst from memory to the D cache, and one or more eight-bit transfers from the D cache to the D channel. Note that all memory reads are in four-word bursts.

The D channel contains a 32-byte cache (the D cache) and five programmable registers. The D cache holds data that are being transferred between the D channel and memory. See Section 3.2 for more information on the internal cache setup and Section 4.3 for D-cache specific information.

The five registers are the DMA Address Counter Register, DMA Next Address Register, DMA Byte Counter, DMA Next Byte Counter, and Control/Status Register (CSR). The Address Counter and Next Address Register contain the virtual addresses for the current and next memory transfers, respectively. The Byte Counter and Next Byte Counter contain the byte counts for the current and next memory transfers, respectively. The two Next registers are used exclusively in the data block chaining mode described in Section 4.2.

The CSR contains several programmable fields that configure the D-channel interface. The CSR also provides status information on the D and E channels.

### 4.2 Register Operation

This section describes the operation of the address and byte count registers during a memory transfer between the D channel and the L64853A. It discusses two modes of operation: with and without data block chaining. Data block chaining provides a method of pipelining data block setups, thereby reducing latency time between block transfers. Data block chaining is enabled by the EN\_NEXT bit in the CSR.

Note that the subsections below assume that the EN\_CNT bit in the CSR is set so that Byte Counter is enabled.

# Operation without Data Block Chaining

When data block chaining is disabled (EN\_NEXT = 0), the Address Counter Register and Byte Counter (if EN\_CNT = 1) are used in the DMA transfer. Before a DMA transfer begins, the byte count for the block transfer is loaded into the Byte Counter. The starting virtual address is loaded into the Address Counter.

Each time a byte is transferred between the L64853A and the D channel, the byte count is decremented by one and the address is incremented by one. The Byte Counter expires (changes from 0x00.0001 to 0x00.0000) upon completion of the block transfer. When the Byte Counter expires, the L64853A sets the Terminal Count (TC) bit in the CSR.

When the first block transfer completes, the L64853A generates an interrupt. At this time, the Address Counter Register and Byte Counter can be loaded with the values for the next memory transfer.

#### Operation with Data Block Chaining

When data block chaining is enabled (EN\_NEXT = 1), the Address Counter Register, Next Address Register, Byte Counter, Next Byte Counter, and Control/Status Register are all used in the DMA transfer. By using the Next Address Register and the Next Byte Counter, the starting virtual address and data block size for an ensuing data transfer can be loaded while another transfer is occurring. This concurrence of operation reduces the amount of overhead between transfers.

The byte count for the block transfer is loaded into the Byte Counter. The L64853A automatically copies this byte count into the Next Byte Counter. The starting virtual address is written into the Address Counter Register, then each time a byte is transferred between the L64853A and the D channel, the byte count decrements by one and the address increments by one.

During the block transfer, the parameters for the next memory transfer can be set up. Software loads the Next Byte Counter with the byte count of the next block. (This step is optional if the byte count for the next block is the same as for the current block.) Software loads the Next Address Register with the starting address of the next block. When the Next Address Register is loaded, the L64853A sets the NA\_LOADED bit in the CSR.

The Byte Counter expires upon completion of the block transfer. At this time, the L64853A sets the TC bit and clears the A\_LOADED bit in the CSR. If TCI\_DIS is equal to 0, then the L64853A generates an interrupt when the TC bit is set. When A\_LOADED is cleared, the contents of the Next Address Register and Next Byte Counter are transferred to the Address Counter Register and Byte Counter, respectively. This transfer sets A\_LOADED and clears NA\_LOADED. The L64853A immediately services the next data block transfer.

If the Next Address Register is not loaded before the first block transfer completes, then DMA activity stops after the terminal count expires. The next data block transfer begins when an address is written into the Address Counter Register. As shown previously in Table 2.2, a write when EN\_NEXT = 1 and A\_LOADED = 0 loads the Address Counter Register and not the Next Address Register.

4-3

Refer to Section 4.6, "Programming Notes," for more information on handling the next block transfer.

#### 4.3 D-Channel Cache Operation

This section discusses how the L64853A handles data in the D cache for DMA read and write operations. The D cache resides between the D channel and the SBus interfaces. For memory reads, the L64853A loads data from memory into the D cache before transferring the data to the D channel. For memory writes, the L64853A loads data into the D cache from the D channel before transferring the data to memory. Slave accesses to the D channel bypass the D cache. Refer to Section 3.2, "Internal Cache Memory," for more details on the D cache.

#### Memory Reads

The D-channel controller initiates memory reads. On a memory read, the L64853A first checks for the data in the D cache, using the address loaded in the Address Counter Register. If the data requested by the D channel are not in the D cache or are marked as invalid, then a cache miss occurs. The Least Recently Used cache line is filled with a four-word burst from memory containing the requested data. The four words are aligned on a four-word boundary, and the word containing the requested data is the first one to be read from memory. The L64853A marks each byte it reads into the D cache as valid. As soon as the requested data are written to the D cache, the L64853A transfers the data to the D channel, even if the entire D-cache line has not yet been filled. As soon as the L64853A transfers a byte to the D channel, it marks the byte as invalid.

If the D channel requests data that are in the D cache and are marked as valid, then a cache hit occurs. The L64853A transfers the data to the D channel and marks the byte or bytes as invalid.

If the least significant address bits of the requested data are  $0100_2$ , the next four-word line in memory is on the same four-Kbyte page as the current cache line, and a cache hit occurs, then the L64853A performs a readahead operation. When a read-ahead occurs, the L64853A fills the cache line that does not contain the data requested by the D channel with the next line from memory. The read-ahead happens concurrently with the transfer of the requested data to the D channel.

If the least significant address bits of the requested data are  $0100_2$ , the next four-word line in memory is on the same four-Kbyte page as the current cache line, and a cache miss occurs, the L64853A performs two four-word

bursts. The first burst operation fulfills the cache miss and the second burst operation performs the read-ahead operation. The L64853A does not assert the  $\overline{D\_ACK}$  signal to acknowledge the D-channel request until the SBus burst transfer caused by the cache miss is complete.

Software can mark any data left in the cache after the read as invalid either by setting the FLUSH bit in the CSR or by writing a new address in the DMA Address Counter Register.

#### **Memory Writes**

DMA memory write operations write a byte or series of bytes from the D channel to the D cache. When the L64853A packs data into a cache line for a memory write, the L64853A sets the dirty bit for the cache line and marks each byte of data written into the cache line as valid. When the L64853A writes the last byte (byte 15) of that cache line, it queues the dirty bytes for draining to memory. The DMA Controller marks that cache line as the LRU and starts packing data into the other cache line (now the MRU). Once the L64853A transfers the data to memory, the L64853A clears the dirty and valid bits.

Any time the L64853A detects a D-channel interrupt, byte count expiration, or CPU slave access (read or write) to a D-channel-related register (Next Address, Next Byte Counter, Address Counter, Byte Counter, CSR, or any register in the D channel), the L64853A queues all valid bytes in the D-cache lines for draining to memory, unless a memory error has occurred. Hardware automatically drains queued bytes to memory. When the L64853A is draining dirty bytes, the DRAINING field in the CSR reads as 11<sub>2</sub>.

#### 4.4 Memory Errors and Interrupts

Interrupts to the L64853A occur as a result of memory access errors, interrupts from the D-channel controller, or completion of a DMA transfer. When one of these interrupts occurs, the L64853A generates an SBus interrupt request by asserting INTREQ provided the INT\_EN bit in the CSR is set.

As mentioned in Section 4.1, a transfer from the D channel to memory consists of two separate transfers: one between the D channel and the L64853A, and one between the L64853A and memory. A memory, timeout, or protection error only occurs in a transfer between the L64853A and memory. When an error is detected, the L64853A sets the ERR\_PEND bit in the CSR and generates an interrupt to the SBus (if INT\_EN = 1). No

transfers occur between the L64853A and memory until the interrupt is cleared; however, up to seven additional words could be transferred from the D channel to the L64853A before the interrupt is generated. The interrupt is active until the ERR\_PEND bit is cleared by either setting the FLUSH or RESET bits in the CSR.

Parity, memory time-out, or protection errors may occur on transfers from memory to the L64853A. Because of read-ahead operations, the L64853A reads data that the D channel has not requested. The L64853A may detect an error on this data. Whether the D channel requested that data or not, the L64853A does not write the data to the D channel. The L64853A sets the ERR\_PEND bit and generates an interrupt to the SBus as long as INT\_EN = 1. The interrupt is active until the ERR\_PEND bit is cleared. To clear the ERR\_PEND bit, set either the FLUSH or RESET bits in the CSR.

The L64853A sets the INT\_PEND bit in the CSR when the D-channel controller asserts  $\overline{D_{IRQ}}$ . The L64853A then generates an interrupt to the SBus as long as INT\_EN = 1.

Similarly, the L64853A sets the INT\_PEND bit when the Byte Counter expires provided that TCI\_DIS = 0. The L64853A then generates an interrupt to the SBus as long as INT\_EN = 1.

#### 4.5 Read/Write Transactions

The L64853A D-channel interface supports DMA Master read/write and Slave register read/write operations. This section describes the signal sequences for each type of operation. Functional timing diagrams of the various operations are provided. This section is intended for hardware designers.

#### DMA Reads and Writes (Master Mode)

This subsection discusses DMA read and write operations for the D channel. Read operations are discussed first followed by a description of write operations.

### **D-Channel Read Operations**

A DMA read consists of an SBus read from memory to the L64853A and a write from the L64853A to the D channel. A DMA read indicates a

transfer from memory to the D-channel device. The signal sequence for a D-channel read operation is as follows:

- The D-channel controller asserts the Request signal (D\_REQ) in order to request a DMA transfer. Since the WRITE bit in the CSR is LOW, the L64853A performs a read operation.

- The L64853A compares the value in the Address Counter Register

with the address tag on each cache line. If the values do not match or

if the data at the requested location are marked as invalid, then a cache

miss occurs.

If a cache miss occurs, the L64853A asserts  $\overline{BR}$  to request control of the SBus. When the SBus controller asserts  $\overline{BG}$  to give control of the SBus to the L64853A, the L64853A outputs the virtual address of the data requested from the Address Counter Register onto the SBus data lines, D[31:0], along with the appropriate signals to indicate a fourword burst read.

- 3. The SBus controller's MMU translates this virtual address into a 28-bit physical address, and places the physical address on the SBus physical address lines, PA[27:0].

- 4. The L64853A reads the SBus data lines D[31:0] after each SBus clock where  $\overline{ACK2}$  is asserted, until all four words are transferred to the D cache.

- If a cache hit occurs or the L64853A has loaded the data into the D cache from the cache miss above, the L64853A asserts D\_ACK and D\_WR, and begins transferring data to the D-channel peripheral.

- 6. The L64853A writes the requested data onto the D\_D[7:0] lines from the D cache until all requested bytes are transferred.

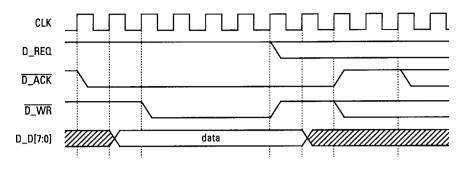

The setup of the FASTER bit in the CSR and the  $\overline{\text{SLOW}}$  pin determines the speed of the read operation. Figures 4.1 through 4.3 illustrate DMA read operations. Table 4.1 lists the figures with their respective settings for the FASTER bit and the  $\overline{\text{SLOW}}$  pin.

Table 4.1 DMA Read Operation Settings

| Figure Number | FASTER bit     | SLOW pin |

|---------------|----------------|----------|

| Figure 4.1    | $\mathbf{x}^1$ | 0        |

| Figure 4.2    | 0              | 1        |

| Figure 4.3    | 1              | 1        |

|               |                |          |

1. x = don't care.

In all three figures, the data requested by the D channel are present in the D cache. If the data are not present, the L64853A delays asserting the  $\overline{D_ACK}$  and  $\overline{D_WR}$  strobes until an SBus memory read fills the cache (see the SBus Read Cycle).

Figure 4.2 DMA Read with FASTER = 0, SLOW = 1

Figure 4.3 DMA Read with FASTER = 1, SLOW = 1

## **D-Channel Write Operations**

A DMA write indicates a transfer from the D-channel device to memory. The write consists of a read from the D channel to the L64853A and an SBus write from the L64853A to memory. The signal sequence for a D-channel write operation is as follows:

- 1. The D-channel controller asserts the Request signal (D\_REQ) in order to request a DMA transfer.

- 2. The L64853A asserts  $\overline{D_ACK}$  and  $\overline{D_RD}$  in response to the D channel's request.

- 3. The L64853A reads the data from the D\_D[7:0] lines into the D cache until the last byte in the MRU cache line is loaded or an interrupt occurs.

- 4. The L64853A asserts  $\overline{BR}$  in order to request control of the SBus. The SBus Controller asserts  $\overline{BG}$  to grant control to the L64853A. During the SBus transfer, the L64853A can also be reading data into the LRU cache line.

- 5. The L64853A outputs a 32-bit virtual address from the Address Counter Register onto the SBus data lines, D[31:0].

- 6. The SBus Controller's MMU translates this virtual address into a 28-bit physical address, and places the physical address on the SBus physical address lines, PA[27:0].

- 7. The L64853A outputs the contents of the D cache onto the SBus data lines, D[31:0]. The memory controller transfers the data to the memory array.

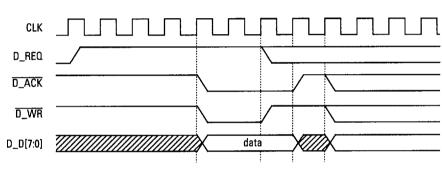

The setup of the FASTER bit in the CSR and the  $\overline{\text{SLOW}}$  pin determines the speed of the write operation. Figures 4.4 through 4.6 illustrate DMA write operations. Table 4.2 lists the figures with their respective settings for the FASTER bit and the  $\overline{\text{SLOW}}$  pin.

Table 4.2 DMA Write Operation Settings

| Figure Number | FASTER bit     | $\overline{SLOW}$ pin |  |  |

|---------------|----------------|-----------------------|--|--|

| Figure 4.4    | $\mathbf{x}^1$ | 0                     |  |  |

| Figure 4.5    | 0              | 1                     |  |  |

| Figure 4.6    | 1              | 1                     |  |  |

<sup>1.</sup> x = don't care.

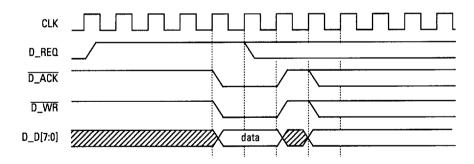

Figure 4.5

DMA Write with

FASTER = 0,

SLOW = 1

Figure 4.6

DMA Write with

FASTER = 1,

SLOW = 1

Register Reads and Writes (Slave Mode) Register reads and writes allow the CPU to read status conditions and to set up data transfer parameters. The CPU is the Bus Master throughout these operations, and the L64853A is the Slave.

The following steps summarize a D-channel register read or write operation:

1. The CPU executes a LOAD or STORE instruction using the system-dependent address that asserts the L64853A's Slave Select signal (SEL). The physical address is also driven onto PA[27:0] along with the appropriate states of RD, SIZ[2:0], and AS.

- 2. The L64853A recognizes the read or write access (SEL is asserted), and interprets the value (10<sub>2</sub>) on the physical address lines PA[X:Y]. This value indicates that an external D-channel controller register is the target of the read or write. Note that Chapter 8, "Applications," describes the register addresses for the external registers on the SPARCstation 1.

- 3. The D-channel data transfer size over the SBus is one byte. The L64853A passes the data between the SBus and the D-channel controller without any buffering in the D cache. The data are transferred over the D\_D[7:0] lines to or from an eight-bit register in the D-channel controller. To accomplish this transfer, the L64853A also asserts various strobes (D\_CS, D\_RD, D\_WR).

- 4. Finally, the L64853A asserts ACK1, thus informing the SBus controller that the Slave-mode operation has completed.

- 5. If the D channel is busy transferring data to or from the D cache when the CPU selects that channel, the L64853A asserts Rerun Acknowledgment on the ACK[2:0] pins to tell the CPU to rerun its operation.

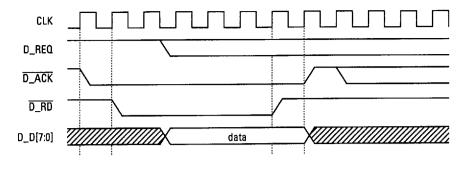

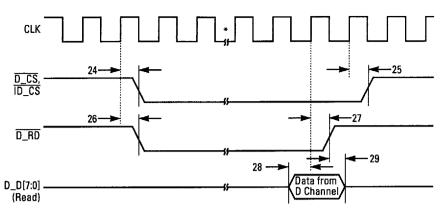

Figure 4.7 illustrates a D-channel register read operation in fast mode  $(\overline{SLOW} = 1)$ . Figure 4.8 illustrates a D-channel register read operation in slow mode  $(\overline{SLOW} = 0)$ . The main difference between the two operations is that  $\overline{D\_CS}$  and  $\overline{D\_RD}$  are held LOW three clock cycles longer in slow mode than in fast mode.

Figure 4.7

Fast Mode

D-Channel Register

Read (SLOW = 1)

Figure 4.8 Slow Mode D-Channel Register Read (SLOW = 0)

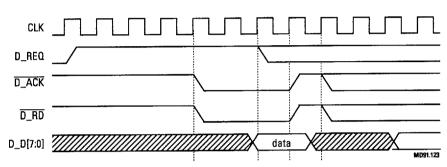

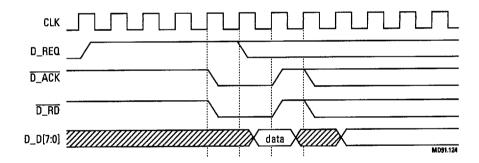

Figure 4.9 illustrates a D-channel register write operation in fast mode  $(\overline{SLOW} = 1)$ . Figure 4.10 illustrates a D-channel register write operation in slow mode  $(\overline{SLOW} = 0)$ . The main differences between the two operations are that  $\overline{D\_CS}$  and  $\overline{D\_WR}$  are extended by two clock cycles in slow mode.

Figure 4.9

Fast-Mode

D-Channel Register

Write (SLOW = 1)

Figure 4.10 Slow-Mode D-Channel Register Write (SLOW = 0)

## 4.6 Programming Notes

This section provides some D-channel programming hints for the software programmer on the following topics:

- Setting Up, Suspending, and Stopping Transfers

- Using the Byte Counter with EN\_NEXT = 0

- Using the Byte Counter with EN\_NEXT = 1

## Setting Up, Suspending, and Stopping Transfers

This subsection discusses procedures for setting up, suspending, and halting DMA transfers. The following procedure is recommended for correct operation of transfers between the L64853A and the D channel:

Step 1. Configure the CSR for the data transfer.

First clear the CSR to ensure no error bits are set. To clear the CSR, issue either a FLUSH or RESET command. Then program the WRITE, INT\_EN, EN\_CNT, FASTER, EN\_DMA, EN\_NEXT, and TCI\_DIS bits for the operation.

- Step 2. Load the transfer size into the Byte Counter.

- Step 3. Load the starting address of the data transfer into the Address Counter Register. The L64853A is now ready to service any D-channel master transactions, provided that DMA ON is set.

- Step 4. Program the D-channel controller for the particular transfer and initiate the transfer.

To suspend transfers between the D channel and the L64853A, the device driver clears the EN\_DMA bit in the CSR. The L64853A ignores new

DMA requests from the D channel when EN\_DMA = 0. Note that the L64853A can still access SBus memory even with EN\_DMA = 0. The device driver restarts the DMA transfer by setting EN\_DMA.

One of three events halts the transfer:

- An error. The device driver must poll the D-channel controller for status.

- An interrupt. The device driver must provide service.

- Expiration of the Byte Counter.

## Using the Byte Counter with EN\_NEXT = 0

The following procedure is recommended for correct operation of the internal Byte Counter when EN\_NEXT = 0:

Step 1. Load the CSR with:

INTREO.

INT\_EN = EN\_DMA = EN\_CNT = 1

TCI\_DIS = FLUSH = RESET = EN\_NEXT = Reserved = 0

WRITE = ALE/AS = as read or required for the operation

Note that the SBus interrupt request signal (INTREQ) is enabled

(INT\_EN = 1) and the Terminal Count flag is enabled

(EN\_CNT = 1 and TCI\_DIS = 0). The expiration of the byte count sets the TC bit in the CSR and generates an interrupt on

- Step 2. Load the transfer size for the first block into the Byte Counter.

- Step 3. Load the starting address of the first block into the Address Counter Register.

Once the address is loaded, the L64853A is ready to service any D-channel requests.

Step 4. Tell the D-channel controller to initiate the transfer.

Data are transferred until the Byte Counter expires. At this time, the L64853A halts DMA activity, sets the TC flag in the CSR, and generates an interrupt. The L64853A also clears A\_LOADED, which in turn clears DMA\_ON and prevents further DMA activity. DMA remains stopped, independent of the value of EN\_DMA, until a new value is loaded into the Address Counter Register. The interrupt service routine should clear EN\_DMA before writing a new address to the Address Counter Register.

To initiate another DMA operation:

- Issue a FLUSH command to clear the TC flag.

- Repeat the process from Step 1 above.

Using the Byte Counter with EN NEXT = 1