# CX20201/CX20202

# 10-Bit, 100 MHz D/A Converters

## Description

The CX20201/CX20202 are ICs which have been developed for 10-bit high-speed D/A converters. They are suitable for digital VTR, digital measuring instruments, graphic displays, high definition video systems, which require high precision, high resolution and ultra high-speed signal processing.

#### **Features**

- High resolution: 10 bits

- High-speed: Maximum conversion rate of 100MSPS

- Low-power consumption

- Operates with a single power supply of -5V

- · Low glitches

- ECL compatible input

- Small number of external parts

- · Enables to invert digital input code

- Multiplying function

# Absolute Maximum Ratings (Ta=25°C)

| <ul> <li>Power supply voltage</li> </ul>  | VEE        | <b>-</b> 7       | V            |

|-------------------------------------------|------------|------------------|--------------|

| <ul> <li>Data input voltage</li> </ul>    | VI         | VEE to $\pm 0.3$ | V            |

| <ul> <li>Clock input voltage</li> </ul>   | VCLK, VCLK | VEE to $\pm 0.3$ | V            |

| <ul> <li>Invert input voltage</li> </ul>  | VINV       | VEE to $\pm 0.3$ | V            |

| <ul> <li>Bias input voltage</li> </ul>    | VBIAS      | VEE to +0.3      | V            |

| <ul> <li>Operating temperature</li> </ul> | Topr       | -20 to $+75$     | $^{\circ}$ C |

| <ul> <li>Storage temperature</li> </ul>   | Tstg       | -55 to $+150$    | $^{\circ}$ C |

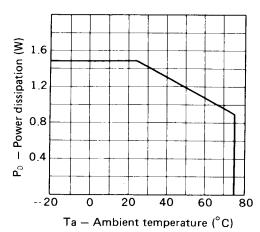

| Allowable power dissip                    | ation      |                  |              |

| P <sub>D</sub> CX2                        | 20201      | 870              | mW           |

|                                           |            |                  |              |

| CX2                                       | 20202      | 1480             | mW           |

|                                           |            |                  |              |

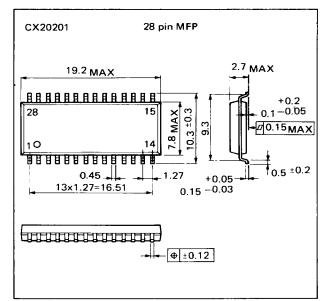

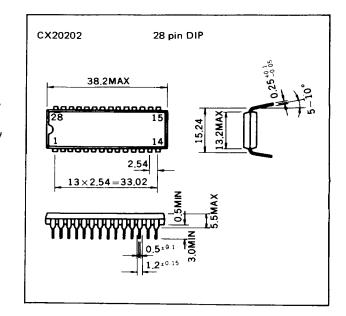

# Package Outline

Unit: mm

# **Recommended Operating Conditions**

| <ul> <li>Power supply voltage</li> </ul> | VEE                       | $-5.0 \pm 0.25$       | V     |

|------------------------------------------|---------------------------|-----------------------|-------|

| <ul> <li>Data input voltage</li> </ul>   | ViH                       | $-0.89 \pm 0.15$      | V     |

|                                          | VIL                       | $-1.75 \pm 0.15$      | V     |

| <ul> <li>Clock input voltage</li> </ul>  | Vclкн, V <del>clк</del> н | $-0.89 \pm 0.15$      | V     |

|                                          | Vclkl, V <del>clk</del> l | $-1.75 \pm 0.15$      | , v   |

| Bias voltage                             | VBIAS                     | VEE + 0.62 to VEE + 1 | .02 V |

SONY reserves the right to change products and specifications without notice.

This information does not convey any license under patent rights of SONY corporation or others.

T

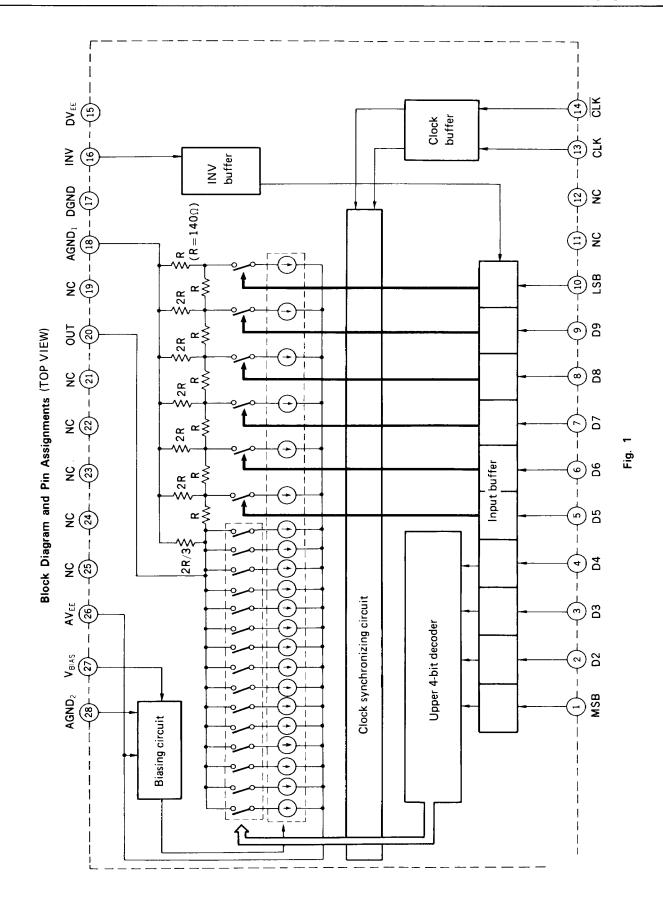

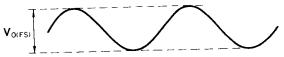

#### Pin Description

① MSB ② D2

③ D3 ④ D4

⑤ D5

6 D6

8 D8

10-bit digital data input pin. ⑦ D7

If the device is used as n-bit ( $n \le 9$ ) D/A converter, pin 1 to pin n are to be used normally, and the rest pins (n+1) to 10 opened or connected to VEE.

9 D9 10 LSB

Non-Connection 12)

13 CLK 14 CLK

: Digital clock input is to be applied.

15 D. VEE

: Digital clock bar input is to be applied. : Power supply pin of digital circuitry.

(16) INV

: Code inverse input pin which inverts the relation between the binary code of digital data and D/A output voltage level. See "Note on use".

① D.GND

: Ground pin of digital circuitry.

18 A.GND<sub>1</sub>

: Ground pin connected directly to R-2R output resistance circuit network within the IC.

19 Non-connection

20 OUT

: D/A output 21 22 23 24 25 : Non-connection

26 A. VEE

: Power supply pin of analog circuitry.

(27) VBIAS

: Bias pin which controls D/A output voltage range, and to which a proper voltage should be applied

externally.

28 A.GND<sub>2</sub>

: Ground pin of the analog circuitry except R-2R output resistance circuit network.

$\top$

Electrical Characteristics (Ta = 25°C,  $AV_{EE} = DV_{EE} = -5.0V$ , AGND = DGND = 0V)

| See | Fig  | - |

|-----|------|---|

| SCC | 1.15 | 4 |

| Item                              |           | Symbol                                | Min.                                             | Тур.  | Max.  | Unit    | Measuring point |

|-----------------------------------|-----------|---------------------------------------|--------------------------------------------------|-------|-------|---------|-----------------|

| Consular arrange                  | CX20201   | · · · · · · · · · · · · · · · · · · · | 60                                               | 75    | 90    |         | Y1              |

| Supply current                    | CX20202   | $I_{EE}$                              | 65                                               | 82    | 99    | mA      | I1              |

| Data input current                | (H level) | $I_{IH(U)}$                           | 0.5                                              | 1.3   | 3.0   | μΑ      |                 |

| (upper 4 bits)                    | (L level) | $I_{IL(U)}$                           | 0.5                                              | 1.3   | 3.0   | μА      |                 |

| Data input current (lower 6 bits) | (H level) | I <sub>IH(L)</sub>                    | 0.25                                             | 0.65  | 1.5   | μA      |                 |

|                                   | (L level) | $I_{IL(L)}$                           | 0.25                                             | 0.65  | 1.5   | μА      |                 |

| Clock input current               | CX20201   | T                                     | 7                                                | 21    | 52    | μΑ      | 13              |

| (H level)                         | CX20202   | $I_{CLKH}$                            | 7                                                | 23    | 54    | μΩ      | 15              |

| Clock bar input                   | CX20201   | T                                     | 7                                                | 21    | 52    |         | 14              |

| current (H level)                 | CX20202   | $I_{\overline{CLKH}}$                 | 7                                                | 23    | 54    | $\mu A$ | <b>I</b> 4      |

| Invert input current (            | H level)  | I <sub>INVH</sub>                     | 0.3                                              | 1.0   | 2.4   | μА      | <b>I</b> 5      |

| Bias input current                |           | I <sub>BIAS</sub>                     | -1.0                                             | -0.38 | -0.10 | μА      | <b>I</b> 6      |

| Outrut register as                | CX20201   |                                       | 54                                               | 64    | 74    |         |                 |

| Output resistance                 | CX20202   | R <sub>o</sub>                        | 52                                               | 62    | 72    | Ω       | V1              |

| Resolution                        |           | RSL                                   |                                                  | 10    |       | Bit     |                 |

|                                   |           |                                       | <del>                                     </del> | +     |       |         |                 |

| Resolution                   | RSL                |      | 10 |      | Bit  |

|------------------------------|--------------------|------|----|------|------|

| Differential linearity error | DLE                | -1.0 |    | +1.0 | LSB  |

| Maximum conversion rate      | f <sub>C MAX</sub> | 100  |    |      | MSPS |

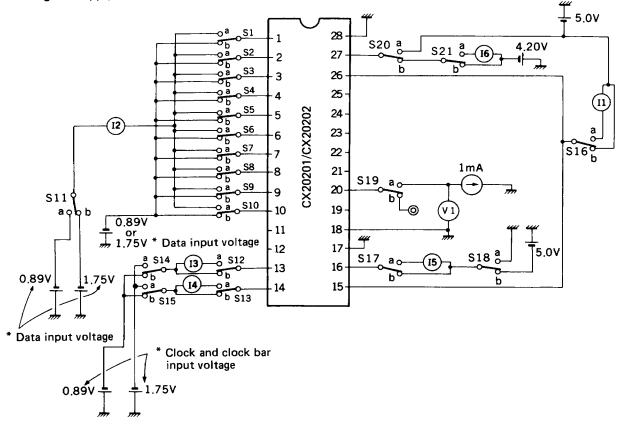

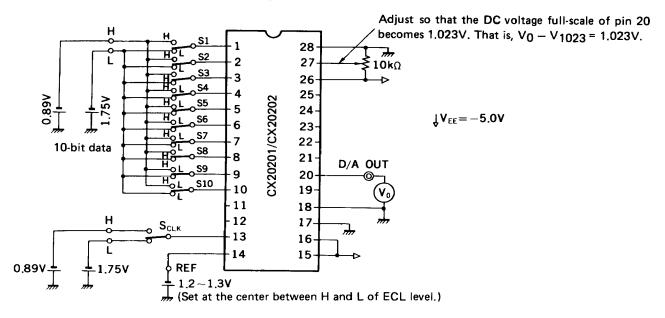

#### **Electrical Characteristics Measuring Circuit Diagram**

Fig. 2 Supply Current, Input Current and Output Resistance Measuring Circuit

Fig. 3 Differential Linearity Error Measuring Circuit

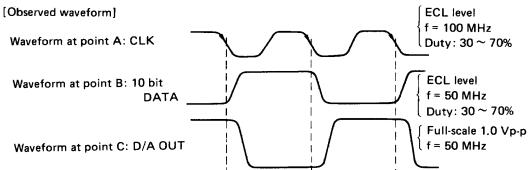

[Meausuring Circuit Condition of Fig. 3] (H="1" level; L="0" level)

| Operating  |          |              | S             | Swite    | chin     | g co     | ondi     | tior     | 1        |     |          | Measur-<br>ing |                                                              |  |  |  |  |

|------------|----------|--------------|---------------|----------|----------|----------|----------|----------|----------|-----|----------|----------------|--------------------------------------------------------------|--|--|--|--|

| order      | S1       | S2           | S3            | S4       | S5       | S6       | S7       | S8       | S9       | S10 | Scle     | point          | Explanation of measuring method                              |  |  |  |  |

| 1          | Н        | Н            | Н             | Н        | Н        | Н        | Н        | Н        | Н        | Н   | L        |                |                                                              |  |  |  |  |

| 2          | <b>↓</b> | 1            | ↓             | ↓        | 1        | 1        | 1        | <b>↓</b> | 1        | 1   | Н        |                |                                                              |  |  |  |  |

| 3          | 1        | 1            | <b>→</b>      | 1        | Ţ        | 1        | <b>1</b> | <b>↓</b> | 1        | 1   | L        | V <sub>o</sub> | Measuring DC voltage. Measured value V0 ≡ (Unit: mV)         |  |  |  |  |

| 4          | 1        | <b>+</b>     | ↓             | J        | <b>1</b> | 1        | ↓        | 1        | <b>↓</b> | L   | <b>↓</b> |                |                                                              |  |  |  |  |

| 5          | 1        | <b>↓</b>     | $\downarrow$  | 1        | <b>↓</b> | <b>↓</b> | <b>↓</b> | <b>1</b> | ↓        | 1   | H        |                |                                                              |  |  |  |  |

| 6          | <b>↓</b> | 1            | <b>→</b>      | 1        | ↓        | 1        | <b>↓</b> | <b>↓</b> | <b>↓</b> | 1   | L        | V <sub>o</sub> | Measuring DC voltage. Measured value V₁ ≡ (Unit: mV)         |  |  |  |  |

| 7          | <b>↓</b> | <b>↓</b>     | $\rightarrow$ | 1        | ↓        | <b>↓</b> | <b>↓</b> | <b>→</b> | L        | Н   | J        |                |                                                              |  |  |  |  |

| 8          | 1        | $\leftarrow$ | <b>↓</b>      | 1        | ↓        | J        | <b>↓</b> | <b>1</b> | 1        | 1   | Н        |                |                                                              |  |  |  |  |

| 9          | <b>↓</b> | 1            | 1             | <b>↓</b> | ↓        | <b>1</b> | 1        | 1        | ↓        | 1   | L        | V <sub>o</sub> | Measuring DC voltage. Measured value $V_2 \equiv (Unit: mV)$ |  |  |  |  |

| 10         | ↓        | ↓            | <b>1</b>      | <b>↓</b> | ↓        | 1        | 1        | 1        | ↓        | L   | 1        |                |                                                              |  |  |  |  |

| $\sim\sim$ |          |              |               |          |          |          |          |          |          |     |          | $\sim$         | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~                      |  |  |  |  |

Proceed the measurement reducing the input data (voltage of pin 1 to pin 10) in regular sequence of binary notation, and continue until the final data becomes LLL...L

$$\Delta V_{0-1} \equiv V_0 - V_1$$

(Unit mV)

$\Delta V_{1-2} \equiv V_1 - V_2$  (Unit mV)

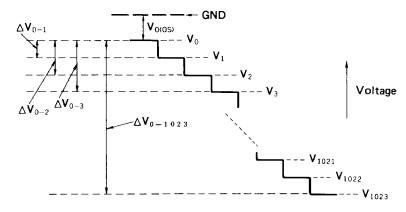

$\Delta V_{1022\text{-}1023} \equiv V_{1022} = V_{1023} \text{ (Unit: mV)}$  are to be calculated. (See Fig. 4) With  $\Delta V_{0\text{-}1}, \ \Delta V_{1\text{-}2}, \dots,$

T

Fig. 4 Relation between  $V_0, V_1, \ldots$  and  $\Delta V_{0-1}, \Delta V_{1-2}, \ldots$

$\varepsilon_{i-j} \equiv \frac{\Delta V_{i-j}-1}{1}$  (i=0,1,...,1022; j=1,2,...,1023) (UnitLSB)

are to be obtained. Each of 1023 pieces of  $\epsilon_{ij}$  is differential linearity error, respectively.

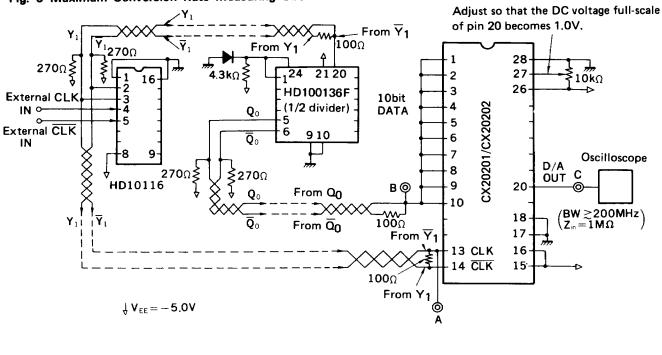

# [Measuring Method of Maximum Conversion Rate]

The external CLK IN and CLK IN should satisfy the following conditions.

- ECL level

- fclk = 100 MHz

- Duty ≈ 50%

At point C, a rectangular waveform (1.0 Vp-p, f=50 MHz) is to be obtained.

# Circuit Design Data

$\left(\begin{array}{c} Ta=25^{\circ}C, \text{ however, * mark is } Ta=-20 \text{ to } +75^{\circ}C \\ AVEE=DVEE=-5.0V, AGND=DGND=0V \end{array}\right)$

| Item                                                | Symbol  | Min.  | Тур.  | Max.  | Unit      | Condition                                                                                                                                                             |

|-----------------------------------------------------|---------|-------|-------|-------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Integral linearity error                            | ILE     | -0.4  |       | +0.4  | % of F.S. |                                                                                                                                                                       |

| Output voltage full-scale                           | VO(FS)  | 0.890 | 1.000 | 1.110 | Vp-p      | Voltage of pin 27 is $-4.20$ V. The load to be connected to pin 20 is $Z_L > 10 \text{ k}\Omega$ .                                                                    |

| Output voltage zero offset                          | Vo(os)  | -15   | -4    | -1    | mV        |                                                                                                                                                                       |

| Output voltage full-scale temperature coefficient*  | TCF(FS) | 0     | 150   | 500   | ppm/°C    |                                                                                                                                                                       |

| Output voltage zero offset temperature coefficient* | Tcf(os) | 6     | 16    | 22    | μV/°C     |                                                                                                                                                                       |

| Output voltage full-scale dynamic range             | DR      | -3.3  | 0     | +3.3  | dB        | 0dB denotes 1.000V of full-scale output voltage. (This full-scale voltage is set by adjusting the voltage of pin 27.) The load to be connected to pin 20 is ZL>10 kΩ. |

| Glitch energy                                       | GE      |       | 15    |       | pV-sec    | See Glitch energy measuring method.                                                                                                                                   |

| Set-up time                                         | ts      | 7.0   |       |       | ns        | See measuring circuit and observed                                                                                                                                    |

| Hold time                                           | th      | 1.0   |       |       | ns        | waveform diagrams (Fig. 9).                                                                                                                                           |

| Propagation delay                                   | tpd     |       | 2.8   |       | ns        | Loading: RL CL<0.1 nS.  / RL: pure resistance                                                                                                                         |

| Rise time                                           | tr      |       | 1.5   |       | ns        | CL: capacitive load                                                                                                                                                   |

| Fall time                                           | tf      |       | 1.5   |       | ns        | They are connected to pin 20.                                                                                                                                         |

| Settling time                                       | tset    |       | 4.7   |       | ns        | See Explanation of settling time.                                                                                                                                     |

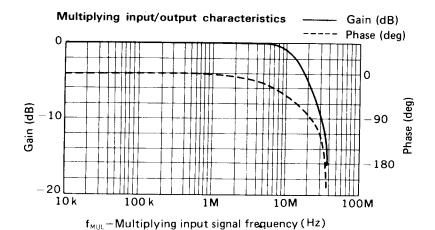

| Multiplying bandwidth                               | BWMUL   |       |       | 10    | MHz       | The frequency in which the gain of D/A output becomes -3 dB. See Fig. 11.                                                                                             |

# [Measuring Method for Circuit Design Data]

## 1. Integral linearity error

In differential linearity error measuring circuit (Fig. 3).

$$\Delta V_{0-1} \equiv V_0 - V_1$$

(Unit: mV)

$\Delta V_{0-2} \equiv V_0 - V_2$  (Unit: mV)

$$\Delta V_{0-3} \equiv V_0 - V_3$$

(Unit: mV)

•

$$\Delta V_{0-1023} \equiv V_0 - V_{1023}$$

(Unit: mV)

and

$$\epsilon_{absi} \equiv \frac{\Delta V_{0\text{-}i} - i}{1023} \times \ 100 \ (i=1,\ 2,\ 3,\ \dots,\ 1023) \ (Unit:\ \%)$$

Each of 1023 pieces of εabsi is integral linearity error.

Fig. 6 Relation between  $V_0, V_1 \dots$  and  $\Delta V_{0-1}, \Delta V_{0-2}, \dots$

# 2. Output voltage zero offset

In Fig. 6, the potential difference between GND level and Vo is defined as zero offset, Vo(os).

D/A OUT

T

#### Glitch energy Adjust so that the full-scale of the staircase waveform of pin 20 becomes 1.023 V. 28 CLK buffer 2 27 禁 22μF CX20201/CX20202 3 26 Generates 10-bit Ď staircase waveform. Ď., -6 Ď. External Oscilloscope D, OUT **CLK IN** С D<sub>B</sub>-20 9 9 10 LSB SONY TEKTRONIX ECL level 18 HD10116 7A13 unit with 5 HD10116 f = 1 MHz CLK From CLK 17 CLK 🎞 MHz filter 13 CLK 16 $BW \le 5MHz$ $Z_{in} = 1 M\Omega$ 14 CLK 15 From CLK COUNTER CLK 21 20 2120 21 20 \$4.7kΩ HD100136F HD100136F 10-bit counter -HD100136F Resistance value is $270\Omega$ otherwise specified. $\downarrow V_{EE} = -5.0V$ $\overrightarrow{\mathbf{D}_9}$ $\overrightarrow{\mathbf{D}_9}$ $\overline{\,\textbf{D}_{8}\,}\,\,\textbf{D}_{8}$ $\overline{D}_{10}$ $D_{10}$ $\overline{\mathsf{D}_6} \; \mathsf{D}_6$ $\overline{D_5}$ $D_5$ $\overline{D_4}$ $D_4$ $\overline{D}_3$ $D_3$ $\overline{D_7}$ $\overline{D_7}$ $\overline{D_2}$ $D_2$ $\overline{D_1} D_1$ Fig. 7(a) Glitch energy measuring circuit ECL level Waveform at point A: f = 1 MHzCLK Duty: 50% ECL level Waveform at point B: f = 0.5 MHz DATA of LSB Duty: 50% 10-bit staircase waveform 1 step corresponds to 1 mV Waveform at point C:

Fig. 7(b) Observed waveforms of the above-mentioned measuring circuit

Voltage

- Time

# [Measuring Method of Glitch Energy]

The signal to be fed to External CLK IN terminal should satisfy the following conditions.

- ECL level

- fclk = 1 MHz

- Duty = 50%

In this case, the observed waveforms at points A, B and C become as shown in Fig. 7(b), respectively.

In Fig. 7(b), GE is the integrated value of the difference between an ideal voltage waveform and the overshoot which is generated actually. It is marked with oblique lines.

It is measured at the transient points shown in the following table.

|    | D <sub>1</sub> | $\overline{D_2}$ | $D_3$ | $D_4$ | $D_5$ | $D_6$ | $D_7$ | $D_8$ | $D_9$ | D <sub>10</sub> | <br>$D_1$      | $D_2$ | $D_3$ | $D_4$ | $D_5$ | $D_6$ | $\mathbf{D}_7$ | $D_8$ | $D_9$ | $D_{10}$ |

|----|----------------|------------------|-------|-------|-------|-------|-------|-------|-------|-----------------|----------------|-------|-------|-------|-------|-------|----------------|-------|-------|----------|

| 1  | L              | L                | L     | L     | Н     | Н     | Н     | Н     | Н     | Н               | <br><b>→</b> L | L     | L     | Н     | L     | L     | L              | L     | L     | L        |

| 2  | L              | L                | L     | Н     | Н     | H     | Н     | Н     | H     | Н               | <br><b>→</b> L | L     | H_    | L     | L     | L     | L              | L     | L     | L        |

| 3  | L              | L                | Н     | L     | Н     | Н     | H     | Н     | Н     | Н               | → L            | L     | Н     | Н     | L     | L     | L              | L     | L     | L        |

| 4  | L              | L                | Н     | Н     | Н     | Н     | Н     | Н     | Н     | Н               | → L            | Н     | L     | L     | L     | L     | L              | L     | L     | L        |

| 5  | L              | Н                | L     | L     | Н     | Н     | Н     | Н     | Н     | Н               | <br><u> </u>   | Н     | L     | H     | L     | L     | L              | L     | L     | L        |

| 6  | L              | Н                | L     | Н     | Н     | Н     | Н     | Н     | Н     | Н               | <br><u> </u>   | Н     | H     | L     | L     | L     | L              | L     | L     | L        |

| 7  | L              | Н                | Н     | L     | Н     | Н     | Н     | Н     | Н     | Н               | <br>→ L        | Н     | Н     | Н     | L     | L     | L              | L     | L     | L        |

| 8  | L              | Н                | Н     | Н     | Н     | Н     | Н     | Н     | Н     | Н               | <b>→</b> H     | L     | L     | L     | L     | L     | L              | L     | L     | L        |

| 9  | Н              | L                | L     | L     | Н     | H     | Н     | Н     | Н     | Н               | <br>→ H        | L     | L     | Н     | L     | L     | L              | L     | L     | L        |

| 10 | Н              | L                | L     | Н     | Н     | Н     | Н     | Н     | Н     | Н               | <br>- H        | L     | Н     | L     | L     | L     | L              | L     | L     | L        |

| 11 | Н              | L                | Н     | L     | Н     | Н     | Н     | Н     | Н     | H               | <b>→</b> H     | L     | H     | Н     | L     | L     | L              | L     | L     | L        |

| 12 | Н              | L                | Н     | Н     | Н     | Н     | Н     | Н     | Н     | Н               | <b>→</b> H     | Н     | L     | L     | L     | L     | L              | L     | L     | L        |

| 13 | Н              | Н                | L     | L     | Н     | Н     | Н     | Н     | Н     | H               | <br><b>→</b> H | Н     | L     | Н     | L     | L     | L              | L     | L     | L        |

| 14 | Н              | Н                | L     | Н     | Н     | Н     | Н     | Н     | Н     | Н               | H              | Н     | H     | L     | L     | L     | L              | L     | L     | L        |

| 15 | Н              | Н                | Н     | L     | Н     | Н     | Н     | Н     | Н     | Н               | <br><b>→</b> H | Н     | Н     | H     | L     | L     | L              | L     | L     | L        |

(H and L mean the high and low of ECL levels.)

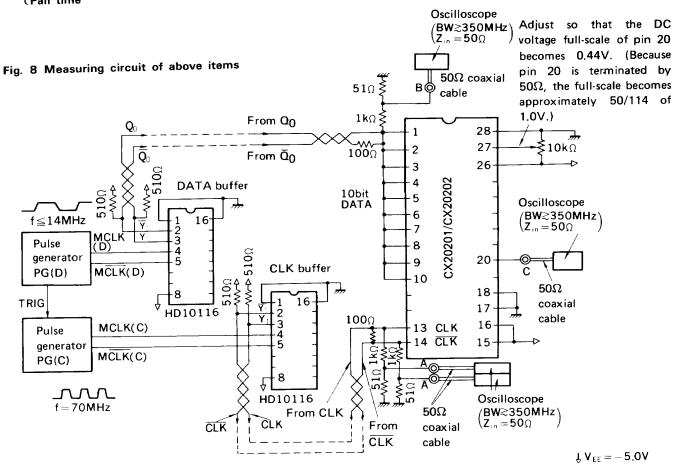

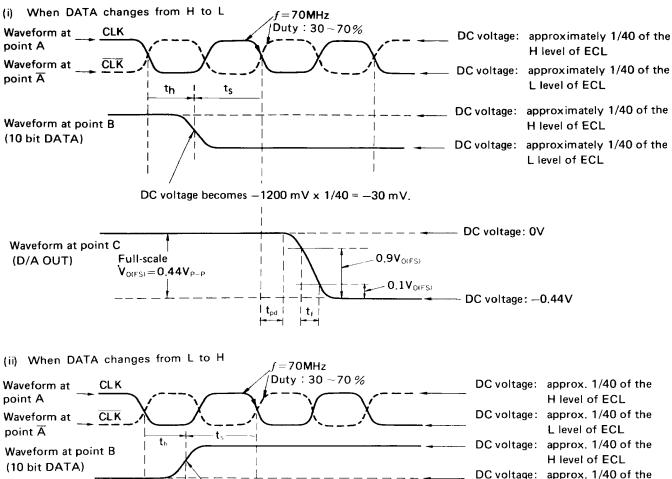

Set-up time Hold time Propagation delay Rise time Fall time

# [Measuring Method of Above Items]

The signals which are generated by pulse generators PG(C) and PG(D) should satisfy the following conditions.

- 1) PG(C)

- ECL level

- f=70 MHz

- Duty  $\simeq$  50%

- (2) PG(D)

- ECL level

- f≦14 MHz

By changing the delay time of the mutual pulses generated from PG(C) and PG(D), control phase relations among those of observed waveforms at points A,  $\overline{A}$  and B. And then, obtain the range of  $t_s$  and  $t_h$  where D/A output changes at

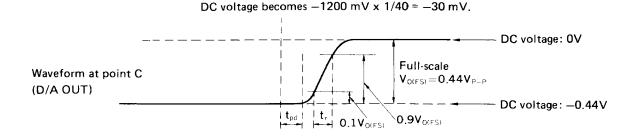

Desired waveforms to be observed at points, A,  $\overline{A}$ , B and C, are sketched as follows:

L level of ECL

Fig. 9 Observed waveforms

In addition, measure t<sub>pd</sub> (The interval between the switchover points of CLK and CLK, and the time when D/A OUT waveform begins to change by 1 LSB.), and also, rise time t<sub>r</sub> and fall time t<sub>f</sub> (as shown in Fig. 9).

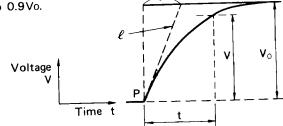

# 5. Settling time

The settling time described in Circuit Design Data is the value calculated with rise time and fall time.

The calculation method is as shown below.

In the D/A output waveform shown in Fig. 10,

$$V = Vo(1 - e^{-\frac{t}{\tau}})$$

The dotted line is the tangential line at point P. Settling time of 10-bit (tset) can be obtained by setting V=0.999Vo in the above equation. Thus,

$$t_{set} = 6.91 \tau ... (1)$$

Rise time  $t_r$  is the interval in which V varies from 0.1Vo to 0.9Vo.

When V=0.1Vo,  $t_{10}=-\tau ln0.9$

When V=0.9Vo,  $t_{90} = -\tau ln0.1$

$t_r = t_{90} - t_{10} = \tau \ln 9$

.. t<sub>r</sub>=2.20τ ... (2)

From eqs. (1) and (2)

tset=3.14tr.... (3)

Thus, t<sub>set</sub> can be calculated.

Fig. 10 D/A output waveform

# Multiplying bandwidth

Fig. 11 Multiplying bandwidth measuring circuit

28 1 1.75V -27 2  $10k\Omega$ Sine wave (L level generator 26 **-**D-3 of ECL) CX20201/CX20202 0.00 Ï <sub>µ</sub>F 5 6 Oscillo  $\begin{pmatrix} BW \gtrsim 75MHz \\ Z_m = 1M\Omega \end{pmatrix}$ 7 scope 8 Oscillo 20 BW≳75MHz\ 9 scope  $\mathbf{Z}_{\mathsf{in}} = \mathbf{1} \mathbf{M} \mathbf{\Omega}$ -10 18 17 13 16 0.89V 14 15 (H level

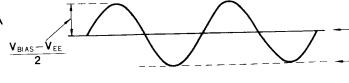

(1) Adjust so that DC voltage at point B becomes -1.00V when sine wave is not fed.

Then, the DC voltage at point A is defined as VBIAS-

(2) Apply sine wave to pin 27, and adjust the amplitude so that the amplitude of waveform at point A becomes VBIAS - VEE.

$\int V_{EE} = -5.0V$

# of ECL) [Observed waveform]

Frequency f MUL

Waveform at point A

- DC voltage: VBIAS

DC voltage: VBIAS + VEE

Waveform at point B

When fMUL  $\leq$  14 MHz, the following relation is to be satisfied 0.71  $\leq$  VO(FS)  $\leq$  1.00 (Unit: Vp-p)

Fig. 12 Typical Circuit Connection

# Note on use

See Fig. 12

Supplementary items are described below:

# (1) Setting of pin 16 (INV)

The relation, between the binary code of digital data and D/A output voltage, can be selected in two ways as shown in the following list.

CASE1: In case pin 16 is connected to D.VEE. CASE2: In case pin 16 is connected to D.GND.

|          | 5E2. III |   | D/A output voltage (Unit: V) |            |    |    |    |    |     |                           |                           |

|----------|----------|---|------------------------------|------------|----|----|----|----|-----|---------------------------|---------------------------|

| MSB      | D2       |   |                              | <b>D</b> 5 | D6 | D7 | D8 | D9 | LSB | CASE 1                    | CASE 2                    |

| H        | H        | Н | H                            | Н          | Н  | Н  | Н  | Н  | Н   | V <sub>0</sub> (OS)       | V <sub>0</sub> (OS)-1.000 |

|          | H        | Н | H                            | Н          | H  | Н  | Н  | Н  | L   | V <sub>0</sub> (OS)-0.001 | V <sub>0</sub> (OS)-0.999 |

| <u>н</u> | Н        | H | Н                            | Н          | Н  | Н  | Н  | L  | Н   | V <sub>0</sub> (OS)-0.002 | V <sub>0(OS)</sub> -0.998 |

|          |          |   |                              | :          | :  |    |    |    |     |                           |                           |

| Н        |          | L |                              | L          | L  | L  | L  | L  | L   | V <sub>0</sub> (OS)-0.500 | V <sub>0</sub> (OS)-0.502 |

|          | <u>-</u> | H | Н                            | Н          | Н  | Н  | Н  | Н  | Н   | V <sub>0</sub> (OS)-0.501 | V <sub>0</sub> (OS)-0.501 |

|          | Н        | H | Н                            | Н          | Н  | Н  | H  | Н  | L   | V <sub>0</sub> (OS)-0.502 | V <sub>0(OS)</sub> -0.500 |

|          |          |   | i                            | -          |    |    |    |    |     |                           |                           |

| L        | L        | L | L                            | L          | L  | L  | L  | L  | L   | V <sub>0</sub> (OS)-1.000 | V <sub>0</sub> (OS)       |

This is the case when the voltage at pin 27 is so adjusted that the full-scale output voltage becomes 1.000V. Vo(os) is the voltage of zero offset.

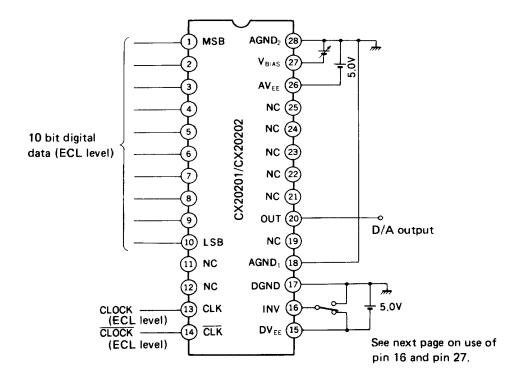

# (2) Setting of pin 27 (VBIAS)

Pin 27 to be fed a reference voltage externally.

The full-scale of D/A output voltage is determined by the reference voltage.

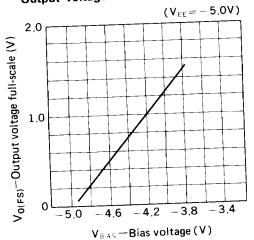

There is a range in which a linear relation is established between the reference voltage VBIAS and the full-scale Vo(FS).

The range is

0.50≦Vo(FS)≦1.50 (Unit: V)

(It is a typical value at VEE=-5.0V and Ta=25°C.)

As a concrete circuit to apply reference voltage externally to pin 27, several kinds of circuits are conceivable. The example are shown below. Provided that ZL, to be connected to pin 20, is considerably larger than 10 k $\Omega$ .

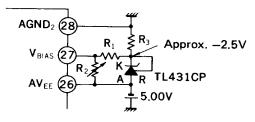

Fig. 14 Example using the TL431CP regulator.

#### (Ex.1) An example of comparatively simpler circuit

In Fig. 13, adjust VBIAS so that the full-scale of D/A output voltage becomes 1.000V.

In this case, it is necessary to determine R<sub>1</sub> and R<sub>2</sub> so as to obtain I<sub>R</sub>>500  $\mu$ A. For example, R<sub>1</sub>=8.2 k $\Omega$  and R<sub>2</sub>  $\simeq$ 1.5 k $\Omega$ .

When  $V_{EE}$ =-5.00V, VBIAS becomes nearly -4.20V.

#### (Ex.2) An improved example of Ex.1 (Countermeasure against power supply voltage fluctuation)

Fig. 14 is an example which is improved in the sensitivity of D/A output to power supply voltage fluctuation. Make R2 variable and adjust VBIAS so that the full-scale of D/A output voltage becomes 1.000V. In this case, too, it is necessary to determine constants of R1, R2 and R3 so as to be IR $\geq$ 500 uA. R1=3.6 k $\Omega$ , R2>1.5 k $\Omega$  and R3=5.1 k $\Omega$  are suitable values.

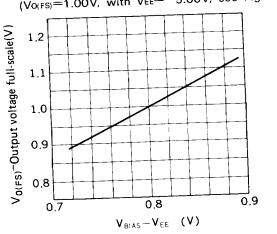

# Dependence of Output Voltage Full-scale on Power Supply Voltage

The relation between Vo(FS) and VBIAS-VEE is shown in Fig. 20.

VBIAS is set with the circuit shown in Fig. 14.

From the figure, relational equation is derived, as follows.

$\Delta V_{O(FS)} = K \cdot \Delta \text{ (VBIAS} - VEE)$  K=1.29

where  $\Delta \text{Vo(FS)}$  and  $\Delta$  (VBIAS—VEE) denote changed values.

VBIAS-VEE is also fluctuated by the fluctuation of both VBIAS and VEE.

As a result, the fluctuation of D/A output voltage full-scale occurs, which will be obtained by the equation.

# (3) Phase relation between digital data and clock

To obtain the specified characteristics as a D/A converter, it is necessary to establish correctly phase relation between data and clock externally applied.

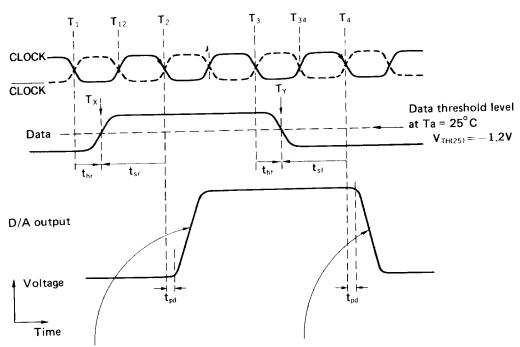

The phase relation among data clock and D/A output voltage waveforms are shown in Fig. 15.

The relation between data and D/A output corresponds to the case when pin 16 (INV) is connected to D.VEE

Fig. 15 Timing chart

At  $t=T_1+t_{hr}=T_2-t_{sr}$ , data of individual bits run across VTH(25), and at t=T2, CLK and CLK are switched over, then D/A output changes synchronized. D/A output is synchronous with the falling edge of CLK. Data are taken inside at the rising edge of CLK (at t=T12).

At  $t=T_3+t_h=T_4-t_{sf}$ , data of indicidual bits run across V<sub>TH(25)</sub>, and at t=T<sub>4</sub>, CLK and CLK are switched over, then D/A output changes synchronized. D/A output is synchronous with the falling edge of CLK. Data are taken inside at the rising edge of CLK (at t=T34).

The phase relation between data of individual bits and clock should satisfy the following conditions,  $\bigcirc$  and  $\bigcirc$  . [Conditions]

In the above figure, when each data are switched over from L to H at t=Tx, and from H to L: at t=Ty,

- (1) thr≥1.0 (Unit: ns), and also, t<sub>sr</sub>≥6.7 (Unit: ns) with,  $t_{hr}=T_x-T_1$ ,  $t_{sr}=T_2-T_x$ .

- ② thf≥1.0 (Unit: ns), and also, tsf≥6.7 (Unit: ns) with, thf= $T_y$ - $T_3$ , tsf= $T_4$ - $T_y$ .

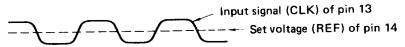

# (4) Another method of feeding clock signals

Instead of using clock and clock bar, inverse in phase each other, it is also possible to feed clock of ECL level to pin 13 (CLK), setting the voltage of pin 14 (CLK) at the central value between H and L of ECL level. In this case, the setting voltage of pin 14 has to be supplied externally.

Fig. 16 Another method of feeding clock signal

#### (5) Multiplying

It is possible to apply amplitude modulation to D/A output, with multiplying signal fed to pin 27 (VBIAS) externally. In normal usage, after setting the voltage of pin 27 and holding steady the full-scale of D/A output voltage, change digital data. As against this, in the use of multiplying method, D/A conversion is carried out while varying the full-scale of D/A output voltage, by fluctuating the voltage at pin 27 with multiplying signal.

As for the input and output characteristics of the multiplying, see Fig. 21.

An example of the circuit of standard use is shown in Fig. 17.

5.07 10kΩ 28 2 27 Modulation signal 3 25 4 CX20201/CX20202 0.001μF (Ó) A 24 5 10 bit digital 23 6 data (ECL level) 7 22 21 8 9 20--⊚ B 19 -10 18 - 11 17 12 As for the usage of pin 16. 16 13 CLOCK see (1) of "Note on use". (ECL level) 14 15 CLOCK

Fig. 17 Example of multiplying circuit of standard use

#### Adjustment Method

- 1) Set pins 1 to 10, 13, 14 and 16 in accordance with the conditions shown in Fig. 11.

- 2 Adjust VR so that DC voltage at point B becomes -1.00V, with no sine wave fed to pin 27. Then, the DC voltage at point A is defined as VBIAS (Unit: V).

- 3 Apply sine wave to pin 27, and adjust the amplitude so that the amplitude of the waveform observed at point A becomes (VBIAS+5.0)/2 (Unit: V).

#### (6) Load of D/A output terminal

The value of the temperature coefficient TcF(OS) of D/A output voltage full-scale and the value of the temperature coefficient TcF(OS) of output voltage zero offset are those in condition that load ZL of output terminal (pin 20) satisfies  $ZL > 10 \text{ k}\Omega$ . When  $ZL \le 10 \text{ k}\Omega$ , the temperature coefficient of the load resistance exerts an effect, and both TcF(OS) shift. In addition, TcF(FS) and TcF(OS) change in accordance with the kind of loads to be connected. Accordingly, in order to obtain the above-mentioned TcF(FS) and TcF(OS), it is necessary to make ZL to be  $ZL > 10 \text{ k}\Omega$ . That is, pin 20 should be connected to the high impedance as mentioned above.

#### (7) Noise reduction countermeasure

Т

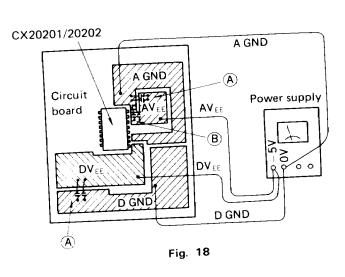

Since 1 step of the D/A output voltage is such a small voltage of approx. 1 mV, it is necessary to reduce noises coming into from outside, as much as possible. Accordingly, the following are to be considered:

- When the device is mounted on a circuit board, the board layout should have a ground plane and VEE plane as large as possible in order to reduce sheet resistance and inductance.

- It is desirable that A GND (Analog Ground) and D GND (Digital Ground) are separated each other, and so as, A VEE and DVEE are. It is recommended that, for example as shown in Fig. 18, the wiring of A GND and D GND, A VEE and D VEE should be separated each other except the power supply, and they should be made common very close to the

- ullet The coupling capacitors, 47  $\mu$ F (tantalum) and 1000 pF (ceramic) in parallel, should be utilized between the VEE and GND plane which are placed next to each other (As shown in Fig. 18 (A).) Also, it is desired that they should be placed between the VEE and GND plane in the vicinity of the IC. (As shown in Fig. 18 (B) .) These parts are needed to prevent bad effects in characteristics of the IC caused by noises coming inside.

- It is recommended to insert a capacitor of over 0.1 uF between pin 27 and pin 26, in order to reduce spurious noise which disturbs D/A output. This is only applicable when multiplying is not needed.

# Output voltage full-scale v.s. Bias voltage

Fig. 19

Output voltage full-scale v.s. VBIAS-VEE  $(V_{O(FS)}=1.00V, \text{ with } V_{EE}=-5.00V, \text{ see Fig. 14.})$

Fig. 20

Fig. 21

# Power dissipation decreasing curve

Fig. 22