# HDD Equalizer (Pulse Slimming) IC

Description

CXA1175 is an IC for HDD, read data equalizers.... (cosine equalization).

The delay circuit realized through the adoption of an active filter circuit dispenses from the expensive delay line so far in use. Delay time may be changed at will by altering the resistance value.

#### Features

- The delay circuit obtained through an active filter circuit dispenses from external delay lines. Delay time adjustment is possible by changing the external resistance value.

- Mix ratio adjustment is possible by changing the external resistance value.

- Variation of characteristics on both inner and outer tracks is possible through TTL signal Minute adjustment is possible when necessary through the use of discrete devices.

- Single power supply, 5V.

- Low power consumption.

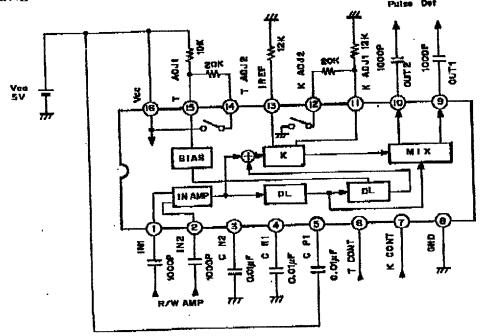

### Block Diagram and Pin Configuration

FR9419-HP

SONY reservors the right to change products and specifications without notice.

Absolute Maximum Ratings (Ta=25°C)

$V_{CC}$  Supply voltage -55 to +150 Tsix • Storage temperature

**Operating Conditions** 4.75 to 5.25 Vcc ·C

Supply voltageAmbient temperature -20 to +75 Topr

#### Pin Description

| in Description  No. Symbol Volb |        | Voltage | Equivalent circuit      | Description                                                                                                                                                                                                       |  |  |  |

|---------------------------------|--------|---------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1                               | INI    | 2.0V    | CHO WE                  | Inputs data signals from read amplifier es differential signals through a capacitor, internal impedance is approx. 16kΩ.                                                                                          |  |  |  |

| 2                               | IN2    |         | 2 THE 200 H SOUTH SOUTH |                                                                                                                                                                                                                   |  |  |  |

| 3                               | CN2    | 1.5V    | <b>∞</b>                | Connects capacitor (0.01 µF) between this pin and GND to control noise in the                                                                                                                                     |  |  |  |

| 4                               | CN1    |         | ***                     | circuit.                                                                                                                                                                                                          |  |  |  |

| 5                               | CPI    | 3.5V    | 1                       | Connects capacitor (0.01 $\mu$ F) between this pin and $V_{\rm CC}$ to control noise in the circuit.                                                                                                              |  |  |  |

| 6                               | T CONT | * 2.0V  | S W W SOUTH             | To vary characteristics on the inner of outer track, delay time is varied according to the signals (TTL level) input this pin.  When this pin is at Low, delay time is a according to the resistance connected to |  |  |  |

|                                 |        | * 0.8V  |                         | pin 15 (T ADJ1).  When this pin is at High, delay time is set according to the parallel resistance value of the resistances connected to Pins 15 (T ADJ1) and 14 (T ADJ2).                                        |  |  |  |

|     |        |         | ·                   |                                                                                                                                                                                                                          |  |  |  |

|-----|--------|---------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| No. | Symbol | Voltage | Equivalent circuit  | Description                                                                                                                                                                                                              |  |  |  |

| 7   |        | ≠ 2.0V  | A South             | To vary characteristics on the inner or outer track, Mix ratio K is varied according to the signals (TTL level) input to this pin."  When this pin is at Low, Mix ratio is set according to the parallel resistance val- |  |  |  |

|     | K CONT | * 0.8V  | CHD 20              | ue of the resistances connected to pins 11 (K ADJ1) and 12 (K ADJ2). When this pin is at High, Mix ratio is set according to the resistance connected to Pin 11 (K ADJ1).                                                |  |  |  |

| 8   | GND    | ov      |                     | GND pin for all circuits.                                                                                                                                                                                                |  |  |  |

| g   | OUTI   | 3.8V    | 90 ±                | Signal output pin. Equalized signal is output to pulse detector.                                                                                                                                                         |  |  |  |

| 10  | OUT2   |         | eut T               | Output to pro-                                                                                                                                                                                                           |  |  |  |

| 11  | K ADJI | 1.2V    | CNID THE            | A resistor is connected to set Mix ratio.<br>K=approx.0.23 at 12kΩ (Typ.). Varying<br>the resistance value from ∞ to 4KΩ<br>varies K from 0 to 0.3.                                                                      |  |  |  |

| 12  | K ADJ2 |         | GND #               | When Pin 7 (K-CONT) is at Low, this pin is set to the parallel value of the resistances connected to this pin and to pin 11 (K ADJ1).                                                                                    |  |  |  |

| 13  | I REF  | 1.29    | (3) W65 W77 W77 W77 | 12kΩ resistor is connected to obtain internal reference current.                                                                                                                                                         |  |  |  |

| 14  | SLOA T |         | VCE ME              | When Pin 6 (T CONT) is at High, delay time is set according to the parallel value of the resistances connected to this pin and to pin 15 (T ADJ1).                                                                       |  |  |  |

|     |        |         | Equivalent circuit                          | Description                                                                                                                                     |  |  |  |

|-----|--------|---------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| No. | Symbol | Voltage | Education                                   |                                                                                                                                                 |  |  |  |

| 15  | T ADJ1 | 4.0     | (B) AND | A resistor is connected to set delay time. Set to 58ns at $10k\Omega$ (Typ.). Varying from 5 to $25k\Omega$ produces a change from 40 to 150ns. |  |  |  |

|     |        |         |                                             | Connects 5V power supply.                                                                                                                       |  |  |  |

| 16  | Vcc    | 5V      |                                             |                                                                                                                                                 |  |  |  |

### Electrical Characteristics

| lectrical Characteristics   | Symbol | Conditions                    | Test<br>point | Min   | Тур | Max.     | Unit  |

|-----------------------------|--------|-------------------------------|---------------|-------|-----|----------|-------|

| Item                        |        |                               | IM1           | 8     | 11  | 14       | Am    |

| Consumption current         | ICC    | \$1 <u>=0N</u>                |               |       |     |          |       |

| Mix ratio accuracy *        | K      | 1=200kHzVIN=100mVp-p<br>31=0N | VM1           | -10   | 0   | +10      | %     |

| MIX (BIID BUMBE)            | TI     | f=6MHz VIN=100mVpp<br>S1=0N   | VM1           | -13.0 | 0   | +13.0    | %     |

| Delay time accuracy 🗷       | T2     | f=10MHzVIN=100mVp-p<br>SI=0N  | VM1           | -22.0 | 0   | +22.0    | %     |

| Frequency characteristics   | FC     | -3dB VIN=25mVp-p<br>S1=OFF    | VM1           | 15    |     | <u> </u> | MHz   |

| Frequency Character         | 0.00   | S1=OFF f=200kHz               | VM1           | 7.5   | 9   | 10.5     | dB    |

| Gain                        | GAIN   | W+                            |               | 7     | 7   |          | mVp-p |

| Maximum input voltage range | KAMNIV | S1=OFF (=3MHz<br>THD≦5%       | VM1           | 300   |     |          | ]     |

x With the center value of mix ratio and delay time taken as K=0.230 and T=58ns.

The testing methods of mix ratio and delay time can be defined as follows,

Equalizer frequency characteristics on cosine equalizer is shown below:

$$H(\omega)=1-2K\times COS(\omega\Delta T)$$

Here S1 is OFF (Where K is set to Q), 200kHz and 6MHz gain are taken as  $G_0$ ,  $G_2$ , (dB). When a certain K is set, 200kHz and 6MHz gain are taken as  $G_1$ ,  $G_2$ , (dB).

K is Calculated through the following formula:

Delay time T1 is calculated through the following formula:  $T1 = \frac{1}{\omega} COS^{-1} \left( \frac{1 - 10^{MOx - Ga)/341}}{1 - 10^{MOx - Ga)/341}} \right)$

$$T1 = \frac{1}{\omega} \cos^{-1} \left( \frac{1 - 10^{\frac{1}{1}(G_1 - G_0)(30)}}{1 - 10^{\frac{1}{1}(G_1 - G_0)(30)}} \right)$$

For T2 test and with 10MHz characteristics, as the equalizer frequency characteristics have exceeded the gain peak, delay time when 10MHz goin are taken as G<sub>2</sub>, G<sub>3</sub>, (dB) is expressed by the following formula

$$72 = \frac{1}{a} \left\{ 2x - \cos^{-1} \left( \frac{1 - 10^{((GI - GS)/84)}}{1 - 10^{((GI - GS)/84)}} \right) \right\}$$

The calculating method for this delay time is applied when it is set around 50ns. For setting to any other dolay time, the frequency used to test the gain should be changed.

#### Transfer Characteristics

The cosine equalizer transfer characteristics expressed by the transfer function is indicated as follows, where transfer function is taken as H ( $\omega$ ) and delay time as  $\Delta T$ , then,

$$H(\omega)=1-2K\times COS(\omega\times\Delta T)$$

Calculation of delay time

T ADJI Pin current is taken as I, while delay time is obtained. ..

through the following formula:

$$\Delta t = \frac{5.4 \times 10^{-13}}{1}$$

As T ADJ1 pin voltage is 4.0V, the resistance to be connected to T ADJ1 pin is taken as R. We have

$$I = \frac{1.0}{R}$$

T ADJ1 pin voltage changes slightly according to the connected resistance value. However, ignoring this fluctuation, the relation between the delay time and R is given through the following formula:

$$\Delta t = \frac{6.4 \times 10^{-12}}{1.0} \times R$$

= 5.4×10<sup>-12</sup> × R

When R=10kΩ, We have

Calculation of mlx ratio K

Mix ratio calculation generally follows the following formula:

$$2K = \frac{11}{11+12}$$

Where  $11=11$  pin (K ADJ) current  $12=13$  pin (I REF) current

K ADJ1 pin, I REF pin voltage is approx. 1.2V.

As a  $12k\Omega$  is connected to I REF pin,  $12=100\mu\text{A}$ . K ADJ1 pin voltage changes slightly according to the connected resistance value. However, ignoring this fluctuation, the relation between the mix ratio and R is given through the following formula:

$$11 = \frac{1.2}{R}$$

Therefore, the relation between K and R is as follows:

For example, when  $R=12k\Omega$ , We have

$$K = \frac{0.6}{1.2 + 100 \times 10^{-4} \times 12 \times 10^{4}} = 0.25$$

## Electrical Characteristics Test Circuit

## Delay time vs. Setting resistance

## Mix ratio vs. Setting resistance

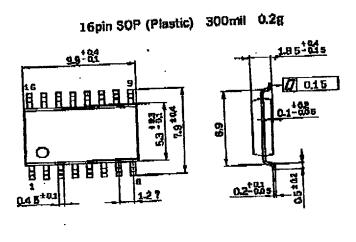

## Package Outline Unit: mm