# **DUAL INJECTION DRIVER**

## ADVANCE DATA

- WIDE SUPPLY RANGE (5.5 40V)

- VERY LOW ON RESISTANCE (TYP. 300mΩ).

- OUTPUT CURRENT UP TO 2A

- HIGH PERFORMANCE DIAGNOSTIC

- UNDERVOLTAGE DISABLE

- OVERVOLTAGE AND SHORT CIRCUIT PRO-TECTION

- CMOS COMPATIBLE CONTROL INPUTS

#### DESCRIPTION

The L9360 is a monolithic dual low side smart Power switch with DMOS power outputs, rated for operation in automotive environment.

It is intended to drive injectors connected to the positive battery voltage.

Thanks to its CMOS compatibility and its high performance diagnostic it is very well suited for handshake data with a microcontroller.

# Clipwatt 11 ORDERING NUMBER: L9360 Multiwatt 11 ORDERING NUMBER: L9360M SO20L (12+4+4) ORDERING NUMBER: L9360D

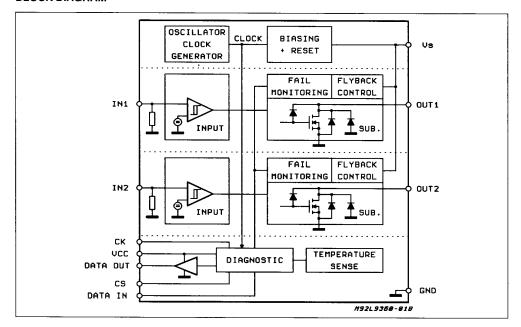

#### **BLOCK DIAGRAM**

October 1992

1/7

This is advanced information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol              | Parameter                               | Value      | Unit |

|---------------------|-----------------------------------------|------------|------|

| Vs                  | Supply Voltage                          | 40         | V    |

| locu                | Output Clamping Current                 | 2          | Α    |

| Eocl                | Output Dissipated Energy                | TBD        | J    |

| lor                 | Reverse Output Current (Pd ≤ 1W)        | -2         | Α    |

| Vcc                 | Stabilized Logic Supply Voltage         | 7          | V    |

| V <sub>CCrev</sub>  | Reverse Stabilized Logic Supply Voltage | -0,3       | V    |

| Vi                  | Input Voltage                           | 7          | V    |

| V <sub>Irev</sub>   | Reverse Input Voltage                   | -0.3       | V    |

| V <sub>Id</sub>     | Data Pin Voltage                        | 7          | V    |

| V <sub>Idrev</sub>  | Reverse Data Pin Voltage                | -0.3       | V    |

| T <sub>stg</sub>    | Storage Temperature                     | -55 to 150 | °C   |

| T <sub>j-case</sub> | Operating Junction Temperature          | -40 to 150 | °C   |

| T <sub>j-SD</sub>   | Thermal Overload Detection Temperature  | 150 to 165 | °C   |

| T <sub>i-SDH</sub>  | Thermal Threshold Hysteresis            | Typ. 20    | °C   |

| V <sub>ESD</sub>    | Protected According to MIL883C          | •          |      |

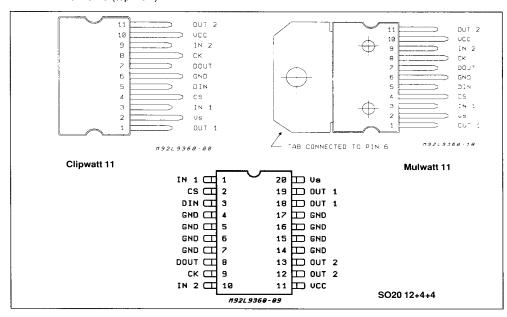

# PIN CONNECTIONS (top view)

#### THERMAL DATA

| Symbol                 | Parameter                              |              | Max. Value | Unit |

|------------------------|----------------------------------------|--------------|------------|------|

| R <sub>th j-amb</sub>  | Thermal resistance junction to ambient | Clipwatt 11  | 70         | °C/W |

| 1                      | 1                                      | Multiwatt 11 | 60         | °C/W |

| R <sub>th j-pins</sub> | Thermal resistance junction to pins    | SO20L        | 20         | °C/W |

| R <sub>th j-case</sub> | Thermal Resistance junction-case       | Multiwatt 11 | 3          | °C/W |

2/7

SGS-THOMSON MICROELECTRONICS

**ELECTRICAL CHARACTERISTICS** ( $V_S = 5.5$  to 25V,  $V_{CC} = 4.5$  to 5.5V,  $T_j = -40$  to 150°C unless otherwise specified; the voltage and currents are assumed positive, when oriented in the arrows direction shown in the application circuit diagram)

# **OUTPUT STAGE (EACH CHANNEL)**

| Symbol            | Parameter                  | Test Condition                                  | Min.   | Тур.              | Max.        | Unit      |

|-------------------|----------------------------|-------------------------------------------------|--------|-------------------|-------------|-----------|

| R <sub>DSON</sub> | On Resistance              | $VI = HIGH, V_S > 7V$<br>$V_I = HIGH, V_S < 7V$ |        | 300<br>400        | 600<br>1000 | $m\Omega$ |

| losc              | Out Short Circuit Current  |                                                 | 2      | 3                 | 4           | Α         |

| VocL              | Output Clamping Voltage    | 1 <sub>O</sub> = 0.2mA                          | 70     | 80                | 100         | ٧         |

| V <sub>ODG</sub>  | Output Internal Voltage    | V <sub>i</sub> = LOW, see Fig. 5                | 0.45Vs | 0.5V <sub>S</sub> | 0.55VS      | ٧         |

| R1 <sub>ODG</sub> | Internal Output Resistance | V <sub>I</sub> = LOW, see Fig. 5                |        | 20                |             | ΚΩ        |

#### SUPPLY VOLTAGE

| Symbol | Parameter                        | Test Condition            | Min. | Тур. | Max. | Unit |

|--------|----------------------------------|---------------------------|------|------|------|------|

| Iccoc  | DC Supply Current (VCC)          |                           |      | 1    | 2    | mA   |

| Is     | Supply Current (V <sub>S</sub> ) | VI1 = VI2 = LOW           |      | 4    | 7    | mA   |

|        |                                  | VI1 = VI2 = HIGH          |      | 16   | 25   | mA   |

|        |                                  | VI1 = VI2 = HIGH; VS= 14V |      | 10   |      | mA   |

#### **CONTROL INPUTS**

| Symbol           | Parameter                  | Test Condition                 | Min. | Тур. | Max. | Unit |

|------------------|----------------------------|--------------------------------|------|------|------|------|

| VIL              | Input LOW Level            | VCC = 5V                       |      | 2    | 1.5  | V    |

| VIH              | Input HIGH Level           | V <sub>CC</sub> = 5V           | 3.5  | 3.2  |      | V    |

| VITH             | Input Threshold Hysteresis |                                | 1    | 1.2  | 1.6  | V    |

| td <sub>ON</sub> | Input to Out Delay Time    | $R_L = 14\Omega; V_S = 14V$    |      | 1.5  | 10   | μs   |

| ton              | Output Rise Time           | $R_L = 14\Omega$ ; $V_S = 14V$ |      | 3.5  | 10   | μs   |

| tdOFF            | Input to Out Delay Time    | $R_L = 14\Omega; V_S = 14V$    |      | 2    | 10   | μs   |

| tor              | Output Fall Time           | $R_L = 14\Omega; V_S = 14V$    |      | 1.2  | 10   | μs   |

| Rin              | Input Resistance           |                                | 100  | 200  | 300  | KΩ   |

# **DIAGNOSTIC & PROTECTIONS**

| Symbol           | Parameter                                              | Test Condition                      | Min. | Тур. | Max. | Unit |

|------------------|--------------------------------------------------------|-------------------------------------|------|------|------|------|

| V <sub>CSL</sub> | CS Input LOW Level                                     | Vcc = 5V                            |      | 2    | 1.5  | ٧    |

| Voil             | Data Input LOW Level                                   | Vcc = 5V                            |      | 2    | 1.5  | V    |

| V <sub>CKL</sub> | CK Input LOW Level                                     | Vcc = 5V                            |      | 2    | 1.5  | V    |

| Vcsh             | CS Input HIGH Level                                    | Vcc = 5V                            | 3.5  | 3.2  |      | V    |

| V <sub>DIH</sub> | Data Input HIGH Level                                  | Vcc = 5V                            | 3.5  | 3.2  |      | V    |

| V <sub>CKH</sub> | CK Input HIGH Level                                    | Vcc = 5V                            | 3.5  | 3.2  |      | V    |

| V <sub>DOL</sub> | Data Output LOW                                        | I <sub>DO</sub> = 1mA               |      | 0.2  | 0.5  | V    |

| $V_{DOH}$        | Data Output HIGH                                       | $I_{DO} = -200 \mu A; V_{CC} = 5 V$ | 4    |      |      | V    |

| I <sub>DOL</sub> | Data Output Leakage Current                            | V <sub>DO</sub> = V <sub>CC</sub>   |      | 1    | 10   | μΑ   |

| RLOL             | External Recognized Resistance for Open Load Detection | See fig. 5                          |      | 10   |      | KΩ   |

| Voed             | Output Excessive Drop Thresh                           | See fig. 5                          | 2    | 2.5  |      | V    |

| Ross             | Output Resistance to GND for Short to GND Detection    | See fig. 5                          |      | 5    |      | ΚΩ   |

| tposg            | Output Short to GND Switch OFF                         |                                     |      | 50   | 150  | μs   |

| t <sub>ES</sub>  | Error Recognition Time for the Stochastic Error        | See fig. 4                          |      | 5    |      | μs   |

| ts               | Time for Error Recognized                              | See fig. 4                          |      | 50   | 150  | μs   |

| fosg             | Internal Oscillator Frequency                          |                                     |      | 500  |      | KHz  |

| folk             | External Clock Frequency                               |                                     |      |      | 1    | MHz  |

#### CIRCUIT DESCRIPTION

The device is realized in the BCD100 technology which combines CMOS logic, bipolar components and as output stages DMOS transistors which can withstands 100V drain-source voltage.

Via the CMOS compatible inputs (IN1, IN2) the power DMOS can be switched ON and OFF independently from each other. All functions of the device are guaranteed between 5.5V and 40V supply voltage. Between 5.5 to to 7V supply voltage the typical drain-source resistance increases from  $250m\Omega$  to  $500m\Omega$  typ. With this limitation a charge pump could be avoided.

For V<sub>S</sub> below 5.5V the device can be disabled. Both outputs are switched OFF independently from the input status. The data output is switched to tristate. In the undervoltage mode ( $V_S < 5.5V$ ) a possible failure status was reset. Below 3V the

chip functions are not defined. The device is protected against short circuit to supply but not protected against thermal overload due to security reason. Only via the diagnostic the system is informed about a thermal overload and the other possible failure modes which are described separately. A quasi digital filter avoids that short time stochastic failures are stored in the diagnostic register.

When a short circuit to the supply is recognized and stored in the diagnostic register the output transistor is switched OFF. The output can be switched ON again only via a new input pulse.

The device needs a second supply voltage (V<sub>CC</sub>) which comes normally from the same supply as for the  $\mu$ C.

This voltage supplies the logic and avoides problems whith logic level disturbances.

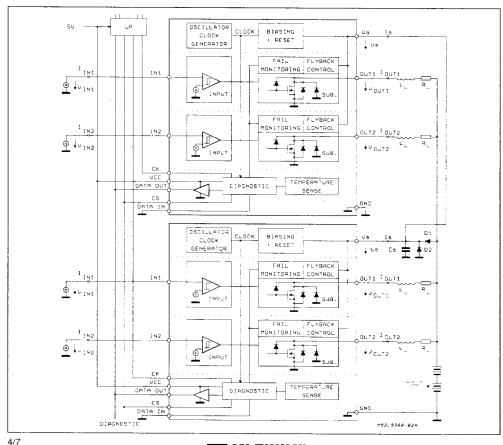

Figure 1: Two Chip Solution To Drive Four Valves: Parallel Data Out

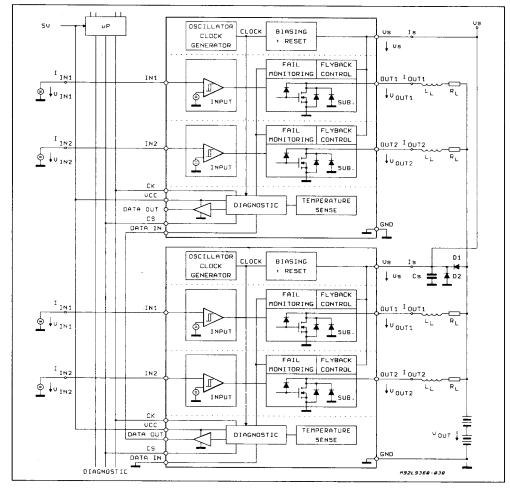

Figure 2; Two Chip Solution To Drive Four Valves: Serial Data Out

## **DIAGNOSIS**

The diagnosis is able to detect the following states:

- OUTPUT SHORT-CIRCUIT TO BATTERY (SUPPLY VOLTAGE)

- OUTPUT SHORT-CIRCUIT TO GROUND

- OPEN LOAD

- THERMAL OVERLOAD

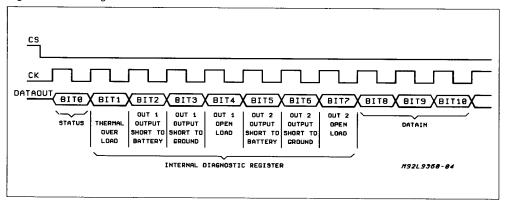

## **READING OF THE DIAGNOSIS REGISTER**

A low signal at the chip select CS-input and a positive edge of the clock signal at CK-input starts

the reading of the diagnosis register.

The serial diagnosis register (Ref. to figure 3) is loaded synchronously with CK-signal at DATAOUT and new data fed through DATAIN as long as CS is "LOW".

After the nineth clock cycle the first DATAIN information is present at DATAOUT. The STATUS BIT 0 is "HIGH if one diagnosis register is set or the DATAIN-input is "HIGH", hence the presence of a failure can be detected by BIT 0.

The positive edge at CS clears the diagnosis register. During reading the diagnosis register (CS = "LOW") the single bits cannot be changed.

SGS-THOMSON

5/7

Figure 3: Serial Diagnostic

# CASCADING OF SEVERAL INJECTOR DRIVERS

The possibility is given to read the diagnosis registers of several injector drivers via one diagnosis bus. Additionally the user can choose between two versions.

#### 1. (figure 1):

The CK and DATAOUT terminals of the injector drivers are connected in parallel to the diagnosis bus. Each IC is provided with a separate CS-wire. The DATAIN-input is connected to GND.

### 2. (figure 2)

The CK and CS terminals are connected to the parallel diagnosis bus. The data line is connected in series through the terminals DATAIN and DATAOUT or each single IC. The DATAIN input of the first IC must be connected to GND

The first version allow to read the desired diagnosis register immediately after the CS-signal is applied. in the other version all diagnosis registers have to be read one after the other whereby only a 3-wire bus is sufficient. In the other case each IC needs a separate CS-lead to the processor.

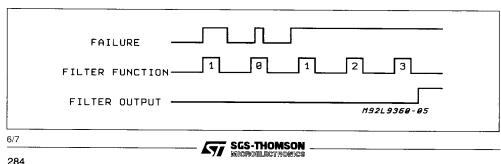

#### **FAILURE DETECTION**

Except the overtemperature signal all failure sig-

nals are filtered before setting the corresponding BIT in the diagnosis register.

The filter checks whether the failure signal is present during three times running the measure cycle within Ts. Spikes shorter than tes are ignored.

#### THERMAL OVERLOAD

If the chip exceeds T<sub>JSB</sub> the "thermal overload"-BIT is set. Because the transistors are not switched off the element can be thermally destroyed if the control does not set the IN1 and IN2 inputs to "LOW".

# OUTPUT SHOTR-CIRCUIT TO BATTERY (BIT2/5)

The output currents  $l_{01/2}$  are internally limited to 3A (typ). If the output current reaches the current limit the power DMOS leaves the resistive region and changes to the saturation region.

Consequently the drain source voltage increases and after reaching of typ. 2V the "output-short-circuit to battery" BIT is set and the power DMOS are switched off.

Repetitive control of  $IN_1$  and  $IN_2$  inputs (low-high sequence) switches on the DMOS again. But the bit in the diagnosis register is not resetted.

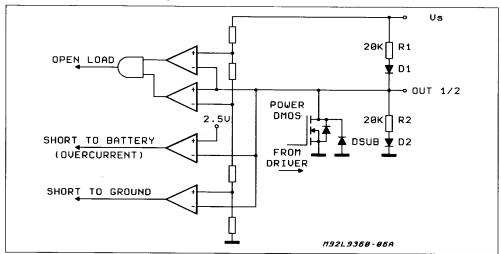

Figure 5: Principle Of Internal Diagnostic Detection

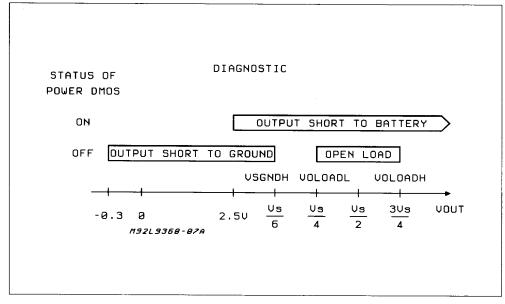

# OUTPUT SHORT-CIRCUIT TO GND (BIT3/6) AND OPEN LOAD (BIT4/9).

In case of the switched off power DMOS the internal 20K resistors  $R_1$  and  $R_2$  divide the output voltage to half the supply voltage without load (fig.5).

A window comparator detects the output voltage and sets the "open load" BIT if the voltage deviates more than +/-0.25Vs from 0.5Vs. But if the output voltage decreases below 0.16Vs the "output short circuit to ground" BIT is set.

Figure 6: Diagnostic Detection Voltage Range

7/7