# SONY

# CXD2526AQ/AR

# **Audio Skip Guard Memory Controller**

## Description

The CXD2526AQ/AR is a memory controller designed for audio skip guard memory control configurations in MD systems. The CXD2526AQ/AR controls MD-format signal encoding/decoding as well as main data, C2PO data, subdata, system data for the microcontroller, and the external I/O status.

#### **Features**

- Data and C2PO FIFO function. External RAM for C2PO is not needed.

- Subdata buffering function. Subdata can be input and output through an external subdata interface.

- TOC data buffering function.

- All RAM data can be read/written via a serial interface for the microcontroller.

- DRAM refresh function (for both normal and low power mode).

- External RAM address space can be expanded up to 32M-bit

(2 × 16M DRAMs: 1783 sectors max.)

(When using SRAM, expansion up to 8 M-bit is possible.)

- RAM data capacity and remaining capacity calculation and comparison functions.

- C2PO/external input monitor function.

#### Absolute Maximum Ratings (Ta=25°C)

Supply voltage

Input voltage

Volt

## **Recommended Operating Conditions**

Supply voltage

Operating temperature

Topr

43.0 to +5.5

C

#### Input/Output Capacitance

• Input pin C<sub>I</sub> 9 (Max.) pF

• I/O pins Cyo 11 (Max.) pF When high impedance

• Output pin Cout 11 (Max.) pF

Note) Measurement conditions: VDD=Vi=0V

f=1MHz

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

#### Structure

Silicon gate CMOS IC

## **Application**

Mini Disc

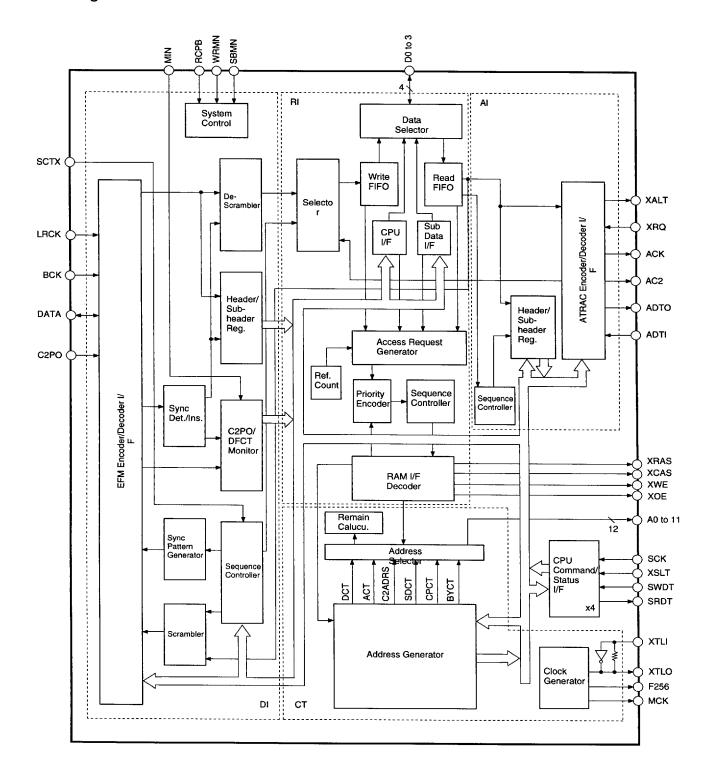

## **Block Diagram**

#### **Description of Each Block**

The CXD2526A basically consists of four blocks.

#### (1) DI block

This is the interface block for the EFM encoder/decoder.

During playback, the input data from the EFM decoder is synchronized internally in sector units by the synchronization detection circuit. Synchronization is not only for input sync pattern detection but also is protected against detection errors by the insertion circuit; in addition, synchronization is controlled so that rapid recovery is possible even if synchronization is lost due to a track jump, etc. If write mode is in effect, input data and C2PO data that have passed through the descrambler circuit are sent to the RI block and are written to RAM based on the address generated by the counter within the CT block.

In addition, this block monitors C2PO data and MIN input pin, and passes the signals to the controller. Knowing the number and position of errors makes more sophisticated control possible.

During recording, this block encodes MD-format sector data. This block generates the sync byte, reads the header time from the register, reads the necessary data from memory, and then passes the data to the EFM encoder via the scrambler circuit. There are three types of sector data and, depending on the settings of the microcontroller, linking data, subdata, and main data can be generated.

## (2) RI block

This is the RAM interface block.

This block accepts I/O requests from each of the other blocks and controls RAM access according to a priority ranking. There are five blocks that issue data I/O access requests to RAM; their priority rankings are as follows:

- 1. Di block

- 2. Al block

- 3. Refresh (in DRAM mode)

- 4. CPU RAM access

- 5. Subdata access via the external interface

As a result, access to the playback/recording data from the disc has the highest priority, while CPU and external subdata interface data access may be forced to wait due to the generation of internal requests.

## (3) CT block

This block contains the counters that generate addresses in RAM. There are five types of counters:

- 1. DCT Generates addresses for read/write data for the EFM encoder/decoder.

- 2. ACT Generates addresses for transfer data for the ATRAC encoder/decoder.

- 3. CCT Generates addresses for CPU memory access.

- 4. SDCT Generates addresses for read/write data for the EFM encoder/decoder.

Also generates addresses for memory access by the external subdata interface. This counter is useful for reading/writing subdata.

5. BCT Performs the transfer data count operations.

In addition, this block also provides functions that use the DCT and ACT to calculate C2PO addresses, monitor the data capacity, and compare whether the data capacity is greater or smaller than the specified threshold value.

#### (4) Al block

This is the interface block for the ATRAC encoder/decoder. 8382383 0009141 537 MI

This block performs I/O with the ATRAC encoder/decoder and issues requests to the RI block to exchange data.

## **Pin Configuration**

```

(60)(59)(58)(57)(56)(55)(54)(53)(52)(51)(50)(49)(48)(47)(46)(45)(44)(43)(42)(41)

OX

SCAS

RMSL

TEST

Vss

XTLI

XTLO

F256

₩Ç

SRDY

×₩

AC2 (40)

A10

ACK (39)

XWE

ADTO (38)

XRAS

ADTI

(65)

A11

(66)

A9

ZZ0

A0

ZZ1

Α1

A2

BUSY

CXD2526AR

(70)

АЗ

VDD

VDD

TXST

A8

BTOV4

Α7

ERWR

A6

OVER

A5

UNDER

A4

MEMEMP

A12

MEMFUL

A13

MDSY

A14

XINT

(80)

A15

SBMN (21)

WRMN

C2PO

DATA

Vss

TEST

XRST

MIN

SRDT

SWDT

XSLT

2(3(4)5)6(7)8(9)(10(11)(12)(13)(14)(15)(16)(17)(18)(19)(20)

XTLO

ΙX

₩ĊĶ

ĄĊK

XWT

XWE

ADTO (40)

(65)

(66)

XRAS

ADTI

(67)

A11

XALT

(68)

Α9

ZZ0

A0

ZZ1

Α1

ZZ2

A2

BUSY

АЗ

VDD

CXD2526AQ

VDD

TXST

A8

BTOV4

Α7

ERWR

OVER

A6

A5

UNDER

A4

MEMEMP

MEMFUL (26)

A12

MDSY (25)

(80)

A13

BCK

C2PO

DATA

VSS

TEST

XRST

3 (4 (5 (6 (7 ) 8 (9 ) 10 (11 ) 12 (13 (14 ) 15 (16 ) 17 (18 (19 ) 20 (21 ) 22 (23 ) (24 )

```

## **Pin Description**

|     |    | · · · · · · · · · · · · · · · · · · · |          |            |                                                                                                     |

|-----|----|---------------------------------------|----------|------------|-----------------------------------------------------------------------------------------------------|

| Pin |    | Symbol                                | 1/       | 0          | Pin Description                                                                                     |

| Q   | R  |                                       |          |            | ·                                                                                                   |

| 1   | 79 | A14                                   | 0        | H, L       | When RMSL is high, SRAM address bus A14: when RMSL is low, WFFUL. *1                                |

| 2   | 80 | A15                                   | 0        | H, L       | When RMSL is high, SRAM address bus A15: when RMSL is low, RFEMP. *2                                |

| 3   | 1  | A16                                   | 0        | H, L       | When RMSL is high, SRAM address bus A16: when RMSL is low, WFOVF. *3                                |

| 4   | 2  | A17                                   | 0        | H, L       | When RMSL is high, SRAM address bus A17: when RMSL is low, WDTM. *4                                 |

| 5   | 3  | A18                                   | 0        | H, L       | When RMSL is high, SRAM address bus A18: when RMSL is low, ZERO. *5                                 |

| 6   | 4  | A19                                   | 0        | H, L       | When RMSL is high, SRAM address bus A19: when RMSL is low, MDTST. *6                                |

| 7   | 5  | A20                                   | 0        | H, L       | When RMSL is high, SRAM address bus A20: when RMSL is low, CMPSY. *7                                |

| 8   | 6  | LRCK                                  | ı        |            | LRCK (=Fs) input from the EFM encoder/decoder.                                                      |

| 9   | 7  | ВСК                                   | 1        |            | BCK (=64Fs) input from the EFM encoder/decoder. *8                                                  |

| 10  | 8  | C2PO                                  | I        |            | C2PO input from the EFM encoder.                                                                    |

| 11  | 9  | DATA                                  | I/O      | H, L       | When playback mode, data input from EFM decoder; when recording mode, data output to EFM encoder.   |

| 12  | 10 | Vss                                   |          |            | Connect to GND.                                                                                     |

| 13  | 11 | TEST                                  | ı        |            | Test pin. Fix low.                                                                                  |

| 14  | 12 | XRST                                  | 1        |            | Reset input. (Reset when low.)                                                                      |

| 15  | 13 | MIN                                   | 1        |            | Monitor signal input for external input. Input the signal to be monitored. *9                       |

| 16  | 14 | SRDT                                  | 0        | H, Z,<br>L | Microcontroller serial data output. High impedance when the CXD2526A read resister is not selected. |

| 17  | 15 | SWDT                                  |          |            | Microcontroller serial data input.                                                                  |

| 18  | 16 | XSLT                                  | _        |            | Microcontroller serial data latch signal input. Latched when fall time.                             |

| 19  | 17 | SCK                                   |          |            | Microcontroller serial data shift clock input                                                       |

| 20  | 18 | SCTX                                  | _        |            | Data output enable signal input in recording mode. Enabled when high.                               |

| 21  | 19 | RCPB                                  | ı        |            | Low: playback mode; High: monitor recording mode.                                                   |

| 22  | 20 | WRMN                                  | ı        |            | High: write mode; low: monitor mode.                                                                |

| 23  | 21 | SBMN                                  | ı        |            | High: records input signal based on SDCT; Low: records based on DCT.                                |

| 24  | 22 | XINT                                  | 0        | H, L       | Input data MD sync detection signal.                                                                |

| 25  | 23 | MDSY                                  | 0        | H, L       | Interrupt request output. Low when interrupt status is generated.                                   |

| 26  | 24 | MEMFUL                                | 0        | H, L       | High when the main data area becomes full.                                                          |

| 27  | 25 | МЕМЕМР                                | 0        | H, L       | High when the main data area is empty.                                                              |

| 28  | 26 | UNDER                                 | 0        | H, L       | High when RMS < THUND.                                                                              |

| 29  | 27 | OVER                                  | 0        | H, L       | High when RMS ≥ THOVR                                                                               |

| 30  | 28 | ERWR                                  | 0        | H, L       | High when the data from C2PO is written to RAM.                                                     |

| 31  | 29 | BTOV4                                 | 0        | H, L       | High when BCT ≥ 400 (Hex).                                                                          |

| 32  | 30 | TXST                                  | 0        | H, L       | High during data transfer.                                                                          |

| 33  | 31 | V <sub>DD</sub>                       |          |            | System power supply.                                                                                |

| 34  | 32 | BUSY                                  | 0        | H, L       | High during RAM access.                                                                             |

|     |    |                                       | <u> </u> |            |                                                                                                     |

| Pin I | No. |        |     |              |                                                                                                                             |

|-------|-----|--------|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------|

| a     | R   | Symbol | 1/0 | <sup>)</sup> | Pin Description                                                                                                             |

| 35    | 33  | ZZ2    | ı   |              | Test pin. Fix low.                                                                                                          |

| 36    | 34  | ZZ1    | 1   |              | Test pin. Fix low.                                                                                                          |

| 37    | 35  | ZZ0    | ı   |              | Test pin. Fix low.                                                                                                          |

| 38    | 36  | XALT   | 0   | H, L         | Data ready or latch signal for the ATRAC encoder/decoder.                                                                   |

| 39    | 37  | ADTI   | 1   |              | Data input from the ATRAC encoder/decoder.                                                                                  |

| 40    | 38  | ADTO   | 0   | H, L         | Data output to the ATRAC encoder/decoder.                                                                                   |

| 41    | 39  | ACK    | 0   | H, L         | Data transfer clock output to the ATRAC encoder/decoder.                                                                    |

| 42    | 40  | AC2    | 0   | H, L         | C2PO output for output data to the ATRAC encoder/decorder.                                                                  |

| 43    | 41  | XRQ    | ı   |              | Data request signal input from the ATRAC encoder/decorder.                                                                  |

| 44    | 42  | SDCK   | ı   |              | External subdata interface shift clock input.                                                                               |

| 45    | 43  | SBDT   | 1/0 | H, L         | In playback mode, external subdata interface data output; in recording mode, data input.                                    |

| 46    | 44  | хwт    | 0   | H, L         | External subdata interface wait signal. When low, the clock for reading new data must not be sent.                          |

| 47    | 45  | SRDY   | 0   | H, L         | External subdata interface access enable signal. When low, if the clock for reading/writing subdata is sent, it is ignored. |

| 48    | 46  | мск    | 0   | H, L         | 128Fs output.                                                                                                               |

| 49    | 47  | F256   | 0   | H, L         | 256Fs output.                                                                                                               |

| 50    | 48  | XTLO   | 0   |              | System clock output. (XTLI inverted output)                                                                                 |

| 51    | 49  | XTLI   | ı   |              | System clock input. Input (512Fs=22.5792MHz)                                                                                |

| 52    | 50  | Vss    |     |              | Connect to GND.                                                                                                             |

| 53    | 51  | TEST   | ı   |              | Test pin. Fix low.                                                                                                          |

| 54    | 52  | RMSL   |     |              | External RAM select. High: SRAM; low: DRAM.                                                                                 |

| 55    | 53  | ERR    | 1/0 | H, L         | C2PO I/O when EXTC2R, bit 4 of write register WR04 is 1. When 0, open.                                                      |

| 56    | 54  | D7     | 1/0 | H, L         | When RMSL is high, SRAM data bus D7; when low, open.                                                                        |

| 57    | 55  | D4     | 1/0 | H, L         | When RMSL is high, SRAM data bus D4; when low, open.                                                                        |

| 58    | 56  | D0     | I/O | H, L         | RAM data bus D0.                                                                                                            |

| 59    | 57  | D1     | I/O | H, L         | RAM data bus D1.                                                                                                            |

| 60    | 58  | D3     | 1/0 | H, L         | RAM data bus D3.                                                                                                            |

| 61    | 59  | D2     | 1/0 | H, L         | RAM data bus D2.                                                                                                            |

| 62    | 60  | XCAS   | 1/0 | H, L         | When RMSL is high, RAM data bus D6; when low, CAS output for DRAM.                                                          |

| 63    | 61  | XOE    | 0   | H, L         | RAM output enable.                                                                                                          |

| 64    | 62  | A10    | 0   | H, L         | RAM address bus A10.                                                                                                        |

| 65    | 63  | XWE    | 0   | H, L         | RAM write enable.                                                                                                           |

| 66    | 64  | XRAS   | 1/0 | H, L         | When RMSL is high, data bus D5; when low, RAS output for DRAM.                                                              |

| Pin | No. | Cumbal | 17  | _    | Din Deservintion                                                   |

|-----|-----|--------|-----|------|--------------------------------------------------------------------|

| Q   | R   | Symbol | 17' | 0    | Pin Description                                                    |

| 67  | 65  | A11    | 0   | H, L | RAM address bus A11.                                               |

| 68  | 66  | A9     | 0   | H, L | RAM address bus A9.                                                |

| 69  | 67  | A0     | 0   | H, L | RAM address bus A11. *12                                           |

| 70  | 68  | A1     | 0   | H, L | RAM address bus A1.                                                |

| 71  | 69  | A2     | 0   | H, L | RAM address bus A2.                                                |

| 72  | 70  | А3     | 0   | H, L | RAM address bus A3.                                                |

| 73  | 71  | VDD    |     |      | System power suypply.                                              |

| 74  | 72  | A8     | 0   | H, L | RAM address bus A8.                                                |

| 75  | 73  | A7     | 0   | H, L | RAM address bus A7.                                                |

| 76  | 74  | A6     | 0   | H, L | RAM address bus A6.                                                |

| 77  | 75  | A5     | 0   | H, L | RAM address bus A5.                                                |

| 78  | 76  | A4     | 0   | H, L | RAM address bus A4.                                                |

| 79  | 77  | A12    | 0   | H, L | When RMSL is high, RAM address bus A12; when low, CS output. *10   |

| 80  | 78  | A13    | 0   | H, L | When RMSL is high, RAM address bus A13; when low, SYOK output. *11 |

- \*1 WFFUL : High if write FIFO buffer becomes full.

- \*2 RFEMP: High if write FIFO buffer becomes empty.

- \*3 WFOVF: High if write FIFO buffer overflows.

- \*4 WDTM : Outputs the window timing within the DI block.

- \*5 ZERO : High when BCT=0.

- \*6 MDTSC: High for input data header sectors #00 to 1F; low in all other cases.

- \*7 CMPSY: Insertion sync timing.

- \*8 Polarity is set by WR0E LRSL.

- \*9 MIN can be read by RR0F.

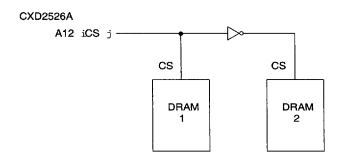

- \*10 CS: DRAM chip select in the case of using two memory chips for WR04. (Refer to the figure below)

- \*11 Refer to the read resistrer RR01 SYOK for SYOK.

- \*12 This pin is used for DRAM. Leave this pin open if SRAM is selected when RMSL=high. In this case, the lowest bit of the address is used from A1.

**Exampled of two DRAMs used**

#### **Electrical Characteristics**

#### 1. DC characteristics

#### DC characteristics 1

$(V_{DD}=3.0\pm0.3V, Vss=0V, Topr=-20 to +75^{\circ}C)$

|                      | Item                      |         | Conditions  | Min.    | Тур. | Max.   | Unit | Applicable pins |

|----------------------|---------------------------|---------|-------------|---------|------|--------|------|-----------------|

| Input                | High level input voltage  | ViH (1) |             | 0.7Vpd  |      |        | ٧    | *1              |

| voltage (1)          | Low level input voltage   | VIL (1) |             |         |      | 0.3Vpp | ٧    | 1               |

| Input<br>voltage (2) | High level input voltage  | Vн (2)  |             | 1.8     |      |        | ٧    | *2              |

|                      | Low level input voltage   | VIL (2) |             |         |      | 0.5    | ٧    | 1 2             |

| Input                | High level input voltage  | Vін (3) |             | 0.8Vpd  |      |        | ٧    | *3              |

| voltage (3)          | Low level input voltage   | VIL (3) |             |         |      | 0.2VDD | ٧    |                 |

| Output               | High level output voltage | Vон (4) | loн=-1mA    | VDD-0.8 |      |        | μΑ   | *4              |

| voltage (4)          | Low level output voltage  | Vol (4) | loL=-2mA    |         |      | 0.4    | μΑ   |                 |

| Input leak current   |                           | IιL     |             | -10     |      | 10     | μΑ   | *5              |

|                      |                           | IIL.    | VIN=VSS=VDD | -40     |      | 40     | μΑ   | *6              |

| Tri-state out        | put leak current          | loz     |             | -40     |      | 40     | μΑ   | *7              |

## DC characteristics 2

(VDD=4.0±5.5V, Vss=0V, Topr=-20 to +75°C)

|                      | Item                          |                     | Conditions  | Min.               | Тур. | Max.   | Unit | Applicable pins |

|----------------------|-------------------------------|---------------------|-------------|--------------------|------|--------|------|-----------------|

| Input                | High level input voltage      | Vıн (1)             |             | 0.7V <sub>DD</sub> |      |        | V    | *1              |

| voltage (1)          | Low level input voltage       | Vı∟ (1)             |             |                    | -    | 0.3Vdd | ٧    |                 |

| Input                | High level input voltage      | ViH (2)             |             | 2.2                |      |        | ٧    | *2              |

| voltage (2)          | Low level input voltage       | VIL (2)             |             |                    |      | 0.8    | ٧    | 1 2             |

| Input<br>voltage (3) | High level input voltage      | V <sub>IH</sub> (3) |             | 0.8Vpp             |      |        | ٧    | *3              |

|                      | Low level input voltage       | VIL (3)             |             |                    |      | 0.2VDD | V    | 1 '3            |

| Output               | High level output voltage     | Vон (4)             | loн=-1mA    | VDD-0.8            | -    |        | μA   | *4              |

| voltage (4)          | Low level output voltage      | Vol. (4)            | loL=-2mA    |                    |      | 0.4    | μA   | 4               |

| Input leak current   |                               | Iı∟                 |             | -10                |      | 10     | μA   | *5              |

|                      |                               | IIL.                | VIN=VSS=VDD | -40                |      | 40     | μΑ   | *6              |

| Tri-state out        | Tri-state output leak current |                     |             | -40                |      | 40     | μΑ   | *7              |

## Applicable pins

- \*1 LRCK, BCK, C2PO, DATA, TEST, SWDT, XSLT, SCK, SCTX, RCPB, WRMN, SBMN, ZZ2, ZZ1, ZZ0, ADTI, XRQ, SDCK, SBDT, TEST, RMSL, ERR

- \*2 D7, XRAS, XCAS, D4, D3, D2, D1, D0

- \*3 XRST, MIN

- \*4 A20 to A0, SRDT, XINT, MDSY, ADTO, AC2, XWT, SRDY, XOE, XWE, D7, XRAS, XCAS, D4, D3, D1, D0, MCK, F256, MEMFUL, MEMEMP, UNDER, OVER, ERWR, BTOV4, TXST, BUSY, DATA, XALT, ACK, SBDT, ERR

- \*5 LRCK, BCK, C2PO, TEST, SWDT, XSLT, SCK, SCTX, RCPB, WRMN, SBMN, ZZ2, ZZ1, ZZ0, ADTI, SDCK, TEST, RMSL

- \*6 DATA, XRQ, SBDT, ERR

💻 8385383 0004746 077 🖿

## 2. AC characteristics

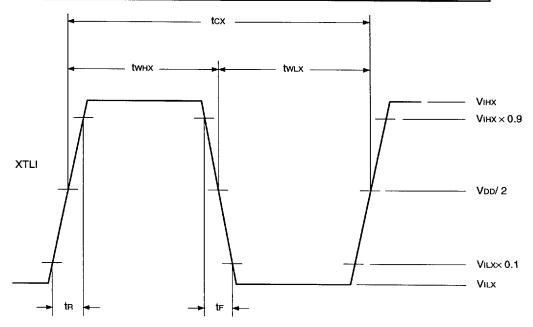

## (1) XTLI pin

## • When using self-oscillation

(Topr=-20 to +75\*C, VDD=3.0 to 5.5V)

| ltem                  | Symbol | Min. | Тур.    | Max. | Unit |

|-----------------------|--------|------|---------|------|------|

| Oscillation frequency | fmax.  | 20   | 22.5792 | 25   | MHz  |

## • When inputting a pulse to XTLI

(Topr=-20 to +75°C, VDD=3.0 to 5.5V)

| ltem                   | Symbol    | Min.            | Тур. | Max.   | Unit |

|------------------------|-----------|-----------------|------|--------|------|

| High-level pulse width | twnx      | 20              |      | 25     | ns   |

| Low-level pulse width  | twLx      | 20              |      | 25     | ns   |

| Pulse cycle            | tcx       | 40              |      | 50     | ns   |

| Input high level       | Vінх      | 0.7 <b>V</b> pd |      |        | ٧    |

| Input low level        | VILX      |                 |      | 0.3Vpd | V    |

| Rise time<br>Fall time | ta,<br>tr |                 |      | 10     | ns   |

• When inputting a sine wave to the XTLI pin via a capacitor

(Topr=-20 to +75°C, VDD=3.0 to 5.5V)

| Item            | Symbol | Min. | Тур. | Max.    | Unit         |

|-----------------|--------|------|------|---------|--------------|

| Input amplitude | Vı     | 2.0  |      | VDD+0.3 | <b>V</b> p-p |

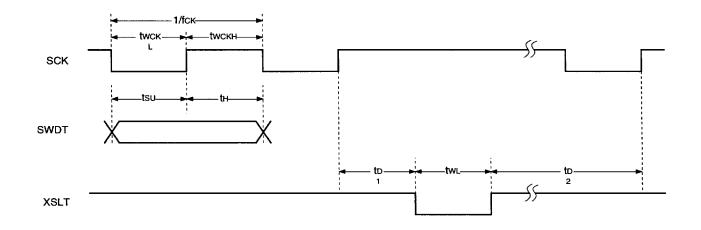

(2) SCK, SWDT and XSLT pins

(V<sub>DD</sub>=3.0 to 5.5V, Vss=0V, Topr=-20 to +75°C)

| ltem                  | Symbol        | Min. | Тур. | Max. | Unit |

|-----------------------|---------------|------|------|------|------|

| Clock frequency       | fск           | 100  |      | 2.5  | MHz  |

| Clock pulse width (L) | twckL         | 0.2  |      | 120  | μs   |

| Clock pulse width (H) | <b>t</b> wckh | 0.2  |      | 120  | μs   |

| Setup time            | <b>t</b> su   | 200  |      |      | ns   |

| Hold time             | tн            | 200  |      |      | ns   |

| Delay time 1          | <b>t</b> D1   | 200  |      |      | ns   |

| Delay time 2          | <b>t</b> D2   | 200  |      |      | ns   |

| Latch pulse width     | twL           | 400  |      |      | ns   |

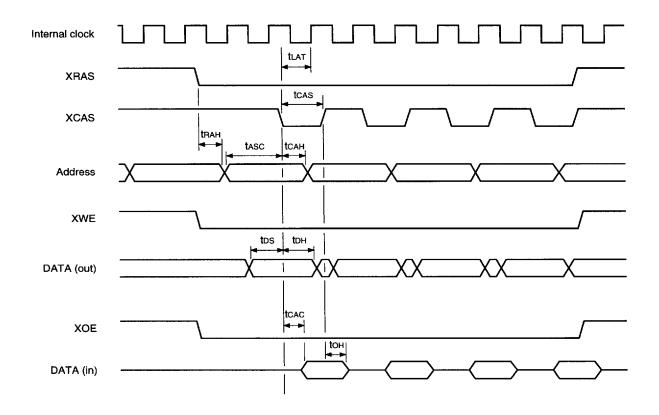

## 3. DRAM interface (VDD=3.0V to 5.5V; external load: 40pF or less)

DRAM that can be connected to the CXD2526AQ/AR are those that can handle a  $\times$  4-bit data bus, high-speed page mode (early write cycle), and CAS before RAS refresh. For the access times, refer to the timing chart shown above.

| tcas     70     —     —       trah     75     —     —       tasc     65     —     —       tcah     75     —     —       tdh     65     —     —       tds     60     —     —       toh     50     —     —       tcac     —     40 |              | Min. | Typ.         | Max.         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|--------------|--------------|

| tasc     65     —     —       tcah     75     —     —       tdh     65     —     —       tds     60     —     —       toh     50     —     —       tcac     —     40                                                             | tcas         | 70   | _            | <u> </u>     |

| tcah         75         —         —           tdh         65         —         —           tds         60         —         —           toh         50         —         —           tcac         —         40                   | trah         | 75   | <u>—</u>     | _            |

| tDH         65         —         —           tDS         60         —         —           tOH         50         —         —           tCAC         —         40                                                                 | tasc         | 65   |              | <del>_</del> |

| tos         60         —         —           toн         50         —         —           tcac         —         40                                                                                                              | <b>t</b> cah | 75   | <del>-</del> |              |

| toн 50 — —<br>tcac — 40                                                                                                                                                                                                          | tон          | 65   |              |              |

| tcac — — 40                                                                                                                                                                                                                      | tos          | 60   | _            |              |

|                                                                                                                                                                                                                                  | <b>t</b> on  | 50   | <del></del>  | <del>_</del> |

|                                                                                                                                                                                                                                  | tcac         | _    | _            | 40           |

| tlat 50 70 85                                                                                                                                                                                                                    | <b>t</b> lat | 50   | 70           | 85           |

(Unit: ns)

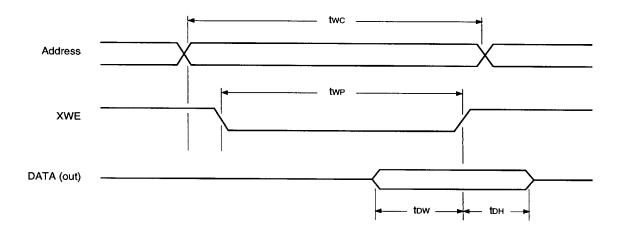

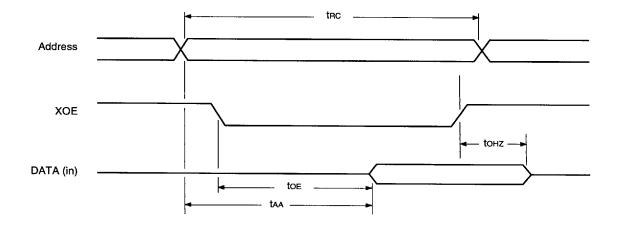

## 4. SRAM interface (VDD=3.0 to 5.5V; external load: 40pF or less)

|             | MIn. | Тур. | Max.        |

|-------------|------|------|-------------|

| twc         | 150  |      | -           |

| twp         | 100  | _    | _           |

| <b>t</b> ow | 60   | _    | <del></del> |

| tон         | 0    | _    | <del></del> |

| <b>t</b> RC | 150  |      |             |

| toe         |      |      | 70          |

| <b>t</b> AA |      |      | 150         |

| tонz        | _    | _    | 50          |

(Unit: ns)

#### **Description of Functions**

#### 1. Basic Operation

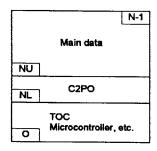

#### (1) Partitioned use of memory

In order to share memory resources effectively, memory is generally partitioned as shown below. The memory size is N. NU and NL are set by WR10 and WR11. The main data size is N-NU.

During playback mode, the C2PO area must be at least 1/8 the size of the main data area. It is also necessary to select NU and NL so that the following equation is true:

$$NL \le NU - \frac{N - NU}{8} = \frac{9NU - N}{8}$$

The area from 0 to NL-1 can be used as extended RAM for the microcontroller for subdata, TOC, etc.

In addition, during recording mode, because there is no need to handle C2PO data, the area from NL to NU-1 can be used freely. Normally, NL is set to be NU.

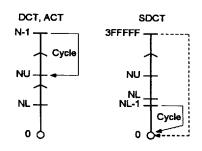

#### (2) Counters

The CXD2526A has four counters that generate addresses and one that keeps a count of the transfer bytes.

- (1) DCT (drive read/write counter)

- : Generates R/W addresses for I/O data for the EFM encoder/decoder.

- (2) ACT (ATRAC encoder/decoder R/W counter)

- : Generates R/W addresses for I/O data for the ATRAC encoder/decoder.

- (3)CCT (CPU R/W counter)

- : Generates R/W addresses for I/O data accessed by the CPU.

- (4) SDCT (Sub Data R/W counter)

- : Generates R/W addresses either for I/O data for the microcontroller for external subdata, or for I/O data for the EFM encoder/decoder.

- (5) BCT (byte counter)

- : Byte transferring counter and also down counter either for the EFM encoder or for the ATRAC encoder/decoder.

DCT and ACT are cyclical counters that return to the value NU as the next step after highest address specified for the normal RAM size (WR04) is reached. SDCT is a cyclical counter that returns to 0 as the next step after the value NL-1 is reached.

ACT and DCT never contain a value below NU and SDCT never contains a value equal to NL or more. There is no chance of data in other areas being damaged.

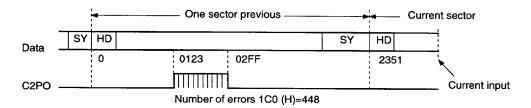

## (3) C2PO address generation

When SBMN=low and EXTC2R (WR04)=0 in playback mode, the C2PO address is automatically calculated based on the values of DCT and ACT, and is input/output at the same time as data. The relationship between a data address and the address where the C2PO information for that data is recorded as described below.

## Setting example:

When using a 1M DRAM, 48 sectors were allocated as the main data area.

In this case, the C2PO corresponding to the data in address 12345 (H) =74,565 is as follows.

Furthermore, the bit position is bit 5, since the lowest significent bits of 12345 (H) are 101 (B).

(In the above example)

Address 12340: no errors in data (0)

Address 12341: error in data (1)

Address 12342: no errors in data (0)

Address 12343: error in data (1)

Address 12344: error in data (1)

Address 12345: error in data (1)

Address 12346: no errors in data (0)

Address 12347: no errors in data (0)

In this case, the data in 2B68 (H) is 0011, 1010=3A (H).

N 131,072 20,000 (H)

48 sectors

NU=18176=4700 (H)

NL=4064=FE0 (H)

a b c d e f g h

8 bytes out of main data

NU

NL

1 byte (8 bits) out of main data

Even during playback mode, if SDCT is selected for getting data (SBMN is high), C2PO data is not retrieved.

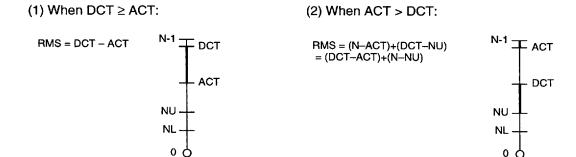

## (4) Data size calculation

RMS=DCT-ACT is calculated, and the result is stored in a read register (RR0C). At this point, NU is used for compensation:

The RMS value in playback mode is the amount of main data buffered, and in recording mode, is the amount of free area in the main data area.

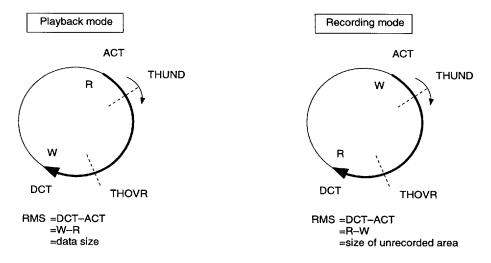

#### (5) Data size comparison

The RMS value computed in item (4) above is compared with the threshold values set in write registers WR12 and 13, and an interrupt is generated based on their relationship.

This function is useful in generating the timing for starting and stopping data retrieval.

If RMS ≥ THOVR changes from false to true, the THOVR status (RR00) is set.

If RMS < THUND changes from false to true, the THUND status (RR00) is set.

## 2. Operation during Playback

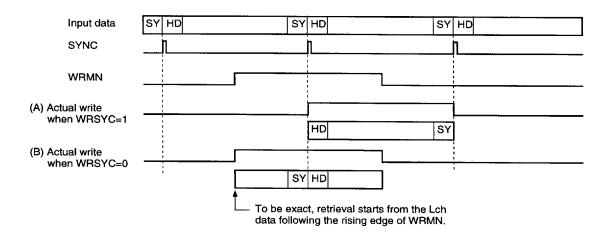

## (1) Write mode/monitor mode switching

If the external input pin WRMN is

high: write mode low: monitor mode

In write mode, writing to RAM is enabled for all input data, including sync/headers, from the EFM decoder.

## Bit 6 of write register WR0E:

When WRSYC=1, writes are synchronized with the input sync timing. When WRSYC=0, writes are not synchronized with the input sync timing.

If monitor mode is selected, all writes to RAM are prohibited. The headers/subheaders are pulled in internal registers (RR02, RR03), regardless of the mode.

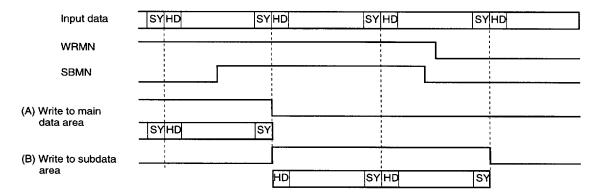

## (2) Sub/main switching

When the external input pin SBMN is

high: external input is pulled in memory based on the SDCT counter

low: external input is pulled in memory based on the DCT counter

If the DCT counter is selected and EXTC2R (WR04)=0, C2PO information is pulled in the same manner, based on the address shown in section 6-1.(3).

If the SDCT counter is selected, C2PO information is not pulled in.

Note that this switching is performed in synchronization with SYNC.

## (3) Decoder

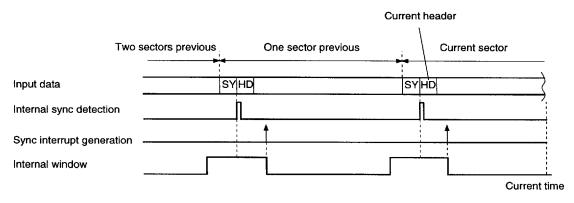

This section describes the internal operation of the MD sector data decoder.

The sector being input to this IC is called the "current sector". When sync is detected or after 12 LRCK cycles of the inserted timing (the timing for closing the window), a sync interrupt is generated. At this point, the current header sync status (RR01), the header data (RR02) and the four bytes of data (RR03) following the header can be read from the register; in addition, if in write mode (WRMN is high), it is also possible to read as the current header address (RR04) the address in memory where the first byte of the current header is written.

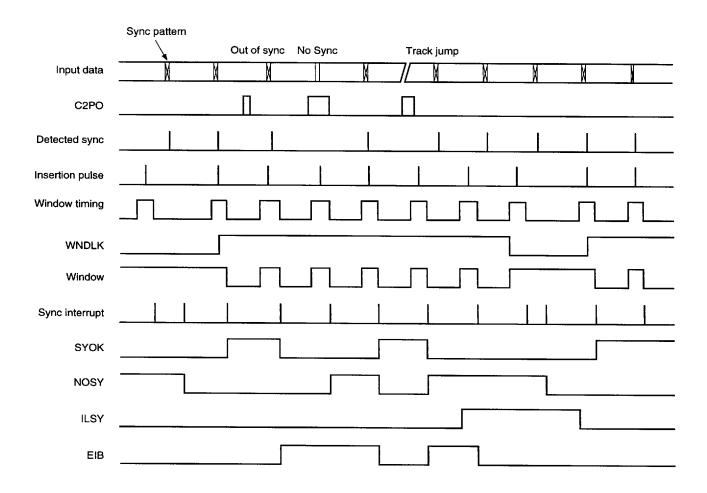

The contents of the sync status register are as follows:

SYOK : Indicates that the current header sync was read either after the previous sector sync or

after 2352 bytes in the insertion timing.

NOSY : Indicates that the current header sync was not detected in the window.

ILSY : Set when the sync pattern was detected outside of the window.

WNDLK : Indicates that the insertion timing is synchronized correctly and the window is active. EIB : Indicates that a C2PO error exists within the sector previous to the current sector.

## Decoder's automatic algorithm (sync detection/windows/insertion protection)

The input data sync pattern is detected and the insertion counter is reset with the same timing. If sync is detected after 2352 bytes, the insertion timing is assumed to be synchronized, and the window is activated. Sync detected while the window is not active are all effective and are treated as insertion counter reset inputs. When the window is active, only sync detected within the window are effective as resets; sync outside the window are read as illegal sync.

If illegal sync occur in two consecutive frames, it is decided that the insertion synchronization has been lost, the window is opened, and any sync detection becomes valid for synchronization purposes.

## (4) Transfers to the ATRAC decoder

#### a) Normal transfers

During playback, the following procedure is necessary in order to transfer data to the ATRAC decoder:

- 1. Set the start address of the data to be transferred in ACT. (WR08)

- 2. Set the number of bytes to be transferred in BCT. (WR08) (Actually, set the number of bytes-1; refer to the register commands.)

- 3. Transfer triggered. (WR06)

The CXD2526A transfers data to the ATRAC decoder based on the ACT address value while counting down the BCT. When the BCT reaches zero and the last bit of the last byte has been transferred, the PBTXED status of RR00 is generated.

Although transfers are made at a maximum data rate of 5.6448Mbps (705KB/s), if the input XRQ pin from the ATRAC decoder goes high, the transfer process waits. The following are the transfer trigger options:

- 1. Getting the transmission header time ----- ACHDLD

- 2. Autoloading the byte counter value ----- BTLD

- 3. Autotrigger AUTTRG

For details, refer to the WR06 register commands.

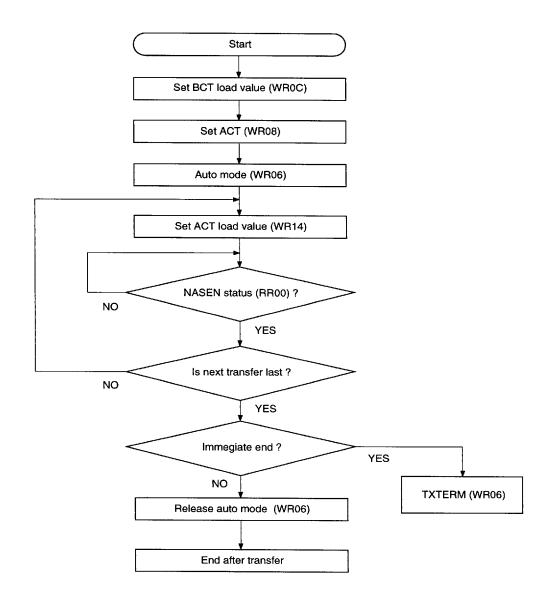

## b) Autotrigger mode transfer (AUTTRAG of WR06)

In autotrigger mode, when a transfer ends, the next setting values for the ACT (ACTLV value of WR14) and BCT (BCTLV value of WR0C) are automatically loaded and the next transfer is triggered automatically.

Because the value loaded to the BCT is normally the same as the previous value, there is no special reason to set it again once it has been set, but the start address for the transfer does need to be set before one transfer is completed. In other words, it must be set before the ATRAC decoder finishes reading the transfer bytes for one sector (approximately 65ms).

First, set the ACT value and then send the transfer trigger in autotrigger mode. At this point, write the ACT start address for the next transfer in WR14. Once the transfer is completed and this ACTLV load value and the BCTLV load value are loaded, the NASEN status (RR00) is generated. In this way, data can be sent one after the other (without demanding strict timing). If auto trigger mode is cleared, transfer is terminated once the current transfer bytes have all been sent and the PBTXED (RR00) status is generated. Note that the auto trigger mode is always set during the recording mode.

## 3. Operation during Recording

C2PO data is not written during recording.

Data from the ATRAC encoder is stored in a buffer as is; after a header is added and the data is scrambled, the sync pattern is added and the data is sent to the EFM encoder.

## (1) Recording data buffering

If WRMN is high, the data from the ATRAC encoder is immediately stored in a buffer according to the ACT value.

## (2) Recording data transfer

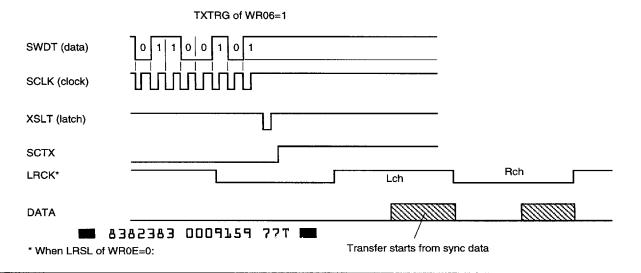

When the trigger command (TXTRG of WR06) is sent from the microcontroller and the SCTX pin is high, data transfer starts from Lch (data immediately after the changing of LRCK polarity to Lch) to the EFM encoder.

After synchronized (12 bytes), the header (4 bytes) specified by register WR02 and the subheader (4 bytes) specified by WR03 are sent, followed by the number of bytes of data (based on SC0 and SC1 (WR06)) specified by BCTLV (WR0C).

In the case of the MD format, the number of bytes of main data to be sent per sector is:

2352-12-8=2332 bytes, which is further adjusted as follows:

2332-1=2331=91B (H)

Therefore, it is necessary to send 09, 1B (H) to WR0C. All data after synchronized is scrambled before it is sent.

Data specified by SC0 and SC1 are as follows:

SC1, 0=00 : linking data

Generates/transfers all-zero data. Data is not read from memory, and the DCT value

does not change.

SC1, 0=01 : main data

Data is read from memory based on the address indicated by DCT and sent.

SC1, 0=10 : subdata

Data is read from memory based on the address indicated by SDCT and sent.

SC1, 0=11 : transfer end

## Timing chart for start of record data transfer

#### 4. External Subdata Interface

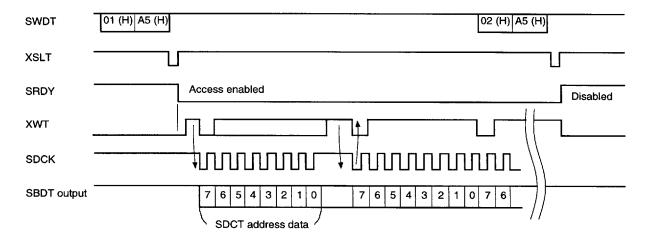

Data I/O can be performed through the external subdata interface.

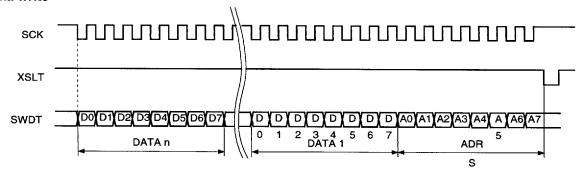

During playback, the external subdata interface is used for reading memory. If the control microcontroller sends the command SBDTEN of WR05=1, the SRDY pin goes low, indicating that external interface access is enabled. If the clock is then sent to SDCK, memory is read according to the address based on SDCT, and the data is read from the SBDT pin MSB first. SDCT is automatically incremented with each read from memory. If XWT is high, it is permissible to send the clock for the read and then read the data. In this case, XWT becomes low while the MSB bits are being output, but if a wait has been initiated regarding internal access, XWT will remain low for an extended period. Normally, because XWT returns to the high level right away, it is permissible to continuously send the clock needed to read the next byte. If XWT is low when the next new byte is to be read, the internal memory read operation is not yet complete; therefore, the clock must not be sent until XWT is high.

If the SBDTDS of WR05=1 command is sent, SRDY pin goes high, and external interface access is disabled. Data in memory at the address indicated by the SDCT value can be read through the external interface. In order to pass subdata to the external interface, it is necessary to load the subdata into a certain area in memory beforehand and then set the start address value in SDCT before sending the external interface access command. Doing this requires the following controls, for example:

- 1. Set the start address to which data is to be loaded in SDCT.

- 2. Load the target subdata on the disc into memory based on SDCT. (Sectors FC to FF (H); in the case of a recordable MD, FF (H))

- 3. Once the data is loaded, set the SDCT again.

- 4. Send the external access enable command.

- 5. Send the external access disable command.

The control microcontroller must not make any accesses that would use the SDCT because SDCT is surrendered to the external interface during the interval of step 4 and 5.

## • Timing chart for external subdata interface read system (during playback)

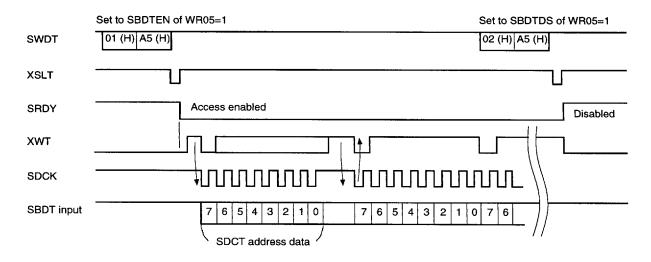

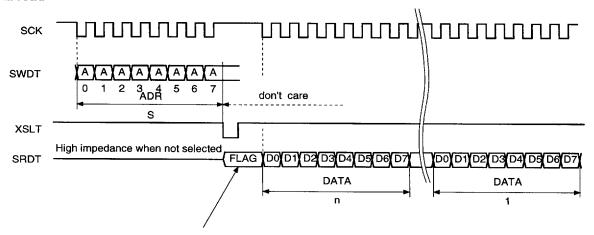

Operation during recording is basically the same as during playback. The SBDT pin becomes the input for writing data from the external interface.

## • Timing chart for external subdata interface write system (during recording)

## Description of Register Commands (All transfers are performed LS bit first, MS byte first)

## • Write Register

| Register No. | Name                            | BIT0       | BIT1       | BIT2       | BIT3       | BIT4       | BIT5       | BIT6       | BIT7       |

|--------------|---------------------------------|------------|------------|------------|------------|------------|------------|------------|------------|

| WR00         | Interrupt Control Register      | MDSY       | PBTXED     | RPSEN      | OVRFUL     | THOVR      | THUND      | NASEN      | SGSY       |

| WR01         | Decoder Control Register        | AUTALG     | INSEN      | WNDEN      | WNDRST     | SYDTEN     | 1          | 0          | 1          |

| WR02 -1      |                                 | RTHD<br>24 | RTHD<br>25 | RTHD<br>26 | RTHD<br>27 | RTHD<br>28 | RTHD<br>29 | RTHD<br>30 | RTHD<br>31 |

| -2           | REC TX Header                   | RTHD<br>16 | RTHD<br>17 | RTHD<br>18 | RTHD<br>19 | RTHD<br>20 | RTHD<br>21 | RTHD<br>22 | RTHD<br>23 |

| -3           | TLO IX Headel                   | RTHD<br>08 | RTHD<br>09 | RTHD<br>10 | RTHD<br>11 | RTHD<br>12 | RTHD<br>13 | RTHD<br>14 | RTHD<br>15 |

| -4           |                                 | RTHD<br>00 | RTHD<br>01 | RTHD<br>02 | RTHD<br>03 | RTHD<br>04 | RTHD<br>05 | RTHD<br>06 | RTHD<br>07 |

| WR03 -1      |                                 | RTSH<br>24 | RTSH<br>25 | RTSH<br>26 | RTSH<br>27 | RTSH<br>28 | RTSH<br>29 | RTSH<br>30 | RTSH<br>31 |

| -2           | REC TX Subheader                | RTSH<br>16 | RTSH<br>17 | RTSH<br>18 | RTSH<br>19 | RTSH<br>20 | RTSH<br>21 | RTSH<br>22 | RTSH<br>23 |

| -3           | TIES TX Oublieddel              | RTSH<br>08 | RTSH<br>09 | RTSH<br>10 | RTSH<br>11 | RTSH<br>12 | RTSH<br>13 | RTSH<br>14 | RTSH<br>15 |

| -4           |                                 | RTSH<br>00 | RTSH<br>01 | RTSH<br>02 | RTSH<br>03 | RTSH<br>04 | RTSH<br>05 | RTSH<br>06 | RTSH<br>07 |

| WR04         | RAM SIZE Reg.                   | RAMSZ<br>0 | RAMSZ<br>1 | RAMSZ<br>2 | REFSEL     | EXTC2R     | OVRST<br>P | 0          | 0          |

| WR05         | SUB DATA CTL                    | SBDTEN     | SBDTDS     | RFRST      | WFRST      | 0          | 0          | 0          | 0          |

| WR06         | TX Trigger                      | TXTRG      | TXTRM      | 0          | ACHDLD     | BTLD       | AUTTR<br>G | SC0        | SC1        |

| WR07 -1      |                                 | DCT<br>16  | DCT<br>17  | DCT<br>18  | DCT<br>19  | DCT<br>20  | DCT<br>21  | 0          | 0          |

| -2           | Drive R/W CT<br>(DCT)           | DCT<br>08  | DCT<br>09  | DCT<br>10  | DCT<br>11  | DCT<br>12  | DCT<br>13  | DCT<br>14  | DCT<br>15  |

| -3           |                                 | DCT<br>00  | DCT<br>01  | DCT<br>02  | DCT<br>03  | DCT<br>04  | DCT<br>05  | DCT<br>06  | DCT<br>07  |

| WR08 -1      | ATRAC                           | ACT<br>16  | ACT<br>17  | ACT<br>18  | ACT<br>19  | ACT<br>20  | ACT<br>21  | 0          | 0          |

| -2           | Encoder/Decoder<br>R/W CT (ACT) | ACT<br>08  | ACT<br>09  | ACT<br>10  | ACT<br>11  | ACT<br>12  | ACT<br>13  | ACT<br>14  | ACT<br>15  |

| -3           |                                 | ACT<br>00  | ACT<br>01  | ACT<br>02  | ACT<br>03  | ACT<br>04  | ACT<br>05  | ACT<br>06  | ACT<br>07  |

| WR09 -1      |                                 | CCT<br>16  | CCT<br>17  | CCT<br>18  | CCT<br>19  | CCT<br>20  | CCT<br>21  | 0          | 0          |

| -2           | CPU R/W CT<br>(CCT)             | CCT<br>08  | CCT<br>09  | CCT<br>10  | CCT<br>11  | CCT<br>12  | CCT<br>13  | CCT<br>14  | CCT<br>15  |

| -3           |                                 | CCT<br>00  | CCT<br>01  | CCT<br>02  | CCT<br>03  | CCT<br>04  | CCT<br>05  | CCT<br>06  | CCT<br>07  |

| WR0A -1      | Subdata R/W CT<br>(SDCT)        | SDCT<br>16 | SDCT<br>17 | SDCT<br>18 | SDCT<br>19 | SDCT<br>20 | SDCT<br>21 | 0          | 0          |

| -2           |                                 | SDCT<br>08 | SDCT<br>09 | SDCT<br>10 | SDCT<br>11 | SDCT<br>12 | SDCT<br>13 | SDCT<br>14 | SDCT<br>15 |

| -3           |                                 | SDCT<br>00 | SDCT<br>01 | SDCT<br>02 | SDCT<br>03 | SDCT<br>04 | SDCT<br>05 | SDCT<br>06 | SDCT<br>07 |

| WR0B -1      | Byte CT                         | BCT<br>08  | BCT<br>09  | BCT<br>10  | BCT<br>11  | BCT<br>12  | 0          | 0          | 0          |

| -2           | (BCT)                           | BCT<br>00  | BCT<br>01  | BCT<br>02  | BCT<br>03  | BCT<br>04  | BCT<br>05  | BCT<br>06  | BCT<br>07  |

| Register No. | Name                  | BIT0       | BIT1       | BIT2       | ВІТЗ       | BIT4       | BIT5       | ВІТ6       | BIT7       |

|--------------|-----------------------|------------|------------|------------|------------|------------|------------|------------|------------|

| WR0C -1      | Byte CT Load Value    | BLV<br>08  | BLV<br>09  | BLV<br>10  | BLV<br>11  | BLV<br>12  | 0          | 0          | 0          |

| -2           | (BCTLV)               | BLV<br>00  | BLV<br>01  | BLV<br>02  | BLV<br>03  | BLV<br>04  | BLV<br>05  | BLV<br>06  | BLV<br>07  |

| WROD         | CPU Write Data        | CPDT<br>00 | CPDT<br>01 | CPDT<br>02 | CPDT<br>03 | CPDT<br>04 | CPDT<br>05 | CPDT<br>06 | CPDT<br>07 |

| WR0E         | Input Format          | LMSL       | BCKSL      | BCKMD      | C2SL       | LRSL       | DPSL       | WRSYC      | 1          |

| WROF         | Reserved              | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          |

| WR10 -1      |                       | NL<br>16   | NL<br>17   | NL<br>18   | NL<br>19   | NL<br>20   | NL<br>21   | 0          | 0          |

| -2           | NL                    | NL<br>08   | NL<br>09   | NL<br>10   | NL<br>11   | NL<br>12   | NL<br>13   | NL<br>14   | NL<br>15   |

| -3           |                       | NL<br>00   | NL<br>01   | NL<br>02   | NL<br>03   | NL<br>04   | NL<br>05   | NL<br>06   | NL<br>07   |

| WR11 -1      |                       | NU<br>16   | NU<br>17   | NU<br>18   | NU<br>19   | NU<br>20   | NU<br>21   | 0          | 0          |

| -2           | NU                    | NU<br>80   | NU<br>09   | NU<br>10   | NU<br>11   | NU<br>12   | NU<br>13   | NU<br>14   | NU<br>15   |

| -3           |                       | 0          | 0          | ō          | NU<br>03   | NU<br>04   | NU<br>05   | NU<br>06   | NU<br>07   |

| WR12 -1      |                       | UND<br>16  | UND<br>17  | UND<br>18  | UND<br>19  | UND<br>20  | UND<br>21  | UND<br>22  | UND<br>23  |

| -2           | THUND                 | UND<br>08  | UND<br>09  | UND<br>10  | UND<br>11  | UND<br>12  | UND<br>13  | UND<br>14  | UND<br>15  |

| -3           |                       | 0          | 0          | 0          | 0          | 0          | 0          | UND<br>06  | UND<br>07  |

| WR13 -1      |                       | OVR<br>16  | OVR<br>17  | OVR<br>18  | OVR<br>19  | OVR<br>20  | OVR<br>21  | OVR<br>22  | OVR<br>23  |

| -2           | THOVR                 | OVR<br>08  | OVR<br>09  | OVR<br>10  | OVR<br>11  | OVR<br>12  | OVR<br>13  | OVR<br>14  | OVR<br>15  |

| -3           |                       | 0          | 0          | 0          | 0          | 0          | 0          | OVR<br>06  | OVR<br>07  |

| WR14 -1      | ATRAC Decoder         | ALV<br>16  | ALV<br>17  | ALV<br>18  | ALV<br>19  | ALV<br>20  | ALV<br>21  | 0          | 0          |

| -2           | Address<br>Load Value | ALV<br>08  | ALV<br>09  | ALV<br>10  | ALV<br>11  | ALV<br>12  | ALV<br>13  | ALV<br>14  | ALV<br>15  |

| -3           | (ACTLV)               | ALV<br>00  | ALV<br>01  | ALV<br>02  | ALV<br>03  | ALV<br>04  | ALV<br>05  | ALV<br>06  | ALV<br>07  |

## • Read Register

| Register No. | Name                      | BIT0      | BIT1      | BIT2      | ВІТЗ      | BIT4      | BIT5      | BIT6      | BIT7      |

|--------------|---------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| RR00         | Interrupt Status          | MDSY      | PBTXED    | RPSEN     | OVRFUL    | THOVR     | THUND     | NASEN     | SGSY      |

| RR01         | Decoder Status            | SYOK      | NOSY      |           | ILSY      | WNDLK     | EIB       |           |           |

| RR02 -1      |                           | CHD<br>24 | CHD<br>25 | CHD<br>26 | CHD<br>27 | CHD<br>28 | CHD<br>29 | CHD<br>30 | CHD<br>31 |

| -2           | Current Header            | CHD<br>16 | CHD<br>17 | CHD<br>18 | CHD<br>19 | CHD<br>20 | CHD<br>21 | CHD<br>22 | CHD<br>23 |

| -3           | Current neader            | CHD<br>08 | CHD<br>09 | CHD<br>10 | CHD<br>11 | CHD<br>12 | CHD<br>13 | CHD<br>14 | CHD<br>15 |

| -4           |                           | CHD<br>00 | CHD<br>01 | CHD<br>02 | CHD<br>03 | CHD<br>04 | CHD<br>05 | CHD<br>06 | CHD<br>07 |

| RR03 -1      |                           | CSH<br>24 | CSH<br>25 | CSH<br>26 | CSH<br>27 | CSH<br>28 | CSH<br>29 | CSH<br>30 | CSH<br>31 |

| -2           |                           | CSH<br>16 | CSH<br>17 | CSH<br>18 | CSH<br>19 | CSH<br>20 | CSH<br>21 | CSH<br>22 | CSH<br>23 |

| -3           | Current Subheader         | CSH<br>08 | CSH<br>09 | CSH<br>10 | CSH<br>11 | CSH<br>12 | CSH<br>13 | CSH<br>14 | CSH<br>15 |

| -4           |                           | CSH<br>00 | CSH<br>01 | CSH<br>02 | CSH<br>03 | CSH<br>04 | CSH<br>05 | CSH<br>06 | CSH<br>07 |

| RR04 -1      |                           | CHA<br>16 | CHA<br>17 | CHA<br>18 | CHA<br>19 | CHA<br>20 | CHA<br>21 |           |           |

| -2           | Current Header Address    | CHA<br>08 | CHA<br>09 | CHA<br>10 | CHA<br>11 | CHA<br>12 | CHA<br>13 | CHA<br>14 | CHA<br>15 |

| -3           |                           | CHA<br>00 | CHA<br>01 | CHA<br>02 | CHA<br>03 | CHA<br>04 | CHA<br>05 | CHA<br>06 | CHA<br>07 |

| RR05 -1      |                           | THD<br>24 | THD<br>25 | THD<br>26 | THD<br>27 | THD<br>28 | THD<br>29 | THD<br>30 | THD<br>31 |

| -2           |                           | THD<br>16 | THD<br>17 | THD<br>18 | THD<br>19 | THD<br>20 | THD<br>21 | THD<br>22 | THD<br>23 |

| -3           | TX Header                 | THD<br>08 | THD<br>09 | THD<br>10 | THD<br>11 | THD<br>12 | THD<br>13 | THD<br>14 | THD<br>15 |

| -4           |                           | THD<br>00 | THD<br>01 | THD<br>02 | THD<br>03 | THD<br>04 | THD<br>05 | THD<br>06 | THD<br>07 |

| RR06 -1      |                           | TSH<br>24 | TSH<br>25 | TSH<br>26 | TSH<br>27 | TSH<br>28 | TSH<br>29 | TSH<br>30 | TSH<br>31 |

| -2           | TV Outshands              | TSH<br>16 | TSH<br>17 | TSH<br>18 | TSH<br>19 | TSH<br>20 | TSH<br>21 | TSH<br>22 | TSH<br>23 |

| -3           | TX Subheader              | TSH<br>08 | TSH<br>09 | TSH<br>10 | TSH<br>11 | TSH<br>12 | TSH<br>13 | TSH<br>14 | TSH<br>15 |

| -4           |                           | TSH<br>00 | TSH<br>01 | TSH<br>02 | TSH<br>03 | TSH<br>04 | TSH<br>05 | TSH<br>06 | TSH<br>07 |

| RR07 -1      |                           | DCT<br>16 | DCT<br>17 | DCT<br>18 | DCT<br>19 | DCT<br>20 | DCT<br>21 |           |           |

| -2           | Drive R/W CT<br>(DCT)     | DCT<br>08 | DCT<br>09 | DCT<br>10 | DCT<br>11 | DCT<br>12 | DCT<br>13 | DCT<br>14 | DCT<br>15 |

| -3           |                           | DCT<br>00 | DCT<br>01 | DCT<br>02 | DCT<br>03 | DCT<br>04 | DCT<br>05 | DCT<br>06 | DCT<br>07 |

| RR08 -1      | ATRAC                     | ACT<br>16 | ACT<br>17 | ACT<br>18 | ACT<br>19 | ACT<br>20 | ACT<br>21 |           |           |

| -2           | Encoder/Decoder<br>R/W CT | ACT<br>08 | ACT<br>09 | ACT<br>10 | ACT<br>11 | ACT<br>12 | ACT<br>13 | ACT<br>14 | ACT<br>15 |

| -3           | (ACT)                     | ACT<br>00 | ACT<br>01 | ACT<br>02 | ACT<br>03 | ACT<br>04 | ACT<br>05 | ACT<br>06 | ACT<br>07 |

/: don't care

| Register No. | Name                      | BIT0       | BIT1       | BIT2       | BIT3       | BIT4       | BIT5       | BIT6       | BIT7       |

|--------------|---------------------------|------------|------------|------------|------------|------------|------------|------------|------------|

| RR09 -1      |                           | CCT<br>16  | CCT<br>17  | CCT<br>18  | CCT<br>19  | CCT<br>20  | CCT<br>21  |            |            |

| -2           | CPU R/W CT<br>(CCT)       | CCT<br>08  | CCT<br>09  | CCT<br>10  | CCT<br>11  | CCT<br>12  | CCT<br>13  | CCT<br>14  | CCT<br>15  |

| -3           |                           | CCT<br>00  | CCT<br>01  | CCT<br>02  | CCT<br>03  | CCT<br>04  | CCT<br>05  | CCT<br>06  | CCT<br>07  |

| RR0A -1      |                           | SDCT<br>16 | SDCT<br>17 | SDCT<br>18 | SDCT<br>19 | SDCT<br>20 | SDCT<br>21 |            |            |

| -2           | Sub Data R/W CT<br>(SDCT) | SDCT<br>08 | SDCT<br>09 | SDCT<br>10 | SDCT<br>11 | SDCT<br>12 | SDCT<br>13 | SDCT<br>14 | SDCT<br>15 |

| -3           |                           | SDCT<br>00 | SDCT<br>01 | SDCT<br>02 | SDCT<br>03 | SDCT<br>04 | SDCT<br>05 | SDCT<br>06 | SDCT<br>07 |

| RR0B -1      | Byte CT                   | BCT<br>08  | BCT<br>09  | BCT<br>10  | BCT<br>11  | BCT<br>12  |            |            |            |

| -2           | (BCT)                     | BCT<br>00  | BCT<br>01  | BCT<br>02  | BCT<br>03  | BCT<br>04  | BCT<br>05  | BCT<br>06  | BCT<br>07  |

| RR0C -1      |                           | RMS<br>16  | RMS<br>17  | RMS<br>18  | RMS<br>19  | RMS<br>20  | RMS<br>21  |            |            |

| -2           | RMS                       | RMS<br>08  | RMS<br>09  | RMS<br>10  | RMS<br>11  | RMS<br>12  | RMS<br>13  | RMS<br>14  | RMS<br>15  |

| -3           |                           | RMS<br>00  | RMS<br>01  | RMS<br>02  | RMS<br>03  | RMS<br>04  | RMS<br>05  | RMS<br>06  | RMS<br>07  |

| RR0D         | CPU DATA READ             | CPDT<br>00 | CPDT<br>01 | CPDT<br>02 | CPDT<br>03 | CPDT<br>04 | CPDT<br>05 | CPDT<br>06 | CPDT<br>07 |

| RR0E -1      |                           | CMS<br>16  | CMS<br>17  | CMS<br>18  | CMS<br>19  | CMS<br>20  | CMS<br>21  | CMS<br>22  | CMS<br>23  |

| -2           | C2PO Monitor Status       | CMS<br>08  | CMS<br>09  | CMS<br>10  | CMS<br>11  | CMS<br>12  | CMS<br>13  | CMS<br>14  | CMS<br>15  |

| -3           |                           | CMS<br>00  | CMS<br>01  | CMS<br>02  | CMS<br>03  | CMS<br>04  | CMS<br>05  | CMS<br>06  | CMS<br>07  |

| RROF -1      |                           | DMS<br>16  | DMS<br>17  | DMS<br>18  | DMS<br>19  | DMS<br>20  | DMS<br>21  | DMS<br>22  | DMS<br>23  |

| -2           | Ext Monitor Status        | DMS<br>08  | DMS<br>09  | DMS<br>10  | DMS<br>11  | DMS<br>12  | DMS<br>13  | DMS<br>14  | DMS<br>15  |

| -3           |                           | DMS<br>00  | DMS<br>01  | DMS<br>02  | DMS<br>03  | DMS<br>04  | DMS<br>05  | DMS<br>06  | DMS<br>07  |

/: don't care

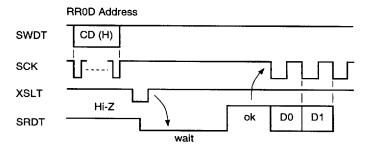

## 1. Register Data I/O

Register data I/O is performed according to the CPU interface timing (described later).

Data is sent MS Byte first (most significant (or higher) byte first) and read LS Bit first. The 1 byte immediately preceding the latch means the address; if these are not selected properly, the data is ignored.

## 2. Write Registers

## (1) Interrupt Control Register (WR00)

By setting each bit of this register to "1", interrupt requests from this IC to the CPU according to the corresponding interrupt status are enabled. As a result, if an enabled interrupt is generated, the XINT pin goes low. The values of each bit of this register have no effect on the corresponding interrupt status.

All status are reset by reading the status from RR00.

header time can be read.

Reset is executed when the RR00 address is transferred from SWDT then XSLT is at falling edge.

Bit 0 : MDSY (Sync Interrupt) ... default 0

In playback mode, the MDSY status is set when either the sync pattern is detected within the sync window or after 12 LRCK cycles of the inserted timing. After this status is set, the sync status or

Bit 1 : PBTXED (PB TX End) ... default 0

In playback mode, PBTXED is set according to the timing when the transfer of data to the ATRAC decoder is completed. To be precise, after the transfer byte counter reaches zero, the read FIFO buffer becomes empty, and all of the last byte (8 bits) has been transferred, this bit is not set in auto trigger mode (AUTTRG of WR06).

Bit 2 : RPSEN (Rec Parameter Set Enable) ... default 0

In recording mode, the RPSEN status is set if, when transferring data to the EFM encoder, the recording data parameter values, that is, the TX header (WR02), the TX subheader (WR03) and the sector data type (SC0, SC1 of WR06), are ready to be set.

Bit 3 : OVRFUL (RAM Over or Full) ... default 0

The OVRFUL status is set when the main data area became full while data was being written to it.

If WR04 OVRSTP="1", writing to RAM while it is full is prohibited.

Bit 4 : THOVR (Threshold Over) ... default 0

THOVR is set when the condition RMS ≥ THOVR changes from false to true.

Bit 5 : THUND (Threshold Under) ... default 0

THUND is set when the condition RMS < THUND changes from false to true.

Bit 6 : NASEN (Next ATRAC decoder Address Set Enable) ... default 0

In playback mode, this bit is set if, when transferring data in auto trigger mode (AUTTRG of WR06), it is permissible to set the next ACTLV value (WR14).

Bit 7 : SGSY (Sound Group Sync) ... default 0

This bit is set at the first falling edge of the XRQ pin after the pin has been continuously high for 3ms or more. During the exchange of signals with the ATRAC decoder, this pin is set every 11.6ms.

- When the CXD2527R is used as the ATRAC encoder/decoder, SGSY interruption is set every 11.6ms because the data is transferred by the unit of sound group.

- When the CXD2531BR is used as the ATRAC encoder/decoder, it takes 11.6ms for two SGSY interruptions because the data is transferred by the unit of sound flame.

## (2) Decoder Control Register (WR01)

Bit 0 : AUTALG (Auto Algorithm) ... default 1

1: Selects the automatic algorithm for the MD sector format decoder sync detection/insertion function.

0: Selects manual mode; operation conforms with the settings of bits 1 through 4 of this register. The automatic algorithm is equivalent to INSEN=WNDEN=SYDTEN=1; if the protection window detects two consecutive illegal sync (refer to RR01), then the window is reset and opened.

Bit 1 : INSEN (INSEN) ... default 0

1: Sync insertion is performed.

0: Sync insertion is not performed.

Bit 2 : WNDEN (Window Enable) ... default 0

1: The sync protection window is active. Patterns detected outside of the window are treated as illegal sync, and are not used for reset for the insertion timing, etc.

0: The window is open, and all detected sync are valid.

Bit 3 : WNDRST (Window Reset) ... default 0

If this bit is set to 1 and the window is active, the window is reset and opened. After the window is reset, this bit is automatically reset to 0. This function is effective in the event of a track jump, when a new sync is detected and it is desirable to quickly lock the window.

Bit 4 : SYDTEN (Sync Detect Enable) ... default 0

1: Sync detection is enabled.

0: Sync detection is not performed.

Bits 5, 6, 7: Fixed to 1, 0, 1, respectively.

## (3) REC TX Header (WR02) ... default 00, 00, 00, 00

This is a four-byte register. In recording mode, this register specifies the four bytes of the header portion of the sector data being sent to the EFM encoder. The byte order, starting with the MS Byte, corresponds with the cluster number (2 bytes), the sector number (1 byte), and the mode (1 byte).

## (4) REC TX Subheader (WR03) ... default 00, 00, 00, 00

This is a four-byte register. In recording mode, this register specifies the four bytes that follow the header data in the sector data being sent to the EFM encoder.

In the MD format, these bytes are all zeros, so these bytes can be left at their default values.

## (5) RAM SIZE (WR04)

Bit 0 : RAMSZ 0 ... default 0

Bit 1 : RAMSZ 1 ... default 0

Bit 2 : RAMSZ 2 ... default 0

Specify the RAM size to be used as follows:

RAMSZ2, RAMSZ1, RAMSZ0

=0 0 0:1Mbit

=0 0 1:2Mbits (1M  $\times$  2)

=0 1 0:4Mbits

=0 1 1:8Mbits  $(4M \times 2)$

=1 0 0:16Mbits

=1 0 1:32Mbits (16M  $\times$  2)

Note that when using DRAM, if RAMSZ0=1 it is assumed that two memory chips are being used, and an external circuit is required. Furthermore, A12 output is used as chip select. In addition, 16M DRAM correspond to the 4K refresh type.

Bit 3 : REFSEL (Refresh Select) ... default 0

Selects the refresh cycle.

- 0: Performs CAS before RAS refresh on DRAM with a cycle of 256 times that of the XTLI input, that is, an 11.3µs cycle.

- 1: Suited for low-power versions of DRAM, this selects a refresh cycle of 8 times, that is, 90.7µs.

Bit 4 : EXTC2R (External C2PO R/W Mode) ... default 1

- 0: During playback, C2PO R/W is performed within a single RAM chip based on an address calculated from the main data address using the NU and NL values (WR10, 11).

- 1: This mode uses external RAM exclusively for C2PO. When using this mode, connect a 1-bit RAM data wire to the ERR pin. In this mode, the C2PO area in main data RAM becomes free area.

Bit 5 : OVRSTP (Overrun Stop) ... default 1

- 1: Prohibits subsequent writing of the next main data if the main data area becomes full. (In this case, the OVRFUL status in RR00 is set.)

- 0: Even if the main data area becomes full, writes are not prohibited. As a result, the data write position and data read position may overrun the area. Caution is required, since the RAM capacity remaining is cleared if an overrun occurs.

Bits 6, 7 : Fixed to 0.

## (6) SUBDATA CONTROL (WR05)

This register enables/disables R/W access to subdata from the outside via the SBDT, SDCK, XWT, and SRDY pins.

Bit 0 : SBDTEN (Sub Data Access Enable) ... default 0

If this bit is set to 1, the SRDY pin goes low and subdata access from the outside is enabled.

Bit 1 : SBDTDS (Sub Data Access Disable) ... default 0

If this bit is set to 1, the SRDY pin goes high and subdata access from the outside is disabled. If a clock is input from the SDCK pin, it is ignored.

For details on external subdata access, refer to item 4. External Subdata Interface.

Bit 2 : RFRST (Read FIFO Reset)

If this bit is set to 1, the read FIFO buffer within the RI block is reset.

Bit 3 : WFRST (Write FIFO Reset)

If this bit is set to 1, the write FIFO buffer within the RI block is reset.

Bits 4 to 7 : Fixed to 0.

## (7) TX Trigger (WR06) ... default 00

This register specifies the trigger and various options when transferring data to the ATRAC decoder or the EFM encoder.

## Bit 0 : TXTRG (TX Trigger)

The transfer starts when this bit is set to 1. This bit is actually set in the transfer preparation state; the timing for the actual start of transfer is:

In playback mode, the data is sent after the data is written in the read FIFO buffer and the ATRAC decoder is prepared to receive data (XRQ is low).

In recording mode, the Lch data is sent first, being followed by the sector sync data to EFM encoder, when the SCTX pin is high.

Refer to 3. Operation during Recording.

## Bit 1 : TXTERM (TX Terminate)

If this bit is set to 1, the transfer terminates. The actual termination timing is as follows:

In playback mode, reading new data from RAM is prohibited and once the data written in the read FIFO buffer has all been sent, the transfer is terminated and the PBTXED status (RR00) is set. In recording mode, the transfer is terminated once the sector data currently being sent is

transferred.

## Bit 2 : Fixed to 0.

## Bit 3 : ACHDLD (ATRAC decoder TX Header Load Option)

In playback mode, if this bit is set to "1" at the same time as the TXTRG bit, the initial 8 bytes are not transferred to the ATRAC decoder but are instead loaded into the internal registers RR05 and RR06. The data following the first 9 bytes is sent to the ATRAC decoder.

If the transfer data start address is set to the header data position, the control microcontroller can read the header data of the sector transferred to the ATRAC decoder regardless of the volume of the data stored in memory; based on that address, the microcontroller can calculate and display the playback time, etc.

## Bit 4 : BTLD (BCT Load Option)

In playback mode, if this bit is set to "1" at the same time as the TXTRG bit, the value specified by WR0C is loaded into the transfer byte counter (BCT). Using this option eliminates the necessity of setting the BCT each time a transfer is triggered.

#### Bit 5 : AUTTRG (Auto Trigger Mode)

In playback mode, if this bit is set to "1", the transfer is performed in auto trigger mode. In this mode, when the transfer byte counter (BCT) reaches zero during the data transfer, the value of WR0C is automatically loaded into the BCT and the value of WR14 is automatically loaded into the ACT, and transfer continues without stopping. For details refer to section 2-(4), (b).

## Bit 6 : SC0 (Sector Data Select 0)

## Bit 7 : SC1 (Sector Data Select 1)

During recording mode, this bit specifies the type of the sector data to be sent to the EFM encoder.

SC1, SC0

=0, 0: Linking data

No data is read from memory; instead, all-zero data is created and transferred.

=0, 1: Main data

The contents of memory based on DCT are read sequentially and sent as sector data.

=1, 0: Subdata

The contents of memory based on SDCT are read sequentially and sent as sector data.

=1, 1: End of transfer

8382383 0009169 619

There are two ways of the end of transfer in recording: TXTERM=1 or SC1, SC0=1.1

## (8) Drive R/W (WR07) ... default 00, 00, 00

This is a three-byte register that sets the Drive R/W CT (DCT) value.

The counter is a 22-bit counter. In addition, the value should be specified so that the result will fit in the RAM size specified by WR04.

## (9) ATRAC encoder/decoder R/W CT (WR08) ... default 00, 00, 00

This is a three-byte register that sets the ATRAC encoder/decoder R/W CT (ACT) value.

## (10) CPU R/W CT (WR09) ... default 00, 00, 00

This is a three-byte register that sets the CPU R/W CT (CCT) value.

## (11) SubData R/W CT (WR0A) ... default 00, 00, 00

This is a three-byte register that sets the SubData R/W CT (SDCT) value.

## (12) Byte CT (WR08) ... default 1F, FF

This is a two-byte register that sets the Byte CT (BCT) value.

The Byte CT is a 13-bit counter. Set the number of bytes-1 to be transferred. For example, to transfer 2336 bytes, set 2336–1=2335, or 09, 1F.

## (13) Byte CT Load Value (WR0C) ... default 00, 00

This is a two-byte register.

In playback mode, specify either the value to be loaded in the BCT by the BCT load position (BTLD of WR06) or the value to be loaded each time in auto trigger mode (AUTTRG of WR06).

In recording mode, set the number of main data bytes, which is:

2352-12 (sync) -8 (header/subheader) -1=2331=09, 1B

#### (14) CPU Write Data (WR0D)

This is a one-byte register. The data set in this register is written to the memory address indicated by the CCT (WR09), and then the CCT value is incremented.

Write accesses to memory by the microcontroller may sometimes be forced to wait, depending on the status of other access requests within the RI block. Therefore, after sending the memory write data and command and supplying the latch pulse, the memory write operation is not completed as long as the SRDT pin is low, which means the next latch pulse for writing the next data in RAM must not be supplied until the previous operation is completed.

To write the same data continuously, it is possible to do so just by continuing to send the latch pulse; it is not necessary to resend the data and address.

By using this command together with RR0D, the CPU can read/write any address value within memory via WR09.

## (15) Input Format Register (WR0E)

This register specifies the interface format from the EFM decoder.

Bit 0 : LMSL (LSB/MSB First Select) ... default 0

0: MSB first1: LSB first

Bit 1 : BCKSL (BCK Polarity Select) ... default 0

0: Input LRCK and DATA change and are input at the rising edge of BCK.1: Input LRCK and DATA change and are input at the falling edge of BCK.

Bit 2 : BCKMD (BCK Mode) ... default 0

0: When BCK has 34 clocks or more during 1 LRCK cycle

1: When BCK has 32 input during 1 LRCK cycle

Bit 3 : C2SL (C2PO Byte Order Select) ... default 0

0: C2PO MS Byte First1: C2PO LS Byte First

Bit 4 : LRSL (LRCK Polarity Select) ... default 0

0: Lch data when LRCK is high, Rch data when LRCK is low 1: Lch data when LRCK is low, Rch data when LRCK is high

Bit 5 : DPSL (Data Position Select) ... default 0

0: Data is input by rear word truncation against the LRCK edge1: Data is input by front word truncation against the LRCK edge

Bit 6 : WRSYC (Write Mode Synchronization) ... default 1

1: Data retrieval starts/stops immediately after sync detection or insertion timing arrives after the WRMN pin logic changes. In other words, after WRMN goes high, retrieval starts with the header data after the sync data, and when WRMN goes low, writing stops after the next sync data is retrieved.

0: Write mode starts immediately after WRMN goes high. (To be precise, after WRMN goes high, retrieval starts from the data immediately following the change in polarity of LRCK to the Lch.

Bit 7 : Fixed to 1.

## (16) Reserved (WR0F)

## (17) NL (WR10) ... default 00, 00, 00

This is a three-byte register that sets the start address of the C2PO area. Set a value equal to the actual value-1. For example, to set NL=123 [H], set the value 00, 01, 02.

## (18) NU (WR11) ... default 00, 00, 00

This is a three-byte register that sets the start address of the main data area. The lower 3 bits are fixed to 0, and if these are set to any other values, those values are ignored.

## (19) Threshold Value for Running Under (WR12)

This is a three-byte register that sets the threshold value (THUND) for data size comparisons. When RMS < THUND changes from being untrue to true, the RR00 THUND status is set and an interrupt is generated. Note that the lower 6 bits are fixed to 0, and if they are set to any other values, those values are ignored.

## (20) Threshold Value for Running Over (WR13)

This is a three-byte register that sets the threshold value (THOVR) for data size comparisons. When RMS  $\geq$  THOVR changes from being untrue to true, the RR00 THOVR status is set and an interrupt is generated. Note that the lower 6 bits are fixed to 0, and if they are set to any other values, those values are ignored.

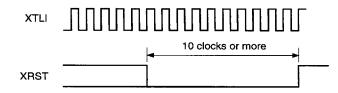

## (21) ATRAC Decoder Load Value (WR14)