16 x 4 Static R/W RAM

# SEMICONDUCTOR

#### **Features**

- Fully decoded, 16 word x 4-bit highspeed CMOS RAMs

- Inverting outputs 27S03, 27LS03, 74S189

- Non-inverting outputs 27S07

- High speed

- -- 25 ns

- Low power

- -210 mW (27LS03)

- Power supply 5V ± 10%

- Advanced high-speed CMOS processing for optimum speed/power product

- Capable of withstanding greater than 2001V static discharge

- Three-state outputs

- TTL-compatible interface levels

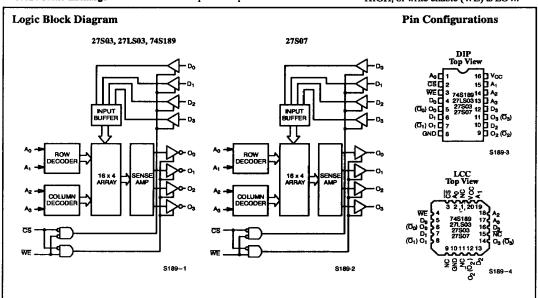

#### **Functional Description**

These devices are high-performance 64-bit static RAMs organized as 16 words by 4 bits. Easy memory expansion is provided by an active LOW chip select (CS) input and three-state outputs. The devices are provided with inverting and non-inverting outputs.

Writing to the device is accomplished when the chip select (CS) and write enable (WE) inputs  $(D_0 \text{ through } D_3)$  is written into the memory location specified on the address pins  $(A_0 \text{ through } A_3)$ . The outputs are preconditioned so that the

write data is present at the outputs when the write cycle is complete. This precondition operation ensures minimum write recovery times by eliminating the "write recovery glitch."

Reading the device is accomplished by taking chip select  $(\overline{CS})$  and output enable  $(\overline{OE})$  LOW, while write enable  $(\overline{WE})$  remains HIGH. Under these conditions, the contents of the memory location specified on the address pins will appear on the four output pins  $(O_0$  through  $O_3)$  in inverted or non-inverted (CY27S07) format

The output pins remain in a high-impedance state when chip select (CS) is HIGH, or write enable (WE) is LOW.

## Selection Guide (For higher performance and lower power, refer to the CY7C189/90 data sheet.)

|                                |            | 27S03<br>27S07 | 27S03, 27S07<br>74S189 | 27LS03 |

|--------------------------------|------------|----------------|------------------------|--------|

| Maximum Access Time (ns)       | Commercial | 25             | 35                     |        |

|                                | Military   | 25             | 35                     | 65     |

| Maximum Operating Current (mA) | Commercial | 90             | 90                     |        |

|                                | Military   | 100            | 100                    | 38     |

## Maximum Ratings

| (Above which the useful life may be impaired. For user guidelines, not tested.) |

|---------------------------------------------------------------------------------|

| Storage Temperature 65°C to +150°C                                              |

| Ambient Temperature with Power Applied 55°C to +125°C                           |

| Supply Voltage to Ground Potential (Pin 16 to Pin 8)                            |

| DC Voltage Applied to Outputs in High Z State 0.5V to +7.0V                     |

| DC Input Voltage 3.0V to +7.0V                                                  |

| Output Current, into Outpus (Low) | 10 mA   |

|-----------------------------------|---------|

| Static Discharge Voltage          | >2001V  |

| Latch-UpCurrent                   | >200 mA |

## **Operating Range**

| Range       | Ambient<br>Temperature | $\mathbf{v}_{\mathbf{cc}}$ |

|-------------|------------------------|----------------------------|

| Commercial  | 0°C to +70°C           | 5V ± 10%                   |

| Military[1] | - 55°C to +125°C       | 5V ± 10%                   |

## Electrical Characteristics Over the Operating Range<sup>[2]</sup>

|                 |                                             |                                 |       | 74S<br>27S03, | 189,<br>27S07 | 27L   | S03      |       |

|-----------------|---------------------------------------------|---------------------------------|-------|---------------|---------------|-------|----------|-------|

| Parameters      | Description                                 | Test Conditio                   | ns    | Min.          | Max.          | Min.  | Max.     | Units |

| V <sub>OH</sub> | Output HIGH Voltage                         | $V_{CC} = Min., I_{OH} = -5$    | .2 mA | 2.4           |               | 2.4   |          | v     |

| V <sub>OL</sub> | Output LOW Voltage                          | $V_{CC} = Min., I_{OL} = 16.0$  | mA    |               | 0.45          |       |          | V     |

|                 |                                             | $V_{CC} = Min., I_{OL} = 8.0 i$ | nA    | T             |               |       | 0.45     | V     |

| V <sub>IH</sub> | Input HIGH Voltage                          |                                 |       | 2.0           | $V_{CC}$      | 2.0   | $v_{cc}$ | V     |

| V <sub>IL</sub> | Input LOW Voltage                           |                                 |       | - 3.0         | 0.8           | - 3.0 | 0.8      | V     |

| I <sub>IX</sub> | Input Leakage Current                       | $GND \le V_I \le V_{CC}$        |       | - 10          | +10           | - 10  | +10      | μA    |

| $V_{CD}$        | Input Diode Clamp Voltage                   |                                 |       |               | ote 3 No      |       | te 3     |       |

| I <sub>OZ</sub> | Output Leakage Current                      | $GND \le V_O \le V_{CC}$        |       | - 40          | +40           | - 40  | +40      | μA    |

| Ios             | Output Short Circuit Current <sup>[4]</sup> | $V_{CC} = Max., V_{OUT} = GND$  |       |               | 90            |       | - 90     | mA    |

| Ios             | Power Supply Current                        | $V_{CC} = Max.,$                | Com'l |               | 90            |       |          | mA    |

|                 |                                             | $I_{OUT} = 0 \text{ mA}$        | Mil   |               | 100           |       | 38       | mA    |

#### Capacitance<sup>[5]</sup>

| Parameters       | Description       | Test Conditions                         | Max. | Units |

|------------------|-------------------|-----------------------------------------|------|-------|

| C <sub>IN</sub>  | InputCapacitance  | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 7    | pF    |

| C <sub>OUT</sub> | OutputCapacitance | $V_{\rm CC} = 5.0 \text{V}$             | 7    | pF    |

#### Notes:

- 1. T<sub>A</sub> is the "instant on" case temperature.

- See the last page of this specification for Group A subgroup testing information.

- 3. The CMOS process does not provide a clamp diode. However these devices are insensitive to 3V DC input levels and 5V undershoot pulses of less than 5 ns (measured at 50% points).

- Not more than 1 output should be shorted at one time. Duration of the short circuit should not exceed 30 seconds.

- Tested initially and after any design or process changes that may affect these parameters.

S189-6

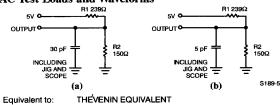

## AC Test Loads and Waveforms

Switching Characteristics Over the Operating Range [2,6]

|                   |                                         |      | 603A<br>607A |      | S03<br>S07 | 748  | 189  | 271  | .S03 |          |

|-------------------|-----------------------------------------|------|--------------|------|------------|------|------|------|------|----------|

| Parameters        | Description                             | Min. | Max.         | Min. | Max.       | Min. | Max. | Min. | Max. | Units    |

| READ CYCL         | E                                       | _    |              |      |            | •    | •    |      |      |          |

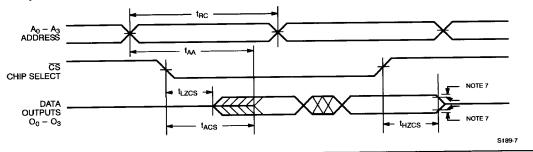

| t <sub>RC</sub>   | Read Cycle Time                         | 25   |              | 35   |            | 35   |      | 65   |      | ns       |

| t <sub>AA</sub>   | Address to Data Valid <sup>[7]</sup>    | 1    | 25           |      | 35         |      | 35   |      | 65   | ns       |

| t <sub>ACS</sub>  | CS LOW to Data Valid <sup>[7]</sup>     |      | 15           |      | 17         |      | 22   |      | 35   | ns       |

| tHZCS             | CS HIGH to High Z <sup>[8, 9, 10]</sup> |      | 15           |      | 20         |      | 17   |      | 35   | ns       |

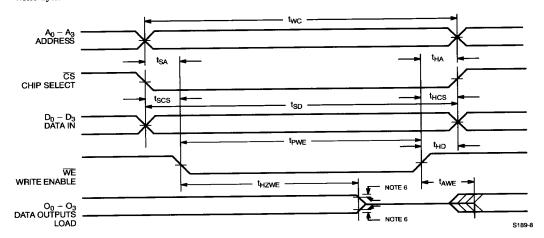

| WRITE CYC         | LE [6, 11, 12]                          |      | <del></del>  |      |            | •    | •    | •    |      | <u> </u> |

| t <sub>WC</sub>   | Write Cycle Time                        | 25   | T            | 35   |            | 35   |      | 65   |      | ns       |

| t <sub>SA</sub>   | Address Set-Up to Write Start           | 0    | 1            | 0    |            | 0    |      | 0    |      | ns       |

| t <sub>HA</sub>   | Address Hold from Write End             | 0    |              | 0    |            | 0    |      | 0    |      | ns       |

| t <sub>SCS</sub>  | CS Set-Up to Write Start                |      |              |      |            | 0    |      |      |      | ns       |

| t <sub>HCS</sub>  | CS Hold from Write End                  |      |              |      |            | 0    |      |      |      | ns       |

| t <sub>SD</sub>   | Data Set-Up to Write End                | 20   |              | 25   |            | 20   |      | 55   |      | ns       |

| t <sub>HD</sub>   | Data Hold from Write End                | 0    |              | 0    |            | 0    |      | 0    |      | ns       |

| t <sub>PWE</sub>  | WE Pulse Width                          | 20   |              | 25   |            | 20   |      | 55   | Ī    | ns       |

| t <sub>HZWE</sub> | WE LOW to High Z <sup>[8, 9, 10]</sup>  |      | 20           |      | 25         |      | 20   |      | 35   | ns       |

| t <sub>AWE</sub>  | WE HIGH to Output Valid <sup>[7]</sup>  |      | 20           |      | 35         | 1    | 30   |      | 35   | ns       |

#### Notes:

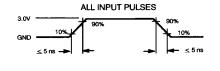

- Test conditions assume signal transition times of 5 ns or less, timing reference levels of 1.5V, output loading of the spcified I<sub>OL</sub>/I<sub>OH</sub> and 30-pF load capacitance.

- t<sub>AA</sub>, t<sub>ACS</sub>, and t<sub>AWE</sub> are tested with C<sub>L</sub> = 30 pF as in part (a) of AC Test Loads. Timing is referenced to 1.5V on the inputs and outputs.

- Transition is measured at steady-state HIGH level 500 mV or steady-state LOW level +500 mV on the output from 1.5V level on the input.

- 9. t<sub>HZCS</sub> and t<sub>HZWE</sub> are tested with C<sub>L</sub> = 5 pF as in part (b) of AC Test

- At any given temperature and voltage condition, t<sub>HZCS</sub> is less than t<sub>LZCS</sub> for any given device.

- Output is preconditioned to data in (inverted or non-inverted) during write to insure correct data is present on all outputs when write is terminated. (No write recovery glitch.)

- 12. The internal write time of the memory is defined by the overlap of CS LOW and WE LOW. Both signals must be LOW to initiate a write and either signal can terminates the write.

# **Switching Waveforms**

## Read Cycle

Write Cycle [13, 14]

#### Notes:

13. All measurements referenced to 1.5V.

14. Timing diagram represents one solution which results in optimum cycle time. Timing may be changed in various applications as long as the worst case limits are not violate.

## **Ordering Information**

| Speed<br>(ns) | Ordering Code | Package<br>Type | Operating<br>Range |

|---------------|---------------|-----------------|--------------------|

| 25            | CY27S03APC    | P1              | Commercial         |

|               | CY27S03ADC    | D2              | 1                  |

|               | CY27S03ALMB   | L61             | Military           |

|               | CY27S03ADMB   | D2              | 1                  |

| 35            | CY27S03PC     | P1              | Commercial         |

|               | CY27S03DC     | D2              | 1                  |

|               | CY27S03LC     | L61             | 1                  |

|               | CY27S03LMB    | L61             | Military           |

|               | CY27S03DMB    | D2              |                    |

| Speed<br>(ns) | Ordering Code | Package<br>Type | Operating<br>Range |

|---------------|---------------|-----------------|--------------------|

| 25            | CY27S07APC    | P1              | Commercial         |

|               | CY27S07ADC    | D2              | 1                  |

|               | CY27S07ALMB   | L61             | Military           |

|               | CY27S07ADMB   | D2              | 1                  |

| 35            | CY27S07PC     | P1              | Commercial         |

|               | CY27S07DC     | D2              | 1                  |

|               | CY27S07LC     | L61             | ]                  |

|               | CY27S07LMB    | L61             | Military           |

|               | CY27S07DMB    | D2              |                    |

| Speed<br>(ns) | Ordering Code | Package<br>Type | Operating<br>Range |

|---------------|---------------|-----------------|--------------------|

| 35            | CY74S189PC    | P1              | Commercial         |

|               | CY74S189DC    | D2              |                    |

| Speed<br>(ns) | Ordering Code | Package<br>Type | Operating<br>Range |

|---------------|---------------|-----------------|--------------------|

| 65            | CY27LS03LMB   | L61             | Military           |

|               | CY27LS03DMB   | D2              |                    |

## MILITARY SPECIFICATIONS Group A Subgroup Testing

## **DC** Characteristics

| Parameters           | Subgroups |

|----------------------|-----------|

| V <sub>OH</sub>      | 1, 2, 3   |

| $v_{OL}$             | 1, 2, 3   |

| $V_{\mathrm{IH}}$    | 1, 2, 3   |

| V <sub>IL</sub> Max. | 1, 2, 3   |

| $I_{IX}$             | 1, 2, 3   |

| $I_{OZ}$             | 1, 2, 3   |

| $I_{CC}$             | 1, 2, 3   |

## **Switching Characteristics**

| Parameters       | Subgroups       |

|------------------|-----------------|

| READ CYCLE       |                 |

| t <sub>RC</sub>  | 7, 8, 9, 10, 11 |

| t <sub>AA</sub>  | 7, 8, 9, 10, 11 |

| tACS             | 7, 8, 9, 10, 11 |

| WRITE CYCLE      |                 |

| twc              | 7, 8, 9, 10, 11 |

| t <sub>SA</sub>  | 7, 8, 9, 10, 11 |

| t <sub>HA</sub>  | 7, 8, 9, 10, 11 |

| t <sub>SCS</sub> | 7, 8, 9, 10, 11 |

| t <sub>HCS</sub> | 7, 8, 9, 10, 11 |

| t <sub>SD</sub>  | 7, 8, 9, 10, 11 |

| t <sub>HD</sub>  | 7, 8, 9, 10, 11 |

| t <sub>PWE</sub> | 7, 8, 9, 10, 11 |

| t <sub>AWE</sub> | 7, 8, 9, 10, 11 |

Document #: 38-00041-C