# VITESSE

# 256 x 4 Static RAM

#### **FEATURES**

- 256 words by 4-bit static RAM for cache and control store applications

- Very fast: Choice of 4, 5, and 6 ns maximum address access times

- · TTL compatible inputs and outputs

- Single +5.0 Volt power supply

- Very low sensitivity to radiation

- Standard 22-pin DIP

- Fully static operation equal access and cycle times

- Pin compatible with standard silicon -422 and -122 products

#### **FUNCTIONAL DESCRIPTION**

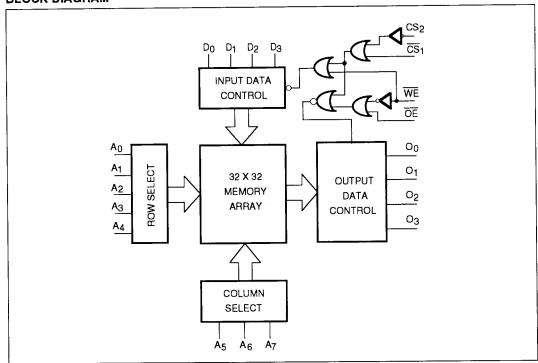

The Vitesse VS12G422T is a very high speed, fully decoded 1024-bit read write static random access memory organized as 256 words by 4 bits. All inputs and outputs of this RAM are TTL compatible and operation is from a standard +5.0 Volt power supply.

Fully static asynchronous internal circuits are used, which require no clocks or refreshing for operation. Memory expansion is provided by an active LOW chip select input  $(C\overline{S}_1)$ , an active HIGH chip select input  $(CS_2)$  and three-state outputs. Due to its static operation, the VS12G422T offers equal read and write cycle times, which further simplifies system design.

# **BLOCK DIAGRAM**

#### TRUTH TABLE

| Inputs |     |                 |    |                  |                 |  |  |  |

|--------|-----|-----------------|----|------------------|-----------------|--|--|--|

| ŌĒ     | ŪS₁ | CS <sub>2</sub> | WE | Output           | Mode            |  |  |  |

| Х      | Н   | ×               | Х  | HIGH Z           | Not Selected    |  |  |  |

| X      | Х   | L               | Х  | HIGH Z           | Not Selected    |  |  |  |

| L      | L   | Н               | Н  | D <sub>out</sub> | READ            |  |  |  |

| X      | L   | Н               | L  | HIĞH Z           | WRITE           |  |  |  |

| Н      | Х   | Х               | Х  | HIGH Z           | Output Disabled |  |  |  |

H = HIGH Voltage Level (2.4 V)

X = Don't Care (HIGH or LOW)

L = LOW Voltage Level (0.4 V)

HIGH Z = High-Impedence

## ARSOLLITE MAYIMLIM RATINGS (1)

| ABSOLUTE MAXIMUM RATINGS                                         |                 |

|------------------------------------------------------------------|-----------------|

| Power Supply Voltage (V <sub>cc</sub> )                          | 0.5 V to +6.0 V |

| Input Voltage Applied, (V <sub>N</sub> )                         | 1.0 V to +7.0 V |

| Input Current, (I <sub>N</sub> ), (DC, output LOW)               |                 |

| Output Current, (I <sub>O(IT)</sub> ), (DC, output LOW)          |                 |

| Case Temperature Under Bias, (T <sub>c</sub> )                   |                 |

| Storage Temperature <sup>(2)</sup> , ( <b>T</b> <sub>STO</sub> ) | 65° to +150°C   |

| RECOMMENDED OPERATING CONDITIONS                                 |                 |

|                                                                  | 4.75 to 5.05 V  |

- (1) CAUTION: Stresses listed under "Absolute Maximum Ratings" may be applied to devices one at a time without causing permanent damage. Functionality at or above the values listed is not implied. Exposure to these values for extended periods may affect device reliability.

- (2) Lower limit is ambient temperature and upper limit is case temperature.

# DC CHARACTERISTICS (Over recommended operating conditions)

|                        |                                       |                 | Commerc        |                 |                |                                                               |  |

|------------------------|---------------------------------------|-----------------|----------------|-----------------|----------------|---------------------------------------------------------------|--|

|                        |                                       | 5,6             | ns             | 4 ns            |                | ]                                                             |  |

| Parameters             | Description                           | Min             | Мах            | Min             | Max            | Test Conditions                                               |  |

| <b>V</b> <sub>OH</sub> | Output HIGH voltage                   | 2.4 V           | _              | 2.4 V           | _              | $V_{CC} = MIN, I_{OH} = -5.2 \text{ mA}$                      |  |

| <b>V</b> <sub>OL</sub> | Output LOW voltage                    | _               | 0.5 V          | _               | 0.5 V          | <b>V</b> <sub>CC</sub> = MIN, <b>I</b> <sub>OL</sub> = 8.0 mA |  |

| <b>V</b> <sub>IH</sub> | Input HIGH voltage                    | 2.0 V           | _              | 2.0 V           |                |                                                               |  |

| <b>V</b> ,,            | Input LOW voltage                     | _               | 0.8 V          | _               | 0.8 V          | _                                                             |  |

| I <sub>IX</sub>        | Input LOAD current                    | -100 μ <b>A</b> | 100 μ <b>A</b> | -100 µ <b>A</b> | 100 μ <b>A</b> | <b>V</b> <sub>IN</sub> = 3.3 V                                |  |

| I <sub>OZ</sub>        | Output current (HIGH-Z)               | -1.0 m <b>A</b> | 1.0 mA         | -1.0 mA         | 1.0 mA         | $V_{OL} \le V_{OUT} \le V_{OH}$<br>Output Disabled            |  |

| I <sub>cc</sub>        | Power supply current (from $V_{cc}$ ) | _               | 300 mA         | _               | 300 mA         | $V_{CC} = MAX$ , $I_{OUT} = 0 mA$                             |  |

# AC PERFORMANCE CHARACTERISTICS (1)

(Over guaranteed operating conditions, GND = 0 V)

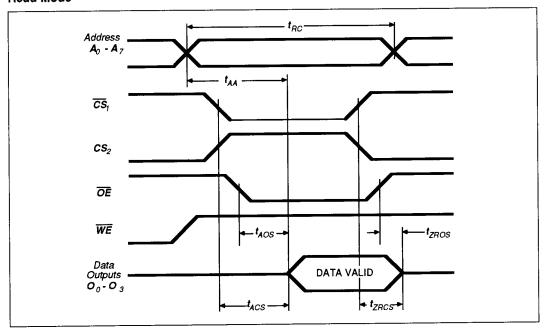

#### Read Mode

| -                                |                         | 6 ns |     | 5 ns |     | 4 ns |     |       |

|----------------------------------|-------------------------|------|-----|------|-----|------|-----|-------|

| Parameters                       | Description             | Min  | Max | Min  | Max | Min  | Max | Units |

| t <sub>RC</sub>                  | Read cycle time         | 6    | _   | 5    | -   | 4    | _   | ns    |

| t <sub>ACS</sub>                 | Chip select time        | _    | 4   | _    | 3.5 |      | 2.5 | ns    |

| t <sub>ZRCS</sub> <sup>(2)</sup> | Chip select to HIGH Z   | -    | 5   | _    | 4   | _    | 3.5 | ns    |

| t <sub>AOS</sub>                 | Output enable time      | _    | 4   | -    | 3.5 | -    | 2.5 | ns    |

| t <sub>ZROS</sub> (2)            | Output enable to HIGH Z | -    | 5   |      | 4   |      | 3.5 | ns    |

| t <sub>AA</sub>                  | Address access time     | _    | 6   |      | 5   |      | 4   | ns    |

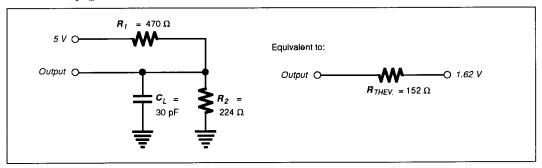

NOTES: 1) Test conditions assume signal transition times of 3 ns or less. Timing reference levels of 1.5 V and output loading of the specified I<sub>OL</sub>I<sub>OH</sub> and 30 pF load capacitance as in Figure 1 on **page X**.

2) Transition is measured at steady state HIGH level -250 mV or steady state LOW level +250 mV on the output from 1.5 V level on the input with load shown in Figure 1 on **page X**.

# AC PERFORMANCE CHARACTERISTICS (con't) (1)

(Over guaranteed operating conditions, GND = 0V)

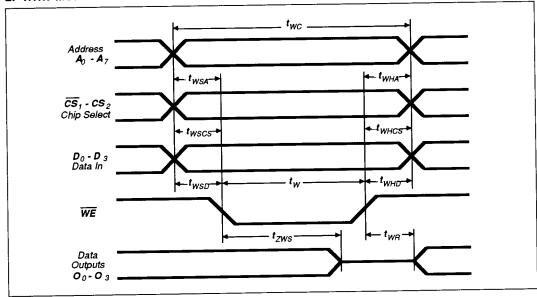

# 2. Write Mode

|                               |                                |     | 6 ns |     | 5 ns |     | s        |       |  |

|-------------------------------|--------------------------------|-----|------|-----|------|-----|----------|-------|--|

| Paramters                     | Description                    | Min | Max  | Min | Max  | Min | Max      | Units |  |

| t <sub>wc</sub>               | Write cycle time               | 6   |      | 5   |      | 4   |          | ns    |  |

| t <sub>zws</sub> (2)          | Write disable to HIGH Z        | _   | 5    |     | 4    |     | 3.5      | ns    |  |

| t <sub>wa</sub>               | Write recovery time            | _   | 4.5  | _   | 3.5  |     | 3        | ns    |  |

| t <sub>w</sub> <sup>(3)</sup> | Write pulse width              | 4   | _    | 3   |      | 2.5 |          | ns    |  |

| t <sub>wsD</sub>              | Data setup time prior to write | 0   | _    | 0   | _    | 0   |          | ns    |  |

| t <sub>whD</sub>              | Data hold time after write     | 2   | _    | 2   | _    | 1.5 |          | ns    |  |

| t <sub>WSA</sub> (3)          | Address setup time             | 0   |      | 0   | _    | 0   | <u> </u> | ns    |  |

| t <sub>WHA</sub>              | Address hold time              | 2   | _    | 2   | _    | 1.5 | _        | ns    |  |

| t <sub>wscs</sub>             | Chip select setup time         | 0   | _    | 0   | -    | 0   |          | ns    |  |

| t <sub>whcs</sub>             | Chip select hold time          | 2   | T -  | 2   | -    | 1.5 |          | ns    |  |

NOTES:

- 1) Test conditions assume signal transition times of 3 ns or less. Timing reference levels of 1.5 V and output

- loading of the specified  $I_{\rm or}/I_{\rm or}$  and 30 pF load capacitance as in Figure 1 on **page X** 2) Transition is measured at steady state HIGH level -250 mV or steady state LOW level +250 mV on the output from 1.5 V level on the input with load shown in Figure 1 on **page X**

- 3)  $t_w$  measured at  $t_{wsA} = min$ ;  $t_{wsA}$  measured at  $t_w = min$

# FIGURE 1: AC TEST LOADING CONDITION

The following conditions apply to the "AC Performance Characteristics" indicated on pages  $\boldsymbol{X}$  and  $\boldsymbol{X}$ .

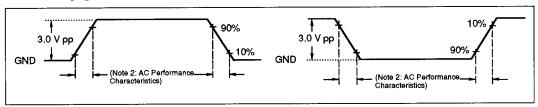

### FIGURE 2: AC TEST INPUT LEVELS

The following conditions apply to the "AC Performance Characteristics" indicated on pages X and X.

#### **ADDRESS DESIGNATORS**

| Address<br>Name      | Address<br>Function | <b>Pin #</b><br>(22-pin DIP) |

|----------------------|---------------------|------------------------------|

| A                    | AX <sub>0</sub>     | 4                            |

| $\mathbf{A}_{1}^{o}$ | AX,                 | 3                            |

| $A_2$                | AX <sub>2</sub>     | 2                            |

| $A_3^2$              | AX <sub>3</sub>     | 1                            |

| $A_4$                | AX <sub>4</sub>     | 21                           |

| $A_5^7$              | AY <sub>5</sub>     | 5                            |

| $A_6^{\circ}$        | AY <sub>6</sub>     | 6                            |

| $A_7^{\circ}$        | AY <sub>7</sub>     | 7                            |

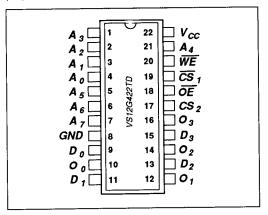

# **CONNECTION DIAGRAM**

(22-pin DIP - Top View)

# PIN DESCRIPTION

| Pin #              | Name                            | 1/0 | Description                      |

|--------------------|---------------------------------|-----|----------------------------------|

| 1-7, 21            | A <sub>0</sub> - A <sub>7</sub> | 1   | Address inputs                   |

| 9, 11, 13, 15      | D <sub>0</sub> - D <sub>3</sub> | 11  | Data Inputs                      |

| 19                 | CS,                             |     | Chip select input (Active LOW)   |

| 10, 12, 14, 16     | 00-03                           | 0   | Data outputs                     |

| 17 CS <sub>2</sub> |                                 |     | Chip select input (Active HIGH)  |

| 20                 | WE                              | T   | Write enable input (Active LOW)  |

| 18                 | ŌĒ                              | 1   | Output enable input (Active LOW) |

| 22                 | v <sub>cc</sub>                 |     | 5.0 V supply connection          |

| 8                  | GND                             |     | Ground connection (0 V)          |