# .

# Preliminary Data Sheet VSC7201C

1 GByte/Sec SCI Compliant Link Controller

#### **Features**

- Conforms to IEEE SCI Standards: IEEE Standard 1596-1992

- Sends and Receives SCI Data in 2ns for 1GByte/s Data Rate

- 18 Signal Parallel Link Interface

- High Speed Link Interface Conforms to Low Voltage Differential I/O Standard (IEEE P1596.3)

- 64-Bit Bi-Directional GTL System Interface

- +3.3V and +2V Power Supplies Required

- 4 Entry Send Queue, 8 Entry Receive Queue Buffers

- 269 Tape Ball Grid Array Package (TBGA - 50 mil centers)

- IEEE Std 1149.1 Test Access Port for Diagnostics

#### 1.0 Introduction

The Scalable Coherent Interface (SCI) provides services similar to those commonly offered in a computer bus architecture. In a multiprocessor environment, however, the scalability of a traditional bus is limited by physics; specifically, problems associated with tapped transmission lines, reflections and capacitive loading. To overcome these problems SCI uses a collection of fast point-to-point unidirectional links instead of a physical bus.

A packet transfer protocol is used by SCI to implement various transactions on the high speed links. This arrangement scales very well from a small number of nodes to a large number of nodes. And SCI has specified protocol and link management to guarantee deadlock free transmission ensuring forward progress on all nodes.

The VSC7201C SCI DataPump implements the link physical transport layer of SCI including guaranteed delivery and forward progress protocol.

# VSC7201C - Block Diagram

G52164-0 Rev. 3.0 2/27/97 9502331 0003518 419 (a) © VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

Preliminary Data Sheet VSC7201C

### 2.0 Terms and Conventions

For reference consult the following documents;

1) IEEE Std 1149.1-1990 IEEE Standard Test Access

Port And Boundary-Scan Architecture.

2) IEEE Std 1212-1991 IEEE Standard Control and

Status Register Architecture for Microcomputer

Buses.

3) IEEE Std 1596-1992 IEEE Standard for Scalable

Coherent Interface (SCI).

### 2.1 Bit and Byte Ordering

The addressable unit in SCI is the byte. SCI packets are constructed from 2-byte (doublet) symbols.

Bit zero is always the most significant bit of a symbol, byte zero is always the most significant byte of a symbol, and the most significant doublet of the address always comes first. Bytes within a packet progress from byte[0] to byte[N] with increasing time. This is big-endian packet notation.

Registers on the DataPump are defined as 4 bytes (quadlet) in size. Data transfers on the NIbus between the DataPump and node interface logic are 8 bytes (octlet) in size. For address invariance, the mapping of bytes within a packet to bytes within a quadlet or octlet is always the same, with byte[0] being the most significant. On the NIBus this means that DATA[0] maps to bit[0] of byte[0] and DATA[63] maps to bit[7] of byte[7]. Within a register, byte[0] is the most significant and byte[3] is the least significant. This big-endian notation implies that smaller address values are more significant than larger ones.

For the defined packets and registers, the sizes of all fields within the data unit (e.g. doublet, quadlet, octlet) are specified; the bit position of each field is implied by the size of the fields to its right or left with the leftmost bit position being 0, or most significant. This labelling convention is more compact than bit-position labels, and avoids the question of whether 0 should be used to label the most or least-significant bit.

#### 2.2 Numerical Values

Decimal, hexadecimal, and binary numbers are used within this specification. Decimal numbers are represented in their standard 0, 1, 2, ... format. Hexadecimal numbers are represented by a string of one or more hexadecimal (0-9, A-F) digits followed by the subscript 16. Binary numbers are represented by a string of one or more binary (0,1) digits followed by the subscript 2. The character x or X is sometimes used as a character in hexadecimal and binary formats and represents the "don't care" value. Each x or X is one digit in size.

1 GByte/Sec SCI Compliant Link Controller

# 3.0 Quick Signal Pin Reference

## 3.1 Node Interface Bus (NIBus) Signals

| Signal        | Туре | Level    | # Pins | Description                                                                                                            |

|---------------|------|----------|--------|------------------------------------------------------------------------------------------------------------------------|

| PDATA[0:63]   | Ю    | GTL      | 64     | Data for packet transfer.                                                                                              |

| PPARITY[0:7]  | Ю    | GTL      | 8      | Byte parity on PDATA. Good parity is odd. PPARITYO corresponds to PDATA [0:7]                                          |

| NDPSEL        | In   | GTL      | 1      | DataPump chip select.                                                                                                  |

| PCMND[0:2]    | In   | GTL      | 3      | DataPump access command for queue and register reads and writes.                                                       |

| NNIACK        | In   | GTL      | 1      | From node interface logic indicating successful access command completion.                                             |

| NNIRDY        | In   | GTL      | 1      | Transfer flow control from node interface logic. Assert equals ready to transfer. De-assert for wait.                  |

| NDPACK        | Out  | GTL      | 1      | From DataPump indicating successful access command completion.                                                         |

| PRCVREQ       | Out  | GTL      | 1      | Indicates Receive Request Queue has data.                                                                              |

| PRCVRSP       | Out  | GTL      | 1      | Indicates Receive Response Queue has data.                                                                             |

| PSNDREQ       | Out  | GTL      | 1      | Indicates Send Request Queue has space.                                                                                |

| PSNDRSP       | Out  | GTL      | 1      | Indicates Send Response Queue has space.                                                                               |

| NINTRNI       | Out  | GTL      | 1      | Node interface logic interrupt for asynchronous link events and errors.                                                |

| NERRNI        | Out  | GTL      | 1      | Asserted low when a node interface bus error occurs.                                                                   |

| PCLKSTB       | Out  | GTL      | 1      | Indicates clockStrobe packet was output on the SCI link.                                                               |

| NRESET        | In   | GTL      | 1      | Resets DataPump and SCI link.                                                                                          |

| NSYNCRQ       | In   | GTL      | 1      | Request to send Sync packet.                                                                                           |

| NSCRUB        | In   | GTL      | 1      | Selects DataPump as SCI link scrubber.                                                                                 |

| PPC[0,1]      | Out  | GTL      | 2      | Performance counters outputs.                                                                                          |

| CLKNI         | In   | TTL      | 1      | Input Clock for NIBus.                                                                                                 |

| CLKHI, NCLKHI | In   | Diff.GTL | 2      | Differential SCI clock input for multiplication to 500Mhz.                                                             |

| PCKHMPY[0:1]  | In   | GTL      | 2      | Divider value for CLKHI to produce internal SCI clock. See SCI clock divide table in Section 5.1.17.                   |

| PCLK250       | In   | TIL      | 1      | Works in conjunction with PCKHMPY[0:1] to determine internal clock rate. See SCI clock divide table in Section 5.1.17. |

| VGREF         | In   | ANALOG   | 1      | GTL external reference input                                                                                           |

| 9502331 0003520 077 **|**

G52164-0 Rev. 3.0 2/27/97 © VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

# Preliminary Data Sheet VSC7201C

### 3.2 SCI Link Interface Signals

| Signal                        | Туре | Level | # Pins | Description                     |

|-------------------------------|------|-------|--------|---------------------------------|

| PSCISI, NSCISI                | In   | LVDS  | 2      | SCI differential input strobe.  |

| PSCIFI,NSCIFI                 | In   | LVDS  | 2      | SCI differential input flag.    |

| PSCIDI[0:15],<br>NSCIDI[0:15] | In   | LVDS  | 32     | SCI differential input data.    |

| PSCISO, NSCISO                | Out  | LVDS  | 2      | SCI differential output strobe. |

| PSCIFO, NSCIFO                | Out  | LVDS  | 2      | SCI differential output flag.   |

| PSCIDO[0:15],<br>NSCIDO[0:15] | Out  | LVDS  | 32     | SCI differential output data.   |

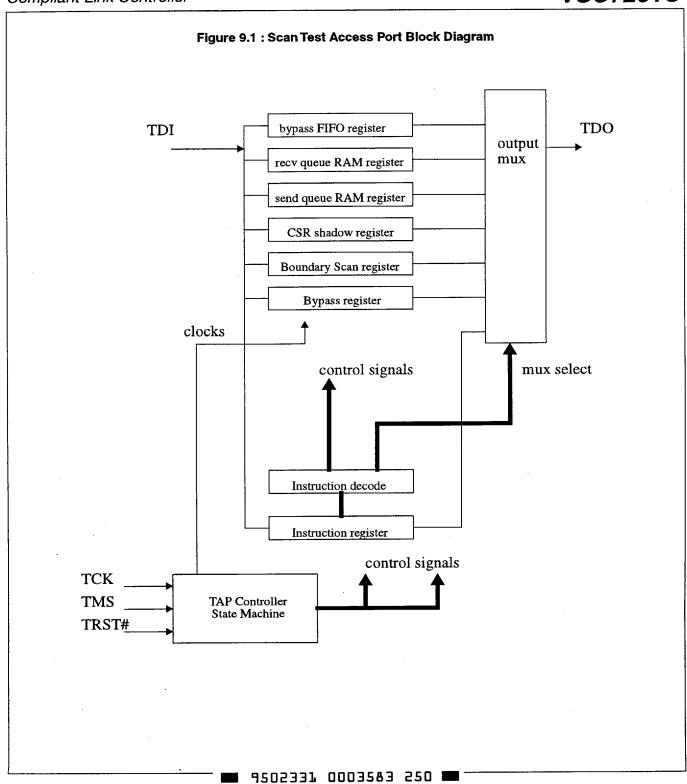

### 3.3 Test Access Port and Internal Scan Test Signals

| Signal        | Туре | Level | # Pins                         | Description                                                                                                       |

|---------------|------|-------|--------------------------------|-------------------------------------------------------------------------------------------------------------------|

| PTDI          | In   | TTL   | 1                              | JTAG Test Access Port (TAP) Test Data In.                                                                         |

| PTMS          | In   | TTL   | 1                              | TAP Test Mode Select                                                                                              |

| PTCK          | In   | TTL   | 1                              | TAP Test Clock.                                                                                                   |

| PTDO          | Out  | TTL   | 1                              | TAP Test Data Out.                                                                                                |

| NTRST         | In   | TTL   | 1                              | TAP Test Reset.                                                                                                   |

| PCKHSEL       | In   | TTL   | 1                              | CLKHI bypass select mux. When asserted CLKHI input will bypass the PLL and drive the internal SCI clock directly. |

| PTSTMD        | In   | TTL   | 1 Not used. Always assert low. |                                                                                                                   |

| PSTEP         | In   | TTL   | 1                              | Not used. Always assert low.                                                                                      |

| PSTOP         | In   | GTL   | 1                              | Not used. Always assert low.                                                                                      |

| PMAINTMD[0:1] | In   | TTL   | 2                              | PMAINTMD0 toggles NIBus parity checking. PMAINTMD1 modifies initialization sequence for test purposes.            |

| PDIV10OUT     | Out  | TTL   | 1                              | Internal 1GHz PLL clock divided by 10 test output.                                                                |

| IPNC          | In   | TTL   | 1                              | Factory test scan input. Tie to VCC.                                                                              |

| OPNC          | Out  | TTL   | 1                              | Factory test scan output. Do not connect.                                                                         |

| TE            | In   | TTL   | 1                              | Factory test enable. Tie to VCC.                                                                                  |

Total Signal Pins = 181

1 GByte/Sec SCI Compliant Link Controller

### 4.0 SCI Overview

The objective of the Scalable Coherent Interface (SCI) standard is to provide a high performance interconnect system between processors and processor elements for tightly coupled, cache coherent data communication.

SCI utilizes point-to-point links and passes data packets to avoid the problems of bus design such as shared resource bandwidth bottlenecks and design of multi-drop, high speed backplane transmission lines.

The DataPump chip provides high speed SCI links, sends and receives packets, and manages the data transfer on the SCI physical layer.

#### 4.1 SCI Node Model

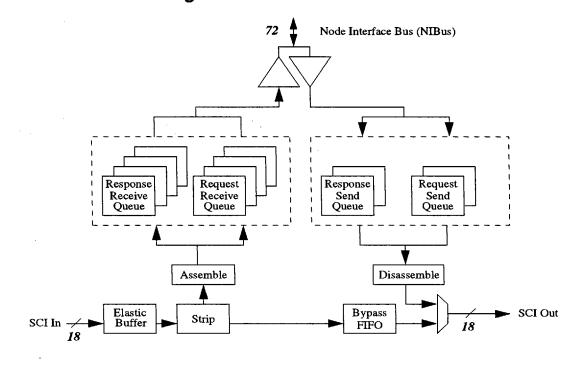

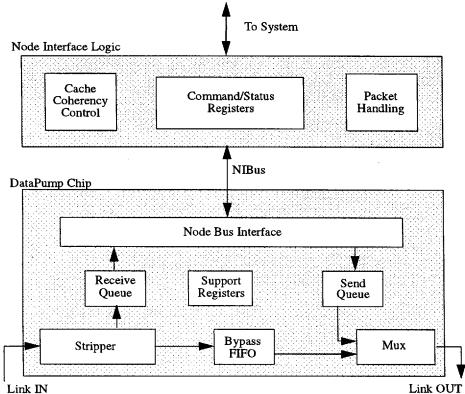

A complete SCI node consists of high speed SCI input and output links, queues for receiving and sending packets, a bypass FIFO for storage when the node is sending a packet, and upper level protocol management for transaction handling. Figure 4.1 shows a block diagram of an SCI node.

Figure 4.1 : SCI Node Mode

The SCI function is broken into two distinct blocks. The physical link interface and queues for packets are handled on the DataPump chip, also known as a link controller. The higher level protocol such as packet handling, cache coherence, CSR (control and status register) register support, and interface to the system is handled in node-specific interface logic.

Therefore, the DataPump chip takes care of getting data packets on and off the high speed SCI link and transferring those packets to and from the node interface logic.

9502331 0003522 947 |

G52164-0 Rev. 3.0 2/27/97 © VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

# Preliminary Data Sheet VSC7201C

### 4.2 DataPump Block Description

The basic block diagram of the DataPump is shown in Figure 4.1. Data is received at the stripper block on the link inputs.

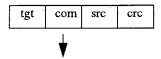

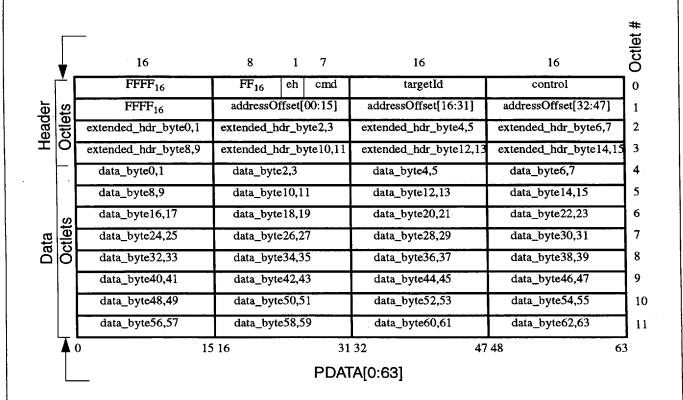

The start of a data packet contains header information. The first 16-bit symbol in the header is the nodeId address of the target node to receive the packet. The stripper block checks this targetId to see if the packet is for this node. If so, the packet is stripped off the ringlet. If there is receive queue space available, the packet will be stored for later unloading by the node controller. If there is no queue space available the received packet will be discarded and a message will be sent to the sender to retry the packet again later.

The receive queue block is split into storage for two types of packets, requests and responses. There is room for up to four packets of each type. Within receive request or response queues, slots are assigned on a first-in/first-out basis.

If the packet is not intended for this node it is sent through the bypass FIFO. The bypass FIFO is required to store a packet as it is received if the DataPump is sending data at the same time. The send queue can only begin to transmit a packet if the bypass FIFO is empty. It is only allowed to transmit one packet at a time before it must again check the bypass FIFO. Therefore, the storage size of the bypass FIFO must be large enough to buffer the largest packet size which can be sent.

The send queue is also split into two types, requests and responses, of which there are two queue slots for each type. The queue slots are loaded from the node interface logic and the slot loading order and transmission order is based on packet age.

The DataPump also contains bus interface logic for communication with the node interface logic and on-board registers for node control and status register (CSR) support. However, on-chip registers are only provided to control the operation of the DataPump - full CSR support according to IEEE Std 1212-1991 must be provided by the node interface logic.

### 4.3 Physical Layer Connection

The SCI physical layer connection consists of 18 differential input and output signals. The inputs consist of 16 data signals (PSCIDI[0:15]), a flag bit (PSCIFI) used to delimit packets, and a strobe signal (PSCISI) for latching incoming data. The outputs consist of 16 data (PSCIDO[0:15]), a flag (PSCIFO), and strobe (PSCISO).

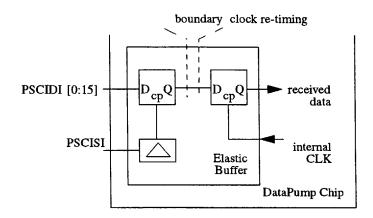

Each 16-bit data quantity transferred is called a symbol and is clocked on each rising and falling edge of the strobe signal. The 16 data plus flag signals transition in phase every 2ns (250 MHz) giving an effective data transfer rate of 1Gbyte/sec. Figure 4.2 illustrates these signals using single-ended notation.

SCISI

SCIDI[0:15]

SCIFI

2 ns

Figure 4.2 : SCI Link Signals

The received strobe PSCISI is used for latching data and flag, but is not used for generating the output strobe PSCISO. The DataPump chip generates its own internal clock for clocking data through the high speed data path and driving out PSCIDO[0:15], PSCISO, and PSCIFO.

The internally generated clock is not guaranteed to be in phase with nor at precisely the same frequency as the incoming PSCISI. Therefore, all SCI link input signals are received on chip through the elastic buffer which re-times the signals to the internal high speed clock and inserts or deletes symbols with a logic state machine to account for small frequency

9502331 0003523 886 📟

© VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

1 GByte/Sec SCI Compliant Link Controller

differences between incoming symbols and the internal clock. The clocking boundaries and elastic buffer data re-timing function are shown in Figure 4.3.

Symbols called idle symbols are transmitted between data packets or if no packets are being sent. The elastic buffer will only delete idle symbols, not symbols within a packet. Every packet must be followed by at least one idle symbol. This guarantees that there will always be enough idle symbols received which can be deleted in order to make up for the worst case clock frequency difference.

Figure 4.3: Elastic Buffer Data Re-timing

#### 4.4 Packet Formats

SCI defines two groups of packet types; those packets involved in the logical protocol (send and echo packets), and other special link related packets.

The VSC7201C does not support any of the special init packets except for the SYNC packet.

#### 4.4.1 Basic Send and Echo Packets

The packets involved in the logical protocol consist of four types; request-send, request-echo, response-send, and response-echo.

Logical protocol transactions are initiated with a requester and completed by a responder. Each transaction consists of two sub-actions; a request sub-action wherein command and possibly data are passed to the responder and a response sub-action where completion status and possibly data are returned to the requester.

Each sub-action involves two packet transfers. One is a send packet initiated at the output link of a producer node and the second is an echo packet returned by the consumer node and received on the input link of the producer node.

Hence, normal SCI transactions are usually four-way transactions initiated with a send-request packet from a requester. The target of the request (the responder) sends an acknowledgment of receipt of the request packet by returning a request-echo packet. When the responder is ready with the requested data, it sends a response-send packet and the original requester acknowledges with a response-echo packet.

All packets are an integer multiple of four symbols in length. The DataPump supports all SCI packet types except 256-byte block sizes. Therefore, the largest packet size is 96-bytes, or 48 16-bit symbols.

The DataPump also uses full 16-bit nodelds for targetId and sourceId decoding.

**9**502331 0003524 712 **1**

G52164-0 Rev. 3.0 2/27/97 © VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

# Preliminary Data Sheet VSC7201C

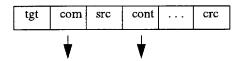

Figure 4.4: Request Send Packet Format

| targetId ( <fff0<sub>16)</fff0<sub> |

|-------------------------------------|

| command                             |

| sourceID                            |

| control                             |

| addressOffset[00.15]                |

| addressOffset[16.31]                |

| addressOffset[32.47]                |

| ext (0 or 16 bytes)                 |

| data<br>(0, 16, 32, 48 or 64 bytes) |

| cyclic-redundancy code (CRC)        |

The basic request-send packet construction is shown in Figure 4.4. Each block in Figure 4.4 comprises a 16-bit symbol value. The targetId is the 16-bit nodeId of the target node. Node ID values above  $FFFO_{16}$  are special reserved values.

The command and control fields contain command and flow-control information. Some of the bits used for flow-control are modified by the DataPump chip. See sections 4.6 and 4.7. The sourceId is the 16-bit node ID of the sending node. The 48-bit address offset is interpreted by the responder.

A packet may also contain a 16-byte extended header. The presence of extended header is indicated by a bit (com.eh) in the command field.

The CRC (cyclic redundancy code) symbol at the end of the packet allows for error checking the entire data packet upon reception.

When transmitting a packet from the send queue, the DataPump forms the CRC and appends it to the end of the packet. When receiving a packet into the receive queue, the DataPump forms the CRC as the packet is being received and checks the generated value against this transmitted value to ensure data correctness.

Figure 4.5: Request-Echo and Response-Echo Packet Format

| targetId ( <fff0<sub>16)</fff0<sub> |

|-------------------------------------|

| command                             |

| sourceId                            |

| cyclic-redundancy code (CRC)        |

The node interface logic external to the DataPump does not need to check or generate the CRC.

Echo packets are 4 symbols long containing the source and target IDs exchanged, a command symbol which is a modified version of the send command, and the CRC.

**-** 9502331 0003525 659 **-**

© VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

1 GByte/Sec SCI Compliant Link Controller

The DataPump automatically generates all required echo packets as a result of received packets. The node interface logic external to the DataPump cannot generate or receive echo packets.

The basic echo packet is shown in Figure 4.5.

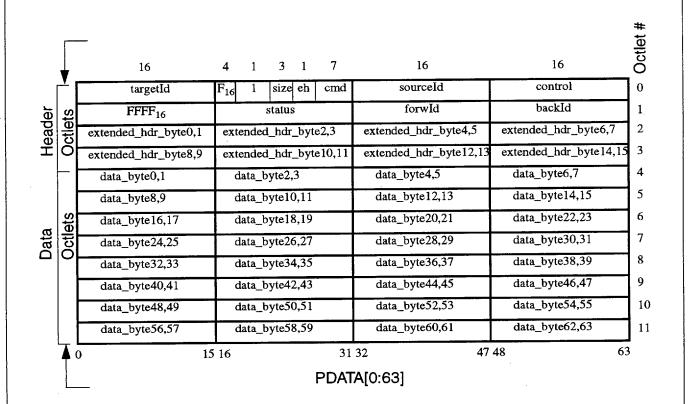

Figure 4.6: Response-Send Packet Format

| targetId ( <fff0<sub>16)</fff0<sub> |

|-------------------------------------|

| command                             |

| sourceId                            |

| control                             |

| status                              |

| forwId                              |

| backId                              |

| ext (0 or 16 bytes)                 |

| data                                |

| (0, 16, 32, 48 or 64 bytes)         |

| cyclic-redundancy code (CRC)        |

The basic response packet is shown in Figure 4.6. The response packet is similar to request packet except a status symbol and two nodeld pointers called forwld and backld are returned. These are used in the cache coherency scheme.

The DataPump does not, however, handle any upper level cache coherency protocol management. Response packets are simply queued with a length of packet indicator.

The DataPump also manages data flow control information contained within packets and idle symbols. When no packet is being received, 16-bit idle symbols are received. The DataPump stores and transmits these idles, while checking and managing flow control information contained in the idle symbol. For more detailed information about packet types and fields within packets, consult the IEEE Std 1596-1992.

■ 9502331 0003526 595 N

© VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

# Preliminary Data Sheet VSC7201C

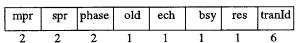

### 4.4.2 Command and Control Symbols

The DataPump uses certain bits in the command and control fields for transaction and flow control. The format for these fields is defined in Figure 4.7. These fields are explained briefly in Table 4.1

Figure 4.7: .Command and Control Symbols

send packet format:

send command symbol (com):

| mpr | spr | phase | old | ech | eh | cmd |

|-----|-----|-------|-----|-----|----|-----|

| 2   | 2   | 2     | 1   | 1   | 1  | 7   |

send control symbol (cont):

| trc | todExp | todMant | tpr | tranId |

|-----|--------|---------|-----|--------|

| 1   | 5      | 2       | 2   | 6      |

echo packet format:

echo command symbol (com):

1 GByte/Sec SCI Compliant Link Controller

**Table 4.1: Command and Control Bit Fields**

| Bit Field                 | Description                                                                                                                        |  |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|

| com.mpr                   | Maximum ringlet priority field. Passed but not used by DataPump.                                                                   |  |  |

| com.spr                   | Send priority. Passed but not used by DataPump.                                                                                    |  |  |

| com.phase                 | Used by queue control on DataPump. See 4.7 Queue Allocation.                                                                       |  |  |

| com.old                   | Packet aging used by scrubber DataPump to remove old packets.                                                                      |  |  |

| com.ech                   | Indicates echo packet; com.ech=0 for send, com.ech=1 for echo. Set by DataPump during transmission.                                |  |  |

| com.eh                    | Indicates use of extended header. If set to 1 a 16-byte extended header is present.                                                |  |  |

| com.cmd                   | Specifies transaction command.                                                                                                     |  |  |

| com.bsy                   | Used in echo packet to indicate no queue space available on target node. See 4.7 Queue Allocation.                                 |  |  |

| com.res                   | In echo packet indicates request or response echo; com.res=0 for request, com.res=1 for response.                                  |  |  |

| com.tranId<br>cont.tranId | Transaction Id set by requester in send-request packet. This tranld value is used in all subaction packets related to the request. |  |  |

| cont.trc                  | Trace bit. Passed but not used by DataPump.                                                                                        |  |  |

| cont.todExp               | Time-of-death; exponent. Passed by but not used by DataPump.                                                                       |  |  |

| cont.todMant              | Time-of-death; exponent. Passed by but not used by DataPump.                                                                       |  |  |

| cont.tpr                  | Transmit priority, set by node interface. Passed but not used by DataPump.                                                         |  |  |

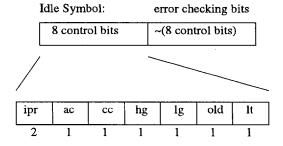

#### 4.4.3 Idle Symbols

Idle symbols fill the spaces between packets. They contain bits associated with ringlet flow control which the DataPump uses to manage the SCI link. Figure 4.8 shows the bit fields and Table 4.2 defines these fields. The least significant byte is the complement of the most significant byte and is used for a simple parity check.

Figure 4.8 : Idle Symbol Fields

G52164-0 Rev. 3.0 2/27/97

© VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

# Preliminary Data Sheet VSC7201C

#### **Table 4.2: Idle Symbol Field Descriptions**

| Bit Field                                                  | Description                                                            |  |

|------------------------------------------------------------|------------------------------------------------------------------------|--|

| idle.ipr                                                   | Idle-priority used for ringlet priority; not used. Set to low.         |  |

| idle.ac                                                    | Allocation count, toggles when all nodes are enabled to transmit.      |  |

| idle.cc                                                    | Circulation count, indicates when idle has circulated around ringlet.  |  |

| idle.hg                                                    | High go bit; not used. Set to low.                                     |  |

| idle.lg                                                    | Low go bit; see Section 4.6 Bandwidth Allocation.                      |  |

| idle.old                                                   | Packet aging bit - used by scrubber to remove old packets from ringlet |  |

| idle.lt Low type priority class bit; not used. Set to low. |                                                                        |  |

### 4.4.4 SYNC Packet and its Flag Encoding

The sync packet is used during initialization for synchronizing the link and can also be sent during normal operation by asserting the NSYNCRQ pin. Although the VSC7201C doesn't have autodeskewing on its input pins, future versions may use the received SYNC packet for deskewing SCI inputs. The format for the SYNC packet is shown in Figure 4.9. No other SCI defined special packets (e.g. ABORT, RESET, etc.) are supported or needed by the VSC7201C. For further information on reset and initialization and the use of the SYNC packet, see sections 4.10 DataPump Reset.

Figure 4.9: SYNC Packet Format

| Symbol |                   | Flag |

|--------|-------------------|------|

| 0      | 11111111111111111 | 1    |

| 1      | 0000000000000000  | 0    |

| 2      | 0000000000000000  | 0    |

| 3      | 0000000000000000  | 0    |

| 4      | 0000000000000000  | 0    |

| 5      | 0000000000000000  | o    |

| 6      | 0000000000000000  |      |

|        | 0000000000000000  |      |

| 7      |                   | 0    |

SYNC Packet

#### 4.4.5 Packet and Idle Alignment to SCI Strobe

For performance reasons the DataPump aligns all packet transmissions to start with the first symbol driven when PSCISO (strobe out) is high. The DataPump also expects to receive packets aligned so that the first symbol is received when PSCISI (strobe in) is high.

Therefore, the minimum number of idle symbols between packets will be 2 and idle deletion and insertion will be done on idle pairs. Idle pairs are also aligned with strobe high followed by strobe low.

**■** 9502331 0003529 2T4 **■**

© VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

1 GByte/Sec SCI Compliant Link Controller

#### 4.5 Transaction Commands

The command in an SCI send packet identifies one of four main types of transactions. Those are response-expected request, move request, event request, and response. The DataPump only decodes the transaction command to determine if it is greater or less than 124 indicating a response versus request packet, or if it is an event00 (clockStrobe) command.

Data payload size within a send packet is only checked for the SCI legal multiple of 8 symbols and for excessive length. When the end of a send packet is received it is checked for length equal to a multiple of 8 symbols and if not is rounded out to 8 symbols, then processed normally.

A send packet not targeted for this VSC7201C is not stripped and is only checked for size less than or equal to 48 symbols. Packets of this length will be bypassed without error as long as they are a multiple of 8 symbols.

Packets which are stripped by the DataPump are checked for length less than or equal to the maximum queue buffer size of 48 symbols. As long as stripped packets are of this size and are a multiple of 8 symbols they will be queued normally.

The transaction types uniquely treated by the DataPump are summarized in Table 4.3. Packet sizes for these commands are only checked as outlined above. For example, a nread256 command implies a data payload of 256-bytes but is not checked for that payload size by the DataPump and could in fact be only 64-bytes.

**Table 4.3: DataPump Receive Packet Handling**

| Received Packet Type                            | Packet Handling                                          | Comments                                                                                                                   |  |

|-------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|

| response-expected request                       | strip if targeted node and<br>generate echo; else bypass | DataPump only checks command value is less than 124 and not event00                                                        |  |

| response                                        | strip if targeted node and<br>generate echo; else bypass | DataPump only checks that command value is greater than or equal to 124                                                    |  |

| directed move (dmovexx)                         | strip if targeted node and<br>generate echo; else bypass | Command value not distinguished from response-<br>expected request                                                         |  |

| broadcast move<br>(rmovexx, smovexx)            | not supported                                            | Command value not distinguished from response-<br>expected request                                                         |  |

| clockStrobe<br>(event00, time-of-day clock)     | strip and toss if targeted node; else bypass             | See Section 4.5.1 Event00 (clockStrobe) Transaction                                                                        |  |

| event16, event64                                | not supported                                            | Command value not distinguished from event00                                                                               |  |

| echo packet strip if targeted node; else bypass |                                                          | stripped echo packet information is used to determine send packet status; see send packet handling in 4.7 Queue Allocation |  |

#### 4.5.1 Event00 (clockStrobe) Transaction

The event00 transaction is supported by the DataPump as the (time-of-day) clockStrobe signal. If targeted to a DataPump, the Event00 packet is accepted immediately and no echo is generated. If received and not targeted to the DataPump, it bypasses the packet.

The DataPump which transmits an event00 targeted to itself from its send queue is called the clockStrobe master. Datapumps which bypass the event00 are clockStrobe slaves. When the event00 packet is transmitted from the send queue it is immediately removed from the queue. When the event00 packet completes its trip around the ringlet and returns to the clockStrobe master, it is stripped and discarded.

When an event00 packet is transmitted on the DataPump's outputs, the clockStrobe pin PCLKSTB is asserted to the node interface logic. PCLKSTB is deasserted when the event00 is received and stripped. The node interface logic can use this signal to enable a timer to measure time around the ringlet.

When an event00 packet is bypassed through a DataPump the PCLKSTB signal is asserted for a duration of approximately 48ns, then deasserted. The through time taken to bypass the packet is also measured by counting SCI clock cycles in the DP\_CLKTHRU register described in Section 4.8. Other event packets are treated like event00 packets.

9502331 0003530 T16

© VITESSE SEMICONDUCTOR CORPORATION

Page 13

G52164-0 Rev. 3.0 2/27/97

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

# Preliminary Data Sheet VSC7201C

### 4.6 Bandwidth Allocation and the Low-go Bit

Since SCI nodes are connected in ringlets, multiple transactions may be transmitted concurrently. Since there is no arbitration for access to the ringlet, certain bandwidth allocation protocols have been defined to guarantee bandwidth to all nodes

Bandwidth allocation is managed by two mechanisms. These are; 1) transmission flow control through the use of a token, or "go" bit, in idle symbols which determine when a node is allowed to transmit, and 2) priority schemes using command.mpr, command.spr, control.tpr, and idle.ipr fields which allow unfair nodes to determine the priority for transmission of unsent packets.

The DataPump uses the idle.lg "low-go" bit for flow control but does not support any priority allocation mechanisms. Since idles are always received in aligned pairs (see Section 4.4.5) the idle.lg bits in idle pairs are essentially or'ed together.

A DataPump can only transmit a packet from its send queue when its bypass FIFO is empty and it can postpend the transmission packet to an idle pair with the low-go bit set. If no idles with low-go set are passed through to the transmitter then the DataPump is disabled from sending packets from the send queue.

The low-go bit in outgoing idles is blocked (set to zero) whenever the DataPump's bypass FIFO is not empty. This prevents a downstream DataPump from transmitting and will eventually free up ringlet bandwidth so the blocked DataPump can empty its bypass FIFO.

While the DataPump is blocking low-go, any idle received with low-go set will set the saved value of low-go which will be transmitted in the first pair of idle symbols after the DataPump is no longer blocked (i.e. bypass FIFO is emptied).

Finally, if a node is not blocked and an idle pair with low-go set is transmitted, the idle pair immediately following will also have their low-gos set. These low-go extensions will prevent a complete loss of low-go bits in a ringlet.

If all low-go bits in all idles are cleared (thus no one is allowed to transmit), the scrubber will detect this and set an error condition.

#### 4.6.1 Allocation Count and Circulation Count

Two flag bits in the idle symbols, idle.ac and idle.cc, keep track of when all producers have had the opportunity to transmit and when an idle symbol has circulated completely around the ringlet. These bits are controlled by the scrubber.

Circulation count is passed by non-scrubber nodes and toggled by the scrubber. When a non-scrubber node is transmitting idles, the value of idle.cc on output is set to the most recently received idle.cc value. In a scrubber node, output idle.cc is the complement of the most recently received idle.cc value. Thus, idle.cc acts as a token which takes roughly the latency of the ringlet to circulate.

The allocation count bit, idle.ac, is similar to idle.cc except it is a token which indicates when all nodes have had an opportunity to transmit. When the idle.ac bit toggles, a time interval has elapsed in which all nodes have had the opportunity to transmit.

The idle.ac bit is passed by a node when its output is not blocked. When its output is blocked (i.e. transmitting from its send queue or emptying bypass FIFO), it must output the idle.ac value saved from the last idle received before transmission began. Therefore, idle.ac cannot change at the output of a blocked node. It can only change after the node has recovered and is enabled for transmission. A non-scrubber node will pass the value of idle.ac which was last received. The scrubber will output the complement of this value. The allocation count and circulation count flags are used to detect error conditions or set time-outs as described in following sections.

#### 4.7 Queue Allocation

Bandwidth allocation protocols guarantee that all nodes get bandwidth to transmit packets. However, if the queues on a consumer node become filled, then new send packets for this node are echoed with a "busy" status and must be re-sent until queue space is available and they are accepted. Queue allocation protocol includes a simple reservation scheme insuring all producer's packets eventually get accepted by consumers.

This reservation mechanism is described in the SCI standard. There are four queue allocation states which the ringlet may

🖿 9502331 0003531 952 **=**

© VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

1 GByte/Sec SCI Compliant Link Controller

be in at any time. These are SERVE\_NA, SERVE\_A, SERVE\_NB, and SERVE\_B. Also, send packets and busy echo packets contain a phase field which has values NOTRY, DOTRY, RETRY\_A, and RETRY\_B.

The DataPump implements this A/B aging protocol. In states SERVE\_NA or SERVE\_NB, basically all packets are accepted if queue space is available. If any packets are busied, the queue will transition to SERVE\_A or SERVE\_B.

In SERVE\_A and SERVE\_B states, the DataPump will only accept packets with phase RETRY\_A or RETRY\_B respectively. Exiting either SERVE\_A or SERVE\_B is handled by maintaining counters for phase A and B which accumulate the number of busied packets for retry and decrementing the counter every time a packet is accepted (the count is incremented every time a packet sent with DOTRY phase is returned busied of type A or B). When the count is back to zero, the queue transitions back to SERVE\_NA or SERVE\_NB.

The busied counter is 4-bits. If the number of busied packets is less than 15 then the DataPump will exit SERVE\_A or SERVE B when all busied packets have been accepted.

If the number of busied packets equals or exceeds 15, exiting SERVE\_A or SERVE\_B will be accomplished by a time-out on the allocation count counter. The allocation counter increments each time all nodes on the ringlet have had the opportunity to transmit. If no more RETRY\_A or RETRY\_B packets have been received within 4 allocation intervals, the queue times out and transitions to SERVE\_NA or SERVE\_NB.

A time-out on the allocation counter when the busied packet counter did not overflow is a ringlet state error and is described in the error handling Section 4.9.

Separate state machines for request and response queues process packet reservations separately to avoid deadlock situations.

For more detailed descriptions of the A/B reservation scheme or the com.phase, com.bsy, or idle.ac fields refer to the SCI standard, Section 3.7.

Queue selection protocol specifies that for a node with multiple request or response send queue entries only one packet at a time may be sent with DOTRY phase for each queue type, request or response. Also, the producer should alternate transmission order between request and response so that both queues are serviced equally. For more information on queue selection, see Section 5.3 Send Queue SCI Transmission Order.

### 4.8 Control and Status Support Registers

SCI follows the CSR (Control and Status Register) architecture as defined in IEEE Std 1212-1991. An SCI node must have the defined registers and behavior as outlined in the standards.

The DataPump does not contain any CSRs but has configuration and status registers modeled after the CSR standard to provide the functionality required to implement full CSR compliance on the node interface logic.

CSR registers are software visible to both the processor elements connected to a node and to remote nodes through the SCI links. CSRs are address mapped into memory address space as defined by the 64-bit fixed address model, which allocates the most significant 256Mbyte space to registers.

Remote access through SCI is provided by read and write request transactions to that address space. The DataPump does not, however, decode requests to CSR address space. It simply queues request packets and sends them up to the node interface logic. The node interface logic is responsible for servicing the CSR requests (both local and remote).

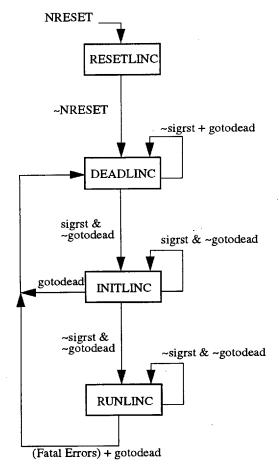

The node interface logic must use the support registers on the DataPump to set state and values in the node CSRs. For example, the DP\_STATE register indicates the operational state of the DataPump. If the DataPump has been reset from the SCI link, it will enter the "initializing" state reflected by the DP\_STATE resetlinc bit. The logical SCI node's STATE CSR is then the combination of the DataPump state and the rest of the node interface logic state.

The CSR support registers can also be accessed through the Test Access Port scan port. See 9.0 Test Access Port for details.

These registers are initialized by toggling the NRESET pin. A complete description of chip reset is given in Section 4.10 DataPump Reset. A summary of the CSR support registers on the DataPump is given in Table 4.6.

**- 9502331 0003532 899**

© VITESSE SEMICONDUCTOR CORPORATION

# Preliminary Data Sheet VSC7201C

### Table 4.6: DataPump CSR Support Registers

| Register            | Offset                                                                         | Description                                                                                                           |

|---------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| DP_STATE            | 000 <sub>16</sub>                                                              | The DP_STATE register contains the current status of the DataPump. It also contains the chip revision number.         |

| DP_NODEID           | 008 <sub>16</sub>                                                              | Contains nodeId value and distanceId value from reset initialization.                                                 |

| DP_CL <b>KTH</b> RU | 070 <sub>16</sub>                                                              | Contains the time interval between arrival and departure of the clockStrobe transaction.  Measured in 4ns increments. |

| DP_ERRLOG           | 184 <sub>16</sub>                                                              | Contains error codes and diagnostic information.                                                                      |

| DP_SENDQ_TAG[3:0]   | 300 <sub>16</sub> ,304 <sub>16</sub> ,<br>308 <sub>16</sub> ,30C <sub>16</sub> | Provide read access to the send queue trankd and targetId values for each packet in the queue.                        |

| DP_PC_CONFIG0       | 32016                                                                          | PPC0 output pin selection/configuration and mask/compare values for performance counters.                             |

| DP_PC_CONFIG1       | 32816                                                                          | PPC1 output pin selection/configuration.                                                                              |

These registers are detailed in the following sections. Tables for each register indicate the register functionality and use the following code for access restrictions; RO - read only; RW - read or write value to 1 or 0; RC - read or clear value on write. The clear function is NOT a bitwise clear. Just writing the CSR register with any data value will clear the register if it is RC.

1 GByte/Sec SCI Compliant Link Controller

4.8.1 DP\_STATE (Offset 00016)

### Table 4.7: DP\_STATE Register

| Name         | Bits  | Access | Description                                                                                              |

|--------------|-------|--------|----------------------------------------------------------------------------------------------------------|

| rev_num[0:3] | 0:3   | RO     | Hardwired chip revision number; 0010 for this chip.                                                      |

| reserved     | 4:7   | -      | (Test usage only: timeadj[7:4])                                                                          |

| stayrun      | 8     | RW     | Stay in running state if a fatal link error occurs when set.                                             |

| moretry      | 9     | RW     | When asserted, enables Queue Allocation as described in Section 4.7. When negated compatible with 7201A. |

| reserved     | 10:11 | -      | (Test usage only: timeadj[2:0])                                                                          |

| insync[0:1]  | 12:13 | RO     | Count of the number of valid sync pakets received during initialization state INIT.                      |

| not used     | 15:14 | -      |                                                                                                          |

| gotodead     | 16    | RW     | When asserted forces DataPump to DEAD state.                                                             |

| not used     | 17    | -      |                                                                                                          |

| ruup         | 18    | RO     | When true indicates SCI input strobe is running.                                                         |

| runlinc      | 19    | RO     | When asserted indicates DataPump is in the RUN state.                                                    |

| initlinc     | 20    | RO     | When asserted indicates DataPump is in the INIT state.                                                   |

| sngerr       | 21    | RW     | Capture first fatal error only (single error; see Section 4.9.)                                          |

| not used     | 22    | -      |                                                                                                          |

| sigrst       | 23    | RW     | Used during initialization.                                                                              |

| deadlinc     | 24    | ·RO    | When asserted indicates DataPump is in the DEAD state.                                                   |

| resetlinc    | 25    | RO     | When asserted indicates DataPump is in the RESET state.                                                  |

| inscrub      | 26    | RO     | Indicates this DataPump is the scrubber when asserted.                                                   |

| not used     | 27:30 | -      |                                                                                                          |

# Preliminary Data Sheet VSC7201C

| Name | Bits | Access |                                                                             |

|------|------|--------|-----------------------------------------------------------------------------|

| dreq | 31   | RW     | Disable requests. DataPump will not accept packets from the NIBus when set. |

### 4.8.2 DP\_NODEID (Offset 008<sub>16</sub>)

### Table 4.8: DP\_NODEID Register

| Name         | Bits  | Access | Description                                                                                                                                            |

|--------------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| nodeid[0:15] | 0:15  | RW     | Node ID value for this DataPump. Should be set before normal operation.                                                                                |

| not used     | 16:25 |        |                                                                                                                                                        |

| clkthru[0:5] | 26:31 | RO     | Count of SCI clock cycles elapsed while an event00 packet was bypassed through a clockStrobe slave DataPump (see Section 5.1.11 on the PCLKSTB signal) |

### 4.8.3 DP\_CLKTHRU (Offset 070<sub>16</sub>)

#### Table 4.9: DP\_CLKTHRU Register

| Name         | Bits  | Access | Description                                 |

|--------------|-------|--------|---------------------------------------------|

| nodeid[0:15] | 0:15  | RO     | Node ID value for this DataPump, read-only. |

| not used     | 16:25 | -      |                                             |

| Name         | Bits  | Access | Description                                                                                                                                            |

|--------------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| clkthru[0:5] | 26:31 | RO     | Count of SCI clock cycles elapsed while an event00 packet was bypassed through a clockStrobe slave DataPump (see Section 5.1.11 on the PCLKSTB signal) |

### 4.8.4 DP\_ERRLOG (Offset 184<sub>16</sub>)

NOTE: A CSR register write to this address clears all register bits.

#### Table 4.10: DP\_ERRLOG Register

| Name         | Bits  | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| not used     | 0:2   | -      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| sqfrz[0:3]   | 3:6   | RC     | Send queue slot "freeze" bits. A set bit indicates an error occurred on the packet in that send queue slot and it was "frozen". Slot is freed when bit is cleared. Tag information for each slot is contained in the DP_SENDQ_TAG registers. The correspondence is as follows; sqfrz0 -> DP_SENDQ_TAG0 sqfrz1 -> DP_SENDQ_TAG1 sqfrz2 -> DP_SENDQ_TAG2 sqfrz3 -> DP_SENDQ_TAG3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| tcode[0:7]   | 7:14  | RC     | NIBus transfer errors - (see Table 4.18) bit 7 (sendQfull) - load attempted to full send Q bit 8 (dupTranId) - send req packet had a duplicate tranId bit 9 (sizeErr) - send packet size error bit 10 (NIregPar) - NIBus parity error on register read/write bit 11 (NIsendqPar) - NIBus parity error on send Q load bit 12 - not used bit 13 (rcvQempty) - read attempted from empty receive Q bit 14 (regAddrErr) - register access to bad address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| notruup      | 15    | RC     | Lost input SCI strobe signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| flgerr       | 16    | RC     | Received packet had a flag error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| not used     | 17    | -      | A STATE OF THE STA |

| strperr[0:6] | 18:24 | RC     | SCI input linc stripper errors - bit 18 (badIdle) - idle symbol had a parity error bit 19 (badThruCrc) - bad CRC in bypassed packet bit 20 (badStrpCrc) - bad CRC in stripped packet bit 21 (strpTooLong) - stripped packet greater than 48 symbols bit 22 (tossClkStb) - received extra clockStrobe packet bit 23 (reqAcTmo) - request Q reservation early ac timeout bit 24 (rspAcTmo) - response Q reservation early ac timeout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

**=** 9502331 0003536 434 **=**

© VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

# Preliminary Data Sheet VSC7201C

| Name          | Bits  | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fatalerr[0:6] | 25:31 | RC     | Fatal linc errors - (except for tooLong which is NOT fatal) bit 25 (noInSync) - elastic buffer lost synchronization bit 26 (tooLong) - bypassed packet greater than 48 symbols bit 27 (scrbLgTmr) - scrubber detected no low-go bits in ringlet bit 28 (reqRsvErr) - bad retry phase on request Q bit 29 (rspRsvErr) - bad retry phase on response Q bit 30 (acFail) - ac toggled more than once while output blocked bit 31 (echoUnkn) - stripped echo doesn't match any in send Q |

4.8.5 DP\_SENDQ\_TAG[0:3]

### Table 4.11: DP\_SENDQ\_TAG3 Register Offset 300<sub>16</sub> (Request Queue Slot 0)

| Name        | Bits  | Access | Description                                              |

|-------------|-------|--------|----------------------------------------------------------|

| not used    | 0     | -      |                                                          |

| reserved    | 1:4   | RO     | (Test usage only: rqvld_s[3:0])                          |

| reserved    | 5     | RO     | (Test usage only: sqvld_s0)                              |

| echoNo      | 6     | RO     | target node for packet doesn't reply, packet scrubbed    |

| sndQpar     | 7     | RO     | parity error occurred on packet transmission from send Q |

| sndQto      | 8     | RO     | cc timeout on packet, no echo received in 4 cc times     |

| validbit    | 9     | RO     | valid bit for send Q slot 3                              |

| not used    | 10:25 | -      |                                                          |

| tranid[0:5] | 26:31 | RO     | transaction ID in send Q slot 3 (request slot 0)         |

### Table 4.12: DP\_SENDQ\_TAG2 Register Offset 304<sub>16</sub> (Request Queue Slot 1)

| Name        | Bits  | Access | Description                                              |

|-------------|-------|--------|----------------------------------------------------------|

| not used    | 0     | -      |                                                          |

| reserved    | 1:4   | RO     | (Test usage only: rqvld_s[7:4])                          |

| reserved    | 5     | RO     | (Test usage only: sqvld_s1)                              |

| echoNo      | 6     | RO     | target node for packet doesn't reply, packet scrubbed    |

| sndQpar     | 7     | RO     | parity error occurred on packet transmission from send Q |

| sndQto      | 8     | RO     | cc timeout on packet, no echo received in 4 cc times     |

| validbit    | 9     | RO     | valid bit for send Q slot 2                              |

| not used    | 10:25 | -      |                                                          |

| tranid[0:5] | 26:31 | RO     | transaction ID in send Q slot 2 (request slot 1)         |

**= 9502331 0003537 370 =**

© VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

1 GByte/Sec SCI Compliant Link Controller

# Table 4.13: DP\_SENDQ\_TAG1 Register Offset 308<sub>16</sub> (Response Queue Slot 0)

| Name        | Bits  | Access | Description                                              |

|-------------|-------|--------|----------------------------------------------------------|

| not used    | 0:5   | -      |                                                          |

| reserved    | 1:4   | RO     | (Test usage only: rqvld_sf[3:0])                         |

| reserved    | 5     | RO     | (Test usage only: sqvld_s2)                              |

| echoNo      | 6     | RO     | target node for packet doesn't reply, packet scrubbed    |

| sndQpar     | 7     | RO     | parity error occurred on packet transmission from send Q |

| sndQto      | 8     | RO     | cc timeout on packet, no echo received in 4 cc times     |

| validbit    | 9     | RO     | valid bit for send Q slot 1                              |

| not used    | 10:25 | -      |                                                          |

| tranid[0:5] | 26:31 | RO     | transaction ID in send Q slot 1 (response slot 0)        |

### Table 4.14: DP\_SENDQ\_TAG0 Register Offset 30C<sub>16</sub> (Response Queue Slot 1)

| Name        | Bits  | Access | Description                                              |

|-------------|-------|--------|----------------------------------------------------------|

| not used    | 0:5   | _      |                                                          |

| reserved    | 1:4   | RO     | (Test usage only: rqvld_f[7:4])                          |

| reserved    | 5     | RO     | (Test usage only: sqvld_s3)                              |

| echoNo      | 6     | RO     | target node for packet doesn't reply, packet scrubbed    |

| sndQpar     | 7     | RO     | parity error occurred on packet transmission from send Q |

| sndQto      | 8     | RO     | cc timeout on packet, no echo received in 4 cc times     |

| validbit    | 9     | RO     | valid bit for send Q slot 0                              |

| not used    | 10:25 | -      |                                                          |

| tranid[0:5] | 26:31 | RO     | transaction ID in send Q slot 0 (response slot 1)        |

# Preliminary Data Sheet VSC7201C

### 4.8.6 DP\_PC\_CONFIG0 (offset 320<sub>16</sub>)

The detailed function of these register bits is described in Section 8.0 Performance Counters.

Table 4.15: DP\_PC\_CONFIG0 Register

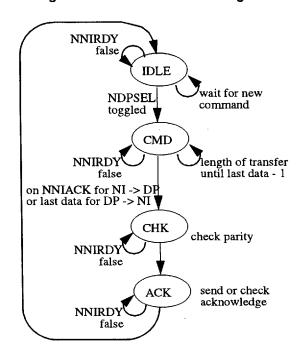

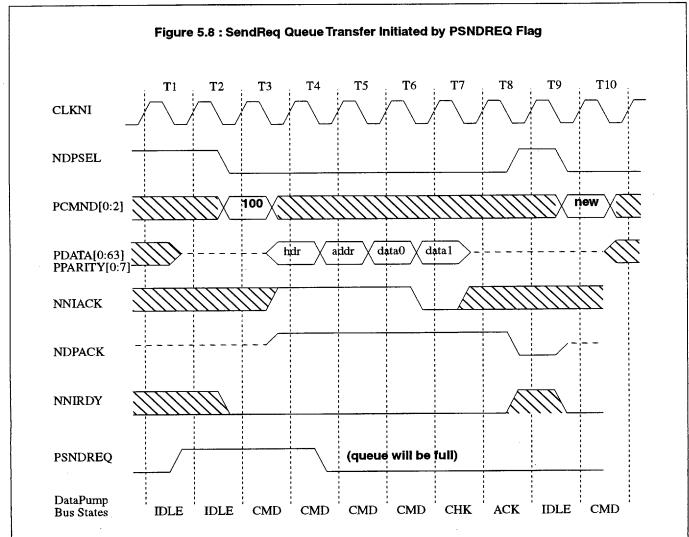

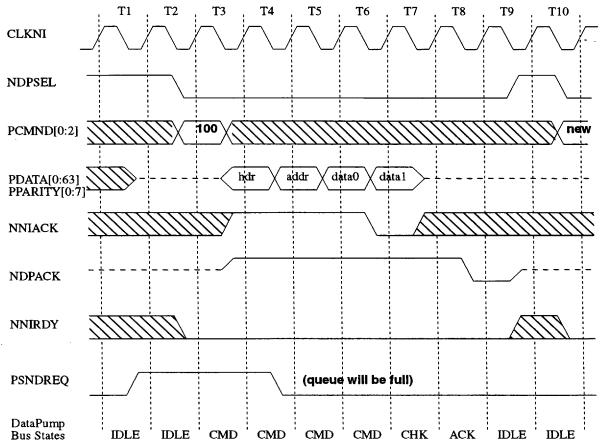

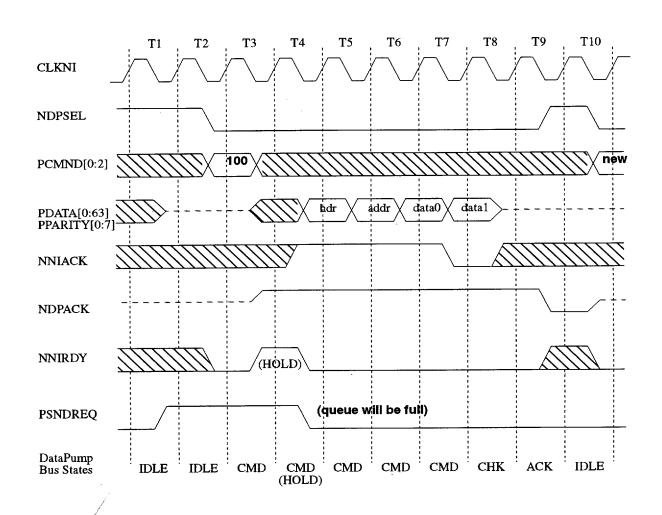

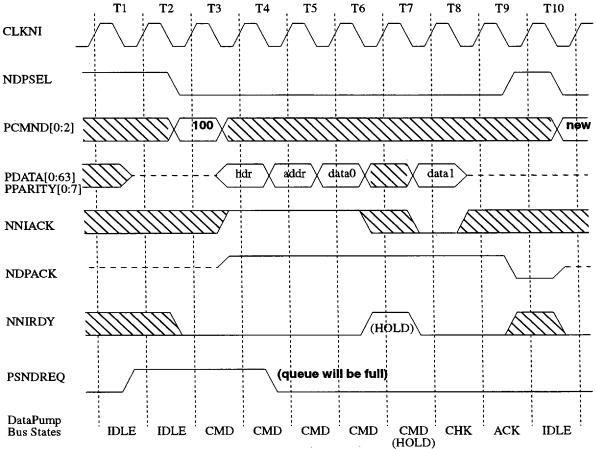

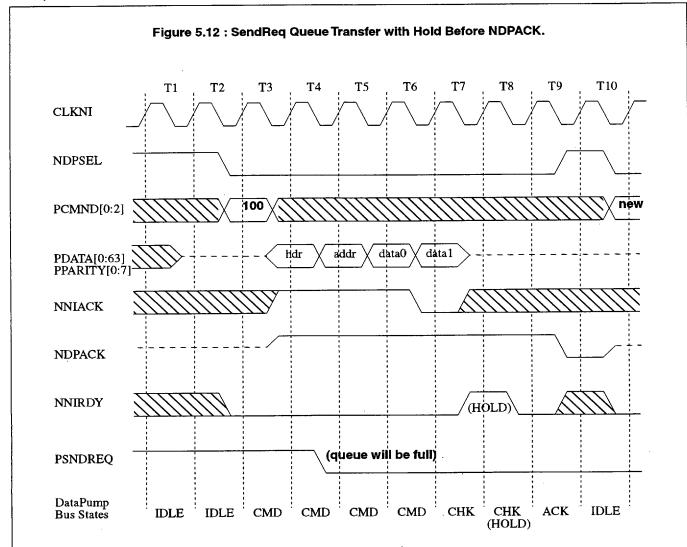

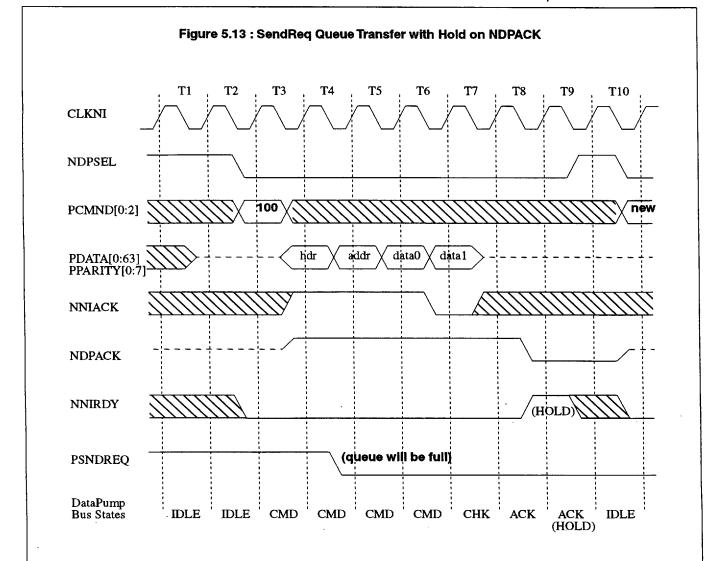

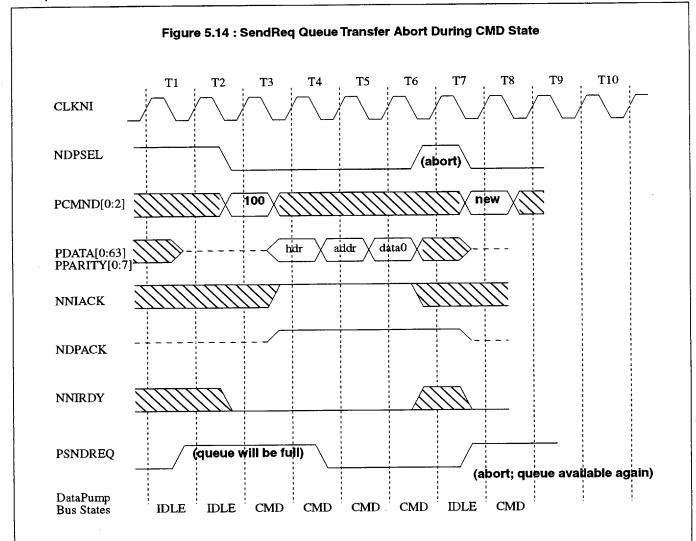

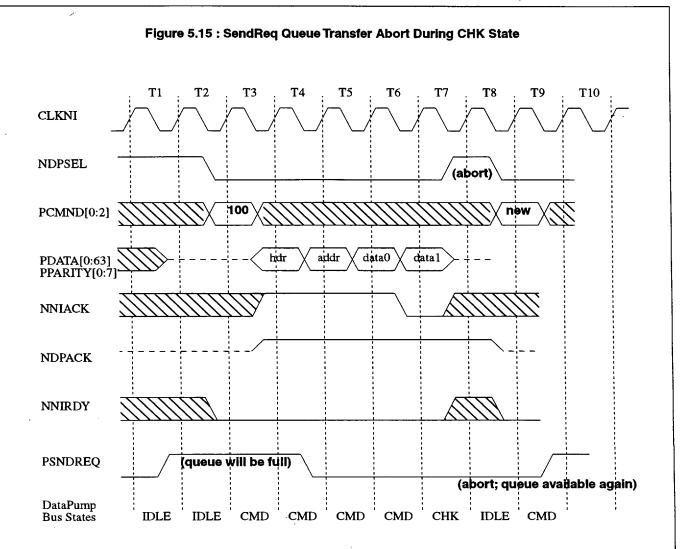

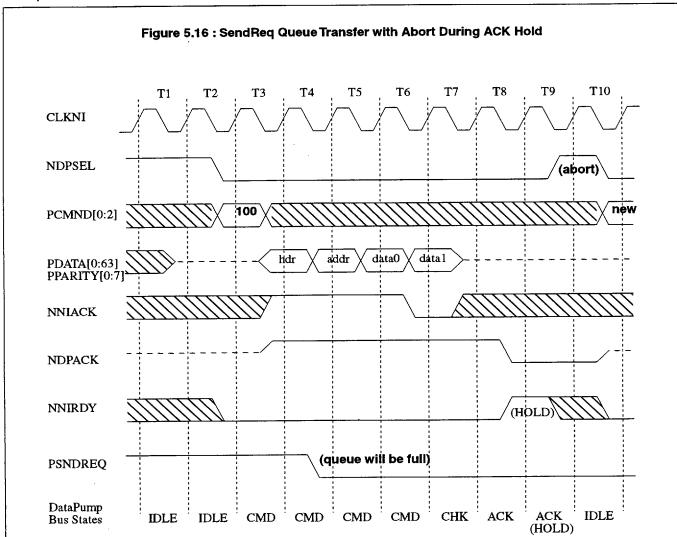

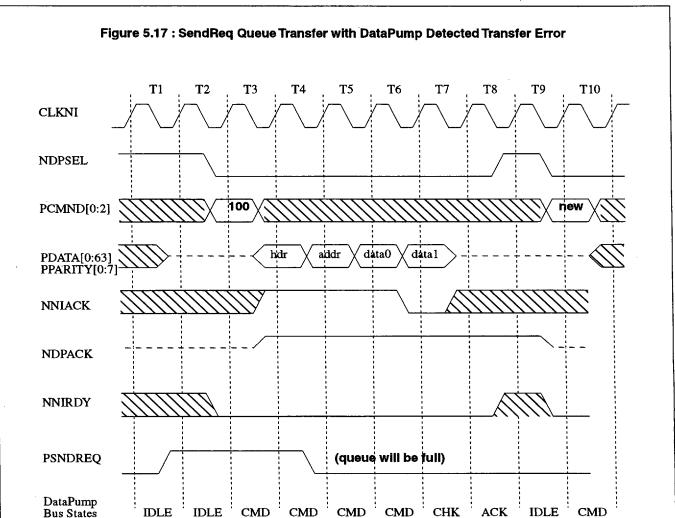

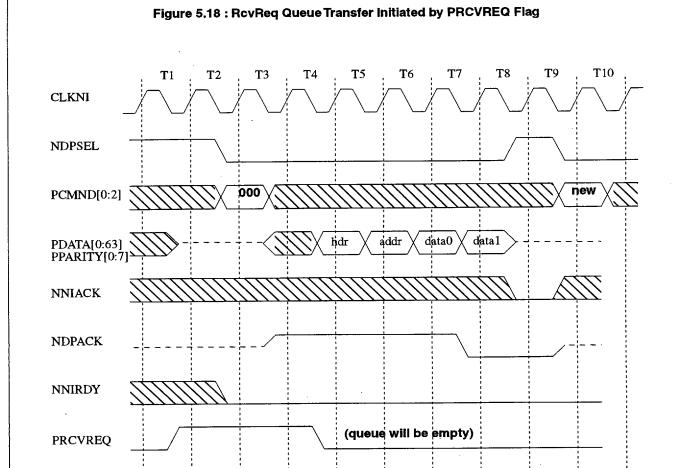

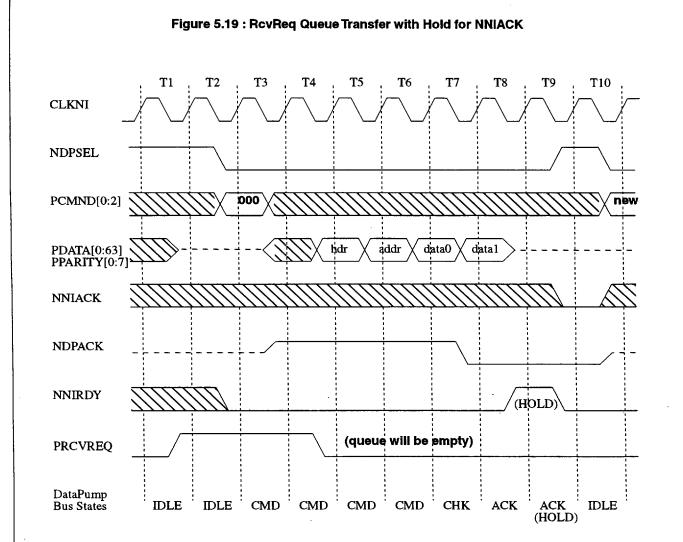

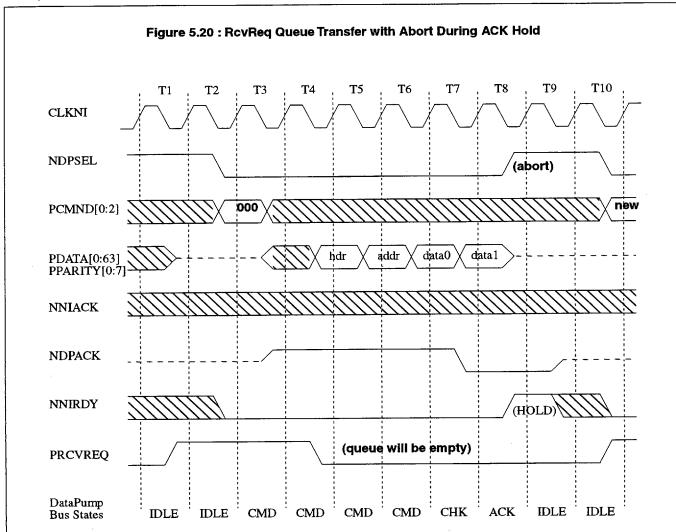

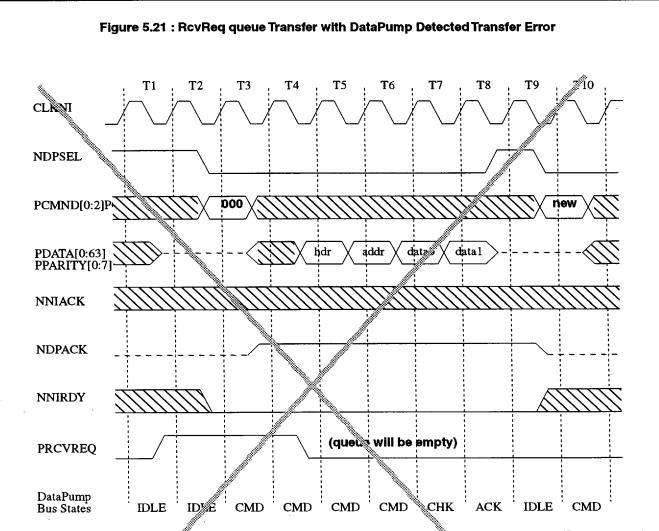

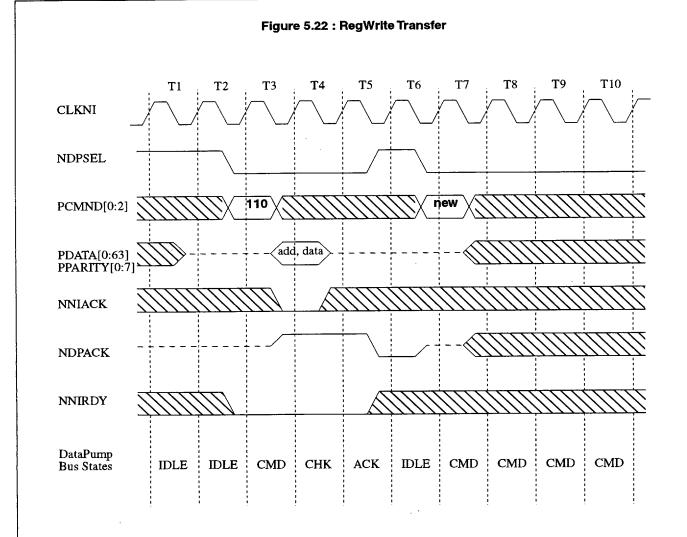

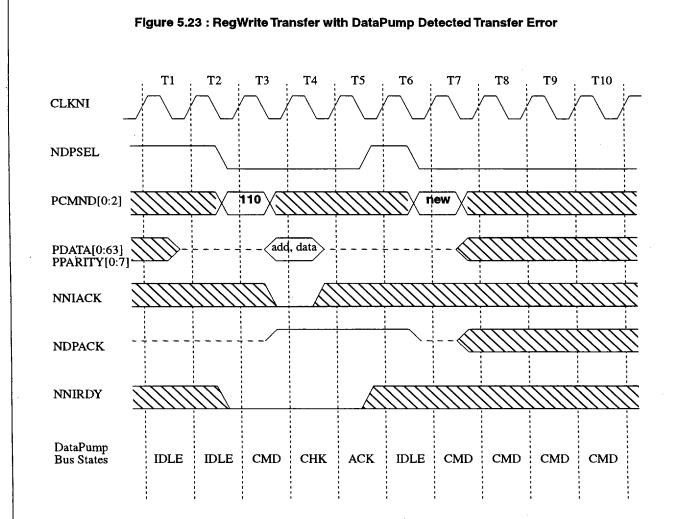

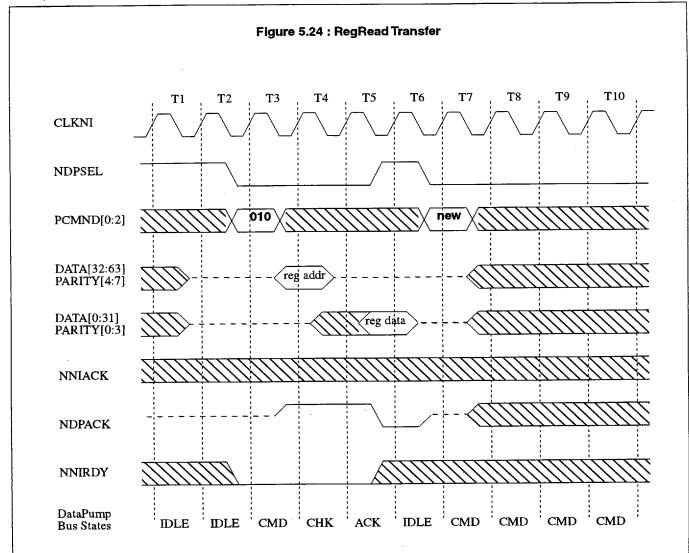

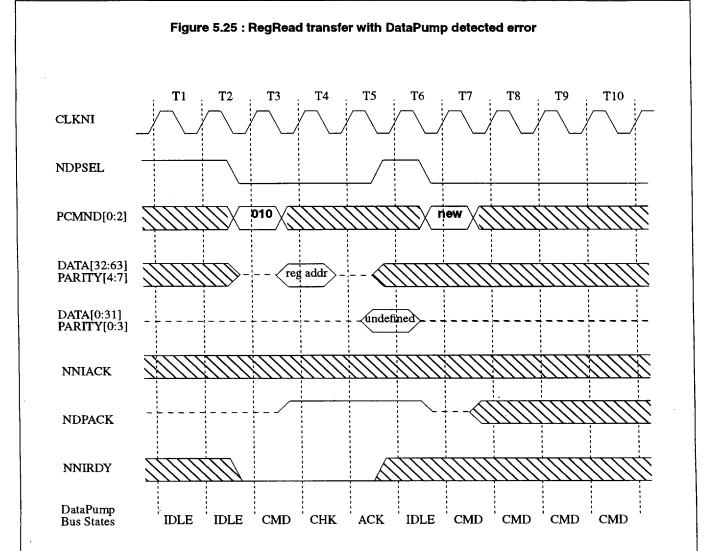

| Name         | Bits  | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |