# 32K X 36 Dual I/O Dual Address Synchronous SRAM

#### **Features**

- · Fast clock speed: 100 and 83 MHz

- Fast Access Times: 5.0/6.0 ns Max.

- Single Clock Operation

- Single 3.3V –5% and +5% power supply VCC

- Separate V<sub>CCQ</sub> for output buffer

- Two chip enables for simple depth expansion

- Address, Data Input, CE1#, CE2, PTX#, PTY#, WEX#, WEY#, and Data Output Registers On-Chip

- Concurrent Reads and Writes

- Two Bidirectional Data Buses

- · Can be configured as separate I/O

- Pass-Through Feature

- Asynchronous Output Enables (OEX#, OEY#)

- LVTTL Compatible I/O

- Self-Timed Write

- Automatic power down

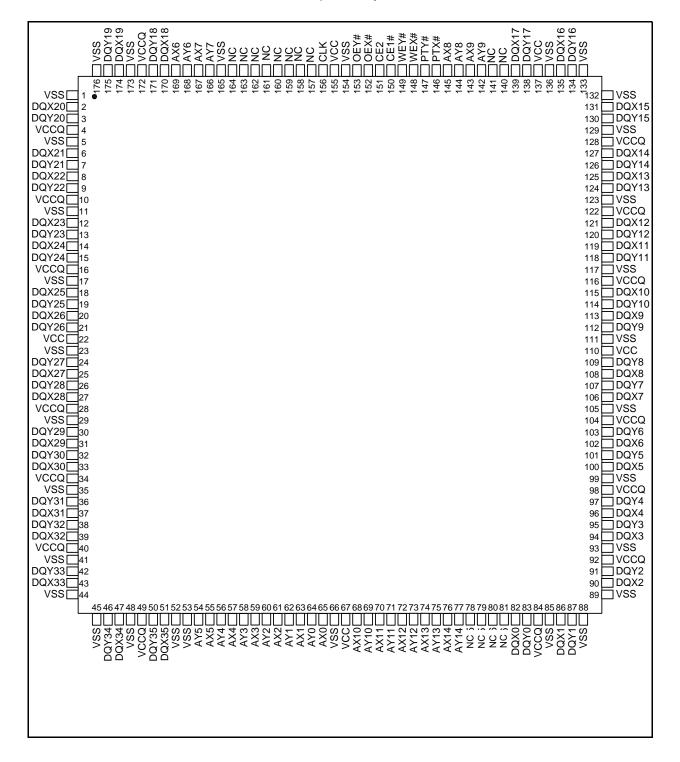

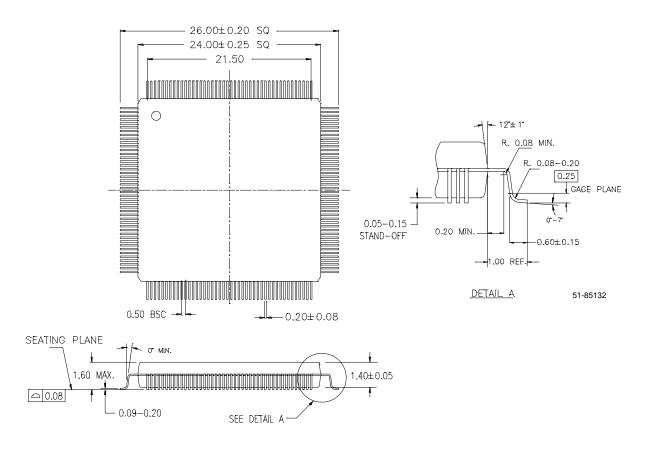

- 176-Pin TQFP Package

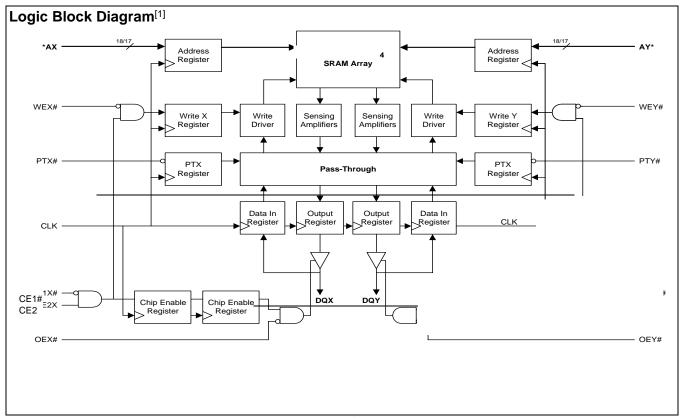

#### **Functional Description**

The CY7C1299A SRAM integrates 32,768 x 36 SRAM cells with advanced synchronous peripheral circuitry. It employs high-speed, low-power CMOS designs using advanced triple-layer polysilicon, double-layer metal technology. Each memory cell consists of four transistors and two high valued resistors.

The CY7C1299A allows the user to concurrently perform reads, writes, or pass-through cycles in combination on the two data ports. The two address ports (AX, AY) determine the read or write locations for their respective data ports (DQX,

All input pins except output enable pins (OEX#, OEY#) are gated by registers controlled by a positive-edge-triggered clock input (CLK). The synchronous inputs include all addresses, all data inputs, depth-expansion chip enables (CE1#, CE2), pass-through controls (PTX# and PTY#), and read-write control (WEX# and WEY#). The pass-through feature allows data to be passed from one port to the other, in either direction. The PTX# input must be asserted to pass data from port X to port Y. The PTY# will likewise pass data from port Y to port X. A pass-through operation takes precedence over a read operation.

For the case when AX and AY are the same, certain protocols are followed. If both ports are read, the reads occur normally. If one port is written and the other is read, the read from the array will occur before the data is written. If both ports are written, only the data on DQY will be written to the array.

The CY7C1299A operates from a +3.3V power supply. All inputs and outputs are LVTTL compatible. These dual I/O, dual address synchronous SRAMs are well suited for ATM, Ethernet switches, routers, cell/frame buffers, SNA switches and shared memory applications.

The CY7C1299A needs one extra cycle after power for proper power-on reset. The extra cycle is needed after V<sub>CC</sub> is stable on the device.

This device is available in a 176-pin TQFP package.

#### **Selection Guide**

|                                   | -100 | -83 |

|-----------------------------------|------|-----|

| Maximum Access Time (ns)          | 5.0  | 6.0 |

| Maximum Operating Current (mA)    | 350  | 300 |

| Maximum CMOS Standby Current (mA) | 100  | 100 |

#### Note:

1. For 32K x 36 Devices, AX and AY are 15-bit wide buses.

### **Pin Configuration**

#### 176-Pin TQFP

# Pin Definitions (176-pin TQFP)

| Name           | I/O                   | Description                                                                                                                                                                                                     |  |

|----------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AX0 -<br>AX14  | Input-<br>Synchronous | Synchronous Address Inputs of Port X: Do not allow address pins to float.                                                                                                                                       |  |

| AY0 - AY14     | Input-<br>Synchronous | Synchronous Address Inputs of Port Y: Do not allow address pins to float.                                                                                                                                       |  |

| WEX#           | Input-<br>Synchronous | Read Write of Port X: WEX# signal is a synchronous input that identifies whether the current loaded cycle is a Read or Write operation.                                                                         |  |

| WEY#           | Input-<br>Synchronous | Read Write of Port Y: WEY# signal is a synchronous input that identifies whether the current loaded cycle is a Read or Write operation.                                                                         |  |

| PTX#           | Input-<br>Synchronous | Pass-Through of Port X: PTX# signal is a synchronous input that enables passing Port X input to Port Y output.                                                                                                  |  |

| PTY#           | Input-<br>Synchronous | Pass-Through of Port Y: PTY# signal is a synchronous input that enables passing Port Y input to Port X output.                                                                                                  |  |

| OEX#           | Input                 | Asynchronous Output Enable of Port X: OEX# must be LOW to read data. When OEX# is HIGH, the DQXx pins are in high impedance state.                                                                              |  |

| OEY#           | Input                 | Asynchronous Output Enable of Port Y: OEY# must be LOW to read data. When OEY# is HIGH, the DQYx pins are in high impedance state.                                                                              |  |

| DQX0-<br>DQX35 | Input/<br>Output      | Data Inputs/Outputs of Port X: Both the data input path and data output path are registered and triggered by the rising edge of CLK.                                                                            |  |

| DQY0-<br>DQY35 | Input/<br>Output      | Data Inputs/Outputs of Port Y: Both the data input path and data output path are regis and triggered by the rising edge of CLK.                                                                                 |  |

| CLK            | Input-<br>Synchronous | Clock: This is the clock input to this device. Except for OEX# and OEY#, all timing references of the address, data in, and all control signals for the device are made with respect to the rising edge of CLK. |  |

| CE1#           | Input-<br>Synchronous | Synchronous Active Low Chip Enable: CE1# is used with CE2 to enable this device. CE1# sampled HIGH at the rising edge of clock initiates a deselect cycle.                                                      |  |

| CE2            | Input-<br>Synchronous | Synchronous Active High Chip Enable: CE2 is used with CE1# to enable this device. CE2 sampled LOW at the rising edge of clock initiates a deselect cycle.                                                       |  |

| VCC            | Supply                | Power Supply: +3.3V –5% and +5%.                                                                                                                                                                                |  |

| VSS            | Ground                | Ground: GND.                                                                                                                                                                                                    |  |

| VSS            | Ground                | Ground: GND. No chip current flows through these pins. However, user needs to connect GND to these pins.                                                                                                        |  |

| VCCQ           | I/O Supply            | Output Buffer Supply: +3.3V –5% and +5%.                                                                                                                                                                        |  |

| NC             | -                     | No Connect: These signals are not internally connected. User can connect them to $V_{CC}$ , $V_{SS}$ , or any signal lines or simply leave them floating.                                                       |  |

### **Cycle Description Truth Table**<sup>[2, 3, 4, 5, 6, 7, 8, 9]</sup>

| Operation                | CE1# | CE2 | WEX# | WEY# | PTX# | PTY# |

|--------------------------|------|-----|------|------|------|------|

| Deselect Cycle           | Н    | Х   | Х    | X    | Х    | Х    |

| Deselect Cycle           | Х    | L   | Х    | X    | Х    | Х    |

| Write PORT X             | L    | Н   | 0    | Х    | Х    | Х    |

| Write PORT Y             | Х    | Х   | Х    | 0    | Х    | Х    |

| Pass-Through from X to Y | L    | Н   | Х    | X    | 0    | Х    |

| Pass-Through from Y to X | L    | Н   | Х    | X    | Х    | 0    |

| read PORT X              | L    | Н   | 1    | Х    | 1    | 1    |

| read PORT Y              | Х    | Χ   | Χ    | 1    | 1    | 1    |

### **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.) Storage Temperature ......-55°C to +125°C Ambient Temperature with Power Applied.....-10°C to +85°C Supply Voltage on V<sub>DD</sub> Relative to GND......-0.5V to +4.6V

| DC Input Voltage <sup>[10]</sup> 0.                    | 5V to V <sub>CCQ</sub> + 0.5V |

|--------------------------------------------------------|-------------------------------|

| Current into Outputs (LOW)                             | 20 mA                         |

| Static Discharge Voltage(per MIL-STD-883, Method 3015) | >1601V                        |

| Latch-Up Current                                       | >200 mA.                      |

### **Operating Range**

| Range | Ambient<br>Temperature <sup>[11]</sup> | V <sub>DD</sub> /V <sub>DDQ</sub> |

|-------|----------------------------------------|-----------------------------------|

| Com'l | 0°C to +70°C                           | 3.3V ± 5%                         |

- X means "don't care." H means logic HIGH. L means logic LOW.

All inputs except OEX# and OEY# must meet set-up and hold times around the rising edge (LOW to HIGH) of CLK.

OEX# and OEY# must be asserted to avoid bus contention during Write and Pass-Through cycles. For a Write and Pass-Through operation following a Read operation, OEX#/OEY# must be HIGH before the input data required set-up time plus High-Z time for OEX#/OEY# and staying HIGH throughout the input data hold time.

- hold time.

Operation number 3–6 can be used in any combination.

Operation number 4 and 7, 3 and 8, 7 and 8 can be combined.

Operation number 5 can not be combined with operation number 7 or 8 because Pass-Through operation has higher priority over a Read operation.

Operation number 6 can not be combined with operation number 7 or 8 because Pass-Through operation has higher priority over a Read operation.

This device contains circuitry that will ensure the outputs will be in High-Z during power-up

Minimum voltage equals –2.0V for pulse duration less than 20 ns.

T<sub>A</sub> is the case temperature.

# **Electrical Characteristics** Over the Operating Range

| Parameter       | Description                             | Test Conditions                                            |                       |       | Max.                   | Unit |

|-----------------|-----------------------------------------|------------------------------------------------------------|-----------------------|-------|------------------------|------|

| V <sub>DD</sub> | Power Supply Voltage                    |                                                            |                       | 3.135 | 3.465                  | V    |

| $V_{DDQ}$       | I/O Supply Voltage                      |                                                            |                       | 3.135 | 3.465                  | V    |

| V <sub>OH</sub> | Output HIGH Voltage                     | $V_{DD} = Min., I_{OH} = -4.0 \text{ mA}$                  |                       | 2.4   |                        | V    |

| V <sub>OL</sub> | Output LOW Voltage                      | $V_{DD} = Min., I_{OL} = 8.0 \text{ mA}$                   |                       |       | 0.4                    | V    |

| V <sub>IH</sub> | Input HIGH Volt-<br>age <sup>[12]</sup> |                                                            |                       |       | V <sub>CC</sub> + 0.5V | V    |

| V <sub>IL</sub> | Input LOW Voltage <sup>[13]</sup>       |                                                            |                       |       | 0.8                    | V    |

| I <sub>X</sub>  | Input Load Current                      | $GND \leq V_{IN} \leq V_{DDQ}$                             |                       |       | 5                      | μΑ   |

| I <sub>OZ</sub> | Output Leakage<br>Current               | $GND \le V_{IN} \le V_{DDQ}$ , Output Disabled             |                       |       | 5                      | μΑ   |

| I <sub>CC</sub> | V <sub>DD</sub> Operating               | $V_{DD} = Max., I_{OUT} = 0 mA,$                           | 7.5-ns cycle, 100 MHz |       | 500                    | mA   |

|                 | Supply                                  | $f = f_{MAX} = 1/t_{CYC}$                                  | 10.0-ns cycle, 83MHz  |       | 430                    | mA   |

| I <sub>SB</sub> | Automatic CE                            | Max. V <sub>DD</sub> , Device Deselected <sup>[14]</sup> , | 7.5-ns cycle, 100 MHz |       | 140                    | mA   |

|                 | Power-Down<br>Current—CMOS<br>Inputs    | $V_{IN} \le 0.3V$ or $V_{IN} \ge V_{DDQ} - 0.3V$ , $f = 0$ | 10.0-ns cycle, 83MHz  |       | 120                    | mA   |

<sup>12.</sup> Overshoot: V<sub>IH</sub> ≤ +6.0V for t ≤ t<sub>KC</sub>/2

13. Undershoot: V<sub>IL</sub> ≤ -2.0V for t ≤ t<sub>KC</sub>/2.

14. "Device Deselected" means the device is in POWER -DOWN mode as defined in the truth table.

## Capacitance<sup>[15]</sup>

| Parameter        | Description              | Test Conditions                         | Max. | Unit |

|------------------|--------------------------|-----------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance        | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 8    | pF   |

| C <sub>CLK</sub> | Clock Input Capacitance  | $V_{CC} = 3.3V,$ $V_{CCQ} = 3.3V$       | 9    | pF   |

| C <sub>I/O</sub> | Input/Output Capacitance |                                         | 8    | pF   |

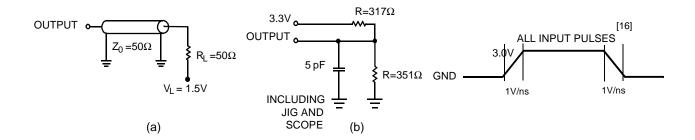

### **AC Test Loads and Waveforms**<sup>[16]</sup>

### Thermal Resistance<sup>[15]</sup>

| Description                              | Test Conditions                              | Symbol          | TQFP Typ. | Units |

|------------------------------------------|----------------------------------------------|-----------------|-----------|-------|

| Thermal Resistance (Junction to Ambient) | (@200lfm) Single-layer printed circuit board | $\Theta_{JA}$   | 40        | °C/W  |

| Thermal Resistance (Junction to Ambient) | (@200lfm) Four-layer printed circuit board   | Θ <sub>JC</sub> | 35        | °C/W  |

| Thermal Resistance (Junction to Board)   | Bottom                                       | $\Theta_{JA}$   | 23        | °C/W  |

| Thermal Resistance (Junction to Case)    | Тор                                          | Θ <sub>JC</sub> | 9         | °C/W  |

<sup>15.</sup> Tested initially and after any design or process change that may affect these parameters.16. AC test conditions assume signal transition time of 1 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading shown in part (a) of AC Test Loads.

# Switching Characteristics Over the Operating Range [ $^{16,\ 17,\ 18}$ ]

|                   |                                               | -1       | 00        |     | 83        |    |

|-------------------|-----------------------------------------------|----------|-----------|-----|-----------|----|

| Parameter         | Description                                   | Min.     | Min. Max. |     | Min. Max. |    |

| Clock             | •                                             | •        | •         | •   |           |    |

| t <sub>KC</sub>   | Clock cycle time                              | 10       |           | 12  |           | ns |

| t <sub>KH</sub>   | Clock HIGH time                               | 3.5      |           | 4.0 |           | ns |

| t <sub>KL</sub>   | Clock LOW time                                | 3.5      |           | 4.0 |           | ns |

| Output times      |                                               | <u>.</u> | •         | •   | •         |    |

| t <sub>KQ</sub>   | Clock to output valid                         |          | 5.0       |     | 6.0       | ns |

| t <sub>KQX</sub>  | Clock to output invalid                       | 1.5      |           | 1.5 |           | ns |

| t <sub>KQLZ</sub> | Clock to output in Low-Z <sup>[19]</sup>      | 0        |           | 0   |           | ns |

| t <sub>KQHZ</sub> | Clock to output in High-Z <sup>[19]</sup>     |          | 3.0       |     | 3.0       | ns |

| t <sub>OEQ</sub>  | OEX#/OEY# to output valid                     |          | 5.0       |     | 6.0       | ns |

| t <sub>OELZ</sub> | OEX#/OEY# to output in Low-Z <sup>[19]</sup>  | 0        |           | 0   |           | ns |

| t <sub>OEHZ</sub> | OEX#/OEY# to output in High-Z <sup>[19]</sup> |          | 3.0       |     | 3.0       | ns |

| Set-up times      |                                               | <u>.</u> | •         | •   | •         |    |

| tS                | Addresses, Controls and Data In               | 1.8      |           | 2.0 |           | ns |

| Hold times        |                                               | •        |           | •   |           | •  |

| tH                | Addresses, Controls and Data In               | 0.5      |           | 0.5 |           | ns |

t<sub>CHZ</sub>, t<sub>CLZ</sub>, t<sub>OEV</sub>, t<sub>EOLZ</sub>, and t<sub>EOHZ</sub> are specified with AC test conditions shown in part (a) of AC Test Loads. Transition is measured ± 200 mV from steady-state voltage.

At any given voltage and temperature, t<sub>EOHZ</sub> is less than t<sub>EOLZ</sub> and t<sub>CHZ</sub> is less than t<sub>CLZ</sub> to eliminate bus contention between SRAMs when sharing the same data bus. These specifications do not imply a bus contention condition, but reflect parameters guaranteed over worst case user conditions. Device is designed to achieve High-Z prior to Low-Z under the same system conditions.

This parameter is sampled and not 100% tested.

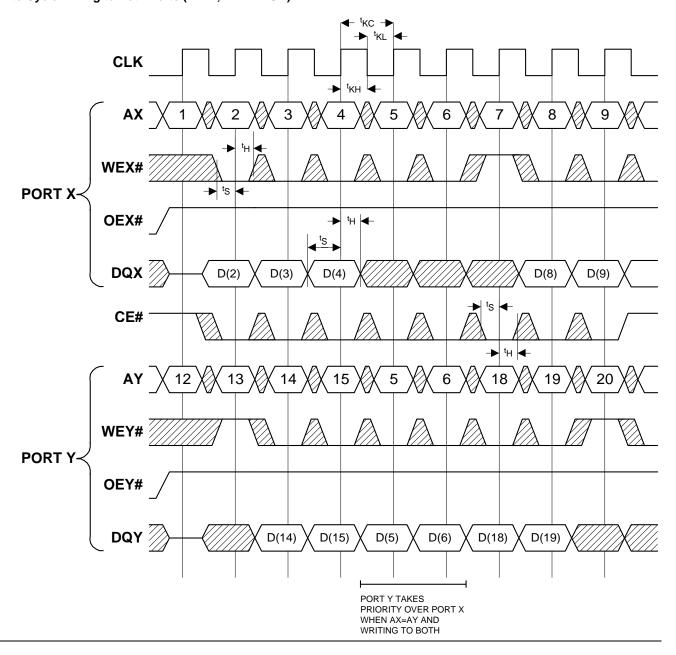

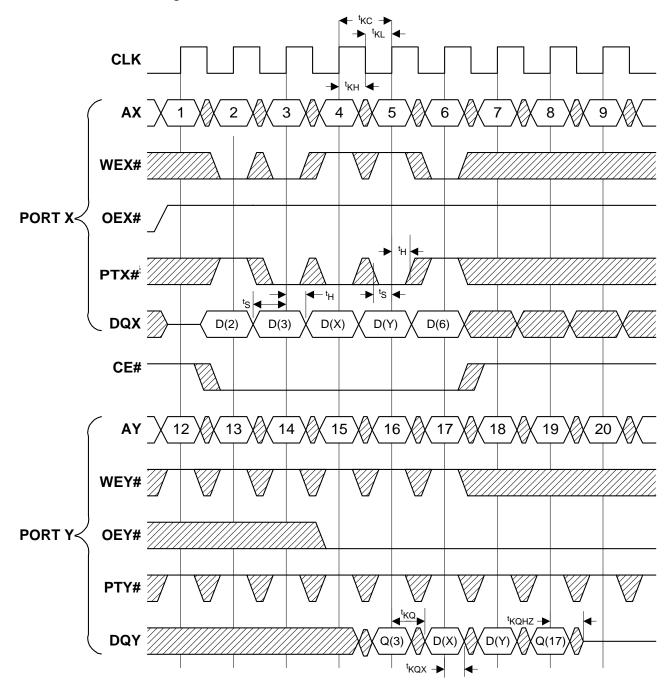

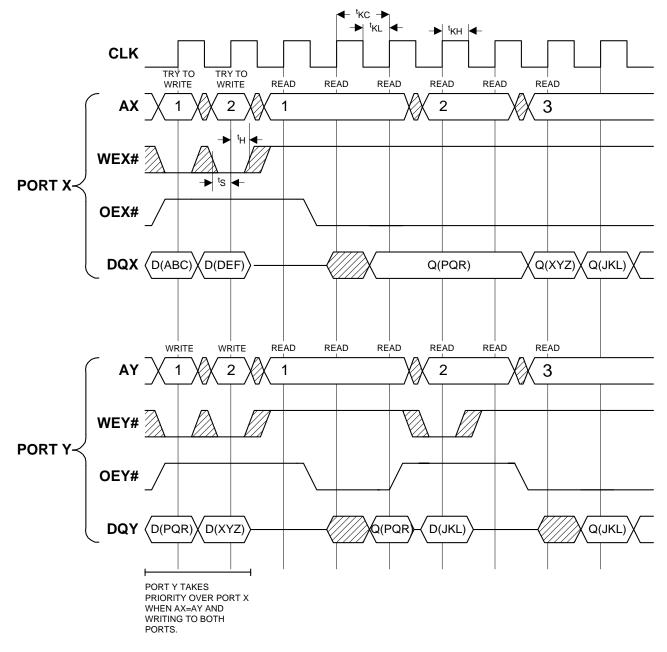

# Switching Waveforms [20]

### Read Cycle Timing from Both Ports (WEX#, WEY#, PTX#, PTY# HIGH)

#### Note:

20. CE# LOW means CE1# equals LOW and CE2 equals HIGH. CE# HIGH means CE1# equals HIGH or CE2 equals LOW.

# Switching Waveforms (continued)<sup>[20]</sup>

### Write Cycle Timing to Both Ports (PTX#, PTY# HIGH)

# Switching Waveforms (continued)<sup>[20]</sup>

### Write to Port X and Pass-Through to Port Y

## Switching Waveforms (continued)<sup>[20]</sup>

### Combination Read/Write with Same Address on Each Port

PTX# = PTY# = HIGH

D(Value) = Value is the input of the data port. Q(Value) = Value is the output of the data port.

### **Ordering Information**

| Speed<br>(MHz) | Ordering Code   | Package<br>Name | Package Type | Operating<br>Range |

|----------------|-----------------|-----------------|--------------|--------------------|

| 100            | CY7C1299A-100AC | A176            | 176-Pin TQFP | Commercial         |

| 83             | CY7C1299A-83AC  |                 |              |                    |

### **Package Diagram**

### 176-Lead Thin Quad Flat Pack (24x24x1.4 mm) A176

| Document Title: CY7C1299A - 32K x 36 Dual I/O Dual Address Synchronous SRAM Document Number: 38-05138 |         |               |                    |                       |  |  |

|-------------------------------------------------------------------------------------------------------|---------|---------------|--------------------|-----------------------|--|--|

| REV.                                                                                                  | ECN NO. | Issue<br>Date | Orig. of<br>Change | Description of Change |  |  |

| **                                                                                                    | 109817  | 10/16/01      | NSL                | New Data Sheet        |  |  |