# 7532 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### **DESCRIPTION**

The 7532 Group is the 8-bit microcomputer based on the 740 family core technology.

The 7532 Group has a USB, 8-bit timers, and an A-D converter, and is useful for an input device for personal computer peripherals.

# **FEATURES**

| reature3                                                      |

|---------------------------------------------------------------|

| • Basic machine-language instructions                         |

| $\bullet$ The minimum instruction execution time 0.34 $\mu s$ |

| (at 6 MHz oscillation frequency for the shortest instruction) |

| Memory size                                                   |

| ROM 8K to 16K bytes                                           |

| RAM256 to 384 bytes                                           |

| • Programmable I/O ports                                      |

|                                                               |

| • Interrupts                                                  |

| • Timers                                                      |

| • Serial I/O1                            | used only for Low Speed in USB     |

|------------------------------------------|------------------------------------|

|                                          | (USB/UART)                         |

| Serial I/O2                              | 8-bit × 1                          |

|                                          | (Clock-synchronized)               |

| A-D converter                            | 10-bit X 8 channels                |

| Clock generating circuit                 | Built-in type                      |

| (connect to external ceramic resonate    | ator or quartz-crystal oscillator) |

| Watchdog timer                           | 16-bit X 1                         |

| <ul> <li>Power source voltage</li> </ul> |                                    |

| At 6 MHz XIN oscillation freque          | ncy at ceramic resonator           |

|                                          | 4.1 to 5.5 V                       |

| Power dissipation                        | 30 mW (standard)                   |

| Operating temperature range              | –20 to 85 °C                       |

|                                          |                                    |

# **APPLICATION**

Input device for personal computer peripherals

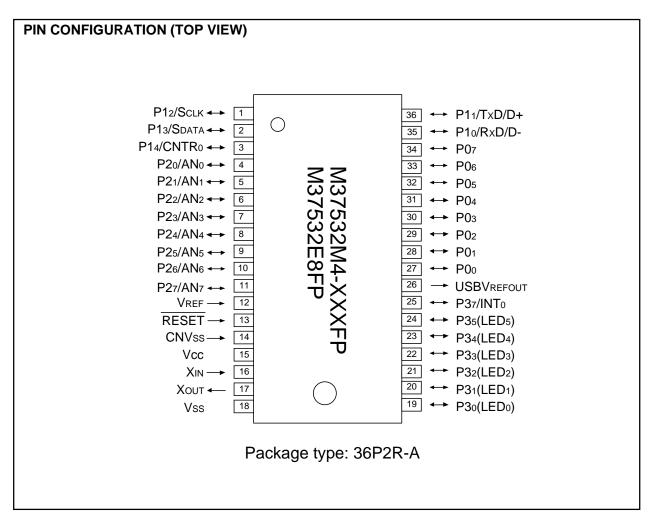

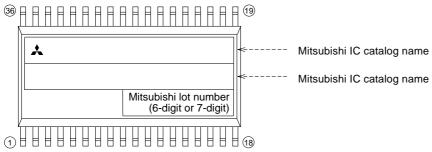

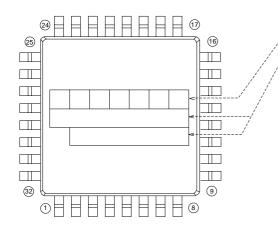

Fig. 1 Pin configuration of M37532M4-XXXFP,M37532E8FP

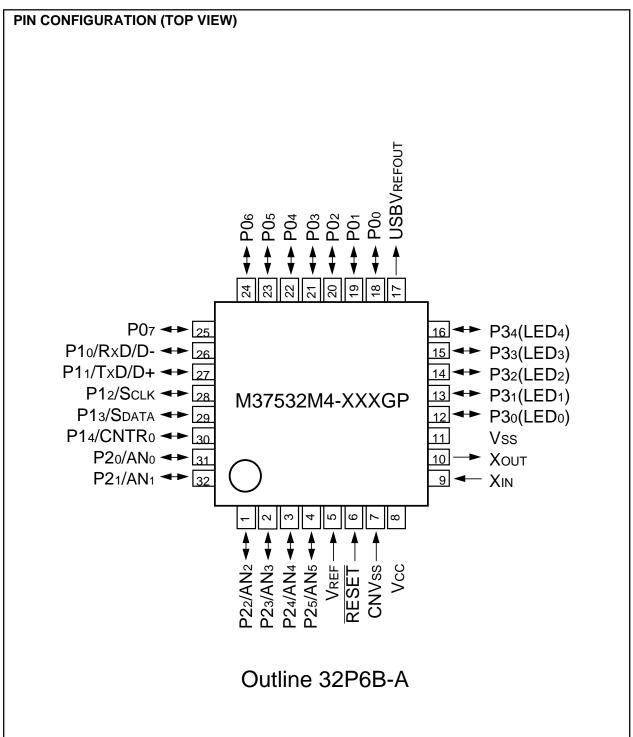

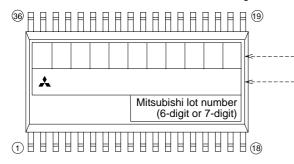

Fig. 2 Pin configuration of M37532M4-XXXGP

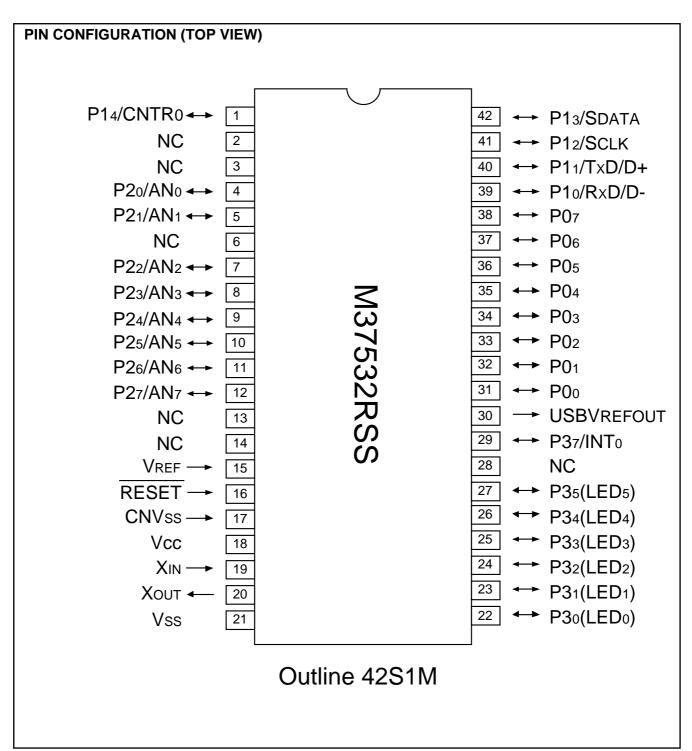

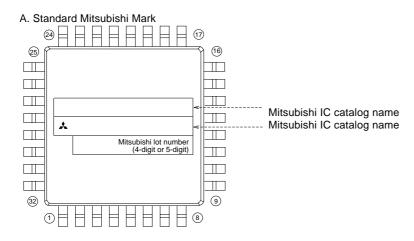

Fig. 3 Pin configuration of M37532RSS

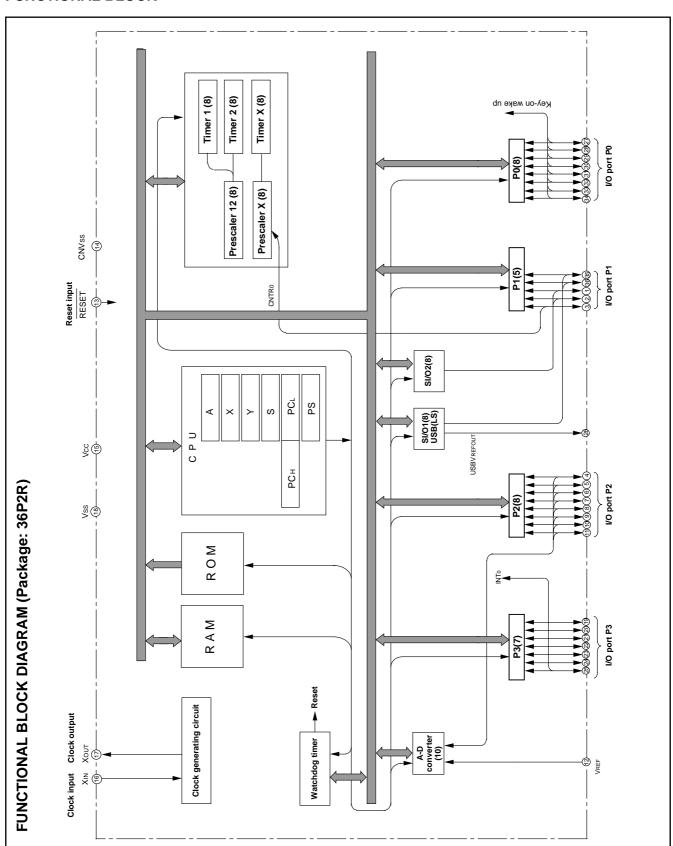

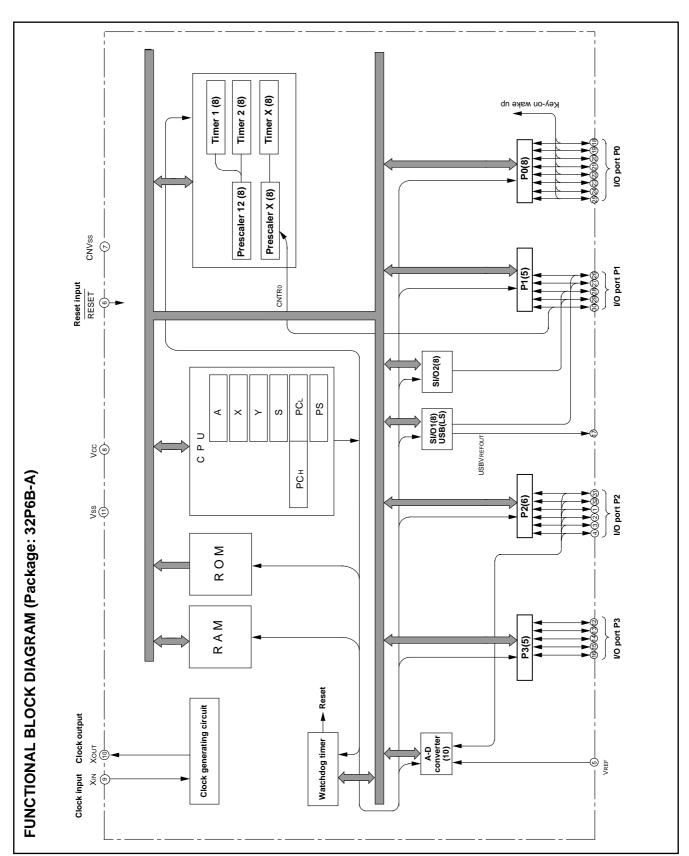

# **FUNCTIONAL BLOCK**

Fig. 4 Functional block diagram

Fig. 5 Functional block diagram

# **PIN DESCRIPTION**

Table 1 Pin description

| Pin                   | Name                         | Function                                                                                                                                   | Function expect a port function  |  |  |  |  |

|-----------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|--|--|

| Vcc, Vss              | Power source                 | •Apply voltage of 4.1 to 5.5 V to Vcc, and 0 V to Vss.                                                                                     |                                  |  |  |  |  |

| VREF                  | Analog reference voltage     | •Reference voltage input pin for A-D converter                                                                                             |                                  |  |  |  |  |

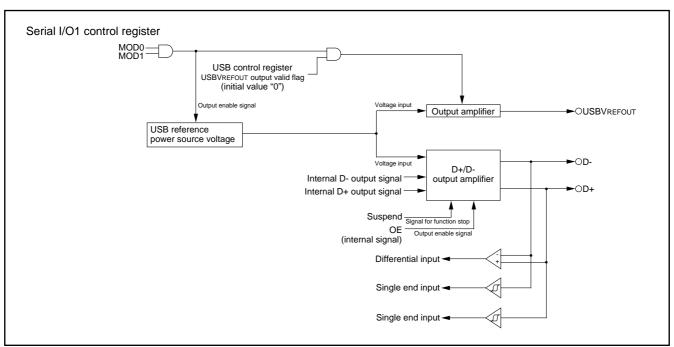

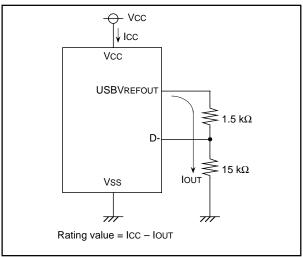

| USBVREFOUT            | USB reference voltage output | •Output pin for pulling up a D- line with 1.5 kΩ external resistor                                                                         |                                  |  |  |  |  |

| CNVss                 | CNVss                        | •Chip operating mode control pin, which is always connected to V                                                                           | /ss.                             |  |  |  |  |

| RESET                 | Reset input                  | •Reset input pin for active "L"                                                                                                            |                                  |  |  |  |  |

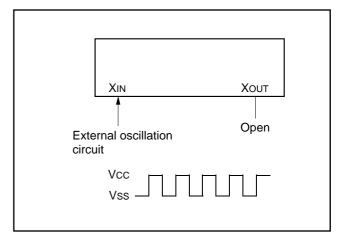

| XIN                   | Clock input                  | •Input and output pins for main clock generating circuit                                                                                   |                                  |  |  |  |  |

|                       | 01 1 1                       | Connect a ceramic resonator or quartz crystal oscillator between                                                                           | the Xin and Xouт pins.           |  |  |  |  |

| Xout                  | Clock output                 | •If an external clock is used, connect the clock source to the Xin բ                                                                       | oin and leave the Χουτ pin open. |  |  |  |  |

| P00-P07               | I/O port P0                  | •8-bit I/O port.                                                                                                                           | •Key-input (key-on wake up       |  |  |  |  |

|                       |                              | •I/O direction register allows each pin to be individually programmed as either input or output.                                           | interrupt input) pins            |  |  |  |  |

|                       |                              | •CMOS compatible input level                                                                                                               |                                  |  |  |  |  |

|                       |                              | •CMOS 3-state output structure                                                                                                             |                                  |  |  |  |  |

|                       |                              | •Whether a built-in pull-up resistor is to be used or not can be determined by program.                                                    |                                  |  |  |  |  |

| P10/RxD/D-            | I/O port P1                  | •5-bit I/O port                                                                                                                            | Serial I/O1 function pin         |  |  |  |  |

| P11/TxD/D+            |                              | •I/O direction register allows each pin to be individually programmed as either input or output.                                           | 0 : 11/00 (                      |  |  |  |  |

| P12/SCLK              |                              | CMOS compatible input level                                                                                                                | •Serial I/O2 function pin        |  |  |  |  |

| P13/SDATA             | _                            | CMOS 3-state output structure                                                                                                              | Time on V from ations in in      |  |  |  |  |

| P14/CNTR <sub>0</sub> |                              | •CMOS/TTL level can be switched for P10, P12, P13.                                                                                         | •Timer X function pin            |  |  |  |  |

|                       |                              | •When using the USB function, input level of ports P1o and P1o becomes USB input level, and output level of them becomes USB output level. |                                  |  |  |  |  |

| P20/AN0-              | I/O port P2                  | •8-bit I/O port having almost the same function as P0                                                                                      | •Input pins for A-D converter    |  |  |  |  |

| P27/AN7               |                              | •CMOS compatible input level                                                                                                               |                                  |  |  |  |  |

|                       |                              | CMOS 3-state output structure                                                                                                              |                                  |  |  |  |  |

| P30-P35               | I/O port P3                  | •7-bit I/O port                                                                                                                            | ·                                |  |  |  |  |

|                       |                              | •I/O direction register allows each pin to be individually programmed as either input or output.                                           |                                  |  |  |  |  |

|                       |                              | •CMOS compatible input level (CMOS/TTL level can be switched for P37).                                                                     |                                  |  |  |  |  |

|                       |                              | •CMOS 3-state output structure                                                                                                             |                                  |  |  |  |  |

|                       |                              | •P3o to P3s can output a large current for driving LED.                                                                                    |                                  |  |  |  |  |

| P37/INT <sub>0</sub>  |                              | •Whether a built-in pull-up resistor is to be used or not can be determined by program.                                                    | •Interrupt input pins            |  |  |  |  |

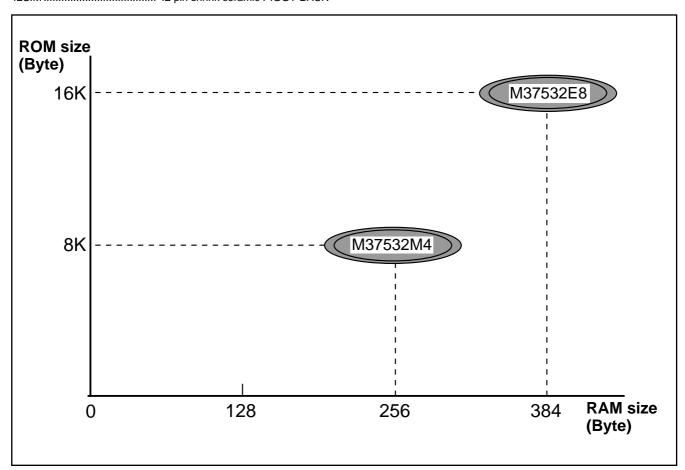

# **GROUP EXPANSION**

Mitsubishi plans to expand the 7532 group as follow:

#### Memory type

Support for Mask ROM version, One Time PROM version, and Emulator MCU .

# Memory size

#### **Package**

Fig. 6 Memory expansion plan

Currently supported products are listed below.

Table 2 List of supported products

| Product        | (P) ROM size (bytes)<br>ROM size for User () | RAM size<br>(bytes) | Package | Remarks                       |

|----------------|----------------------------------------------|---------------------|---------|-------------------------------|

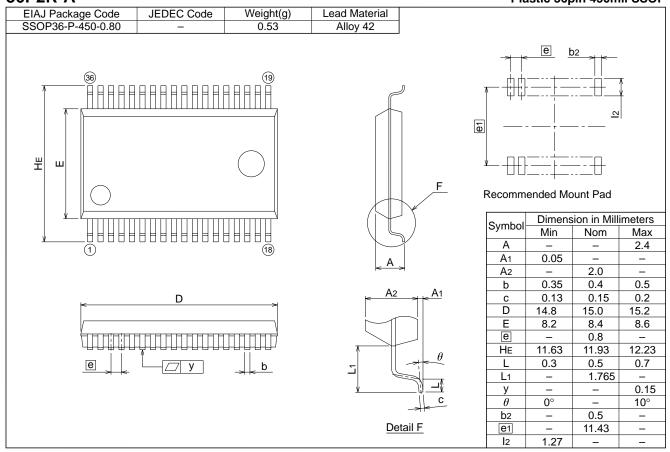

| M37532M4-XXXFP | 8192 (8062)                                  | 256                 | 36P2R-A | Mask ROM version              |

| M37532M4-XXXGP | 8192 (8062)                                  | 256                 | 32P6B-A | Mask ROM version              |

| M37532E8FP     | 16384 (16254)                                | 384                 | 36P2R-A | One Time PROM version (blank) |

| M37532RSS      |                                              | 384                 | 42S1M   | Emulator MCU                  |

7

# **FUNCTIONAL DESCRIPTION**

# **Central Processing Unit (CPU)**

The 7532 Group uses the standard 740 family instruction set. Refer to the table of 740 family addressing modes and machine-language instructions or the 740 Family Software Manual for details on each instruction set.

Machine-resident 740 family instructions are as follows:

- 1. The FST and SLW instructions cannot be used.

- 2. The MUL and DIV instructions cannot be used.

- 3. The WIT instruction can be used.

- 4. The STP instruction can be used.

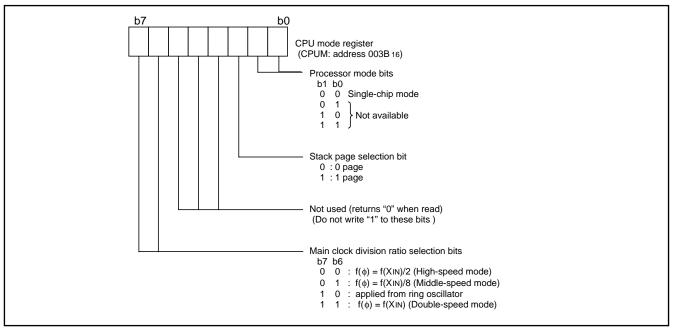

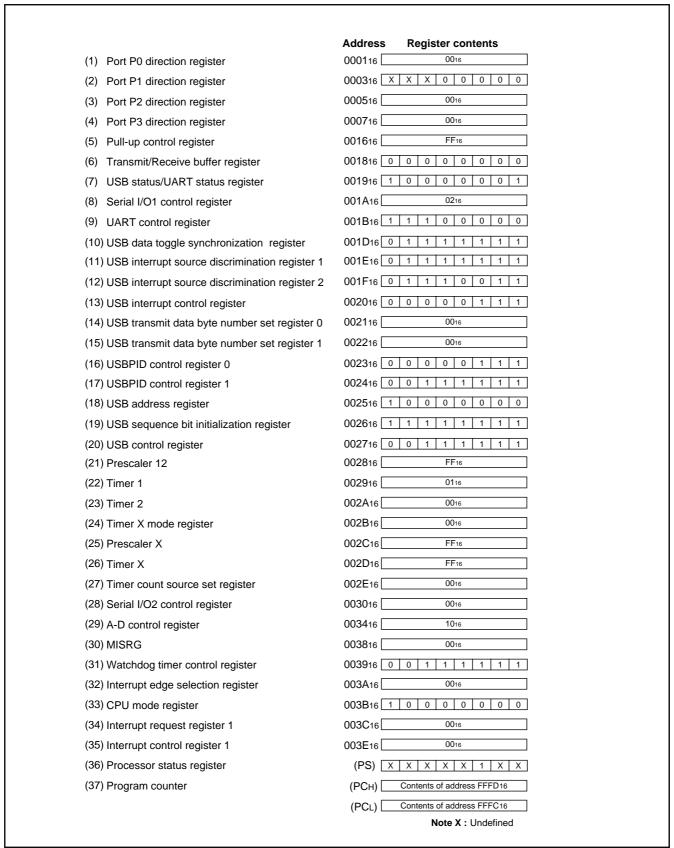

#### [CPU Mode Register] CPUM

The CPU mode register contains the stack page selection bit. This register is allocated at address 003B16.

Fig. 7 Structure of CPU mode register

# Switching method of CPU mode register

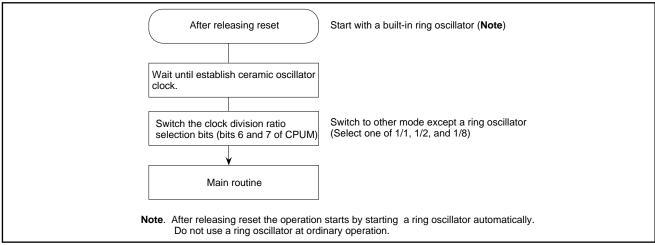

Switch the CPU mode register (CPUM) at the head of program after releasing Reset in the following method.

Fig. 8 Switching method of CPU mode register

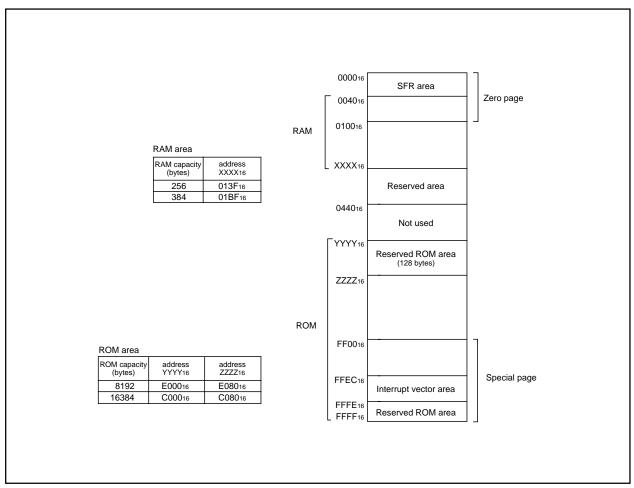

# **Memory**

#### Special function register (SFR) area

The SFR area in the zero page contains control registers such as I/O ports and timers.

#### RAM

RAM is used for data storage and for a stack area of subroutine calls and interrupts.

#### ROM

The first 128 bytes and the last 2 bytes of ROM are reserved for device testing and the rest is a user area for storing programs.

#### Interrupt vector area

The interrupt vector area contains reset and interrupt vectors.

#### Zero page

The 256 bytes from addresses 000016 to 00FF16 are called the zero page area. The internal RAM and the special function registers (SFR) are allocated to this area.

The zero page addressing mode can be used to specify memory and register addresses in the zero page area. Access to this area with only 2 bytes is possible in the zero page addressing mode.

#### Special page

The 256 bytes from addresses FF0016 to FFFF16 are called the special page area. The special page addressing mode can be used to specify memory addresses in the special page area. Access to this area with only 2 bytes is possible in the special page addressing mode.

Fig. 9 Memory map diagram

# **7532 Group**

| 000016             | Port P0 (P0)                                                | 002016             | USB interrupt control register (USBICON)               |

|--------------------|-------------------------------------------------------------|--------------------|--------------------------------------------------------|

| 000116             | Port P0 direction register (P0D)                            | 002116             | USB transmit data byte number set register 0 (EP0BYTE) |

| 000216             | Port P1 (P1)                                                | 002216             | USB transmit data byte number set register 1 (EP1BYTE) |

| 000316             | Port P1 direction register (P1D)                            | 002316             | USBPID control register 0 (EP0PID)                     |

| 000416             | Port P2 (P2)                                                | 002416             | USBPID control register 1 (EP1PID)                     |

| 000516             | Port P2 direction register (P2D)                            | 002516             | USB address register (USBA)                            |

| 000616             | Port P3 (P3)                                                | 002616             | USB sequence bit initialization register (INISQ1)      |

| 000716             | Port P3 direction register (P3D)                            | 002716             | USB control register (USBCON)                          |

| 000816             |                                                             | 002816             | Prescaler 12 (PRE12)                                   |

| 000916             |                                                             | 002916             | Timer 1 (T1)                                           |

| 000A16             |                                                             | 002A16             | Timer 2 (T2)                                           |

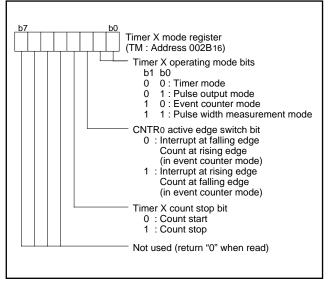

| 000B16             |                                                             | 002B <sub>16</sub> | Timer X mode register (TM)                             |

| 000C16             |                                                             | 002C <sub>16</sub> | Prescaler X (PREX)                                     |

| 000D16             |                                                             | 002D16             | Timer X (TX)                                           |

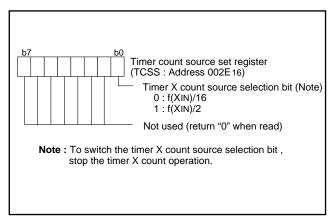

| 000E16             |                                                             | 002E <sub>16</sub> | Timer count source set register (TCSS)                 |

| 000F16             |                                                             | 002F <sub>16</sub> |                                                        |

| 001016             |                                                             | 003016             | Serial I/O2 control register (SIO2CON)                 |

| 001116             |                                                             | 003116             | Serial I/O2 register (SIO2)                            |

| 001216             |                                                             | 003216             |                                                        |

| 001316             |                                                             | 003316             |                                                        |

| 001416             |                                                             | 003416             | A-D control register (ADCON)                           |

| 001516             |                                                             | 003516             | A-D conversion register (low-order) (ADL)              |

| 001616             | Pull-up control register (PULL)                             | 003616             | A-D conversion register (high-order) (ADH)             |

| 001716             | Port P1P3 control register (P1P3C)                          | 003716             |                                                        |

| 001816             | Transmit/Receive buffer register (TB/RB)                    | 003816             | MISRG                                                  |

| 001916             | USB status register (USBSTS)/UART status register (UARTSTS) | 003916             | Watchdog timer control register (WDTCON)               |

| 001A <sub>16</sub> | Serial I/O1 control register (SIO1CON)                      | 003A16             | Interrupt edge selection register (INTEDGE)            |

| 001B <sub>16</sub> | UART control register (UARTCON)                             | 003B <sub>16</sub> | CPU mode register (CPUM)                               |

| 001C <sub>16</sub> | Baud rate generator (BRG)                                   | 003C <sub>16</sub> | Interrupt request register 1 (IREQ1)                   |

| 001D <sub>16</sub> | USB data toggle synchronization register ( TRSYNC)          | 003D16             |                                                        |

| 001E <sub>16</sub> | USB interrupt source discrimination register 1 (USBIR1)     | 003E16             | Interrupt control register 1 (ICON1)                   |

| 001F <sub>16</sub> | USB interrupt source discrimination register 2 (USBIR2)     | 003F16             |                                                        |

Fig. 10 Memory map of special function register (SFR)

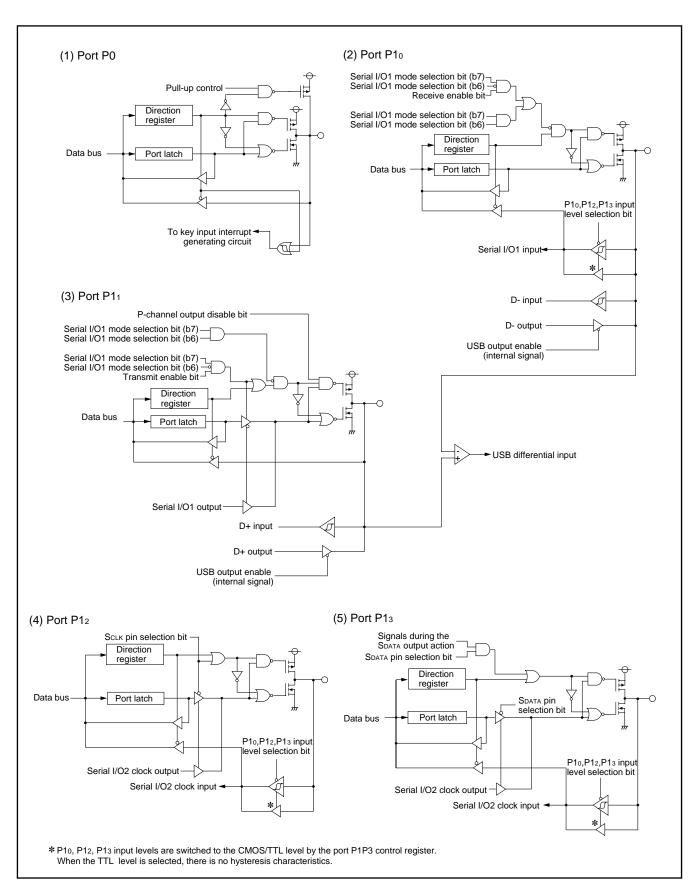

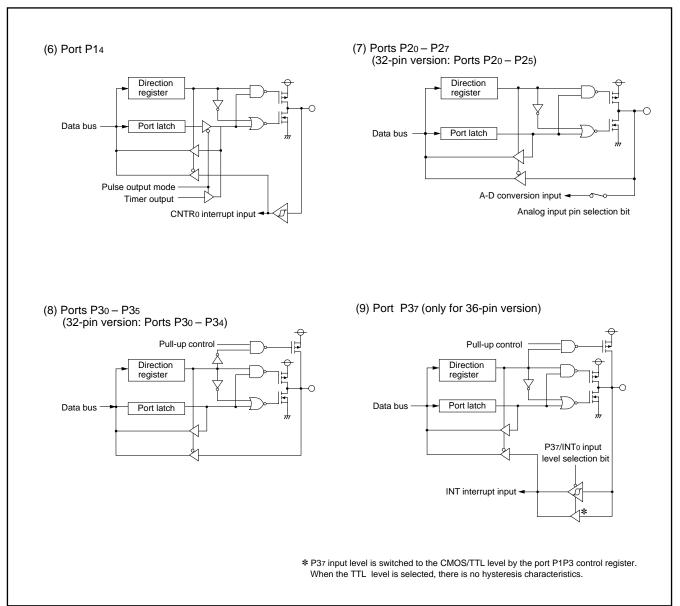

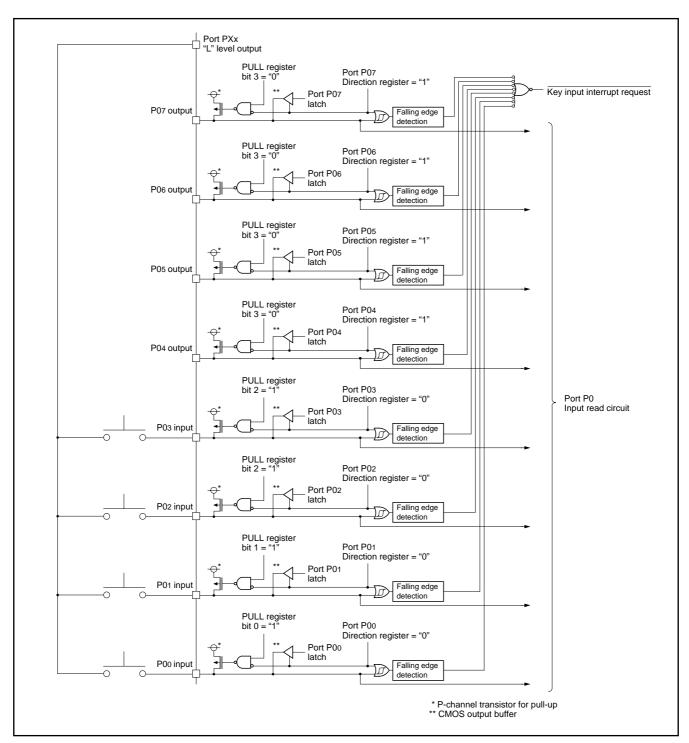

#### I/O Ports

#### [Direction registers] PiD

The I/O ports have direction registers which determine the input/output direction of each pin. Each bit in a direction register corresponds to one pin, and each pin can be set to be input or output.

When "1" is set to the bit corresponding to a pin, this pin becomes an output port. When "0" is set to the bit, the pin becomes an input port. When data is read from a pin set to output, not the value of the pin itself but the value of port latch is read. Pins set to input are floating, and permit reading pin values.

If a pin set to input is written to, only the port latch is written to and the pin remains floating.

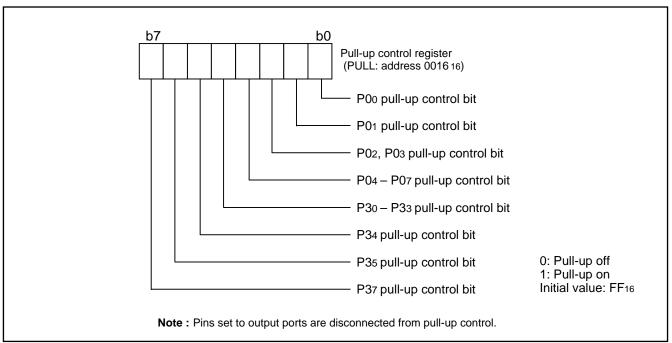

#### [Pull-up control] PULL

By setting the pull-up control register (address 001616), ports P0 and P3 can exert pull-up control by program. However, pins set to output are disconnected from this control and cannot exert pull-up control.

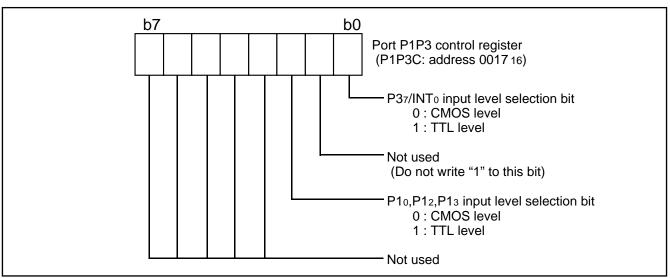

#### [Port P1P3 control] P1P3C

By setting the port P1P3 control register (address 0017<sub>16</sub>), a CMOS input level or a TTL input level can be selected for ports P1<sub>0</sub>, P1<sub>2</sub>, P1<sub>3</sub>, and P3<sub>7</sub> by program.

Then, set "1" to each bit 6 of the port P3 direction register and port P3 register.

Fig. 11 Structure of pull-up control register

Fig. 12 Structure of port P1P3 control register

# **7532 Group**

# SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Table 3 I/O port function table

| Pin                      | Name        | Input/output        | I/O format                                          | Non-port function                 | Related SFRs                      | Diagram No. |

|--------------------------|-------------|---------------------|-----------------------------------------------------|-----------------------------------|-----------------------------------|-------------|

| P00-P07                  | I/O port P0 | I/O individual bits | •CMOS compatible input level •CMOS 3-state output   | Key input interrupt               | Pull-up control register          | (1)         |

| P10/RxD/D-<br>P11/TxD/D+ | I/O port P1 |                     | •USB input/output level when selecting USB function | Serial I/O1 function input/output | Serial I/O1 control register      | (2)<br>(3)  |

| P12/SCLK<br>P13/SDATA    |             |                     | CMOS compatible input level     CMOS 3-state output | Serial I/O2 function input/output | Serial I/O2 control register      | (4)<br>(5)  |

| P14/CNTR0                |             |                     | (Note)                                              | Timer X function input/output     | Timer X mode register             | (6)         |

| P20/AN0-<br>P27/AN7      | I/O port P2 |                     |                                                     | A-D conversion input              | A-D control register              | (7)         |

| P30-P35                  | I/O port P3 |                     |                                                     |                                   |                                   | (8)         |

| P37/INTo                 |             |                     |                                                     | External interrupt input          | Interrupt edge selection register | (9)         |

Note: Port P37 is CMOS/TTL level.

Fig. 13 Block diagram of ports (1)

Fig. 14 Block diagram of ports (2)

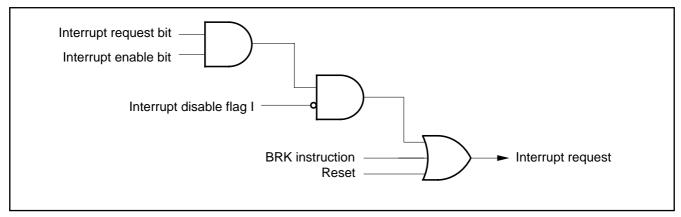

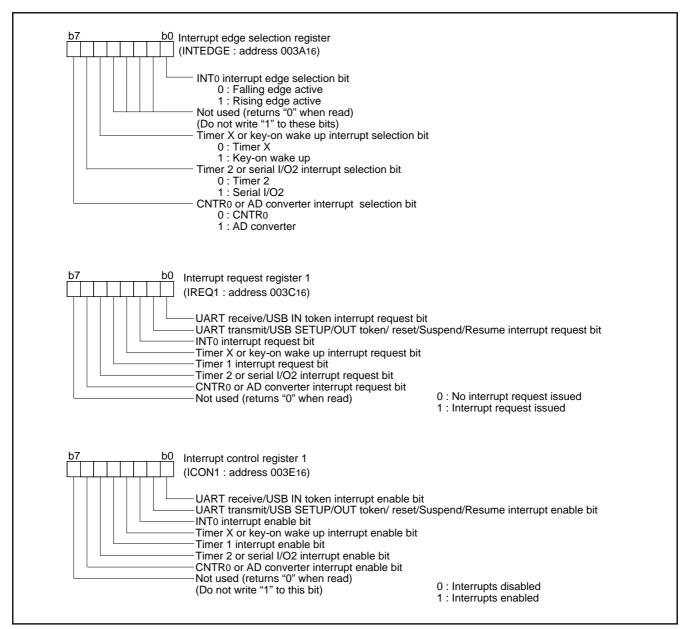

#### Interrupts

Interrupts occur by 13 different sources: 3 external sources, 9 internal sources and 1 software source.

# Interrupt control

All interrupts except the BRK instruction interrupt have an interrupt request bit and an interrupt enable bit, and they are controlled by the interrupt disable flag. When the interrupt enable bit and the interrupt request bit are set to "1" and the interrupt disable flag is set to "0", an interrupt is accepted.

The interrupt request bit can be cleared by program but not be set. The interrupt enable bit can be set and cleared by program.

It becomes usable by switching CNTRo and AD interrupt sources with bit 7 of the interrupt edge selection register, timer 2 and serial I/O2 interrupt sources with bit 6, and timer X and key-on wake-up interrupt sources with bit 5.

The reset and BRK instruction interrupt can never be disabled with any flag or bit. All interrupts except these are disabled when the interrupt disable flag is set.

When several interrupts occur at the same time, the interrupts are received according to priority.

#### Interrupt operation

Upon acceptance of an interrupt the following operations are automatically performed:

- 1. The processing being executed is stopped.

- 2. The contents of the program counter and processor status register are automatically pushed onto the stack.

- The interrupt disable flag is set and the corresponding interrupt request bit is cleared.

- 4. Concurrently with the push operation, the interrupt destination address is read from the vector table into the program counter.

#### Notes on use

When the active edge of an external interrupt (INTo, CNTRo) is set, the interrupt request bit may be set.

Therefore, please take following sequence:

- 1. Disable the external interrupt which is selected.

- Change the active edge in interrupt edge selection register. (in case of CNTRo: Timer X mode register)

- 3. Clear the set interrupt request bit to "0".

- 4. Enable the external interrupt which is selected.

Table 4 Interrupt vector address and priority

|                                             | <u></u>  | Vector addresses (Note 1) |                    |                                                                                                 |                                             |  |

|---------------------------------------------|----------|---------------------------|--------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------|--|

| Interrupt source                            | Priority | High-order                | Low-order          | Interrupt request generating conditions                                                         | Remarks                                     |  |

| Reset (Note 2)                              | 1        | FFFD16                    | FFFC16             | At reset input                                                                                  | Non-maskable                                |  |

| UART receive                                | 2        | FFFB16                    | FFFA <sub>16</sub> | At completion of UART data receive                                                              | Valid in UART mode                          |  |

| USB IN token                                |          |                           |                    | At detection of IN token                                                                        | Valid in USB mode                           |  |

| UART transmit                               | 3        | FFF916                    | FFF816             | At completion of UART transmit shift or when transmit buffer is empty                           | Valid in UART mode                          |  |

| USB SETUP/OUT token<br>Reset/Suspend/Resume |          |                           |                    | At detection of SETUP/OUT token or<br>At detection of Reset/ Suspend/ Resume                    | Valid in USB mode                           |  |

| INT <sub>0</sub>                            | 4        | FFF7 <sub>16</sub>        | FFF6 <sub>16</sub> | At detection of either rising or falling edge of INTo input                                     | External interrupt (active edge selectable) |  |

| Timer X                                     | 5        | FFF516                    | FFF4 <sub>16</sub> | At timer X underflow                                                                            |                                             |  |

| Key-on wake-up                              |          |                           |                    | At falling of conjunction of input logical level for port P0 (at input)                         | External interrupt (valid at falling)       |  |

| Timer 1                                     | 6        | FFF316                    | FFF216             | At timer 1 underflow                                                                            | STP release timer underflow                 |  |

| Timer 2                                     | 7        | FFF1 <sub>16</sub>        | FFF016             | At timer 2 underflow                                                                            |                                             |  |

| Serial I/O2                                 |          |                           |                    | At completion of transmit/receive shift                                                         | 1                                           |  |

| CNTR <sub>0</sub>                           | 8        | FFEF16                    | FFEE16             | At detection of either rising or falling edge of CNTRo input External interrupt (ac selectable) |                                             |  |

| A-D conversion                              |          |                           |                    | At completion of A-D conversion                                                                 | T                                           |  |

| BRK instruction                             | 9        | FFED16                    | FFEC <sub>16</sub> | At BRK instruction execution                                                                    | Non-maskable software interrupt             |  |

Note 1: Vector addressed contain internal jump destination addresses.

2: Reset function in the same way as an interrupt with the highest priority.

Fig. 15 Interrupt control

Fig. 16 Structure of Interrupt-related registers

# **Key Input Interrupt (Key-On Wake-Up)**

A key-on wake-up interrupt request is generated by applying "L" level to any pin of port P0 that has been set to input mode.

In other words, it is generated when the AND of input level goes from "1" to "0". An example of using a key input interrupt is shown in Figure 17, where an interrupt request is generated by pressing one of the keys provided as an active-low key matrix which uses ports P00 to P03 as input ports.

Fig. 17 Connection example when using key input interrupt and port P0 block diagram

#### **Timers**

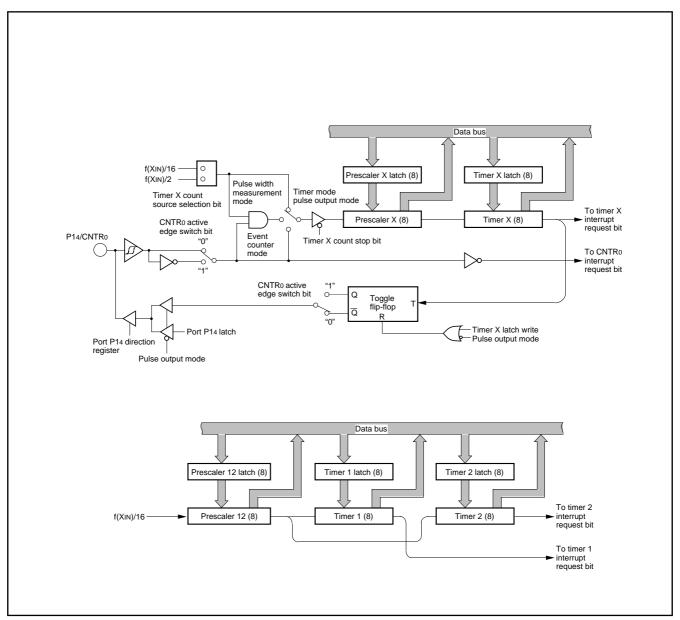

The 7532 Group has 3 timers: timer X, timer 1 and timer 2.

The division ratio of every timer and prescaler is 1/(n+1) provided that the value of the timer latch or prescaler is n.

All the timers are down count timers. When a timer reaches "0", an underflow occurs at the next count pulse, and the corresponding timer latch is reloaded into the timer. When a timer underflows, the interrupt request bit corresponding to each timer is set to "1".

# ●Timer 1, Timer 2

Prescaler 12 always counts f(XIN)/16. Timer 1 and timer 2 always count the prescaler output and periodically sets the interrupt request bit.

#### ●Timer X

Timer X can be selected in one of 4 operating modes by setting the timer X mode register.

#### • Timer Mode

The timer counts the signal selected by the timer X count source selection bit.

#### Pulse Output Mode

The timer counts the signal selected by the timer X count source selection bit, and outputs a signal whose polarity is inverted each time the timer value reaches "0", from the CNTRo pin.

When the CNTR<sub>0</sub> active edge switch bit is "0", the output of the CNTR<sub>0</sub> pin is started with an "H" output.

At "1", this output is started with an "L" output. When using a timer in this mode, set the port P14 direction register to output mode.

#### Event Counter Mode

The operation in the event counter mode is the same as that in the timer mode except that the timer counts the input signal from the CNTR<sub>0</sub> pin.

When the CNTR<sub>0</sub> active edge switch bit is "0", the timer counts the rising edge of the CNTR<sub>0</sub> pin. When this bit is "1", the timer counts the falling edge of the CNTR<sub>0</sub> pin.

#### • Pulse Width Measurement Mode

When the CNTRo active edge switch bit is "0", the timer counts the signal selected by the timer X count source selection bit while the CNTRo pin is "H". When this bit is "1", the timer counts the signal while the CNTRo pin is "L".

In any mode, the timer count can be stopped by setting the timer X count stop bit to "1". Each time the timer overflows, the interrupt request bit is set.

Fig. 18 Structure of timer X mode register

Fig. 19 Timer count source set register

Fig. 20 Block diagram of timer X, timer 1 and timer 2

#### Serial I/O

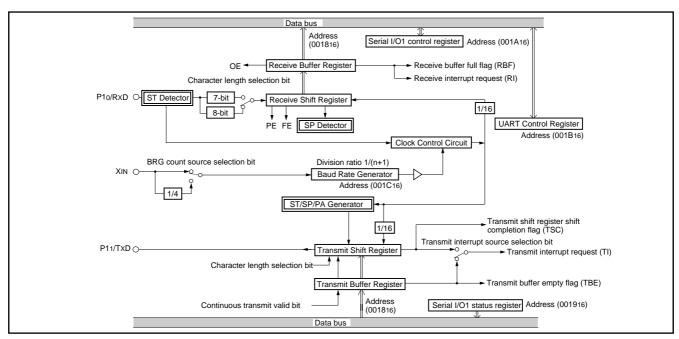

#### ●Serial I/O1

#### • Asynchronous serial I/O (UART) mode

Serial I/O1 can be used as an asynchronous (UART) serial I/O. A dedicated timer (baud rate generator) is also provided for baud rate generation when serial I/O1 is in operation.

Eight serial data transfer formats can be selected, and the transfer formats to be used by a transmitter and a receiver must be identical.

Each of the transmit and receive shift registers has a buffer register

(the same address on memory). Since the shift register cannot be written to or read from directly, transmit data is written to the transmit buffer, and receive data is read from the respective buffer registers. These buffer registers can also hold the next data to be transmitted and receive 2-byte receive data in succession.

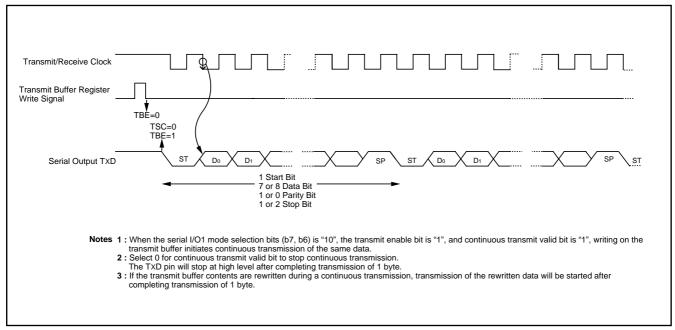

By selecting "1" for continuous transmit valid bit (bit 2 of SIO1CON), continuous transmission of the same data is made possible.

This can be used as a simplified PWM.

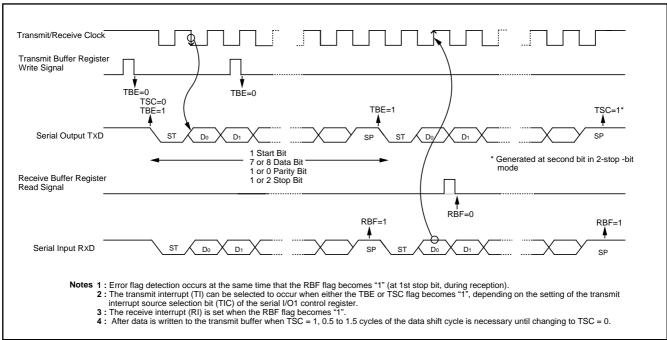

Fig. 21 Block diagram of UART serial I/O

Fig. 22 Operation of UART serial I/O function

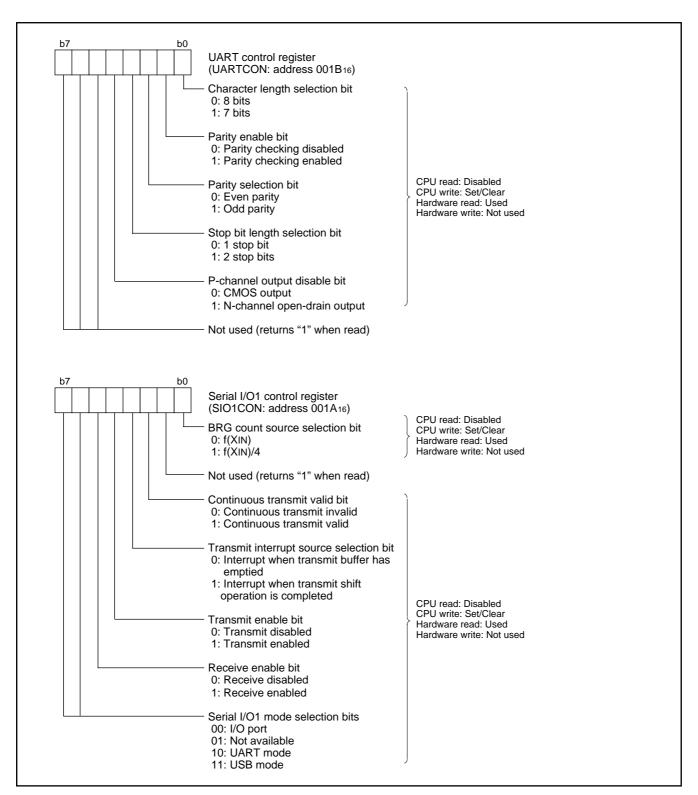

#### [Serial I/O1 control register] SIO1CON

The serial I/O1 control register consists of eight control bits for the serial I/O1 function.

#### [UART control register] UARTCON

The UART control register consists of four control bits (bits 0 to 3) which are valid when asynchronous serial I/O is selected and set the data format of an data transfer. One bit in this register (bit 4) is always valid and sets the output structure of the P1<sub>1</sub>/TxD pin.

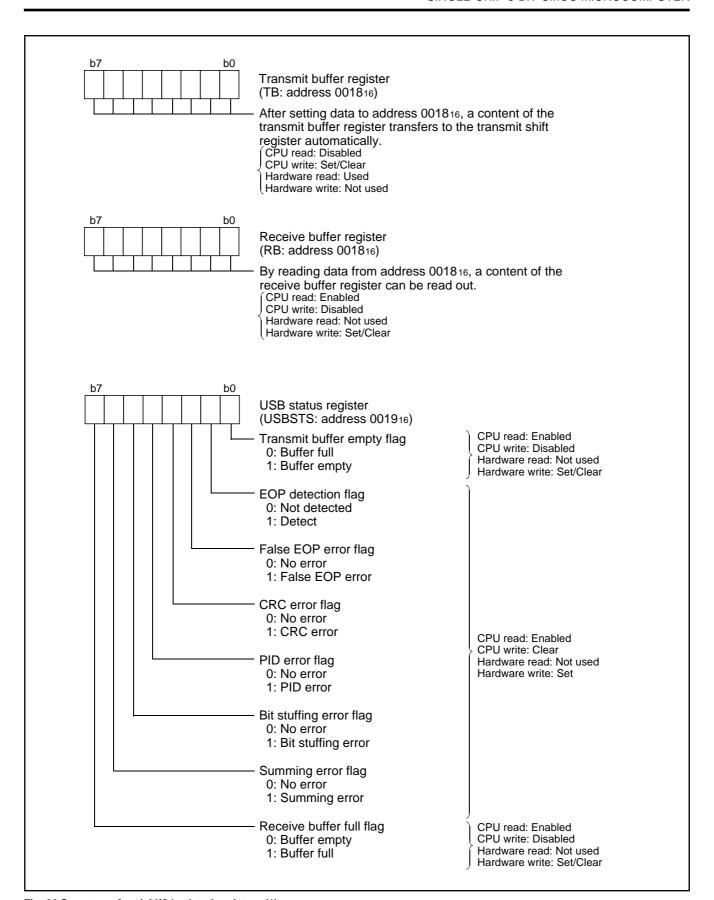

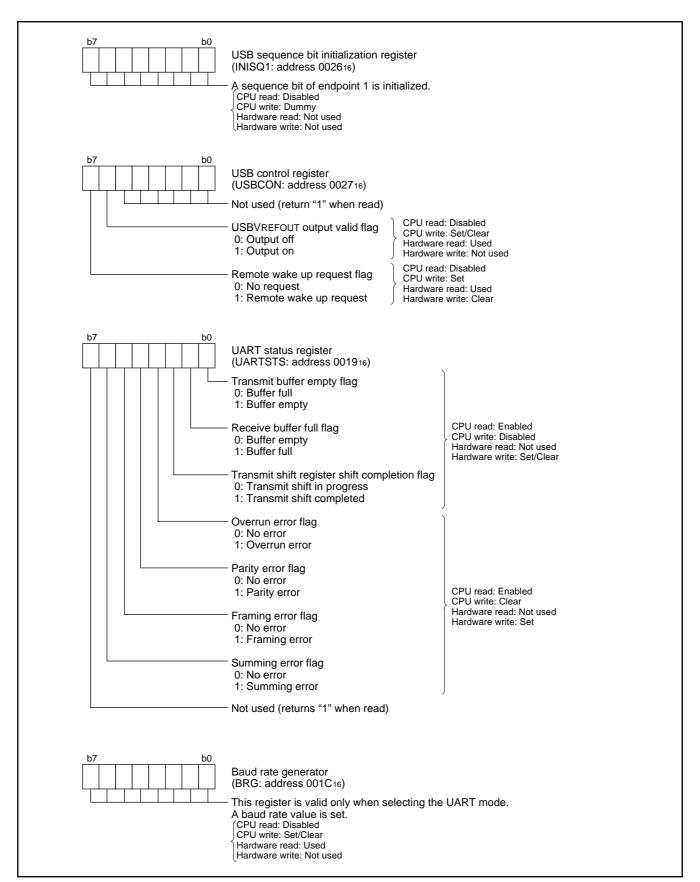

#### [UART status register] UARTSTS

The read-only UART status register consists of seven flags (bits 0 to 6) which indicate the operating status of the UART function and various errors. This register functions as the UART status register (UARTSTS) when selecting the UART.

The receive buffer full flag (bit 1) is cleared to "0" when the receive buffer is read.

If there is an error, it is detected at the same time that data is transferred from the receive shift register to the receive buffer, and the receive buffer full flag is set. A write to the UART status register clears all the error flags OE, PE, FE, and SE (bit 3 to bit 6, respectively). Writing "0" to the serial I/O1 mode selection bits MOD1 and MOD0 (bit 7 and 6 of the Serial I/O1 control register) also clears all the status flags, including the error flags.

All bits of the serial I/O1 status register are initialized to "8116" at reset, but if the transmit enable bit (bit 4) of the serial I/O1 control register has been set to "1", the continuous transmit valid bit (bit 2) becomes "1".

#### [Transmit/Receive buffer register] TB/RB

The transmit buffer and the receive buffer are located at the same address. The transmit buffer is write-only and the receive buffer is read-only. If a character bit length is 7-bit, the MSB of data stored in the receive buffer is "0".

#### [Baud Rate Generator] BRG

The baud rate generator determines the baud rate for serial transfer. The baud rate generator divides the frequency of the count source by 1/(n+1), where n is the value written to the baud rate generator.

Fig. 23 Continuous transmission operation of UART serial I/O

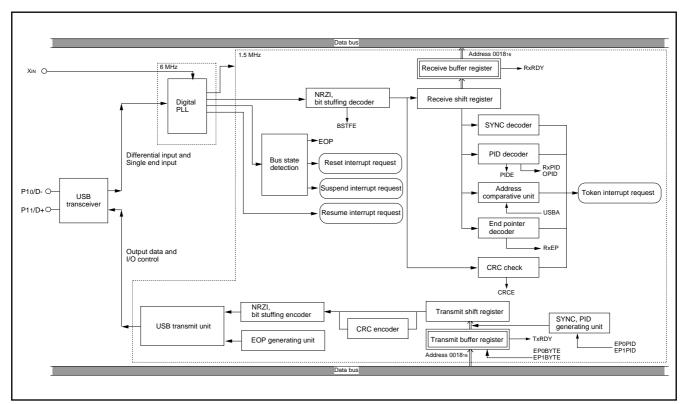

#### • Universal serial bus (USB) mode

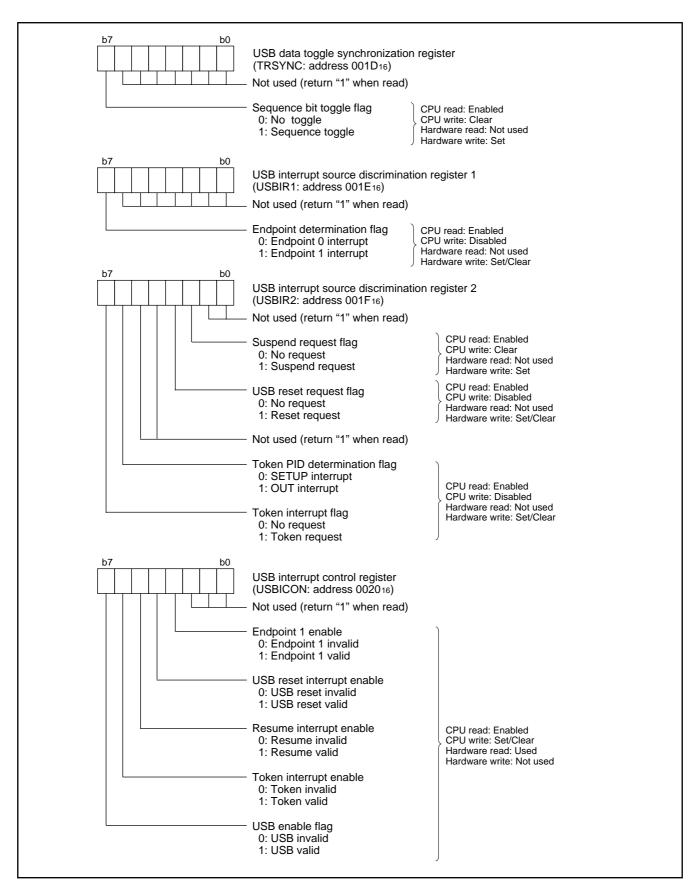

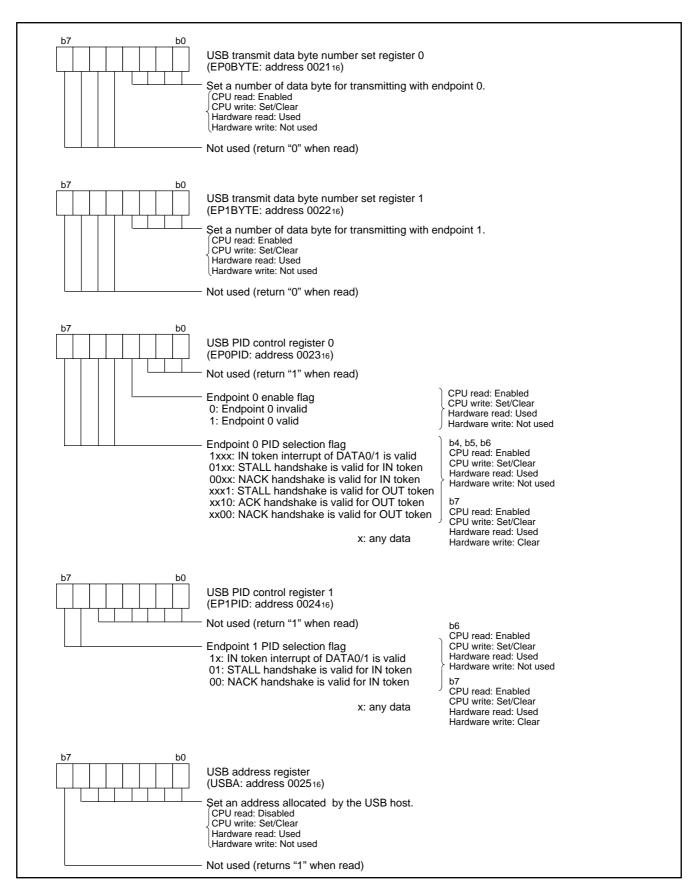

By setting bits 7 and 6 of the serial I/O1 control register (address 001A<sub>16</sub>) to "11", the USB mode is selected.

This mode conforms to "Low Speed device" of USB Specification 1.0. In this mode serial I/O1 interrupt have 5 sources; USB in and out token receive, USB reset, suspend, and resume. The USB

status/UART status register functions as the USB status register (USBSTS). There is the USBVREFOUT pin for the USB reference voltage output, and a D-line with 1.5 k $\Omega$  external resistor can be pull up. USB mode block and USB transceiver block show in figures 24 and 25.

Fig. 24 USB mode block diagram

Fig. 25 USB transceiver block diagram

Fig. 26 Structure of serial I/O1-related registers (1)

Fig. 27 Structure of serial I/O1-related registers (2)

Fig. 28 Structure of serial I/O1-related registers (3)

Fig. 29 Structure of serial I/O1-related registers (4)

Fig. 30 Structure of serial I/O1-related registers (5)

# **7532 Group**

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

# Note on using USB mode

# Handling of SE0 signal in program (at receiving)

7532 group has the border line to detect as USB RESET or EOP (End of Packet) on the width of SE0 (Single Ended 0).

A response apposite to a state of the device is expected.

The name of the following short words which is used in table 5 shows as follow.

- •TKNE: Token interrupt enable (bit 6 of address 2016)

- •RSME: Resume interrupt enable (bit 5 of address 2016)

- •RSTE: USB reset interrupt enable (bit 4 of address 2016)

- •Spec: A response of the device requested by USB Specification 1.0

- •SIE: Hardware operation in 7532 group

- •F/W: Recommendation process in the program

- •FEOPE: False EOP error flag (bit 2 of address 1916)

- •RxPID: Token interrupt flag (bit 7 of address 1F16)

#### Table 5 Relation of the width of SE0 and the state of the device

|                           |      | State of device                                                                           |                                                                                                          |                                                                                                        |         |                                             |  |  |

|---------------------------|------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------|---------------------------------------------|--|--|

| Width of SE0              |      | Idle state<br>TKNE = X<br>RSME = 0<br>RSTE =1                                             | End of Token in transaction  TKNE = 1  RSME = 0  RSTE =1                                                 | End of data or handshake<br>in transaction<br>TKNE = 0<br>RSME = 0<br>RSTE = 0 or 1                    |         | Suspend state  TKNE = 0  RSME = 1  RSTE = 0 |  |  |

|                           | Spec | Ignore                                                                                    | Ignore                                                                                                   | Ignore                                                                                                 |         |                                             |  |  |

| 0 μ sec.<br>0.5 μ sec.    | SIE  | Keep counting suspend timer                                                               | Not detected as EOP(in case of no detection EOP, SIE returns idle state as time out. FEOPE flag is set.) | Not detected as EOP(in case of no detection EOP, SIE returns idle state as timeup. FEOPE flag is set.) | Spec    | Reset or resume                             |  |  |

|                           | F/W  | Not acknowledge                                                                           | Not acknowledge                                                                                          | Wait for the next EOP flag                                                                             |         |                                             |  |  |

|                           | Spec | Keep alive                                                                                | EOP                                                                                                      | EOP                                                                                                    |         |                                             |  |  |

| 0.5 μ sec.                | SIE  | Initialize suspend timer count value                                                      | Token interrupt request                                                                                  | Set EOP flag                                                                                           |         |                                             |  |  |

| 2.5 μ sec.                | F/W  | Not acknowledge                                                                           | Token interrupt processing execute                                                                       | After checking the set of EOP flag, go to the next processing                                          | SIE     | Reset interrupt                             |  |  |

|                           | Spec | Keep alive or Reset                                                                       | EOP or Reset                                                                                             | EOP or Reset                                                                                           |         | request                                     |  |  |

|                           | SIE  | may determine as keep alive and Reset interrupt                                           | may determine as EOP and Reset interrupt                                                                 | may determine as EOP and Reset interrupt                                                               |         |                                             |  |  |

| 2.5 μ sec.<br>2.67 μ sec. | F/W  | Keep alive in case of no interrupt request  Reset processing in case of interrupt request | RxPID = 1> Token<br>interrupt processing<br>RxPID = 0> Reset<br>interrupt processing                     | Continue the processing in case of no interrupt request  Reset processing in case                      | F/W     | Reset interrupt processing                  |  |  |

|                           |      | <u> </u>                                                                                  | Desail                                                                                                   | of interrupt request                                                                                   | ' / V V | Resume interrupt                            |  |  |

|                           | Spec | Reset                                                                                     | Reset                                                                                                    | Reset                                                                                                  | -       | processing                                  |  |  |

| $2.67~\mu$ sec.           | SIE  | Reset interrupt request                                                                   | Reset interrupt request                                                                                  | Reset interrupt request                                                                                |         |                                             |  |  |

|                           | F/W  | Reset processing                                                                          | Reset processing                                                                                         | Reset processing                                                                                       |         |                                             |  |  |

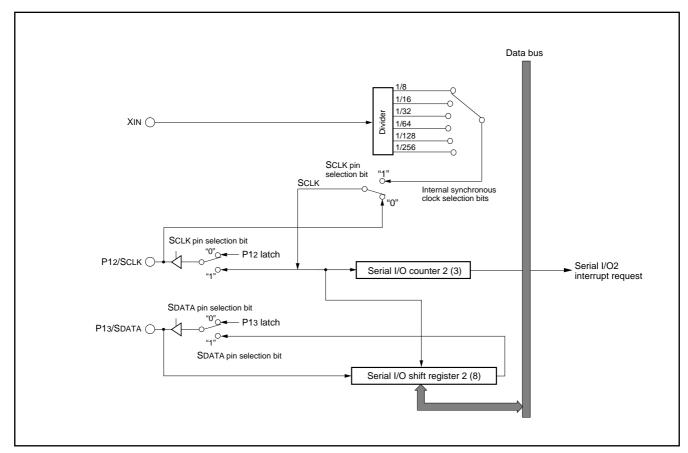

#### ●Serial I/O2

The serial I/O2 function can be used only for clock synchronous serial I/O.

For clock synchronous serial I/O2 the transmitter and the receiver must use the same clock. When the internal clock is used, transfer is started by a write signal to the serial I/O2 register.

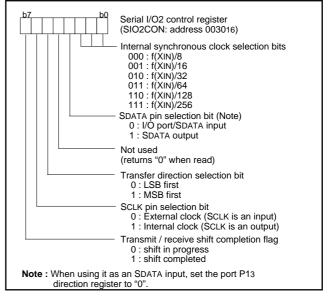

# [Serial I/O2 control register] SIO2CON

The serial I/O2 control register contains 8 bits which control various serial I/O functions.

- For receiving, set "0" to bit 3.

- When receiving, bit 7 is cleared by writing dummy data to serial I/ O2 register after shift is completed.

- Bit 7 is set earlier a half cycle of shift clock than completion of shift operation. Accordingly, when checking shift completion by using this bit, the setting is as follows:

- (1) check that this bit is set to "1",

- (2) wait a half cycle of shift clock,

- (3) read/write to serial I/O2 register.

Fig. 31 Structure of serial I/O2 control registers

Fig. 32 Block diagram of serial I/O2

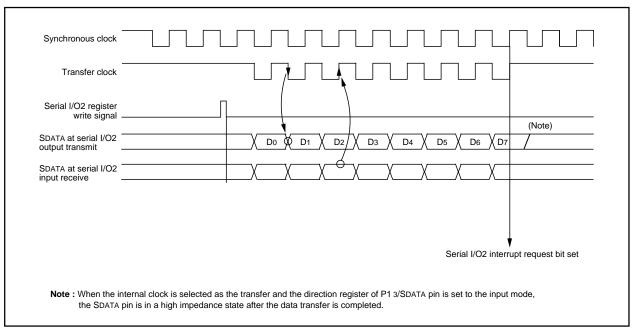

#### Serial I/O2 operation

By writing to the serial I/O2 register(address 003116) the serial I/O2 counter is set to "7".

After writing, the SDATA pin outputs data every time the transfer clock shifts from a high to a low level. And, as the transfer clock shifts from a low to a high, the SDATA pin reads data, and at the same time the contents of the serial I/O2 register are shifted by 1 bit.

When the internal clock is selected as the transfer clock source, the following operations execute as the transfer clock counts up to 8.

- Serial I/O2 counter is cleared to "0".

- Transfer clock stops at an "H" level.

- Interrupt request bit is set.

- Shift completion flag is set.

Also, the SDATA pin is in a high impedance state after the data transfer is complete (refer to figure 33).

When the external clock is selected as the transfer clock source, the interrupt request bit is set as the transfer clock counts up to 8, but external control of the clock is required since it does not stop. Notice that the SDATA pin is not in a high impedance state on the completion of data transfer.

Fig. 33 Serial I/O2 timing (LSB first)

#### **A-D Converter**

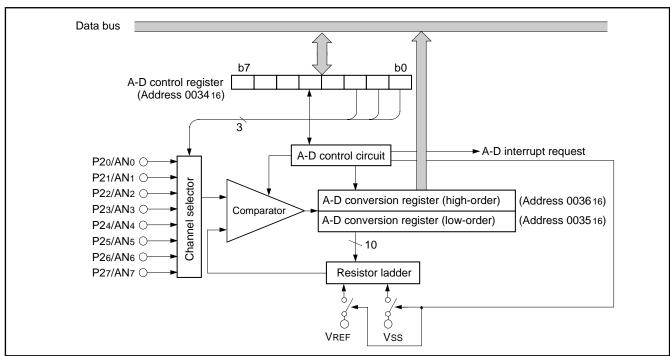

The functional blocks of the A-D converter are described below.

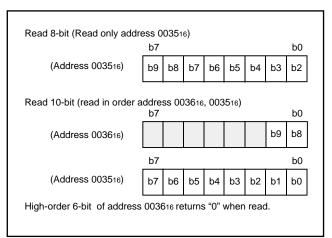

#### [A-D conversion register] AD

The A-D conversion register is a read-only register that stores the result of A-D conversion. Do not read out this register during an A-D conversion.

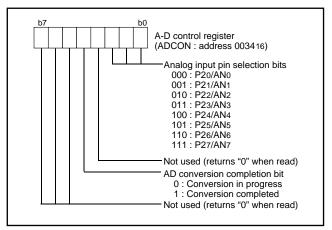

#### [A-D control register] ADCON

The A-D control register controls the A-D converter. Bit 2 to 0 are analog input pin selection bits. Bit 4 is the AD conversion completion bit. The value of this bit remains at "0" during A-D conversion, and changes to "1" at completion of A-D conversion.

A-D conversion is started by setting this bit to "0".

#### [Comparison voltage generator]

The comparison voltage generator divides the voltage between Vss and VREF by 1024 by a resistor ladder, and outputs the divided voltages. Since the generator is disconnected from VREF pin and Vss pin, current is not flowing into the resistor ladder.

#### [Channel Selector]

The channel selector selects one of ports P27/AN7 to P20/AN0, and inputs the voltage to the comparator.

#### [Comparator and control circuit]

The comparator and control circuit compares an analog input voltage with the comparison voltage and stores its result into the A-D conversion register. When A-D conversion is completed, the control circuit sets the AD conversion completion bit and the AD interrupt request bit to "1". Because the comparator is constructed linked to a capacitor, set f(XIN) to 500 kHz or more during A-D conversion.

Fig. 34 Structure of A-D control register

Fig. 35 Structure of A-D conversion register

Fig. 36 Block diagram of A-D converter

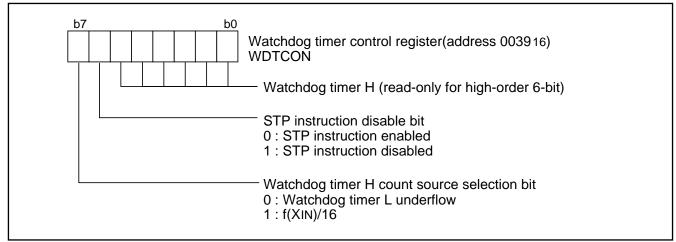

# **Watchdog Timer**

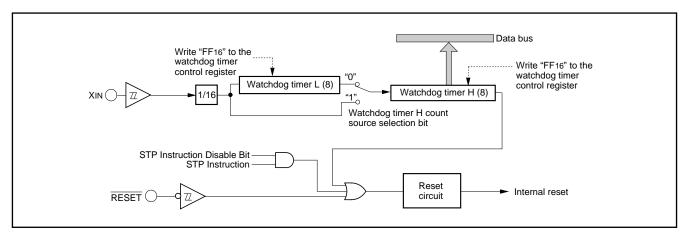

The watchdog timer gives a means for returning to a reset status when the program fails to run on its normal loop due to a runaway. The watchdog timer consists of an 8-bit watchdog timer H and an 8-bit watchdog timer L, being a 16-bit counter.

#### Standard operation of watchdog timer

The watchdog timer stops when the watchdog timer control register (address 003916) is not set after reset. Writing an optional value to the watchdog timer control register (address 003916) causes the watchdog timer to start to count down. When the watchdog timer H underflows, an internal reset occurs. Accordingly, it is programmed that the watchdog timer control register (address 003916) can be set before an underflow occurs.

When the watchdog timer control register (address 003916) is read, the values of the high-order 6-bit of the watchdog timer H, STP instruction disable bit and watchdog timer H count source selection bit are read.

#### Initial value of watchdog timer

By a reset or writing to the watchdog timer control register (address 003916), the watchdog timer H is set to "FF16" and the watchdog timer L is set to "FF16".

#### Operation of watchdog timer H count source selection bit

A watchdog timer H count source can be selected by bit 7 of the watchdog timer control register (address 003916). When this bit is "0", the count source becomes a watchdog timer L underflow signal. The detection time is 174.763 ms at f(XIN)=6 MHz.

When this bit is "1", the count source becomes f(XIN)/16. In this case, the detection time is 683  $\mu s$  at f(XIN)=6 MHz.

This bit is cleared to "0" after reset.

#### Operation of STP instruction disable bit

When the watchdog timer is in operation, the STP instruction can be disabled by bit 6 of the watchdog timer control register (address 0039<sub>16</sub>).

When this bit is "0", the STP instruction is enabled.

When this bit is "1", the STP instruction is disabled, and an internal reset occurs if the STP instruction is executed.

Once this bit is set to "1", it cannot be changed to "0" by program. This bit is cleared to "0" after reset.

Fig. 37 Block diagram of watchdog timer

Fig. 38 Structure of watchdog timer control register

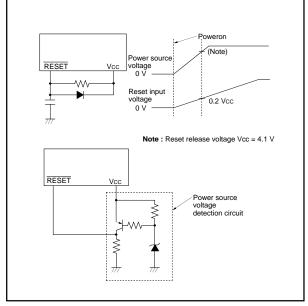

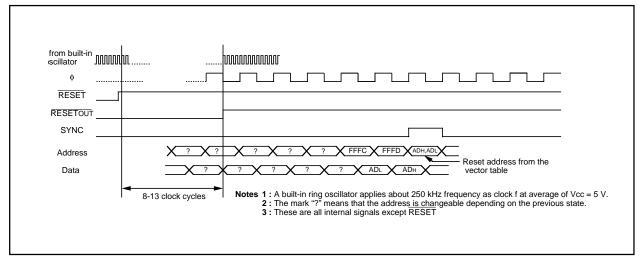

#### **Reset Circuit**

The microcomputer is put into a reset status by holding the RESET pin at the "L" level for 15  $\mu$ s or more when the power source voltage is 4.1 to 5.5 V and XIN is in stable oscillation.

After that, this reset status is released by returning the RESET pin to the "H" level. The program starts from the address having the contents of address FFFD16 as high-order address and the contents of address FFFC16 as low-order address.

Note that the reset input voltage should be 0.82~V or less when the power source voltage passes 4.1~V.

Fig. 39 Example of reset circuit

Fig. 40 Timing diagram at reset

Fig. 41 Internal status of microcomputer at reset

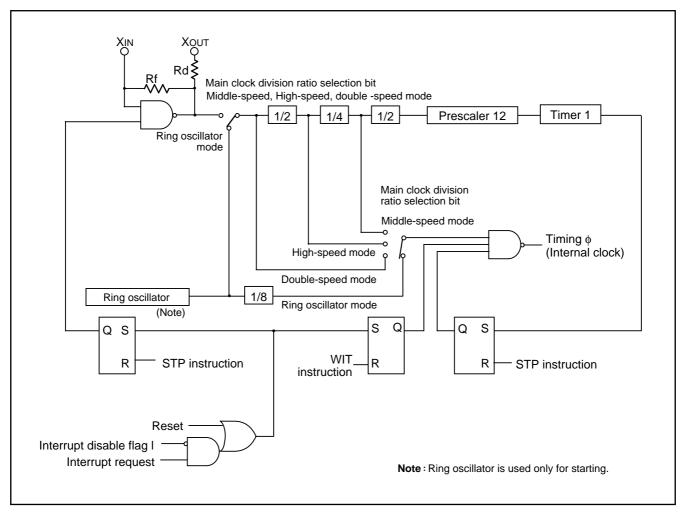

# **Clock Generating Circuit**

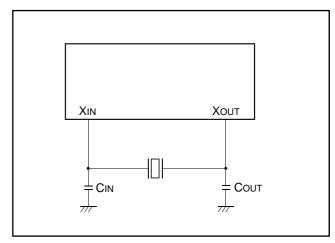

An oscillation circuit can be formed by connecting a resonator between XIN and XOUT.

Use the circuit constants in accordance with the resonator manufacturer's recommended values. No external resistor is needed between XIN and XOUT since a feed-back resistor exists on-chip.

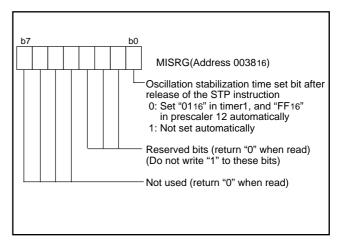

#### Oscillation control

#### Stop mode

When the STP instruction is executed, the internal clock  $\phi$  stops at an "H" level and the XIN oscillator stops. At this time, timer 1 is set to "0116" and prescaler 12 is set to "FF16" when the oscillation stabilization time set bit after release of the STP instruction is "0". On the other hand, timer 1 and prescaler 12 are not set when the above bit is "1". Accordingly, set the wait time fit for the oscillation stabilization time of the oscillator to be used.

f(XIN)/16 is forcibly connected to the input of prescaler 12.

When an external interrupt is accepted, oscillation is restarted but the internal clock  $\varphi$  remains at "H" until timer 1 underflows. As soon as timer 1 underflows, the internal clock  $\varphi$  is supplied. This is because when a ceramic oscillator is used, some time is required until a start of oscillation.

In case oscillation is restarted by reset, no wait time is generated. So apply an "L" level to the RESET pin while oscillation becomes stable.

#### Wait mode

If the WIT instruction is executed, the internal clock  $\phi$  stops at an "H" level, but the oscillator does not stop. The internal clock restarts if a reset occurs or when an interrupt is received.

Since the oscillator does not stop, normal operation can be started immediately after the clock is restarted.

To ensure that interrupts will be received to release the STP or WIT state, interrupt enable bits must be set to "1" before the STP or WIT instruction is executed.

When the STP status is released, prescaler 12 and timer 1 will start counting clock which is XIN divided by 16, so set the timer 1 interrupt enable bit to "0" before the STP instruction is executed.

#### Note

For use with the oscillation stabilization set bit after release of the STP instruction set to "1", set values in timer 1 and prescaler 12 after fully appreciating the oscillation stabilization time of the oscillator to be used.

# Clock mode

Operation is started by a built-in ring oscillator after releasing reset. A division ratio (1/1,1/2,1/8) is selected by setting bits 7 and 6 of the CPU mode register after releasing it.

Fig. 42 External circuit of ceramic resonator

Fig. 43 External clock input circuit

Fig. 44 Structure of MISRG

Fig. 45 Block diagram of system clock generating circuit (for ceramic resonator)

### **NOTES ON PROGRAMMING**

### **Processor Status Register**

The contents of the processor status register (PS) after reset are undefined except for the interrupt disable flag I which is "1". After reset, initialize flags which affect program execution. In particular, it is essential to initialize the T flag and the D flag because of their effect on calculations.

### Interrupts

The contents of the interrupt request bit do not change even if the BBC or BBS instruction is executed immediately after they are changed by program because this instruction is executed for the previous contents. For executing the instruction for the changed contents, execute one instruction before executing the BBC or BBS instruction.

#### **Decimal Calculations**

- For calculations in decimal notation, set the decimal mode flag D to "1", then execute the ADC instruction or SBC instruction. In this case, execute SEC instruction, CLC instruction or CLD instruction after executing one instruction before the ADC instruction or SBC instruction.

- In the decimal mode, the values of the N (negative), V (overflow) and Z (zero) flags are invalid.

#### **Timers**

- When n (0 to 255) is written to a timer latch, the frequency division ratio is 1/(n+1).

- When a count source of timer X is switched, stop a count of timer X.

### **Ports**

• The values of the port direction registers cannot be read.

That is, it is impossible to use the LDA instruction, memory operation instruction when the T flag is "1", addressing mode using direction register values as qualifiers, and bit test instructions such as BBC and BBS.

It is also impossible to use bit operation instructions such as CLB and SEB and read/modify/write instructions of direction registers for calculations such as ROR.

For setting direction registers, use the LDM instruction, STA instruction, etc.

Set "1" to each bit 6 of the port P3 direction register and the port P3 register.

### **A-D Converter**

The comparator uses internal capacitors whose charge will be lost if the clock frequency is too low.

Make sure that f(XIN) is 500kHz or more during A-D conversion. Do not execute the STP instruction during A-D conversion.

### **Instruction Execution Timing**

The instruction execution time can be obtained by multiplying the frequency of the internal clock  $\phi$  by the number of cycles mentioned in the machine-language instruction table.

The frequency of the internal clock  $\phi$  is the same as that of the XIN in double-speed mode, twice the XIN cycle in high-speed mode and 8 times the XIN cycle in middle-speed mode.

### **NOTES ON USE**

### **Handling of Power Source Pin**

In order to avoid a latch-up occurrence, connect a capacitor suitable for high frequencies as bypass capacitor between power source pin (Vcc pin) and GND pin (Vss pin). Besides, connect the capacitor to as close as possible. For bypass capacitor which should not be located too far from the pins to be connected, a ceramic capacitor of 0.01  $\mu F$  to 0.1  $\mu F$  is recommended.

### Handling of USBVREFOUT Pin

In order to prevent the instability of the USBVREFOUT output due to external noise, connect a capacitor as bypass capacitor between USBVREFOUT pin and GND pin (Vss pin). Besides, connect the capacitor to as close as possible. For bypass capacitor, a ceramic or electrolytic capacitor of 0.1  $\mu F$  is recommended.

### **One Time PROM Version**

The CNVss pin is connected to the internal memory circuit block by a low-ohmic resistance, since it has the multiplexed function to be a programmable power source pin (VPP pin) as well.

To improve the noise reduction, connect a track between CNVss pin and Vss pin with 1 to 10  $k\Omega$  resistance.

The mask ROM version track of CNVss pin has no operational interference even if it is connected via a resistor.

### **DATA REQUIRED FOR MASK ORDERS**

The following are necessary when ordering a mask ROM production:

- (1) Mask ROM Order Confirmation Form

- (2) Mark Specification Form

- (3) Data to be written to ROM, in EPROM form (three identical copies)

### **ROM PROGRAMMING METHOD**

The built-in PROM of the blank One Time PROM version can be read or programmed with a general-purpose PROM programmer using a special programming adapter. Set the address of PROM programmer in the user ROM area.

Table 6 Special programming adapter

| Package | Name of Programming Adapter |

|---------|-----------------------------|

| 36P2R-A | PCA7535FP                   |

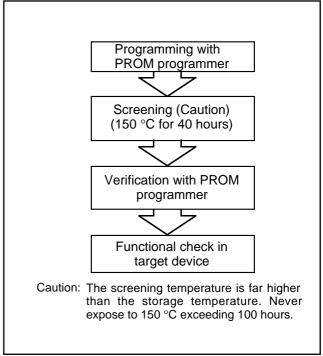

The PROM of the blank One Time PROM version is not tested or screened in the assembly process and following processes. To ensure proper operation after programming, the procedure shown in Figure 46 is recommended to verify programming.

Fig. 46 Programming and testing of One Time PROM version

### **ELECTRICAL CHARACTERISTICS**

### **Absolute Maximum Ratings**

Table 7 Absolute maximum ratings

| Symbol |                    | Parameter                                                     | Conditions                       | Ratings           | Unit |

|--------|--------------------|---------------------------------------------------------------|----------------------------------|-------------------|------|

| Vcc    | Power source volta | age                                                           |                                  | -0.3 to 7.0       | V    |

| VI     | Input voltage      | P00-P07, P10-P14, P20-P27, P30-<br>P35, P37, VREF             | All voltages are                 | -0.3 to Vcc + 0.3 | V    |

| Vı     | Input voltage      | RESET, XIN                                                    | based on Vss. Output transistors | -0.3 to Vcc + 0.3 | V    |

| VI     | Input voltage      | CNVss (Note 1)                                                | are cut off.                     | -0.3 to 13        | V    |

| Vo     | Output voltage     | P00–P07, P10–P14, P20–P27, P30–<br>P35, P37, XOUT, USBVREFOUT | -                                | -0.3 to Vcc + 0.3 | V    |

| Pd     | Power dissipation  |                                                               | Ta = 25°C                        | 300 (Note 2)      | mW   |

| Topr   | Operating tempera  | ature                                                         |                                  | -20 to 85         | °C   |

| Tstg   | Storage temperatu  | ire                                                           |                                  | -40 to 125        | °C   |

Notes 1: It is a rating only for the One Time PROM version. Connect to Vss for the Mask ROM version.

2: 200 mW for 32-pin version.

### **Recommended Operating Conditions**

Table 8 Recommended operating conditions (Vcc = 4.1 to 5.5 V, Ta = -20 to 85 °C, unless otherwise noted)

| 0                  | Barranta                                                                                     | _                                          |         | Lin  | nits       | Unit |

|--------------------|----------------------------------------------------------------------------------------------|--------------------------------------------|---------|------|------------|------|

| Symbol             | Paramete                                                                                     |                                            | Min.    | Тур. | Max.       | Unit |

| Vcc                | Power source voltage                                                                         | f(XIN) = 6 MHz                             | 4.1     | 5.0  | 5.5        | V    |

| Vss                | Power source voltage                                                                         |                                            |         | 0    |            | V    |

| VREF               | Analog reference voltage                                                                     |                                            | 2.0     |      | Vcc        | V    |

| VIH                | "H" input voltage                                                                            | P00-P07, P10-P14, P20-P27, P30-P35, P37    | 0.8 Vcc |      | Vcc        | V    |

| VIH                | "H" input voltage (TTL input level selected)                                                 | P10, P12, P13, P37                         | 2.0     |      | Vcc        | V    |

| VIH                | "H" input voltage                                                                            | RESET, XIN                                 | 0.8 Vcc |      | Vcc        | V    |

| VIH                | "H" input voltage                                                                            | D+, D-                                     | 2.0     |      | 3.6        | V    |

| VIL                | "L" input voltage                                                                            | P00-P07, P10-P14, P20-P27,<br>P30-P35, P37 | 0       |      | 0.3 Vcc    | V    |

| VIL                | "L" input voltage (TTL input level selected)                                                 | P10, P12, P13, P37                         | 0       |      | 0.8        | V    |

| VIL                | "L" input voltage                                                                            | RESET, CNVss                               | 0       |      | 0.2 Vcc    | V    |

| VIL                | "L" input voltage                                                                            | D+, D-                                     | 0       |      | 0.8        | V    |

| VIL                | "L" input voltage                                                                            | XIN                                        | 0       |      | 0.16Vcc    | V    |

| ∑IOH(peak)         | "H" total peak output current (Note 1)                                                       | P00–P07, P10–P14, P20–P27,<br>P30–P35, P37 |         |      | -80        | mA   |

| $\Sigma$ lOL(peak) | "L" total peak output current (Note 1)                                                       | P00-P07, P10-P14, P20-P27,<br>P37          |         |      | 80         | mA   |

| $\Sigma$ lOL(peak) | "L" total peak output current (Note 1)                                                       | P30-P35                                    |         |      | 60         | mA   |

| $\Sigma$ IOH(avg)  | "H" total average output current (Note 1)                                                    | P00-P07, P10-P14, P20-P27,<br>P30-P35, P37 |         |      | -40        | mA   |

| $\Sigma$ lOL(avg)  | "L" total average output current (Note 1)                                                    | P00-P07, P10-P14, P20-P27,<br>P37          |         |      | 40         | mA   |

| $\sum$ IOL(avg)    | "L" total average output current (Note 1)                                                    | P30-P35                                    |         |      | 30         | mA   |

| IOH(peak)          | "H" peak output current (Note 2)                                                             | P00-P07, P10-P14, P20-P27,<br>P30-P35, P37 |         |      | -10        | mA   |

| IOL(peak)          | "L" peak output current (Note 2)                                                             | P00–P07, P10–P14, P20–P27,<br>P37          |         |      | 10         | mA   |

| IOL(peak)          | "L" peak output current (Note 2)                                                             | P30-P35                                    |         |      | 30         | mA   |

| IOH(avg)           | "H" average output current (Note 3)                                                          | P00-P07, P10-P14, P20-P27,<br>P30-P35, P37 |         |      | <b>-</b> 5 | mA   |

| IOL(avg)           | "L" average output current (Note 3)                                                          | P00-P07, P10-P14, P20-P27,<br>P37          |         |      | 5          | mA   |

| IOL(avg)           | "L" average output current (Note 3)                                                          | P30-P35                                    |         |      | 15         | mA   |

| f(XIN)             | Internal clock oscillation frequency (Note 4) at ceramic oscillation or external clock input | VCC = 4.1 to 5.5 V<br>Double-speed mode    |         |      | 6          | MHz  |

Note 1: The total output current is the sum of all the currents flowing through all the applicable ports. The total average current is an average value measured over 100 ms. The total peak current is the peak value of all the currents.

- 2: The peak output current is the peak current flowing in each port.

- 3: The average output current IoL (avg), IoH (avg) in an average value measured over 100 ms.

4: When the oscillation frequency has a duty cycle of 50 %.

### **Electrical Characteristics**

Table 9 Electrical characteristics (1) (Vcc = 4.1 to 5.5 V, Vss = 0 V, Ta = -20 to 85 °C, unless otherwise noted)

| Symbol  |                    | Parameter                                                         | Test conditions                                                                                                                              |         | Limits |      | Unit  |

|---------|--------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|------|-------|

| Symbol  |                    | Falametei                                                         | Test conditions                                                                                                                              | Min.    | Тур.   | Max. | Offic |

| Vон     | "H" output voltage | P00–P07, P10–P14, P20–P27,<br>P30–P35, P37 (Note 1)               | IOH = -5 mA<br>VCC = 4.1 to 5.5 V                                                                                                            | Vcc-1.5 |        |      | V     |

|         |                    |                                                                   | IOH = -1.0 mA<br>VCC = 4.1 to 5.5 V                                                                                                          | Vcc-1.0 |        |      | V     |

| Vон     | "H" output voltage | D+, D-                                                            | Vcc = 4.40 to 5.25 V Pull-down through 15kΩ $\pm$ 5% for D+, D-Pull-up through 1.5kΩ $\pm$ 5% by USBVREFOUT for D- (Ta = 0 to 70 °C)         | 2.8     |        | 3.6  | V     |

| VoL     | "L" output voltage | P00–P07, P10–P14, P20–P27,<br>P37                                 | IOL = 5 mA<br>VCC = 4.1 to 5.5 V                                                                                                             |         |        | 1.5  | V     |

|         |                    |                                                                   | IOL = 1.5 mA<br>VCC = 4.1 to 5.5 V                                                                                                           |         |        | 0.3  | V     |

| VoL     | "L" output voltage | D+, D-                                                            | VCC = 4.40 to 5.25 V Pull-down through $15k\Omega\pm5\%$ for D+, D-Pull-up through $1.5k\Omega\pm5\%$ by USBVREFOUT for D- (Ta = 0 to 70 °C) |         |        | 0.3  | V     |

| VoL     | "L" output voltage | P30-P35                                                           | IOL = 15 mA<br>VCC = 4.1 to 5.5 V                                                                                                            |         |        | 2.0  | V     |

|         |                    |                                                                   | IOL = 1.5 mA<br>VCC = 4.1 to 5.5 V                                                                                                           |         |        | 0.3  | V     |

| VT+-VT- | Hysteresis         | D+, D-                                                            |                                                                                                                                              |         | 0.15   |      | V     |

| VT+-VT- | Hysteresis         | CNTR <sub>0</sub> , INT <sub>0</sub> (Note 2),<br>P00–P07(Note 3) |                                                                                                                                              |         | 0.4    |      | V     |

| VT+-VT- | Hysteresis         | RXD, SCLK, SDATA (Note 2)                                         |                                                                                                                                              |         | 0.5    |      | V     |

| VT+-VT- | Hysteresis         | RESET                                                             |                                                                                                                                              |         | 0.5    |      | V     |

| liн     | "H" input current  | P00–P07, P10–P14, P20–P27,<br>P30–P35, P37                        | VI = VCC<br>(Pin floating. Pull up<br>transistors "off")                                                                                     |         |        | 5.0  | μА    |

| lін     | "H" input current  | RESET                                                             | VI = VCC                                                                                                                                     |         |        | 5.0  | μА    |

| Іін     | "H" input current  | XIN                                                               | VI = VCC                                                                                                                                     |         | 4      |      | μΑ    |

| liL     | "L" input current  | P00–P07, P10–P14, P20–P27,<br>P30–P35, P37                        | VI = VSS<br>(Pin floating. Pull up<br>transistors "off")                                                                                     |         |        | -5.0 | μА    |

| lıL     | "L" input current  | RESET, CNVss                                                      | VI = VSS                                                                                                                                     |         |        | -5.0 | μΑ    |

| lıL     | "L" input current  | XIN                                                               | VI = VSS                                                                                                                                     |         | -4     |      | μА    |

| liL     | "L" input current  | P00–P07, P30–P35, P37                                             | VI = VSS<br>(Pull up transistors"on")                                                                                                        |         | -0.2   | -0.5 | mA    |

| VRAM    | RAM hold voltage   |                                                                   | When clock stopped                                                                                                                           | 2.0     |        | 5.5  | V     |

Note 1: P11 is measured when the P-channel output disable bit of the UART control register (bit 4 of address 001B16) is "0".

2: RXD, SCLK, SDATA, and INTo have hysteresises only when bits 0 and 2 of the port P1P3 control register are set to "0" (CMOS level). 3: It is available only when operating key-on wake-up.

Table 10 Electrical characteristics (2) (Vcc = 4.1 to 5.5 V, Vss = 0 V, Ta = -20 to 85 °C, unless otherwise noted)

| Cumah al | Donomotor            | Test conditions                                                                                                      |                 |      | Limits |      | Unit |

|----------|----------------------|----------------------------------------------------------------------------------------------------------------------|-----------------|------|--------|------|------|

| Symbol   | Parameter            | rest conditions                                                                                                      |                 | Min. | Тур.   | Max. |      |

| Icc      | Power source current | Double-speed mode, f(XIN) = 6 MHz<br>Output transistors "off"                                                        |                 |      | 6      | 10   | mA   |

|          |                      | f(XIN) = 6 MHz (in WIT state) Output transistors "off"                                                               |                 |      | 1.6    | 3.2  | mA   |

|          |                      | Increment when A-D conversion is exe<br>f(XIN) = 6 MHz, Vcc = 5 V                                                    | ecuted          |      | 0.8    |      | mA   |

|          |                      | All oscillation stopped (in STP state)                                                                               | Ta = 25 °C      |      | 0.1    | 1.0  | μА   |

|          |                      | Output transistors "off"                                                                                             | Ta = 85 °C      |      |        | 10   | μА   |

|          |                      | Vcc = 4.40 to 5.25 V Oscillation stopped in USB mode USB (SUSPEND), (pull-up resistor output not included) (Fig. 47) | Ta = 0 to 70 °C |      |        | 300  | μА   |

### **A-D Converter Characteristics**

Table 11 A-D Converter characteristics (1) (Vcc = 4.1 to 5.5 V, Vss = 0 V, Ta = -20 to 85 °C, unless otherwise noted)

| 0       | D                                    | Total conditions                 |      | Limits |      | 1.1-24  |

|---------|--------------------------------------|----------------------------------|------|--------|------|---------|

| Symbol  | Parameter                            | Test conditions                  | Min. | Тур.   | Max. | Unit    |

| _       | Resolution                           |                                  |      |        | 10   | Bits    |

| _       | Linearity error                      | Vcc = 4.1 to 5.5 V<br>Ta = 25 °C |      |        | ±3   | LSB     |

| _       | Differential nonlinear error         | Vcc = 4.1 to 5.5 V<br>Ta = 25 °C |      |        | ±0.9 | LSB     |

| Vот     | Zero transition voltage              | VCC = VREF = 5.12 V              | 0    | 5      | 20   | mV      |

| VFST    | Full scale transition voltage        | VCC = VREF = 5.12 V              | 5105 | 5115   | 5125 | mV      |

| tCONV   | Conversion time                      |                                  |      |        | 122  | tc(XIN) |

| RLADDER | Ladder resistor                      |                                  |      | 55     |      | kΩ      |

| IVREF   | Reference power source input current | VREF = 5.0 V                     | 50   | 150    | 200  |         |

|         |                                      | VREF = 3.0 V                     | 30   | 70     | 120  | — μA    |

| II(AD)  | A-D port input current               |                                  |      |        | 5.0  | μА      |

Fig. 47 Power source current measurement circuit in USB mode at oscillation stop

### **Timing Requirements**

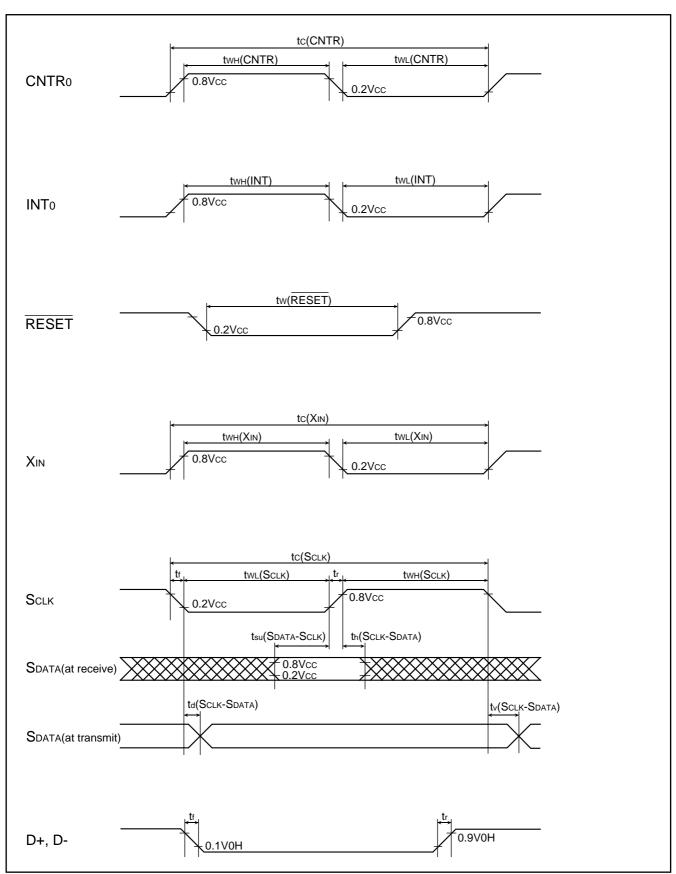

Table 12 Timing requirements (VCC = 4.1 to 5.5 V, Vss = 0 V, Ta = -20 to 85 °C, unless otherwise noted)

| O. mah al       | Devenuetes                              |      | Limits |      |      |

|-----------------|-----------------------------------------|------|--------|------|------|

| Symbol          | Parameter                               | Min. | Тур.   | Max. | Unit |

| tw(RESET)       | Reset input "L" pulse width             | 15   |        |      | μs   |

| tc(XIN)         | External clock input cycle time         | 166  |        |      | ns   |

| twh(XIN)        | External clock input "H" pulse width    | 70   |        |      | ns   |

| twL(XIN)        | External clock input "L" pulse width    | 70   |        |      | ns   |

| tc(CNTR)        | CNTRo input cycle time                  | 200  |        |      | ns   |

| twH(CNTR)       | CNTRo, INTo input "H" pulse width       | 80   |        |      | ns   |

| twL(CNTR)       | CNTRo, INTo input "L" pulse width       | 80   |        |      | ns   |

| tc(Sclk)        | Serial I/O2 clock input cycle time      | 1000 |        |      | ns   |

| twh(Sclk)       | Serial I/O2 clock input "H" pulse width | 400  |        |      | ns   |

| twL(Sclk)       | Serial I/O2 clock input "L" pulse width | 400  |        |      | ns   |