## Electronic Volume and Tone Control for Car Stereo Systems

#### Overview

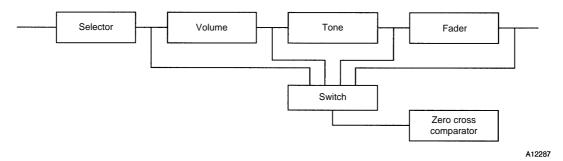

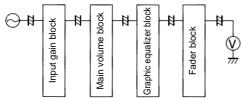

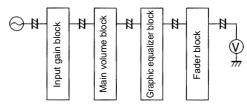

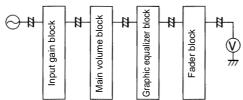

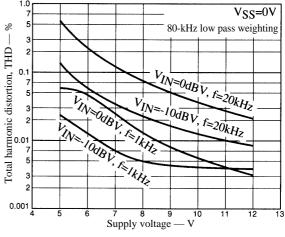

The LC75385NE-R is an electronic volume and tone control IC that can implement volume, balance, fader, bass/treble, loudness, input switching, and input gain control functions with a minimum number of external components.

#### **Features**

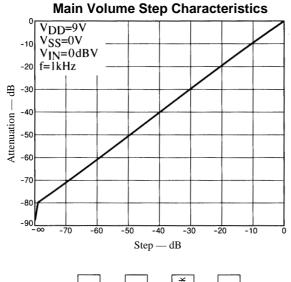

- Volume: 81 positions: from 0 dB to −79 dB in 1-dB steps and -∞

- A balance function can be implemented by controlling the left and right volume settings independently.

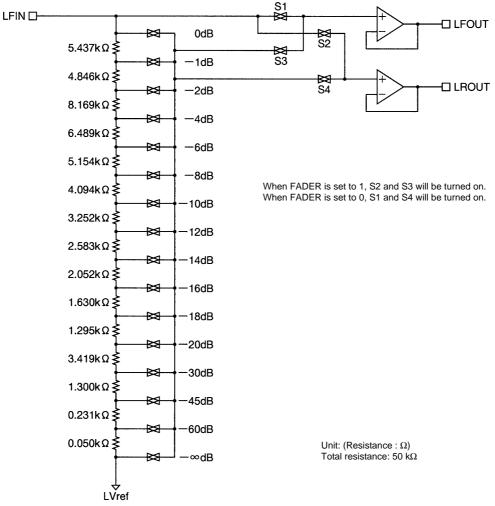

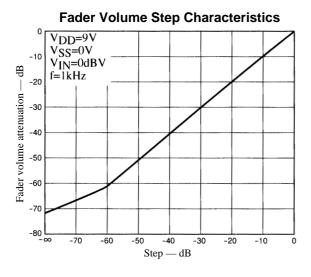

- Fader: Either the rear or front outputs can be attenuated over 16 positions. (16 positions: From 0 dB to -2 dB in 1-dB steps, from -2 dB to -20 dB in 2-dB steps, from -20 to -30 dB in one 10-dB step, -45 dB, -60 dB, and -∞)

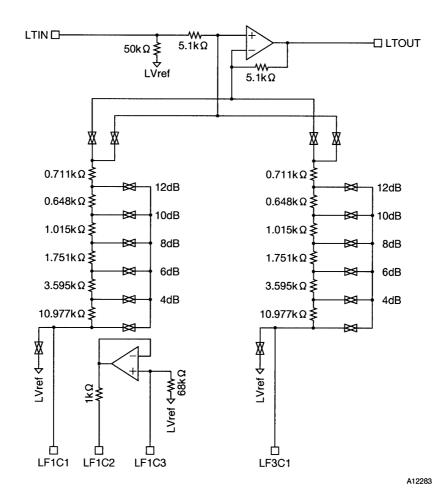

- Bass/treble: Control over ±12 dB in 2-dB steps in each band.

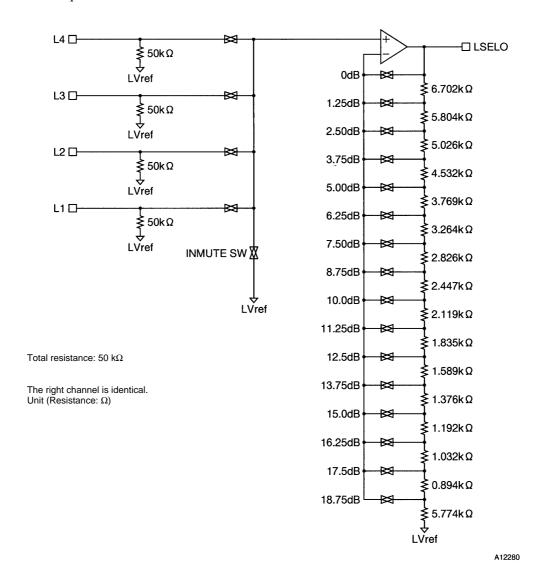

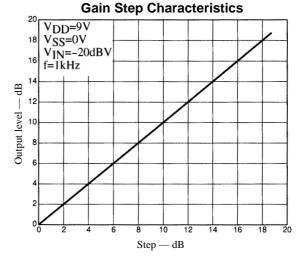

- Input gain: The input signal can be amplified by from 0 to +18.75 dB in 1.25 dB steps.

- Input switching: One of four signals can be selected for each of the left and right channels.

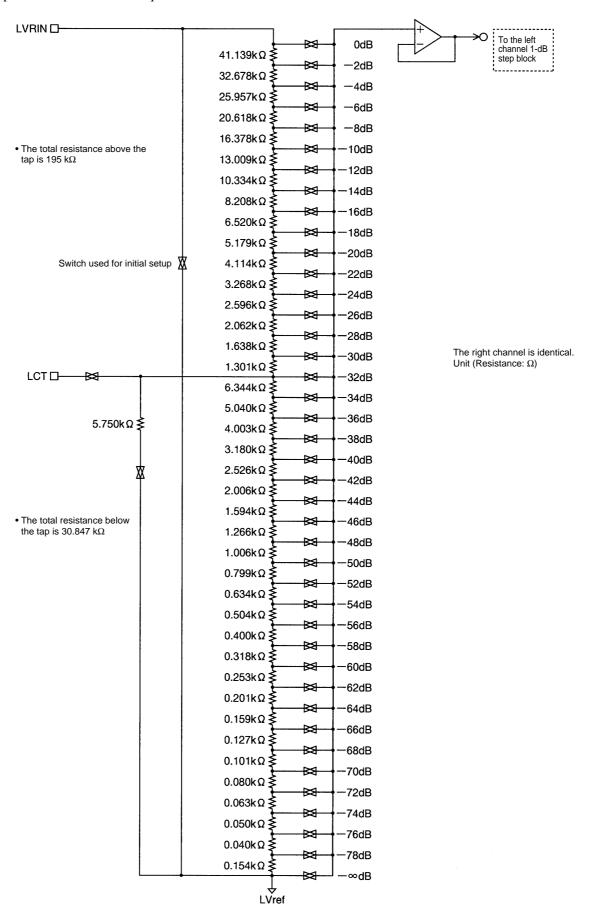

- Loudness: Taps are output from a 2-dB step volume control ladder resistor starting at the -32-dB position. A loudness function can be implemented by attaching external capacitors and resistors.

- On-chip buffer amplifiers minimize the number of required external components.

- Minimal switching noise when no input signals are present due to fabrication in a silicon gate CMOS process that minimizes the noise generated by internal switches.

- Use of zero-cross switching circuits for internal switches minimizes switching noise when signals are present.

- Built-in V<sub>DD</sub>/2 reference voltage generator circuit

- All controls can be set from serial input data transferred over a CCB interface.

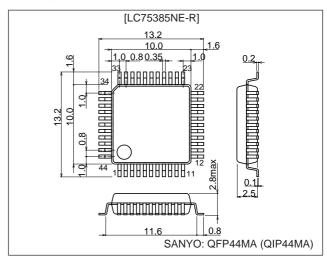

#### **Package Dimensions**

unit: mm

#### 3148-QFP44MA

- CCB is a trademark of SANYO ELECTRIC CO., LTD.

- CCB is SANYO's original bus format and all the bus addresses are controlled by SANYO.

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained berein

# Specifications Absolute Maximum Ratings at Ta = 25°C, $V_{SS}$ = 0 V

| Parameter                   | Symbol              | Symbol Conditions                                  |                                         | Unit |

|-----------------------------|---------------------|----------------------------------------------------|-----------------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max | $V_{DD}$                                           | 11                                      | V    |

| Maximum input voltage       | V <sub>IN</sub> max | All input pins                                     | $V_{SS} - 0.3 \text{ to } V_{DD} + 0.3$ | V    |

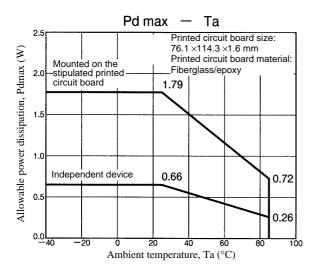

| Allowable power dissipation | Pd max              | Ta ≤ 85°C, when mounted on a printed circuit board | 720                                     | mW   |

| Operating temperature       | Topr                |                                                    | -40 to +85                              | °C   |

| Storage temperature         | Tstg                |                                                    | -50 to +125                             | °C   |

## Allowable Operating Ranges at $Ta=25^{\circ}C,\,V_{SS}=0~V$

| Parameter                | Symbol Conditions  |                 |          | Unit |                 |       |

|--------------------------|--------------------|-----------------|----------|------|-----------------|-------|

| Farameter                |                    |                 | min      | typ  | max             | Ullit |

| Supply voltage           | V <sub>DD</sub>    | V <sub>DD</sub> | 6.0      |      | 10.5            | V     |

| High-level input voltage | V <sub>IH</sub>    | CL, DI, CE      | 4.0      |      | V <sub>DD</sub> | V     |

| Low-level input voltage  | V <sub>IL</sub>    | CL, DI, CE      | $V_{SS}$ |      | 1.0             | V     |

| Input voltage amplitude  | V <sub>IN</sub>    |                 | $V_{SS}$ |      | V <sub>DD</sub> | Vp-p  |

| Input pulse width        | t <sub>øW</sub>    | CL              | 1        |      |                 | μs    |

| Setup time               | t <sub>setup</sub> | CL, DI, CE      | 1        |      |                 | μs    |

| Hold time                | thold              | CL, DI, CE      | 1        |      |                 | μs    |

| Operating frequency      | fopg               | CL              |          |      | 500             | kHz   |

### Electrical Characteristics at $Ta=25^{\circ}C,\,V_{DD}=9~V,\,V_{SS}=0~V$

| Parameter                | 0      | Di                         | Conditions       |       | Unit   |      |      |

|--------------------------|--------|----------------------------|------------------|-------|--------|------|------|

| Parameter                | Symbol | Pins                       | Conditions       | min   | typ    | max  | Unit |

| [Input Block]            |        |                            |                  |       |        |      |      |

| Input resistance         | Rin    | L1 to L4, R1 to R4         |                  | 30    | 50     | 70   | kΩ   |

| Minimum input gain       | Ginmin | L1 to L4, R1 to R4         |                  | -1    | 0      | +1   | dB   |

| Maximum input gain       | Ginmax |                            |                  | +16.5 | +18.75 | +21  | dB   |

| Inter-step setting error | ATerr  |                            |                  |       |        | ±0.6 | dB   |

| Left/right balance       | BAL    |                            |                  |       |        | ±0.5 | dB   |

| [Volume Block]           |        |                            |                  |       |        |      |      |

| Input resistance         | Rvr    | LVRIN, RVRIN, loudness off |                  | 113   | 226    | 339  | kΩ   |

| Inter-step setting error | ATerr  |                            |                  |       |        | ±0.5 | dB   |

| Left/right balance       | BAL    |                            |                  |       |        | ±0.5 | dB   |

| [Tone Control Block]     |        |                            |                  |       |        |      |      |

| Inter-step setting error | ATerr  |                            |                  |       |        | ±1.0 | dB   |

| Bass control range       | Gbass  |                            | max. boost/cut   | ±9    | ±12    | ±15  | dB   |

| Treble control range     | Gtre   |                            | max. boost/cut   | ±9    | ±12    | ±15  | dB   |

| Left/right balance       | BAL    |                            |                  |       |        | ±0.5 | dB   |

| [Fader Block]            |        |                            |                  |       |        |      |      |

| Input resistance         | Rfed   | LFIN, RFIN                 |                  | 25    | 50     | 100  | kΩ   |

|                          |        |                            | 0 dB to -2 dB    |       |        | ±0.5 | dB   |

| Inter-step setting error | ATerr  |                            | -2 dB to -20 dB  |       |        | ±1   | dB   |

| miler-step setting error | Aren   |                            | −20 dB to −30 dB |       |        | ±2   | dB   |

|                          |        |                            | -30 dB to -60 dB |       |        | ±3   | dB   |

| Left/right balance       | BAL    |                            |                  |       |        | ±0.5 | dB   |

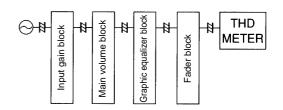

#### **Overall Characteristics**

| Parameter                    | Cumbal               | Symbol Conditions —                                                   |     | Ratings |         |      |  |

|------------------------------|----------------------|-----------------------------------------------------------------------|-----|---------|---------|------|--|

| Parameter                    | Symbol               |                                                                       |     | typ     | typ max |      |  |

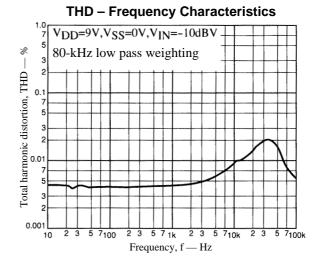

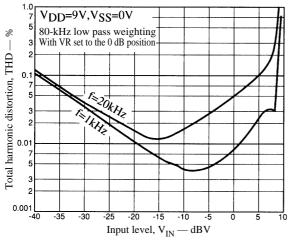

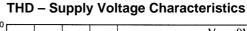

| Total harmonic distortion    | THD 1                | $V_{IN} = -10 \text{ dBV, f} = 1 \text{ kHz}$                         |     | 0.004   |         | %    |  |

| Total Harmonic distortion    | THD 2                | $V_{IN} = -10 \text{ dBV, f} = 10 \text{ kHz}$                        |     | 0.006   |         | %    |  |

| Inter-input crosstalk        | СТ                   | V <sub>IN</sub> = 1 Vrms, f = 1 kHz                                   | 80  | 88      |         | dB   |  |

| Left/right channel crosstalk | СТ                   | V <sub>IN</sub> = 1 Vrms, f = 1 kHz                                   | 80  | 88      |         | dB   |  |

| Maximum attenuation          | V <sub>O</sub> min 1 | V <sub>IN</sub> = 1 Vrms, f = 1 kHz                                   | 80  | 88      |         | dB   |  |

| Maximum attenuation          | V <sub>O</sub> min 2 | $V_{IN}$ = 1 Vrms, f = 1 kHz, INMUTE, with the fader set to $-\infty$ | 90  | 95      |         | dB   |  |

| Output noise voltage         | V <sub>N</sub> 1     | All controls flat, with the IHF-A filter                              |     | 5       | 10      | μV   |  |

| Output hoise voltage         | V <sub>N</sub> 2     | All controls flat, with a 20 Hz to 20 kHz bandpass filter             |     | 7       | 15      | μV   |  |

| Current drain                | I <sub>DD</sub>      |                                                                       |     | 33      | 40      | mA   |  |

| High-level input current     | I <sub>IH</sub>      | CL, DI, CE, V <sub>IN</sub> = 9 V                                     |     |         | 10      | μA   |  |

| Low-level input current      | I <sub>IL</sub>      | CL, DI, CE, V <sub>IN</sub> = 0 V                                     | -10 |         |         | μΑ   |  |

| Maximum input voltage        | V <sub>CL</sub>      | THD = 1 %, $R_L$ = 10 kΩ, all controls flat, FiN = 1 kHz              | 2.5 | 2.9     |         | Vrms |  |

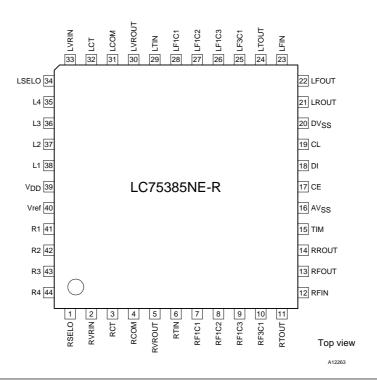

#### **Pin Arrangement**

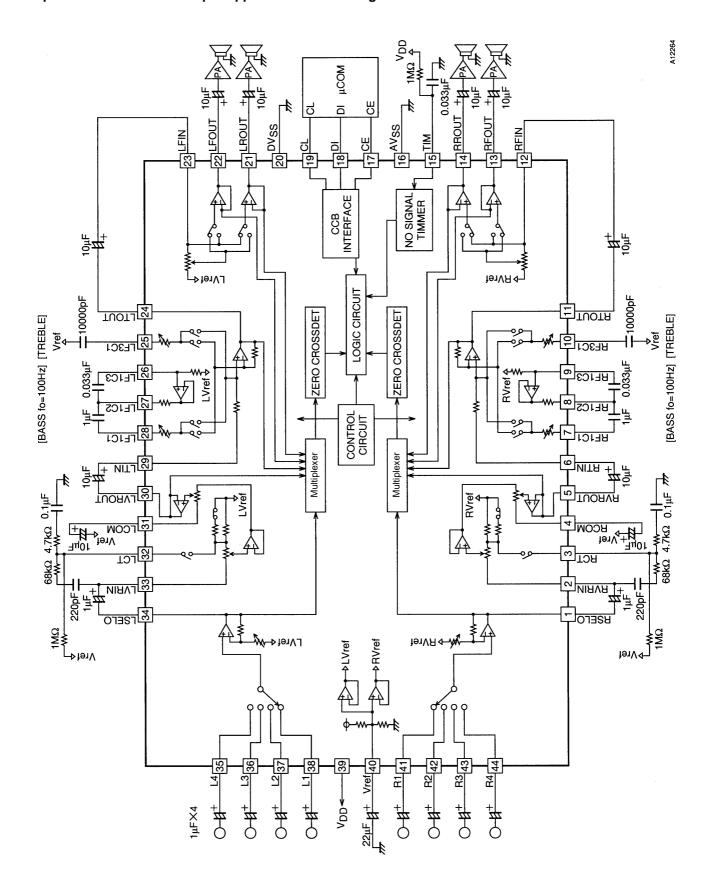

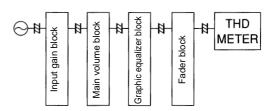

#### **Equivalent Circuit and Sample Application Circuit Diagram**

#### **Pin Functions**

| Pin No. | Pin              | Function                                                                                                                                                                                                  | Notes                 |

|---------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 38      | L1               |                                                                                                                                                                                                           |                       |

| 37      | L2               |                                                                                                                                                                                                           | √ V <sub>DD</sub>     |

| 36      | L3               |                                                                                                                                                                                                           |                       |

| 35      | L4               |                                                                                                                                                                                                           |                       |

| 41      | R1               | Single end inputs                                                                                                                                                                                         |                       |

| 42      | R2               |                                                                                                                                                                                                           | <u> </u>              |

| 43      | R3               |                                                                                                                                                                                                           |                       |

| 44      | R4               |                                                                                                                                                                                                           | LVref<br>RVref A12265 |

|         |                  |                                                                                                                                                                                                           |                       |

| 34<br>1 | LSEL0<br>RSEL0   | Input selector outputs                                                                                                                                                                                    | A12266                |

| 33<br>2 | LVRIN<br>RVRIN   | Inputs for the 2-dB step volume control     These inputs must be driven from low-impedance circuits.                                                                                                      | LVref<br>RVref        |

| 32<br>3 | LCT<br>RCT       | Loudness function pins. Connect the high-band compensation RC circuits between the LCT (RCT) and the LVRIN (RVRIN) pins and connect the low-band compensation RC circuits between the LCT (RCT) and Vref. | □ VDD A12268          |

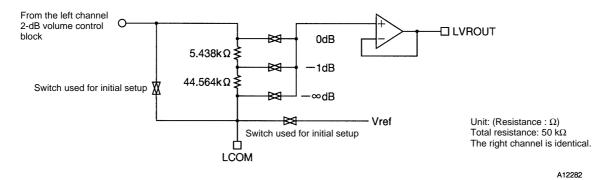

| 31<br>4 | LCOM<br>RCOM     | 2-dB step volume control outputs     To reduce switching noise, each of these pins should be connected to Vref through a capacitor.                                                                       | A12269                |

| 30<br>5 | LVROUT<br>RVROUT | Output from the 1-dB step volume control                                                                                                                                                                  | NDD A12270            |

| 29<br>6 | LTIN<br>RTIN     | Tone control circuit inputs                                                                                                                                                                               | VDD<br>A12271         |

Continued on next page.

Continued from preceding page.

| Pin No.                       | Pin                                                | Function                                                                                                                                                                                                        | Equivalent circuit |

|-------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 28<br>27<br>26<br>7<br>8<br>9 | LF1C1<br>LF1C2<br>LF1C3<br>RF1C1<br>RF1C2<br>RF1C3 | Tone control circuit low band filter capacitor connections The low band compensation capacitors must be connected between the following pins:  LF1C1 (RF1C1) and LF1C2 (RF1C2)  LF1C2 (RF1C2) and LF1C3 (RF1C3) | C2 DW LVref RVref  |

| 39<br>10                      | LF3C1<br>RF3C1                                     | Tone control circuit high band filter capacitor connections     The high band compensation capacitors must be connected between LF3C1 (RF3C1) and Vref.                                                         | C1 — W             |

| 24<br>11                      | LTOUT<br>RTOUT                                     | Tone control circuit outputs                                                                                                                                                                                    | A12274             |

| 23<br>12                      | LFIN<br>RFIN                                       | Fader block inputs     These inputs must be driven from low-impedance circuits.                                                                                                                                 | → V <sub>DD</sub>  |

| 22<br>21<br>13<br>14          | LFOUT<br>LROUT<br>RFOUT<br>RROUT                   | Fader block outputs. The front and rear outputs can be attenuated independently. The attenuation is the same in the left and right channels.                                                                    | A12276             |

| 40                            | Vref                                               | • V <sub>DD</sub> /2 voltage generator block. A capacitor with a value of about 10 μF must be inserted between Vref and AV <sub>SS</sub> (V <sub>SS</sub> ) to reduce power supply ripple.                      | LVref RVref A12277 |

| 39                            | V <sub>DD</sub>                                    | Power supply                                                                                                                                                                                                    |                    |

| 20                            | DV <sub>SS</sub>                                   | Logic system ground                                                                                                                                                                                             |                    |

| 16                            | AV <sub>SS</sub>                                   | Analog system ground                                                                                                                                                                                            |                    |

Continued on next page.

Continued from preceding page.

| Pin No.  | Pin      | Function                                                                                                                                                                                                                                  | Equivalent circuit           |

|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 15       | TIM      | Used for the zero cross circuit no-signal timer function.  If a zero cross signal does not occur between the point when data is loaded and the point when the timer times out, the data will be stored forcibly when the timer times out. | VDD                          |

| 19<br>18 | CL<br>DI | Serial data and clock inputs used for device control                                                                                                                                                                                      | <sup>o</sup> ∨ <sub>DD</sub> |

| 17       | CE       | Chip enable input. Data is written to the internal latch when this pin goes from high to low. The analog switches then operate.  Data transfers are enabled when this pin is high.                                                        | A12279                       |

#### **Internal Equivalent Circuits**

Selector Block Equivalent Circuit

#### 2-dB Step Volume Control Block Equivalent Circuit

#### 1-dB Step Volume Control Block Equivalent Circuit

### Tone Control Block Equivalent Circuit

Unit: (Resistance :  $\Omega$ )

#### Fader Volume Control Block Equivalent Circuit

A12284

If data that sets the main volume control 1-dB step circuit to  $-\infty$  is sent to the device, switches S1 and S2 will be opened (off) and switches S3 and S4 will be closed (on).

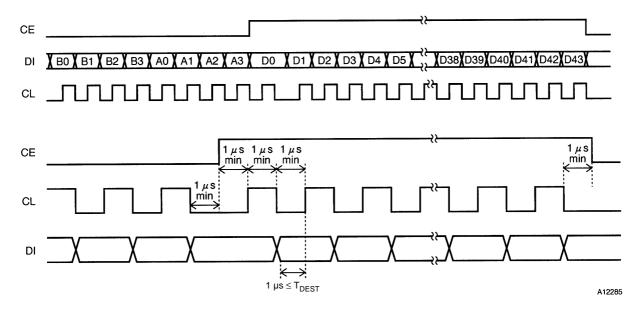

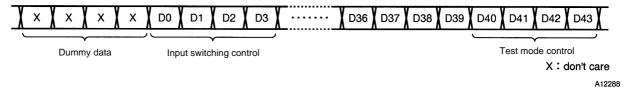

#### **Control System Timing and Data Format**

The LC75385NE-R is controlled by applying the stipulated data to the CL, DI, and CE pins. The data consists of a total of 52 bits, of which 8 bits are the device address and 44 bits are the actual control data.

#### • Address code (B0 to A3)

The LC75385NE-R has an 8-bit address code, and can be used along with other ICs that support the Sanyo CCB serial bus.

#### Address code

| (LSB) | В0 | B1 | B2 | В3 | A0 | A1 | A2 | А3 | (81HEX) |

|-------|----|----|----|----|----|----|----|----|---------|

|       | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |         |

#### • Control code allocation

#### Input switching control

| D0 | D1 | D2 |         |                                       |

|----|----|----|---------|---------------------------------------|

| 0  | 0  | 0  | L1 (R1) |                                       |

| 1  | 0  | 0  | L2 (R2) |                                       |

| 0  | 1  | 0  | L3 (R3) |                                       |

| 1  | 1  | 0  | L4 (R4) |                                       |

|    |    |    |         |                                       |

| 0  | 1  | 1  |         | IC test values. These values must not |

| 1  | 1  | 1  |         | be used during normal operation.      |

| D3 | IC test bit. This bit must be set to 0 during normal operation. |  |

|----|-----------------------------------------------------------------|--|

|----|-----------------------------------------------------------------|--|

### Input gain control

| D4 | D5 | D6 | D7 |           |

|----|----|----|----|-----------|

| 0  | 0  | 0  | 0  | 0 dB      |

| 1  | 0  | 0  | 0  | +1.25 dB  |

| 0  | 1  | 0  | 0  | +2.50 dB  |

| 1  | 1  | 0  | 0  | +3.75 dB  |

| 0  | 0  | 1  | 0  | +5.00 dB  |

| 1  | 0  | 1  | 0  | +6.25 dB  |

| 0  | 1  | 1  | 0  | +7.50 dB  |

| 1  | 1  | 1  | 0  | +8.75 dB  |

| 0  | 0  | 0  | 1  | +10.0 dB  |

| 1  | 0  | 0  | 1  | +11.25 dB |

| 0  | 1  | 0  | 1  | +12.5 dB  |

| 1  | 1  | 0  | 1  | +13.75 dB |

| 0  | 0  | 1  | 1  | +15.0 dB  |

| 1  | 0  | 1  | 1  | +16.25 dB |

| 0  | 1  | 1  | 1  | +17.5 dB  |

| 1  | 1  | 1  | 1  | +18.75 dB |

#### Volume Control

| D8 | D9 | D10 | D11 | D12 | D13 | D14 | D15 |           |

|----|----|-----|-----|-----|-----|-----|-----|-----------|

|    |    |     |     |     |     |     |     | 1 dB STEP |

| 0  |    |     |     |     |     |     |     | 0 dB      |

| 1  |    |     |     |     |     |     |     | –1 dB     |

|    |    |     |     |     |     | I   |     | 2 dB STEP |

|    | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0 dB      |

|    | 1  | 0   | 0   | 0   | 0   | 0   | 0   | –2 dB     |

|    | 0  | 1   | 0   | 0   | 0   | 0   | 0   | –4 dB     |

|    | 1  | 1   | 0   | 0   | 0   | 0   | 0   | −6 dB     |

|    | 0  | 0   | 1   | 0   | 0   | 0   | 0   | –8 dB     |

|    | 1  | 0   | 1   | 0   | 0   | 0   | 0   | -10 dB    |

|    | 0  | 1   | 1   | 0   | 0   | 0   | 0   | –12 dB    |

|    | 1  | 1   | 1   | 0   | 0   | 0   | 0   | –14 dB    |

|    | 0  | 0   | 0   | 1   | 0   | 0   | 0   | –16 dB    |

|    | 1  | 0   | 0   | 1   | 0   | 0   | 0   | –18 dB    |

|    | 0  | 1   | 0   | 1   | 0   | 0   | 0   | –20 dB    |

|    | 1  | 1   | 0   | 1   | 0   | 0   | 0   | –22 dB    |

|    | 0  | 0   | 1   | 1   | 0   | 0   | 0   | –24 dB    |

|    | 1  | 0   | 1   | 1   | 0   | 0   | 0   | –26 dB    |

|    | 0  | 1   | 1   | 1   | 0   | 0   | 0   | –28 dB    |

|    | 1  | 1   | 1   | 1   | 0   | 0   | 0   | –30 dB    |

|    | 0  | 0   | 0   | 0   | 1   | 0   | 0   | -32 dB    |

|    | 1  | 0   | 0   | 0   | 1   | 0   | 0   | –34 dB    |

|    | 0  | 1   | 0   | 0   | 1   | 0   | 0   | –36 dB    |

|    | 1  | 1   | 0   | 0   | 1   | 0   | 0   | –38 dB    |

|    | 0  | 0   | 1   | 0   | 1   | 0   | 0   | –40 dB    |

|    | 1  | 0   | 1   | 0   | 1   | 0   | 0   | –42 dB    |

|    | 0  | 1   | 1   | 0   | 1   | 0   | 0   | –44 dB    |

|    | 1  | 1   | 1   | 0   | 1   | 0   | 0   | –46 dB    |

|    | 0  | 0   | 0   | 1   | 1   | 0   | 0   | –48 dB    |

|    | 1  | 0   | 0   | 1   | 1   | 0   | 0   | –50 dB    |

|    | 0  | 1   | 0   | 1   | 1   | 0   | 0   | –52 dB    |

|    | 1  | 1   | 0   | 1   | 1   | 0   | 0   | –54 dB    |

|    | 0  | 0   | 1   | 1   | 1   | 0   | 0   | –56 dB    |

|    | 1  | 0   | 1   | 1   | 1   | 0   | 0   | –58 dB    |

|    | 0  | 1   | 1   | 1   | 1   | 0   | 0   | –60 dB    |

|    | 1  | 1   | 1   | 1   | 1   | 0   | 0   | −62 dB    |

|    | 0  | 0   | 0   | 0   | 0   | 1   | 0   | -64 dB    |

|    | 1  | 0   | 0   | 0   | 0   | 1   | 0   | –66 dB    |

|    | 0  | 1   | 0   | 0   | 0   | 1   | 0   | –68 dB    |

|    | 1  | 1   | 0   | 0   | 0   | 1   | 0   | –70 dB    |

|    | 0  | 0   | 1   | 0   | 0   | 1   | 0   | –72 dB    |

|    | 1  | 0   | 1   | 0   | 0   | 1   | 0   | –74 dB    |

|    | 0  | 1   | 1   | 0   | 0   | 1   | 0   | –76 dB    |

|    | 1  | 1   | 1   | 0   | 0   | 1   | 0   | –78 dB    |

|    |    |     | T   | T   |     |     |     | MUTE      |

|    | 1  | 1   | 1   | 1   | 1   | 1   | 0   | -∞        |

|    | 0  | 1   | 1   | 1   | 1   | 1   | 0   | INMUTE    |

#### Tone Control

| D16 | D17 | D18 | D19 | Bass   |

|-----|-----|-----|-----|--------|

| D24 | D25 | D26 | D27 | Treble |

| 0   | 1   | 1   | 0   | +12 dB |

| 1   | 0   | 1   | 0   | +10 dB |

| 0   | 0   | 1   | 0   | +8 dB  |

| 1   | 1   | 0   | 0   | +6 dB  |

| 0   | 1   | 0   | 0   | +4 dB  |

| 1   | 0   | 0   | 0   | +2 dB  |

| 0   | 0   | 0   | 0   | 0 dB   |

| 1   | 0   | 0   | 1   | –2 dB  |

| 0   | 1   | 0   | 1   | –4 dB  |

| 1   | 1   | 0   | 1   | –6 dB  |

| 0   | 0   | 1   | 1   | –8 dB  |

| 1   | 0   | 1   | 1   | –10 dB |

| 0   | 1   | 1   | 1   | –12 dB |

| D20 | D21 | D22 | D23 |                             |

|-----|-----|-----|-----|-----------------------------|

| 0   | 0   | 0   | 0   | These bits must be set to 0 |

#### Fader Volume Control

| D28 | D29 | D30 | D31 |        |

|-----|-----|-----|-----|--------|

| 0   | 0   | 0   | 0   | 0 dB   |

| 1   | 0   | 0   | 0   | -1 dB  |

| 0   | 1   | 0   | 0   | −2 dB  |

| 1   | 1   | 0   | 0   | –4 dB  |

| 0   | 0   | 1   | 0   | −6 dB  |

| 1   | 0   | 1   | 0   | –8 dB  |

| 0   | 1   | 1   | 0   | –10 dB |

| 1   | 1   | 1   | 0   | –12 dB |

| 0   | 0   | 0   | 1   | –14 dB |

| 1   | 0   | 0   | 1   | –16 dB |

| 0   | 1   | 0   | 1   | –18 dB |

| 1   | 1   | 0   | 1   | –20 dB |

| 0   | 0   | 1   | 1   | –30 dB |

| 1   | 0   | 1   | 1   | –45 dB |

| 0   | 1   | 1   | 1   | –60 dB |

| 1   | 1   | 1   | 1   | -∞     |

#### **Channel Selection Control**

| D32 | D33 |                                                            |

|-----|-----|------------------------------------------------------------|

| 0   | 0   | Left and right together. This is the mode set up initially |

| 1   | 0   | RCH                                                        |

| 0   | 1   | LCH                                                        |

| 1   | 1   | Left and right together                                    |

### Fader Rear/Front Control

| D34 |       |

|-----|-------|

| 0   | Rear  |

| 1   | Front |

### Loudness Control

| D35 |     |  |

|-----|-----|--|

| 0   | off |  |

| 1   | on  |  |

### Zero Cross Control

| D36 | D37 |                                                                                                         |

|-----|-----|---------------------------------------------------------------------------------------------------------|

| 0   | 0   | Data is written when a zero cross is detected                                                           |

| 1   | 1   | The zero cross detection operation is disabled and data is written on the falling edge of the CE signal |

## Zero Cross Signal Detection Block Control

| D38 | D39 | D40 | D41 |          |

|-----|-----|-----|-----|----------|

| 0   | 0   | 0   | 0   | Selector |

| 1   | 0   | 0   | 0   | Volume   |

| 0   | 1   | 0   | 0   | Tone     |

| 1   | 1   | 0   | 0   | Feder    |

### Test Mode Control

| D42 | D43 |                                                  |

|-----|-----|--------------------------------------------------|

| 0   | 0   | These IC test mode control bits must be set to 0 |

#### **Usage Notes**

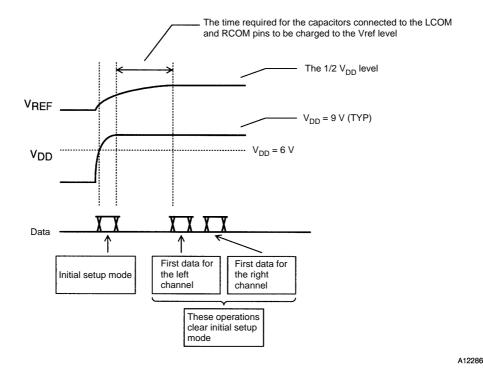

Data Transmission after Power Is First Applied

- When power is first applied, the state of the internal analog switches will be undefined. Applications that use this IC must include external circuits to provide muting until control data has been transferred to the IC.

- After power is first applied, applications should send initial setup data to stabilize the bias levels in each of the IC circuit blocks in a short time.

- 1. The time between initial setup mode and the first actual data settings

- $\bullet$  Applications should send the initial setup data as soon as  $V_{DD}$  rises above 6 V.

- After the LCOM and RCOM pins have stabilized at the Vref level, applications should send the first data settings.

- 2. Procedure for setting up initial setup mode

- When D32 and D33 are set to 00, the IC's internal initial setup switch is turned on and the IC goes to quick charge mode. At this time the other data (D0 to D31 and D34 to D43) will also be set up for the left and right channels at the same time. This means that applications can set up the states of the various blocks at the same time as specifying initial setup mode.

- 3. Procedure for clearing initial setup mode

- Initial setup mode is cleared by setting D32 and D33 to any value other than 00. In other words, any normal left or right channel specification will turn the internal initial setup switch off and clear quick charge mode.

#### Zero Cross Switching Circuit Operating Principles

• The LC75385NE-R includes a function for switching the place where the zero cross comparator operates and thus allows applications to select the optimal detection location for the block for which the control data is updated. Basically, switching noise will be minimized if the signal immediately following the block for which the control data is updated is input to the zero cross comparator. Thus the detection location must be changed for each data update operation. Another issue is the point that if the signal amplitude is lower than the detection sensitivity (a few mV rms) of the zero cross comparator (for example if the volume is set to a low level), the switching noise can be minimized further by selecting a point before the volume control block, namely the selector block output, as the zero cross detection point than by simply waiting for the data write to occur due to the overflow of the zero cross timer. For example, if the volume block input is 1 V rms, and the volume is set to –40 dB or lower, the output will be under 10 mV rms. In this case, detecting at the selector output block will result in lower switching noise.

**Zero Cross Detection Circuit**

#### Zero Cross Switching Control Procedure

• The zero cross switching control procedure consists of first setting the zero cross detection mode with the zero cross control bits (D36 and D37 = 0) and then, after specifying the detection block (with bits D38, D39, D40, and D41), sending the control data. Since these control bits are latched first immediately after the data is sent, i.e. on the falling edge of the CE signal, it is possible to both set the IC mode as well as specify zero cross switching operation in a single data transfer, even when updating the volume and other data. The following presents an example of the control operation when updating the volume block data.

| D36        | D37       | D38 | D39       | D40         | D41 |

|------------|-----------|-----|-----------|-------------|-----|

| 0          | 0         | 1   | 0         | 0           | 0   |

| Zero cross | detection |     | Volume bl | ock setting |     |

#### Zero Cross Timer Setting

• When the input signal has a level lower than the sensitivity of the zero cross comparator, or consists only of extremely low frequencies, the zero cross detection circuit will remain in the state in which it cannot detect a zero cross and the data will not be latched during that period. The zero cross timer specifies a time after which the data will be latched forcibly in states where a zero crossing cannot be detected. The time is determined by the lowest frequency for which a zero cross can be detected reliably.

For example, if the timer is set to 25 ms:

$$T = 0.69 CR$$

If C is taken to be 0.033 µF, then R will be:

$$R = \frac{25 \times 10^{-3}}{0.69 \times 0.033 \times 10^{-6}} \approx 1.1 \text{ M}\Omega$$

Notes on Serial Data Transfer

- The CL, DI, and CE pin signal lines must be covered (and thus shielded) by the ground pattern or formed from shielded cable to prevent the high-frequency digital signals on those lines from entering the analog system.

- The LC75385NE-R data format consists of 8 bits of address and 44 bits of data. When the data is sent in units of 8 bits each (i.e. 48 bits are actually sent), use the data transfer technique shown in figure 1.

LC75385NE-R data reception in 8-bit units

• During CCB transfers, this IC detects address matches on the rising edge of the CE signal. Therefore, applications must set the CL signal low and then set it high at this time.

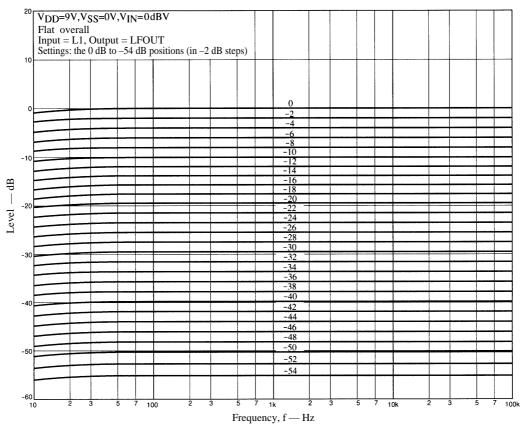

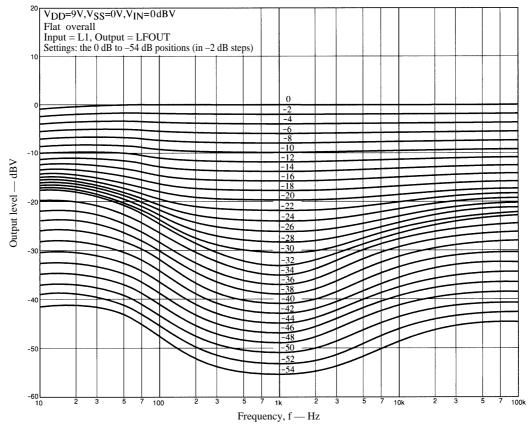

#### **Output Level Characteristics**

#### **Loudness Characteristics**

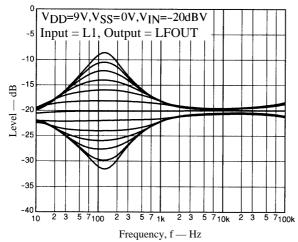

#### **Bass Control Characteristics**

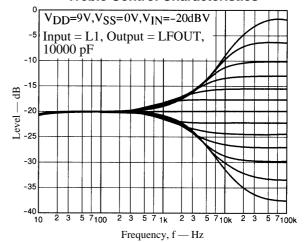

#### **Treble Control Characteristics**

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of April, 1999. Specifications and information herein are subject to change without notice.