Features

# Complete 10µs CMOS 12-Bit ADC

#### **General Description**

The MAX172 is a complete 12-Bit analog-to-digital converter (ADC) that combines high speed, low power consumption, and an on-chip voltage reference. The conversion time is 10µs. The buried zener reference provides low drift and low noise performance.

External component requirements are limited to only decoupling capacitors for the power supply and reference voltages. On-chip clock circuitry is also included which can either be driven from an external source, or in stand-alone applications, can be used with a crystal.

The MAX172 uses a standard microprocessor interface architecture. Three-state data outputs are controlled by Read (RD) and Chip Select (CS) inputs. Data access and bus release times of 90 and 75ns respectively ensure compatibility with most popular microprocessors without resorting to wait states.

### **Applications**

Digital Signal Processing (DSP) High Accuracy Process Control High Speed Data Acquisition Electro-Mechanical Systems

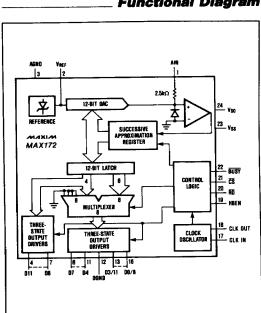

### Functional Diagram

● 12-Bit Resolution and Linearity

- ♦ 10µs Conversion Time

- No Missing Codes

- On-Chip Voltage Reference

- 90ns Access Time

- 215mW Max Power Consumption

- 24-Lead Narrow DIP Package

- Pin-for-Pin AD7572 Replacement

### **Ordering Information**

| PART       | TEMP. RANGE     | PACKAGE*    | ERROR  |

|------------|-----------------|-------------|--------|

| MAX172ACNG | 0°C to +70°C    | Plastic DIP | ±½ LSB |

| MAX172BCNG | 0°C to +70°C    | Plastic DIP | ±1 LSB |

| MAX172ACWG | 0°C to +70°C    | Wide S.O.   | ±½ LSB |

| MAX172BCWG | 0°C to +70°C    | Wide S.O.   | ±1 LSB |

| MAX172CC/D | 0°C to +70°C    | Dice**      | ±1 LSB |

| MAX172AING | -25°C to +85°C  | Plastic DIP | ±½ LSB |

| MAX172BING | -25°C to +85°C  | Plastic DIP | ±1 LSB |

| MAX172AMRG | -55°C to +125°C | CERDIP      | ±½ LSB |

| MAX172BMRG | -55°C to +125°C | CERDIP      | ±1 LSB |

- \* All devices 24 lead packages

- \*\* Consult factory for dice specifications

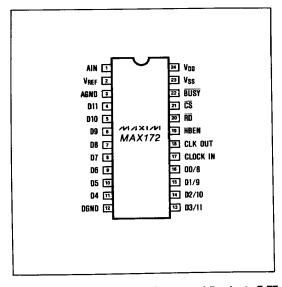

# Pin Configuration

Maxim Integrated Products 7-77

MAXIM is a registered trademark of Maxim Integrated Products.

NINXINI

7

# Complete 10µs CMOS 12-Bit ADC

#### **ABSOLUTE MAXIMUM RATINGS**

| $\begin{array}{llllllllllllllllllllllllllllllllllll$ | Operating Temperature Ranges         0°C to +70°C           MAX172XC         0°C to +85°C           MAX172XI         -25°C to +85°C           MAX172XM         -55°C to +125°C           Storage Temperature Range         -65°C to +160°C           Power Dissipation (any Package) to +75°C         100mW/°C           Derates Above +75°C by         10mW/°C           Lead Temperature (Soldering 10 seconds)         +300°C |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (pins 4-11, 13-10, 16, 22)                           | Lead Temperature (Soldering 10 seconds) +300°C                                                                                                                                                                                                                                                                                                                                                                                   |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(V<sub>DD</sub> = +5V ± 5%, V<sub>SS</sub> = -12V or -15V ± 5%; Slow Memory Mode; T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub> unless otherwise noted, f<sub>CLK</sub> = 1.25MHz.)

| PARAMETER                                     | SYMBOL           | CONDITIONS                                         |                                                                                | MIN  | TYP   | MAX                | UNITS  |

|-----------------------------------------------|------------------|----------------------------------------------------|--------------------------------------------------------------------------------|------|-------|--------------------|--------|

| ACCURACY ,                                    |                  |                                                    |                                                                                |      |       |                    |        |

| Resolution                                    |                  |                                                    | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                         | 12   | -     |                    | Bits   |

|                                               |                  | MAX172A                                            | T <sub>A</sub> = 25°C                                                          |      |       | ±1/2               | 1      |

| Integral NonLinearity                         | INL              | MAX172AC/AI<br>MAX172AM<br>MAX172B                 |                                                                                |      |       | ±1/2<br>±3/4<br>±1 | LSB    |

| Differential NonLinearity                     | DNL              | Guaranteed Monot                                   | onic Over Temp.                                                                |      |       | ±1                 | LSB    |

| 0,                                            |                  | MAX172B                                            | T <sub>A</sub> = 25°C<br>T <sub>A</sub> = T <sub>MIN</sub> to T <sub>MAX</sub> |      |       | ±4<br>±6           | 1.00   |

| Offset Error (Note 1)                         |                  | MAX172A                                            | T <sub>A</sub> = 25°C<br>T <sub>A</sub> = T <sub>MIN</sub> to T <sub>MAX</sub> |      |       | ±3<br>±4           | LSB    |

| Full Scale Error (Note 2)                     |                  | MAX172B                                            | T <sub>A</sub> = 25°C                                                          |      |       | ±15                | LSB    |

| Tuir Scale Error (Note 2)                     |                  | MAX172A                                            | T <sub>A</sub> = 25°C                                                          | 1    |       | ±10                |        |

| Full Scale Tempco (Notes 3, 4)                |                  |                                                    |                                                                                |      |       | ±45                | ppm/°( |

| ANALOG INPUT                                  |                  |                                                    |                                                                                | •    |       |                    | •      |

| Input Voltage Range                           |                  |                                                    |                                                                                | 0    |       | 5                  | V      |

| Input Current                                 |                  | AIN = 0V to +5V                                    |                                                                                |      |       | 3.5                | mA     |

| INTERNAL REFERENCE                            |                  |                                                    |                                                                                |      |       |                    |        |

| V <sub>REF</sub> Output Voltage               |                  | T <sub>A</sub> = 25°C                              |                                                                                | -5.2 | -5.25 | -5.3               | V      |

| V <sub>REF</sub> Output Tempco (Note 5)       |                  |                                                    |                                                                                |      | 40    |                    | ppm/°  |

| Output Current Sink Capability                |                  | (Note 6)                                           |                                                                                |      |       | 500                | μΑ     |

| LOGIC INPUTS                                  |                  |                                                    |                                                                                |      |       |                    |        |

| Input Low Voltage                             | V <sub>IL</sub>  | CS, RD, HBEN, CL                                   | KIN                                                                            |      |       | 0.8                | V      |

| Input High Voltage                            | V <sub>iH</sub>  | CS, RD, HBEN, CL                                   | KIN                                                                            | 2.4  |       |                    | V      |

| Input Capacitance (Note 7)                    | C <sub>IN</sub>  | CS, RD, HBEN, CLKIN                                |                                                                                |      |       | 10                 | pF     |

| Input Current                                 | I <sub>IN</sub>  | CS, RD, HBEN<br>CLKIN                              | VIN = 0 to V <sub>DI</sub>                                                     | )    |       | ±10<br>±20         | μΑ     |

| LOGIC OUTPUTS                                 |                  |                                                    |                                                                                |      |       |                    |        |

| Output Low Voltage                            | V <sub>OL</sub>  | D11-D0/8, BUSY, C                                  | LKOUT I <sub>SINK</sub> = 1.6mA                                                |      |       | 0.4                | l v    |

| Output High Voltage                           | V <sub>OH</sub>  | D11-D0/8, BUSY, CLKOUT I <sub>SOURCE</sub> = 200µA |                                                                                |      |       |                    | V      |

| Floating State Leakage<br>Current             | I <sub>LKG</sub> | D11-D0/8, V <sub>OUT</sub> = 0V to V <sub>DD</sub> |                                                                                |      |       | ±10                | μΑ     |

| Floating State Output<br>Capacitance (Note 7) | Соит             |                                                    |                                                                                |      |       | 15                 | pF     |

| Capacitance (Note 7)                          | 001              |                                                    |                                                                                |      |       | 44 41              |        |

# Complete 10µs CMOS 12-Bit ADC

**ELECTRICAL CHARACTERISTICS (Continued)**

$(V_{DD} = +5V \pm 5\%, V_{SS} = -12V \text{ or } -15V \pm 5\%$ ; Slow Memory Mode;  $T_A = T_{MIN}$  to  $T_{MAX}$  unless otherwise noted,  $f_{CLK} = 1.25MHz$ .)

| PARAMETER                            | SYMBOL            | CONDITIONS                                                           | MIN | TYP       | MAX        | UNITS |

|--------------------------------------|-------------------|----------------------------------------------------------------------|-----|-----------|------------|-------|

| CONVERSION TIME                      |                   |                                                                      |     |           |            |       |

| MAX172                               | t <sub>CONV</sub> | Synchronous (12.5 clock cycles) Asynchronous (12 to 13 clock cycles) | 9.6 |           | 10<br>10.4 | μs    |

| POWER SUPPLY REJECT                  | ION               |                                                                      |     |           |            |       |

| V <sub>DD</sub> Only                 |                   | FS Change, V <sub>SS</sub> = -15V, V <sub>DD</sub> = 4.75V to 5.25V  |     | ±1/2      |            | LSB   |

| V <sub>SS</sub> Only                 |                   | FS Change, V <sub>DD</sub> = 5V, V <sub>SS</sub> = -5% to +5%        |     | ±1/8      |            | LSB   |

| POWER REQUIREMENTS                   | <b>S</b>          |                                                                      |     |           |            |       |

|                                      |                   | ±5% for Specified Performance                                        |     | 5         |            |       |

| V <sub>DD</sub>                      |                   | ±5% for Specified Performance                                        |     | -12 or -1 | 5          |       |

| V <sub>SS</sub> (Note 8)             |                   | CS = RD = V <sub>DD</sub> , AIN = 5V                                 |     | 5         | 7          | mA    |

| DD ·                                 | <del></del>       | CS = RD = V <sub>DD</sub> , AIN = 5V                                 |     | 8         | 12         | mA    |

| 1 <sub>SS</sub><br>Power Dissipation |                   | V <sub>DD</sub> = +5V, V <sub>SS</sub> = -15V                        |     | 145       | 215        | mW    |

Note 1: Typical change over temp is  $\pm 1$  LSB.

Note 2:  $V_{DD}$  = +5V,  $V_{SS}$  = -15V, FS = +5.000V, Ideal last code transition = FS - 3/2LSB. Note 3: Full Scale TC =  $\Delta$ FS/ $\Delta$ T, where  $\Delta$ FS is full scale change from  $T_A$  = 25°C to  $T_{MIN}$  or  $T_{MAX}$ .

Note 4: Includes internal reference drift.

Note 5:  $V_{REF}$  TC =  $\Delta V_{REF}/\Delta T$ , where  $\Delta V_{REF}$  is reference voltage change from  $T_A$  = 25°C to  $T_{MIN}$  or  $T_{MAX}$ . Note 6: Output current should not change during conversion.

Note 7: Guaranteed by design, not subject to test.

Note 8: Functional operation at  $V_{SS}$  = -12V  $\pm$  5% is guaranteed by testing offset error and full scale error.

## TIMING CHARACTERISTICS (Note 9)

$(V_{DD} = +5V, V_{SS} = -12V \text{ or } -15V; T_A = T_{MIN} \text{ to } T_{MAX} \text{ unless otherwise noted.})$

|                                         | SYMBOL          | CONDITIONS                                      | T <sub>A</sub> = 25°C |          | MAX172C/I |                | MAX172M    |                | UNITS      |          |

|-----------------------------------------|-----------------|-------------------------------------------------|-----------------------|----------|-----------|----------------|------------|----------------|------------|----------|

| PARAMETER                               |                 |                                                 | MIN                   | TYP      | MAX       | MIN            | MAX        | MIN            | MAX        | 00       |

| CS to RD Setup Time                     | t,              |                                                 | 0                     |          |           | 0              |            | 0              |            | ns       |

| RD to BUSY Delay                        | 12              | C <sub>1</sub> = 50pF                           |                       | 90       | 190       |                | 230        |                | 270        | ns       |

| Data Access Time (Note 10)              | t <sub>3</sub>  | C <sub>L</sub> = 20pF<br>C <sub>L</sub> = 100pF |                       | 60<br>70 | 90<br>125 |                | 110<br>150 |                | 120<br>170 | ns       |

| RD Pulse Width                          | t <sub>4</sub>  |                                                 | t <sub>3</sub>        |          |           | t <sub>3</sub> |            | t <sub>3</sub> |            | <u> </u> |

| CS to RD Hold Time                      | t <sub>5</sub>  |                                                 | 0                     |          |           | 0              |            | 0              |            | ns       |

| Data Setup Time After BUSY<br>Note (10) | t <sub>6</sub>  |                                                 |                       |          | 70        |                | 90         |                | 100        | ns       |

| Bus Relinquish Time (Note 11)           | t <sub>7</sub>  |                                                 | 20                    |          | 75        | 20             | 85         | 20             | 90         | ns       |

| HBEN to RD Setup Time                   | t <sub>B</sub>  |                                                 | 0                     |          |           | 0              |            | 0              |            | ns       |

| HBEN to RD Hold Time                    | t <sub>9</sub>  |                                                 | 0                     |          |           | 0              |            | 0              |            | ns       |

| Delay Between Read Operations           | t <sub>10</sub> |                                                 | 200                   |          |           | 200            |            | 200            |            | ns       |

Timing specifications are sample tested at 25°C to ensure compliance. All input control signals are specified with Note 9:  $t_r = t_t = 5$ ns (10% to 90% of +5V) and timed from a voltage level of +1.6V.

$t_3$  and  $t_6$  are measured with the load circuits of Figure 1 and defined as the time required for an output to cross 0.8V or 2.4V. Note 10:

Note 11:  $t_7$  is defined as the time required for the data lines to change 0.5V when loaded with the circuits of Figure 2.

# For additional information on using the MAX172 please refer to MAX162 data sheet.

|          | 7-79 |

|----------|------|

| /VIXI/VI | 1-13 |

# Complete 10µs CMOS 12-Bit ADC

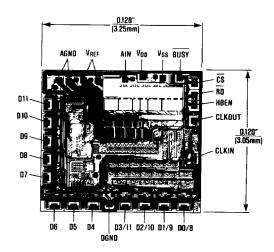

### Chip Topography

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

7-80\_\_\_\_\_\_\_MAXIM