# 27C210 1M (64K x 16) CHMOS EPROM

- JEDEC Approved EPROM Pinouts

- 40-Pin DIP

- 44-Pin PLCC

- **■** Complete Upgrade to Higher Densities

- Versatile EPROM Features

- CMOS and TTL Compatibility

- Two Line Control

- **■** High-Performance

- 120 ns ± 10% V<sub>CC</sub>

- 50 mA I<sub>CC</sub> Active

- **■** Fast Programming

- Quick-Pulse Programming™ Algorithm

- Programming Times As Fast As 8 Seconds

Intel's 27C210 is a 5V only, 1,048,576-bit Erasable Programmable Read Only Memory, organized as 65,536 words of 16 bits each. Its standard pinouts provide for simple upgrades to 4 Mbits in the future.

The 27C210 represents state-of-the-art 1 micron CMOS manufacturing technology while providing unequaled performance. Its 120 ns speed (t<sub>ACC</sub>) offers no-wait-state operation with high performance CPUs in applications ranging from numerical control to office automation to telecommunications.

Intel offers two DIP profile options to meet your prototyping and production needs. The windowed ceramic dip (CERDIP) package provides erasability and reprogrammability for prototyping and early production. Once the design is in full production, the plastic dip (PDIP) one-time programmable part provides a lower cost alternative that is well adapted for auto insertion.

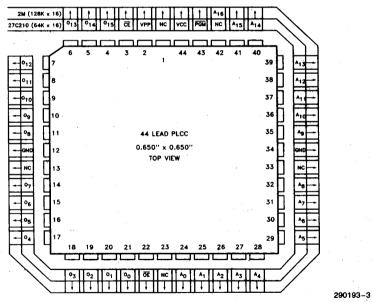

In addition to the JEDEC 40-pin DIP package, Intel also offers a 44-lead PLCC version of the 27C210. This one-time-programmable surface mount device is ideal where board space consumption is a major concern or where surface mount manufacturing technology is being implemented across an entire production line.

The 27C210 is equally at home in both a TTL or CMOS environment. And like Intel's other 1 Mbit EPROMs, the 27C210 programs quickly using Intel's industry leading Quick-Pulse Programming algorithm.

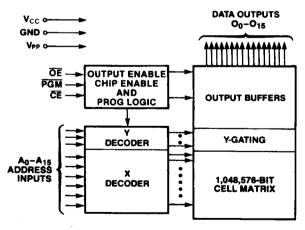

Figure 1. Block Diagram

September 1990 Order Number: 290193-003

290193-1

### Pin Names

| A0-A17                          | ADDRESSES           |

|---------------------------------|---------------------|

| CE                              | CHIP ENABLE         |

| ŌĒ                              | OUTPUT ENABLE       |

| O <sub>0</sub> -O <sub>15</sub> | OUTPUTS             |

| PGM                             | PROGRAM             |

| NC                              | NO INTERNAL CONNECT |

| 4M                | 2M              | 270                    | 27C210              |                 | 4M              |

|-------------------|-----------------|------------------------|---------------------|-----------------|-----------------|

| Vpp               | Vpp             | VPP 1                  | 40 VCC              | Vcc             | Voc             |

| CE -              | CE              | ₹ 🗖 2                  | 39 🗖 PGM            | PGM             | A <sub>17</sub> |

| O <sub>15</sub>   | O <sub>15</sub> | 0 <sub>15</sub> ☐ 3    | 38 E NC             | A <sub>16</sub> | A <sub>16</sub> |

| 014               | - 014           | 014 4                  | 37 E A15            | A <sub>15</sub> | A <sub>15</sub> |

| O <sub>13</sub>   | 013             | 013 5                  | 36 5 414            | A <sub>14</sub> | A14             |

| Q <sub>12</sub> . | 012             | 012 6                  | 35 A13              | A <sub>13</sub> | A <sub>13</sub> |

| 011               | 011             | 0110 7                 | 346 412             | A <sub>12</sub> | A12             |

| O <sub>10</sub>   | O <sub>10</sub> | 010 <b>□ 8</b>         | 33 🗖 🗛 11           | A <sub>11</sub> | A <sub>11</sub> |

| Og                | O <sub>9</sub>  | ° ₽ ₽                  | 32 A10              | A <sub>10</sub> | Ato             |

| O <sub>8</sub>    | O <sub>8</sub>  | <b>08</b> ☐ 10         | 31 🗖 🗛              | Ag              | Ag              |

| GND               | GND             | GND = 11               | 30 GND              | GND.            | GNE             |

| 07                | 07              | 07 🗀 12                | 29 - 18             | As              | As              |

| O <sub>6</sub>    | 06              | <b>06 ☐</b> 13         | 28 - ^7             | A7              | A7              |

| 05                | O <sub>5</sub>  | <sup>0</sup> 5 □ 14    | 27 🗀 👫              | A <sub>6</sub>  | A6              |

| 04                | 04              | °4 <b>□</b> 15         | 26 🗖 <sup>4</sup> 5 | A <sub>5</sub>  | A <sub>5</sub>  |

| $O_3$             | O₃              | °3 ☐ 16                | 25 🗖 🗛              | A4              | A4              |

| O2                | O <sub>2</sub>  | O2 🗖 17                | 24 🗖 ^3             | A <sub>3</sub>  | A <sub>3</sub>  |

| O <sub>1</sub>    | 91              | 01 <b>□</b> 18         | 23 1 1/2            | A <sub>2</sub>  | A <sub>2</sub>  |

| O <sub>0</sub>    | 00              | 00 td 19               | 22 🗖 🐴              | A <sub>1</sub>  | A <sub>1</sub>  |

| Œ                 | QE              | <b>Ō</b> Ē <b>□</b> 20 | 21 🗖 🗛              | Ao              | A <sub>0</sub>  |

Figure 2. DIP Pin Configuration

Figure 3. PLCC Lead Configuration

V<sub>CC</sub> Supply Voltage

#### **ABSOLUTE MAXIMUM RATINGS\***

| Operating Temperature                                                                                       | 0°C to 70°C(1)    |

|-------------------------------------------------------------------------------------------------------------|-------------------|

| Temperature Under Bias                                                                                      | 10°C to 80°C      |

| Storage Temperature                                                                                         | 65°C to 125°C     |

| Voltage on Any Pin<br>(except A <sub>9</sub> , V <sub>CC</sub> and V <sub>PP</sub> )<br>with Respect to GND | 0.6V to 6.5V(2,8) |

| Voltage on A <sub>9</sub> with Respect to GND                                                               | 0.6V to 13.0V(2)  |

| V <sub>PP</sub> Program Voltage with Respect to GND                                                         | 0.6V to 14V(2)    |

with Respect to GND ..... -0.6V to 7,0V(2)

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

Notice: Specifications contained within the following tables are subject to change.

## READ OPERATION DC CHARACTERISTICS(1) V<sub>CC</sub> = 5.0V ± 10%

| Symbol          | Parameter                            | Notes | Min                   | Тур  | Max                   | Unit | Test Condition                                             |

|-----------------|--------------------------------------|-------|-----------------------|------|-----------------------|------|------------------------------------------------------------|

| I <sub>LI</sub> | Input Load Current                   | 7     | •                     | 0.01 | 1.0                   | μΑ   | V <sub>IN</sub> = 0V to V <sub>CC</sub>                    |

| llo             | Output Leakage Current               | 11.5  | 1 : 1 d               |      | ±10                   | μΑ   | V <sub>OUT</sub> = 0V to V <sub>CC</sub>                   |

| I <sub>SB</sub> | V <sub>CC</sub> Standby Current      |       |                       |      | 1.0                   | mA   | CE = VIH                                                   |

|                 |                                      |       |                       |      | 100                   | μΑ   | CE = V <sub>CC</sub> ±0.2V                                 |

| lcc             | V <sub>CC</sub> Operating<br>Current | 3     |                       |      | 50                    | mA   | CE = V <sub>IL</sub><br>f = 5 MHz, I <sub>OUT</sub> = 0 mA |

| I <sub>PP</sub> | V <sub>PP</sub> Operating Current    | 3     |                       |      | 10                    | μΑ   | $V_{PP} = V_{CC}$                                          |

| los             | Output Short<br>Circuit Current      | 4, 6  |                       |      | 100                   | mA   |                                                            |

| V <sub>IL</sub> | Input Low Voltage                    |       | -0.5                  |      | 0.8                   | ٧    |                                                            |

| V <sub>IH</sub> | Input High Voltage                   |       | 2.0                   |      | V <sub>CC</sub> + 0.5 | V    |                                                            |

| V <sub>OL</sub> | Output Low Voltage                   |       |                       |      | 0.45                  | ٧    | I <sub>OL</sub> = 2.1 mA                                   |

| V <sub>OH</sub> | Output High Voltage                  |       | 2.4                   |      |                       | V    | $I_{OH} = -400 \mu\text{A}$                                |

| V <sub>PP</sub> | V <sub>PP</sub> Operating Voltage    | 5     | V <sub>CC</sub> - 0.7 |      | Vcc                   | ٧    |                                                            |

#### NOTES:

- 1. Operating temperature is for commercial product defined by this specification.

- 2. Minimum DC voltage is -0.5V on input/output pins. During transitions, this level may undershoot to -2.0V for periods <20 ns. Maximum DC voltage on input/output pins is V<sub>CC</sub> + 0.5V which during transitions, may overshoot to V<sub>CC</sub> + 2.0V for periods <20 ns.

- 3. Maximum active power usage is the sum Ipp + I<sub>CC</sub>. Maximum current value is with outputs O<sub>0</sub> to O<sub>15</sub> unloaded.

- 4. Output shorted for no more than one second. No more than one output shorted at a time.

- 5. V<sub>PP</sub> may be connected directly to V<sub>CC</sub>, or may be one diode voltage drop below V<sub>CC</sub>. V<sub>CC</sub> must be applied simultaneously or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>.

- 6. Sampled, not 100% tested.

- 7. Typical limits are at  $V_{CC} = 5V$ ,  $T_A = 25$ °C.

- 8. Absolute Maximum ratings apply to NC pins.

## READ OPERATION AC CHARACTERISTICS(1) VCC = 5.0V ±10%

|                 | Versions <sup>(4)</sup>                                             |        | ± 10% | 27C210-120V10 |     | 27C210-150V10<br>P27C210-150V10<br>N27C210-150V10 |     | 27C210-200V10<br>P27C210-200V10<br>N27C210-200V10 |     | Unit |

|-----------------|---------------------------------------------------------------------|--------|-------|---------------|-----|---------------------------------------------------|-----|---------------------------------------------------|-----|------|

| Symbol          | Parameter                                                           |        | Notes | Min           | Max | Min                                               | Max | Min                                               | Max |      |

| tACC            | Address to Output D                                                 | elay   |       | •             | 120 |                                                   | 150 |                                                   | 200 | ns   |

| t <sub>CE</sub> | CE to Output Delay                                                  |        | 2     |               | 120 |                                                   | 150 |                                                   | 200 | ns   |

| <sup>t</sup> OE | OE to Output Delay                                                  |        | 2     |               | 55  |                                                   | 60  |                                                   | 70  | ns   |

| t <sub>DF</sub> | OE High to Output H                                                 | ligh Z | 3     |               | 30  |                                                   | 50  |                                                   | 60  | ns   |

| <sup>t</sup> ОН | Output Hold from<br>Addresses, CE or Oi<br>Change—Whicheve<br>First |        | 3     | 0             |     | 0                                                 |     | 0                                                 |     | ns   |

#### NOTES:

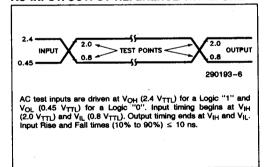

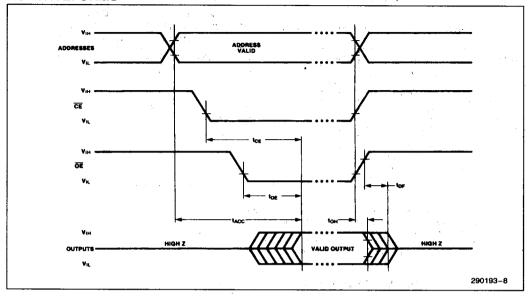

- 1. See AC Input/Output Reference Waveform for timing measurements.

- 2. OE may be delayed up to t<sub>CE</sub>-t<sub>OE</sub> after the falling edge of CE without impact on t<sub>CE</sub>.

- 3. Sampled, not 100% tested.

- 4. Model Number Prefixes: no prefix = CERDIP, P = PDIP, N = PLCC.

- 5. Typical limits are set for T<sub>A</sub> = 25°C and nominal supply voltages.

## CAPACITANCE(3) TA = 25°C, f = 1 MHz

| Symbol | Parameter                   | Typ(5) | Max | Unit | Conditions            |

|--------|-----------------------------|--------|-----|------|-----------------------|

| CIN    | Input Capacitance           | 4      | 8   | pF   | $V_{IN} = 0V$         |

| Cout   | Output Capacitance          | 8      | 12  | pF   | V <sub>OUT</sub> ≈ 0V |

| Сурр   | V <sub>PP</sub> Capacitance | 18     | 25  | pF   | $V_{PP} = 0V$         |

### AC INPUT/OUTPUT REFERENCE WAVEFORM

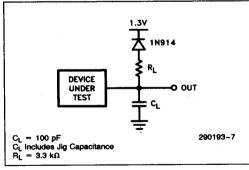

## **AC TESTING LOAD CIRCUIT**

## **AC WAVEFORMS**

## **DEVICE OPERATION**

The Mode Selection table lists 27C210 operating modes. Read Mode requires a single 5V power supply. All inputs, except V<sub>CC</sub> and V<sub>PP</sub>, and A<sub>9</sub> during inteligent Identifier Mode, are TTL or CMOS.

Table 1. Mode Selection

|                         |              |       | 12213 11 110 00 00 100 00 11 |                 |                 |                 |                 | *               |                 |                  |

|-------------------------|--------------|-------|------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|

|                         | Mode         | Notes | CE                           | ŌĒ              | PGM             | Ag              | A <sub>0</sub>  | V <sub>PP</sub> | Vcc             | Outputs          |

| Read                    |              | 1     | V <sub>IL</sub>              | V <sub>IL</sub> | ×               | Х               | Х               | Vcc             | Vcc             | D <sub>OUT</sub> |

| Output Disa             | able         |       | V <sub>IL</sub>              | V <sub>IH</sub> | X               | Х               | X               | Vcc             | Vcc             | High Z           |

| Standby                 |              |       | V <sub>IH</sub>              | Х               | X               | Х               | Х               | V <sub>CC</sub> | V <sub>CC</sub> | High Z           |

| Program                 |              | 2     | V <sub>IL</sub>              | VIH             | VIL             | Х               | Х               | V <sub>PP</sub> | V <sub>CP</sub> | D <sub>IN</sub>  |

| Program Vo              | erify        |       | V <sub>IL</sub>              | V <sub>IL</sub> | V <sub>iH</sub> | Х               | X               | V <sub>PP</sub> | V <sub>CP</sub> | D <sub>OUT</sub> |

| Program In              | hibit        |       | V <sub>IH</sub>              | Х               | ×               | Х               | X               | V <sub>PP</sub> | V <sub>CP</sub> | High Z           |

| int <sub>e</sub> ligent | Manufacturer | 2, 3  | V <sub>I</sub> L             | V <sub>IL</sub> | ×               | V <sub>ID</sub> | V <sub>IL</sub> | Vcc             | V <sub>CC</sub> | 0089 H           |

| Identifier              | Device       | ,     | V <sub>IL</sub>              | V <sub>IL</sub> | Х               | V <sub>ID</sub> | V <sub>IH</sub> | Vcc             | Vcc             | 11EEH            |

### NOTES:

X can be V<sub>IL</sub> or V<sub>IH</sub>

See DC Programming Characteristics for V<sub>CP</sub>, V<sub>PP</sub> and V<sub>ID</sub> voltages.

3.  $A_1 - A_8$ ,  $A_{10} - A_{15} = V_{IL}$

# 5

### Read Mode

The 27C210 has two control functions; both must be enabled to obtain data at the outputs.  $\overline{CE}$  is the power control and device select.  $\overline{OE}$  controls the output buffers to gate data to the outputs. With addresses stable, the address access time ( $t_{ACC}$ ) equals the delay from  $\overline{CE}$  to output ( $t_{\overline{CE}}$ ). Outputs display valid data  $t_{OE}$  after  $\overline{OE}$ 's falling edge, assuming  $t_{ACC}$  and  $t_{CE}$  times are met.

V<sub>CC</sub> must be applied simultaneously or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>.

## **Two Line Output Control**

EPROMs are often used in larger memory arrays. Intel provides two control inputs to accommodate multiple memory connections. Two-line control provides for:

- a) lowest possible memory power dissipation

- b) complete assurance that data bus contention will not occur

To efficiently use these two control inputs, an address decoder should enable  $\overline{CE}$ , while  $\overline{OE}$  should be connected to all memory devices and the system's  $\overline{READ}$  control line. This assures that only selected memory devices have active outputs while deselected memory devices are in Standby Mode.

## Standby Mode

Standby Mode substantially reduces  $V_{CC}$  current. When  $\overline{CE}=V_{IH}$ , the outputs are in a high impedance state, independent of  $\overline{OE}$ .

#### Program Mode

Caution: Exceeding 14V on V<sub>PP</sub> will permanently damage the device.

Initially, and after each erasure, all EPROM bits are in the "1" state. Data is introduced by selectively programming "0s" into the desired bit locations. Although only "0s" are programmed, the data word can contain both "1s" and "0s". Ultraviolet light erasure is the only way to change "0s" to "1s".

Program Mode is entered when  $V_{PP}$  is raised to 12.75V. Data is introduced by applying a 16-bit word to the output pins. Pulsing  $\overline{PGM}$  low while  $\overline{CE} = V_{IL}$  and  $\overline{OE} = V_{IH}$  programs that data into the device.

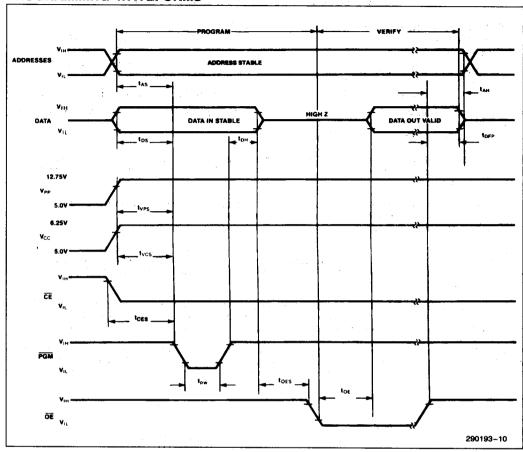

## **Program Verify**

A verify should be performed following a program operation to determine that bits have been correctly programmed. With  $V_{CC}$  at 6.25V, a substantial program margin is ensured. The verify is performed with  $\overline{CE}$  at  $\overline{V_{IL}}$  and  $\overline{PGM}$  at  $\overline{V}_{IH}$ . Valid data is available  $t_{OE}$  after  $\overline{OE}$  falls low.

## Program Inhibit

Program Inhibit Mode allows parallel programming of multiple EPROMs with different data. CE-high inhibits programming of non-targeted devices. Except for CE, parallel EPROMs may have common inputs.

## inteligent Identifier™ Mode

The inteligent Identifier Mode will determine an EPROM's manufacturer and device type, allowing programming equipment to automatically match a device with it's proper programming algorithm.

This mode is activated when a programmer forces  $12V \pm 0.5V$  on  $A_9$ . With  $\overline{CE}$ ,  $\overline{OE}$ ,  $A_1-A_8$ , and  $A_{10}-A_{15}$  at  $V_{IL}$ ,  $A_0 = V_{IL}$  will present the manufacturer code and  $A_0 = V_{IH}$  the device code. This mode functions in the  $25^{\circ}C$  ambient temperature range required during programming.

#### **UPGRADE PATH**

Future upgrades to 2 Mbit and 4 Mbit densities are easily accomplished due to the standardized pin configuration of the 27C210. When the 27C210 is in Read Mode, the  $\overline{PGM}$  input becomes non-functional. The  $\overline{PGM}$  and NC pins may be  $V_{IL}$  and  $V_{IH}$ . This allows address lines  $A_{16}-A_{17}$  to be routed directly to these inputs in anticipation of future density upgrades. Systems designed for 1 Mbit program memories today can be upgraded to higher densities (2 Mbit and 4 Mbit) in the future with no circuit board changes.

## SYSTEM CONSIDERATIONS

EPROM power switching characteristics require careful device decoupling. System designers are interested in 3 supply current issues: standby current levels (ISB), active current levels (ICC), and transient current peaks produced by falling and rising edges of CE. Transient current magnitudes depend on the device output's capacitive and inductive loading. Two-line control and proper decoupling capacitor selection will suppress transient voltage peaks. Each device should have a 0.1 µF ceramic capacitor connected between its VCC and GND. This high frequency, low inherent-inductance capacitor should be placed as close as possible to the device. Additionally, for every 8 devices, a 4.7 µF electrolytic capacitor should be placed at the array's power supply connection between VCC and GND. The bulk capacitor will overcome voltage slumps caused by PC board trace inductances.

# **ERASURE CHARACTERISTICS**

Erasure begins when EPROMs are exposed to light with wavelengths shorter than approximately 4000 Angstroms (Å). It should be noted that sunlight and certain fluorescent lamps have wavelengths in the 3000Å-4000Å range. Data shows that constant exposure to room level fluorescent lighting can erase an EPROM in approximately 3 years, while it takes approximately 1 week when exposed to direct sunlight. If the device is exposed to these lighting conditions for extended periods, opaque labels should be placed over the window to prevent unintentional erasure.

The recommended erasure procedure is exposure to ultraviolet light of wavelength 2537Å. The integrated dose (UV intensity  $\times$  exposure time) for erasure should be a minimum of 15 Wsec/cm². Erasure time is approximately 15 to 20 minutes using an ultraviolet lamp with a 12000  $\mu$ W/cm² power rating. The EPROM should be placed within 1 inch of the lamp tubes. An EPROM can be permanently damaged if the integrated dose exceeds 7258 Wsec/cm² (1 week @ 12000  $\mu$ W/cm²).

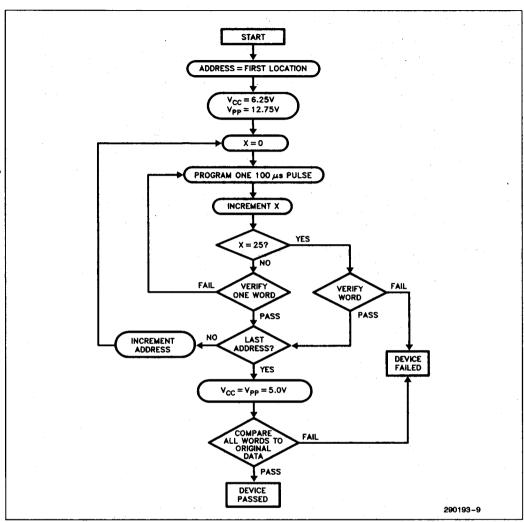

Figure 4. Quick-Pulse Programming™ Algorithm

## Quick-Pulse Programming™ Algorithm

The Quick-Pulse Programming algorithm programs Intel's 27C210. Developed to substantially reduce programming throughput, this algorithm can program the 27C210 as fast as 8 seconds. Actual programming time depends on programmer overhead.

The Quick-Pulse Programming algorithm employs a  $100~\mu s$  pulse followed by a word verification to determine when the addressed word has been successfully programmed. The algorithm terminates if 25 attempts fail to program a word.

The entire program pulse/word verify sequence is performed with  $V_{PP}=12.75V$  and  $V_{CC}=6.25V$ . When programming is complete, all words are compared to the original data with  $V_{CC}=V_{PP}=5.0V$ .

# DC PROGRAMMING CHARACTERISTICS $T_A = 25^{\circ}C \pm 5^{\circ}C$

| Symbol          | Parameter                                    | Notes | Min  | Тур   | Max  | Unit | Test Condition                                       |

|-----------------|----------------------------------------------|-------|------|-------|------|------|------------------------------------------------------|

| I <sub>LI</sub> | Input Load Current                           |       | -    | -     | 1    | μΑ   | V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IH</sub> |

| I <sub>CP</sub> | V <sub>CC</sub> Program Current              | 1     |      |       | 50   | mA   | CE = PGM = VIL                                       |

| Ірр             | V <sub>PP</sub> Program Current              | 1     |      |       | 50   | mA   | CE = PGM = VIL                                       |

| V <sub>IL</sub> | Input Low Voltage                            |       | -0.1 |       | 0.8  | ٧    |                                                      |

| V <sub>IH</sub> | Input High Voltage                           |       | 2.4  |       | 6.5  | ٧    |                                                      |

| V <sub>OL</sub> | Output Low Voltage (Verify)                  |       |      |       | 0.45 | V    | I <sub>OL</sub> = 2.1 mA                             |

| V <sub>OH</sub> | Output High Voltage (Verify)                 |       | 3.5  |       |      | ٧    | $I_{OH} = -2.5  \text{mA}$                           |

| V <sub>ID</sub> | A <sub>9</sub> inteligent Identifier Voltage |       | 11.5 | 12.0  | 12.5 | ٧    |                                                      |

| V <sub>PP</sub> | V <sub>PP</sub> Program Voltage              | 2, 3  | 12.5 | 12.75 | 13.0 | ٧    |                                                      |

| V <sub>CP</sub> | V <sub>CC</sub> Supply Voltage (Program)     | 2     | 6.0  | 6.25  | 6.5  | V    |                                                      |

## AC PROGRAMMING CHARACTERISTICS(4) TA = 25°C ±5°C

| Symbol           | Parameter                  | Notes | Min | Тур | Max | Unit |

|------------------|----------------------------|-------|-----|-----|-----|------|

| t <sub>VCS</sub> | V <sub>CP</sub> Setup Time | 2     | 2   |     |     | μs   |

| t <sub>VPS</sub> | V <sub>PP</sub> Setup Time | 2     | 2   |     |     | μs   |

| t <sub>CES</sub> | CE Setup Time              |       | 2   |     |     | μs   |

| t <sub>AS</sub>  | Address Setup Time         |       | . 2 |     |     | μs   |

| t <sub>DS</sub>  | Data Setup Time            |       | 2   |     |     | μs   |

| tpw              | PGM Program Pulse Width    |       | 95  | 100 | 105 | μs   |

| t <sub>DH</sub>  | Data Hold Time             |       | 2   |     |     | μs   |

| toes             | OE Setup Time              |       | 2   |     |     | μs   |

| t <sub>OE</sub>  | Data Valid from OE         | 5     |     |     | 150 | ns   |

| t <sub>DFP</sub> | OE High to Output High Z   | 5, 6  | 0   |     | 130 | ns   |

| t <sub>AH</sub>  | Address Hold Time          |       | 0   |     |     | μs   |

4. See AC Input/Output Reference Waveform for timing measurements.

6. Sampled, not 100% tested.

<sup>1.</sup> Maximum current is with outputs O<sub>0</sub>-O<sub>15</sub> unloaded.

V<sub>CP</sub> must be applied simultaneously or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>.

When programming, a 0.1 μF capacitor is required across V<sub>PP</sub> and GND to suppress spurious voltage transients which can damage the device.

<sup>5.</sup> t<sub>OE</sub> and t<sub>DFP</sub> are device characteristics but must be accommodated by the programmer.

## PROGRAMMING WAVEFORMS

## **REVISION HISTORY**

| Number | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 03     | Revised general datasheet structure, text to improve clarity Revised speed bin as follows:  t <sub>ACC</sub> was 130 ns, is now 120 ns t <sub>CE</sub> was 130 ns, is now 120 ns t <sub>OE</sub> was 60 ns, is now 55 ns Added PDIP package Revised I <sub>SB</sub> Text Condition from CE = V <sub>CC</sub> to CE = V <sub>CC</sub> ± 0.2V Revised V <sub>OL</sub> from 0.4V to 0.45V Revised V <sub>OH</sub> from V <sub>CC</sub> - 0.8V to 2.4V Deleted 8 meg DIP, 4 and 8 Meg PLCC references Deleted EXPRESS page |  |  |  |  |