# **Dual SLIC**

# Dual Subscriber Line Interface Circuit Le57D11 Device

## **APPLICATIONS**

- Ideal for low cost, high performance line card applications (CO, DLC)

- Meets requirements for countries such as: China, Korea, Japan, Taiwan, and Australia

- Fulfills the following China specifications: GF002-9002.1

## **FEATURES**

- Dual Channel SLIC device with small footprint

- On-chip Thermal Management (TMG) feature in normal and reverse polarity

- Control states: Active (normal and reversal polarity), Standby, and Disconnect

- On-hook transmission

- Low standby power

- -39 V to -58 V battery operation

- Two-wire impedance set by single external impedance

- Per channel fault detection

- Device level thermal shutdown

- Programmable constant-current feed (Range TBD)

- Programmable loop-detect threshold

- Programmable ring-trip detect threshold

- Only +5 V and battery supply required

- Current Gain = 500

## **DESCRIPTION**

The innovative Le57D11 Dual Channel SLIC device was designed for high-density POTS applications requiring a small footprint SLIC device with significant power savings. By combining the line interface of two channels into one SLIC device, the Le57D11 device enables the design of a low cost, high performance, and fully programmable line interface for multiple country applications worldwide. The on-chip Thermal Management (TMG) feature allows for significantly reduced power dissipation on the device. Another benefit is that it is offered in space-saving package types 44-pin eTQFP and 32-pin PLCC. The small footprint of the SLIC device allows designers to save board space, increasing the density of lines on the board. The Le57D11 device is also designed to significantly reduce the number of external components required for line card design.

Legerity offers a range of compatible SLAC devices that perform the codec function in a line card. In particular, the Legerity Quad SLAC device combined with the Le57D11 device provides a programmable line circuit that can be configured for varying requirements.

## RELATED LITERATURE

- 080147 Am79Q02/021/031 Quad SLAC Data Sheet

- 080753 Le58QL02/021/031 QLSLAC<sup>™</sup> Data Sheet

- 080748 Le57D11 Evaluation Board User's Guide

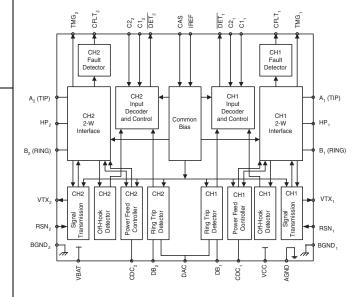

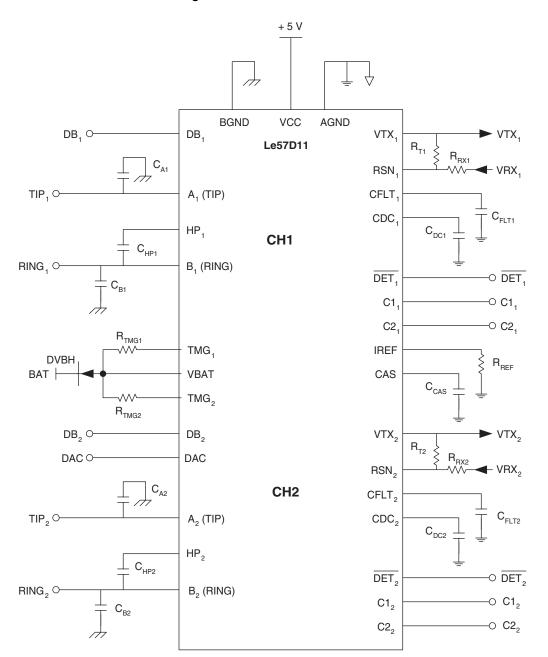

# **BLOCK DIAGRAM**

## ORDERING INFORMATION

32-Pin PLCC

44-pin eTQFP

| Device     | Performance Grade                        |

|------------|------------------------------------------|

| Le57D111JC | 32-pin PLCC, 48 dB Polarity Reversal     |

| Le57D113JC | 32-pin PLCC, 48 dB No Polarity Reversal  |

| Le57D111TC | 44-pin eTQFP, 48 dB Polarity Reversal    |

| Le57D113TC | 44-pin eTQFP, 48 dB No Polarity Reversal |

Publication# 080676 Rev: A

Version: 1.0

Date: Nov 16, 2001

# Table of Contents

| APPLICATIONS                                      |

|---------------------------------------------------|

| FEATURES                                          |

| ORDERING INFORMATION                              |

| DESCRIPTION                                       |

| RELATED LITERATURE                                |

| BLOCK DIAGRAM                                     |

| PRODUCT DESCRIPTION                               |

| BLOCK DESCRIPTIONS                                |

| FAULT DETECTOR                                    |

| TWO-WIRE INTERFACE.                               |

| SIGNAL TRANSMISSION                               |

| POWER FEED CONTROLLER AND COMMON BIAS             |

| INPUT DECODER AND CONTROL                         |

| OFF-HOOK DETECTOR                                 |

| RING-TRIP DETECTOR                                |

| CONNECTION DIAGRAMS                               |

| PIN DESCRIPTIONS                                  |

| ELECTRICAL CHARACTERISTICS                        |

| ABSOLUTE MAXIMUM RATINGS                          |

| OPERATING RANGES                                  |

| Environmental Ranges                              |

|                                                   |

| Electrical Ranges                                 |

| SPECIFICATIONS                                    |

| TRANSMISSION PERFORMANCE                          |

| CROSSTALK BETWEEN CHANNELS                        |

| LONGITUDINAL CAPABILITY                           |

| INSERTION LOSS AND BALANCE RETURN SIGNAL          |

| LINE CHARACTERISTICS                              |

| POWER SUPPLY REJECTION RATIO, ACTIVE NORMAL STATE |

| POWER DISSIPATION                                 |

| SUPPLY CURRENTS                                   |

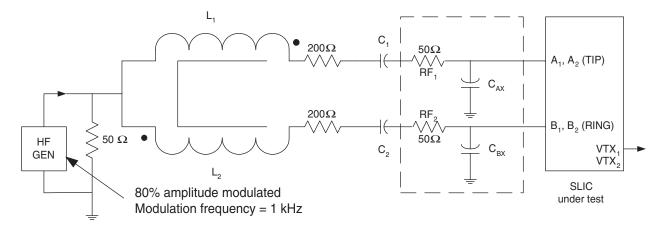

| RFI REJECTION (SEE FIGURE 9.)                     |

| LOGIC INPUTS                                      |

| LOGIC OUTPUT                                      |

| RING-TRIP DETECTOR INPUT (DA, DB)                 |

| CFLT1, CFLT21                                     |

| CFLT TOGGLE RANGE                                 |

| LOOP DETECTOR                                     |

| SLIC DECODING                                     |

| USER-PROGRAMMABLE COMPONENTS                      |

| DC FEED CHARACTERISTICS                           |

| TEST CIRCUITS                                     |

| APPLICATION CIRCUIT                               |

| LINE CARD PARTS LIST                              |

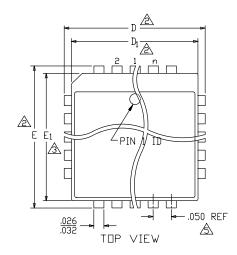

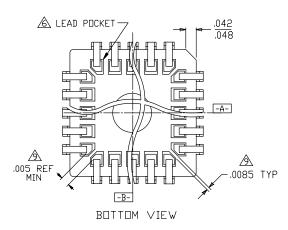

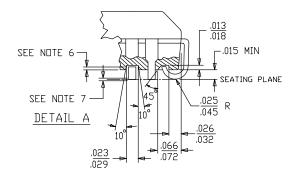

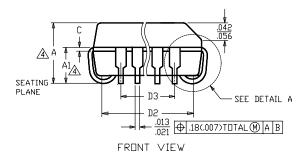

| PHYSICAL DIMENSIONS                               |

| PL032                                             |

| 7070                                              |

## PRODUCT DESCRIPTION

The Le57D11 device is designed for long loop high-density POTS applications requiring a power saving, small footprint SLIC. The Le57D11 device increases line card density by integrating two SLIC devices into a single 32 pin package. This reduction in board space allows for higher density linecard, which allows for amortizing common hardware across more channels. The Le57D11 device gives line card designers a simple control interface that supports four states: Active, Polarity Reversal, Standby, and Disconnect (Ringing). The Le57D11 device is low cost and high performance, providing key features required for POTS markets requiring only loop start. The device includes a thermal management resistor option.

## **BLOCK DESCRIPTIONS**

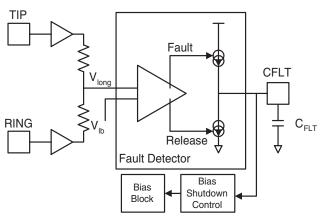

### **Fault Detector**

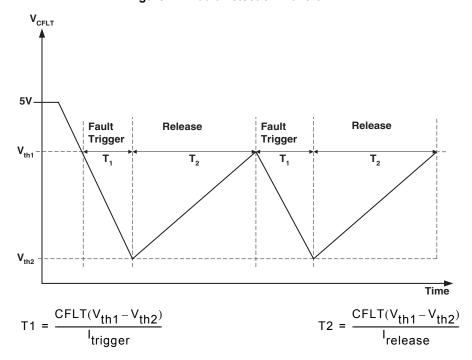

These blocks provide fault detection on a per channel basis for short to ground, short to battery, or certain AC faults. The Le57D11 device provides fault detection by having one fault detector in each channel. Under fault conditions — either a short to ground, a short to battery, or specified AC power cross faults — the Le57D11 device detects the longitudinal unbalance and trips the detector. Once the detector is tripped, the CFLT pin is pulled low and keeps toggling between Vth1 and Vth2 (refer Figure 2) until the fault is removed. An external  $0.1\mu\text{F}$  capacitor is connected between the CFLT pin and AGND, which provides a fault trigger delay of about 4 mS (T1) and release delay of 24 mS (T2). During release delay, the affected channel is shutdown which sets Tip and Ring to a Disconnect state. The trigger delay prevents short transients on Tip and Ring from triggering the channel shutdown when a fault is not present.

Figure 1. Fault Detector

Figure 2. Fault Detection Waveform

## **Two-Wire Interface**

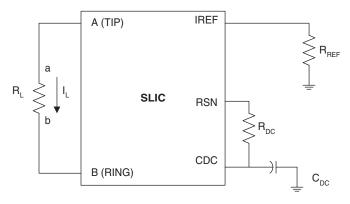

The two-wire interfaces provide DC current and send voice signals to a telephone apparatus connected to the line card with a two-wire line. The two-wire interface also receives the returning voice signals from the telephone transmitter.

## **Signal Transmission**

The AC line voltage is sensed by a differential amplifier between the A<sub>i</sub> (TIP) and HP<sub>i</sub> leads. The output of this amplifier is equal to the AC metallic components of the line voltages and is output at VTX<sub>i</sub>. The transmission circuit also contains a longitudinal feedback circuit to shunt longitudinal signals to a DC bias voltage. The longitudinal feedback does not affect metallic signals.

## **Power Feed Controller and Common Bias**

The power feed controllers have three sections: (1) the battery feed circuit, (2) the polarity reversal circuit, and (3) the common bias circuit. The battery feed circuit regulates the amount of DC current and voltage supplied to the telephone over a wide range of loop resistance. The polarity reversal circuit provides the capability to reverse the loop current for pay telephone key pad disable and other applications. The bias circuit provides a filtered reference voltage, which is offset from the subscriber line voltage, and a signal which sets the current limit.

## **Input Decoder and Control**

The input decoder and control block provides a means for a microprocessor or SLAC IC to control such system states as Active, Standby, Disconnect (Ringing), and Polarity Reversal. The input decoder and control block has TTL-compatible inputs, which set the operating states of the SLIC device.

## **Off-Hook Detector**

The most important loop monitoring function is off-hook detection. Loop current is programmed for both channels by a single resistor. Loop detect threshold is typically 1/3 of the programmed Loop current in the Active and Reverse Polarity states.

## Ring-Trip Detector

In the Disconnect state, the ring-trip detector is active. While the  $DB_i$  pin is more negative than the DAC pin, the  $\overline{DET}$  pin will be high to indicate on hook. When an off hook condition occurs, the  $DB_i$  pin becomes more positive than the DAC pin, and the  $\overline{DET}$  pin will go low to indicate off hook during ringing (ring-trip) has been detected. The system implements the Ringing state using external control of a ring relay in combination with the Disconnect SLIC state, which enables the ring-trip detector.

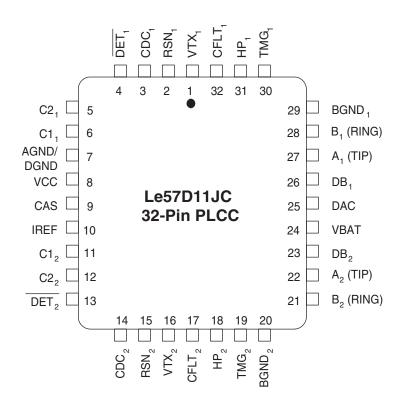

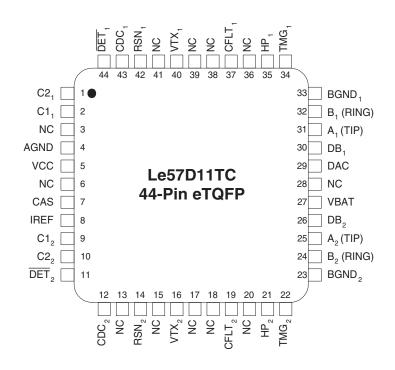

# **CONNECTION DIAGRAMS**

## Note:

- 1. Pin 1 is marked for orientation.

- 2. NC = No Connect

- e = exposed pad

# **PIN DESCRIPTIONS**

| Pin Name              | Туре         | Description                                                                                                                                                                                                                                                     |

|-----------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>1</sub> (TIP)  | Input/Output | Output of A (TIP) power amplifier of channel 1.                                                                                                                                                                                                                 |

| A <sub>2</sub> (TIP)  | Input/Output | Output of A (TIP) power amplifier of channel 2.                                                                                                                                                                                                                 |

| AGND                  | Ground       | Analog and digital ground.                                                                                                                                                                                                                                      |

| B <sub>1</sub> (RING) | Input/Output | Output of B (RING) power amplifier of channel 1.                                                                                                                                                                                                                |

| B <sub>2</sub> (RING) | Input/Output | Output of B (RING) power amplifier of channel 2.                                                                                                                                                                                                                |

| BGND <sub>1</sub>     | Ground       | Battery (power) ground of channel 1                                                                                                                                                                                                                             |

| BGND <sub>2</sub>     | Ground       | Battery (power) ground of channel 2.                                                                                                                                                                                                                            |

| C1 <sub>1</sub>       | Input        | State decoder inputs of channel 1.                                                                                                                                                                                                                              |

| C2 <sub>1</sub>       | Input        | State decoder inputs of charifier 1.                                                                                                                                                                                                                            |

| C1 <sub>2</sub>       | Input        | State decoder inputs of channel 2.                                                                                                                                                                                                                              |

| C2 <sub>2</sub>       | Input        | State decoder inputs of channer 2.                                                                                                                                                                                                                              |

| CAS                   | Capacitor    | Pin for capacitor to filter reference voltage when operating in anti-saturation region.                                                                                                                                                                         |

| CDC <sub>1</sub>      | Capacitor    | DC feed filter capacitor and DC feed programming pin of channel 1.                                                                                                                                                                                              |

| CDC <sub>2</sub>      | Capacitor    | DC feed filter capacitor and DC feed programming pin of channel 2.                                                                                                                                                                                              |

| CFLT <sub>1</sub>     | Input/Output | Fault detector output of channel 1. Connect a capacitor from CFLT <sub>1</sub> to AGND to set fault detector timing.                                                                                                                                            |

| CFLT <sub>2</sub>     | Input/Output | Fault detector output of channel 2. Connect a capacitor from CFLT <sub>2</sub> to AGND to set fault detector timing.                                                                                                                                            |

| DAC                   | Input        | Ring-trip negative of both channels. Negative input to ring-trip comparator.                                                                                                                                                                                    |

| DB <sub>1</sub>       | Input        | Ring-trip positive of channel 1. Positive input to ring-trip comparator.                                                                                                                                                                                        |

| DB <sub>2</sub>       | Input        | Ring-trip positive of channel 2. Positive input to ring-trip comparator.                                                                                                                                                                                        |

| DET <sub>1</sub>      | Output       | Switch-hook/Ring-trip detector output of channel1. Logic low indicates that a detector is tripped.                                                                                                                                                              |

| DET <sub>2</sub>      | Output       | Switch-hook/Ring-trip detector output of channel 2. Logic low indicates that a detector is tripped.                                                                                                                                                             |

| HP <sub>1</sub>       | Capacitor    | Connect High-pass filter capacitor from HP <sub>1</sub> to B <sub>1</sub> (RING).                                                                                                                                                                               |

| HP <sub>2</sub>       | Capacitor    | Connect High-pass filter capacitor from HP <sub>2</sub> to B <sub>2</sub> (RING).                                                                                                                                                                               |

| IREF                  | Resistor     | Connection for reference resistor that programs loop detector threshold and DC feed current of both channels.                                                                                                                                                   |

| RSN <sub>1</sub>      | Input        | Receive Summing Node of channel 1. The metallic current (both AC and DC) between $A_1$ (TIP) and $B_1$ (RING) is equal to 500 times the current into this pin. The networks that program receive gain and two-wire impedance of channel 1 connect to this node. |

| RSN <sub>2</sub>      | Input        | Receive Summing Node of channel 2. The metallic current (both AC and DC) between $A_2$ (TIP) and $B_2$ (RING) is equal to 500 times the current into this pin. The networks that program receive gain and two-wire impedance of channel 2 connect to this node. |

| TMG <sub>1</sub>      | Output       | Thermal management of channel 1. External resistor connects from TMG <sub>1</sub> to VBAT to offload power from the SLIC device.                                                                                                                                |

| TMG <sub>2</sub>      | Output       | Thermal management of channel 2. External resistor connects from TMG2 to VBAT to offload power from the SLIC device.                                                                                                                                            |

| VBAT                  | Battery      | Battery supply and connection to substrate.                                                                                                                                                                                                                     |

| VCC                   | Power        | +5 V power supply.                                                                                                                                                                                                                                              |

| VTX <sub>1</sub>      | Output       | Transmit audio signal of channel 1. This output is a scaled version of the A and B metallic voltage. VTX also sources the two-wire input impedance programming network.                                                                                         |

| VTX <sub>2</sub>      | Output       | Transmit audio signal of channel 2. This output is a scaled version of the A and B metallic voltage. VTX <sub>2</sub> also sources the two-wire input impedance programming network.                                                                            |

Le57D11 Data Sheet

6

## **ELECTRICAL CHARACTERISTICS**

## **Absolute Maximum Ratings**

Stresses greater than those listed under Absolute Maximum Ratings can cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods can affect device reliability

| Storage temperature                                                                                           | –55 to +150° C             |

|---------------------------------------------------------------------------------------------------------------|----------------------------|

| V <sub>CC</sub> with respect to AGND                                                                          | -0.4 to +7.0 V             |

| V <sub>BAT</sub> with respect to AGND:                                                                        |                            |

| Continuous                                                                                                    | +0.4 to -70 V              |

| 10 ms                                                                                                         | +0.4 to -75 V              |

| BGND <sub>1</sub> , BGND <sub>2</sub> with respect to AGND                                                    | +3 to –3 V                 |

| A <sub>1</sub> (TIP), A <sub>2</sub> (TIP), B <sub>1</sub> (RING), B <sub>2</sub> (RING) to                   |                            |

| BGND:                                                                                                         |                            |

| Continuous                                                                                                    | V <sub>BAT</sub> to + 1 V  |

| 10 ms (F = 0.1 Hz)                                                                                            | –70 to +5 V                |

| 1 μs (F = 0.1 Hz)                                                                                             | –80 to +8 V                |

| 250 ns (F = 0.1 Hz)                                                                                           | –90 to +12 V               |

| Current from A <sub>1</sub> (TIP), A <sub>2</sub> (TIP), B <sub>1</sub> (RING), B <sub>2</sub>                | ±150 mA                    |

| (RING)                                                                                                        | 1100 111/1                 |

| DB <sub>1</sub> , DB <sub>2</sub> , and DAC inputs:                                                           |                            |

| Voltage on ring-trip inputs                                                                                   | V <sub>BAT</sub> to 0 V    |

| Current into ring-trip inputs                                                                                 | ±10 mA                     |

| C1 <sub>1</sub> , C2 <sub>1</sub> , C1 <sub>2</sub> , C2 <sub>2</sub> , CFLT <sub>1</sub> , CFLT <sub>2</sub> |                            |

| Input Voltage                                                                                                 | $-0.4$ to $V_{CC}$ + 0.4 V |

| Maximum power dissipation, continuous:                                                                        |                            |

| T <sub>A</sub> = 70° C, No heat sink (see note)                                                               |                            |

| In 32-pin PLCC package                                                                                        | 1.7 W                      |

| In 44-pin eTQFP                                                                                               | 3.3 W                      |

| Thermal Data (Junction to Ambient):                                                                           | $\theta_{JA}$              |

| In 32-pin PLCC package                                                                                        | 43° C/W typ                |

| In 44-pin eTQFP                                                                                               | 22.7° C/W typ              |

| Thermal Data (Junction to Case):                                                                              | $\theta_{JC}$              |

| In 32-pin PLCC package                                                                                        | 16° C/W typ                |

| In 44-pin eTQFP                                                                                               | 9.2° C/W typ               |

| ESD immunity/pin (Human Body Model)                                                                           | 1.5 kV                     |

| ESD immunity/pin (Charge Device Model)                                                                        | 1 kV                       |

#### Note:

- Thermal limiting circuitry on-chip will shut down the circuit at a junction temperature of about 165° C. The device should never see this

temperature, and operation above 145° C junction temperature may degrade device reliability. See the SLIC Packaging Considerations for

more information.

- 2. Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

# **Operating Ranges**

Legerity guarantees the performance of this device over commercial (0° to 70° C) and industrial (-40° to 85° C) temperature ranges by conducting electrical characterization over each range, and by conducting a production test with single insertion coupled to periodic sampling. These characterization and test procedures comply with section 4.6.2 of Bellcore TR-TSY-000357 Component Reliability Assurance Requirements for Telecommunications Equipment.

## **Environmental Ranges**

| Ambient Temperature | –40° to 85° C |

|---------------------|---------------|

# **Electrical Ranges**

| V <sub>CC</sub>                   | 4.75 to 5.25 V           |

|-----------------------------------|--------------------------|

| V <sub>BAT</sub>                  | −39 to −58 V             |

| DB1, DB2, and DAC                 | V <sub>BAT</sub> to –2 V |

| AGND                              | 0 V                      |

| BGND1, BGND2 with respect to AGND | -100 to + 100 mV         |

| Load resistance on VTX to ground  | 20 kΩ minimum            |

#### Note:

The operating ranges define those limits between which the functionality of the device is guaranteed.

## **SPECIFICATIONS**

# **Transmission Performance**

| Description                        | Test Conditions (See Note 1)      | Min  | Тур         | Max | Unit | Note |

|------------------------------------|-----------------------------------|------|-------------|-----|------|------|

| 2-wire return loss                 | 200 Hz to 3.4 kHz (See Figure 8)  | 26   |             |     | dB   | 1, 4 |

| Analog output (VTX) impedance      |                                   |      | 3           | 20  | Ω    | 4    |

| Analog (VTX) output offset voltage |                                   | -50  |             | +50 | mV   |      |

| Overload level, 2-wire             | Active state                      | 2.5  |             |     | Vpk  | 2a   |

| Overload level                     | On hook, $R_{LAC}$ = 600 $\Omega$ | 0.77 |             |     | Vrms | 2b   |

| THD (Total Harmonic Distortion)    | 0 dBm                             |      | -64         | -50 | dB   | 5    |

| THD (Total Harmonic Distortion)    | +7 dBm                            |      | <b>–</b> 55 | -40 | uБ   | 3    |

| THD, On hook                       | 0dBm, $R_{LAC}$ = 600 $\Omega$    |      |             | -36 | dB   | 5    |

# **Crosstalk Between Channels**

| Description             | Test Conditions (See Note 1) | Min | Тур | Max | Unit | Note |

|-------------------------|------------------------------|-----|-----|-----|------|------|

| Crosstalk coupling loss | F = 200 Hz to 3.4 kHz        |     | 80  |     | dB   | 4    |

# **Longitudinal Capability**

(See Figure 7.)

| Description                               | Test Conditions (See Note 1)      | Min | Тур | Max         | Unit  | Note |

|-------------------------------------------|-----------------------------------|-----|-----|-------------|-------|------|

| Longitudinal to metallic L-T, L-4 balance | 200 Hz to 3.4 kHz, 0° C to +70° C | 48  |     |             | dB    | 4    |

| Longitudinal signal generation 4-L        | 200 Hz to 3.4 kHz                 | 40  |     |             |       |      |

| Longitudinal current per pin (A or B)     | Active state (off hook)           | 8.5 | 20  |             | mArms | 8    |

| Longitudinal impedance at A or B          | 0 to 100 Hz                       |     | 25  |             | Ω/pin |      |

| Idle Channel Noise                        | C-Message, $R_L$ = 600 $\Omega$   |     | 7   | 12          | dBrnc | 4    |

| idie Channel Noise                        | Psophometric, 600 Ω               |     | -83 | <b>–</b> 78 | dBmP  |      |

# **Insertion Loss and Balance Return Signal**

(See Figure 5 and Figure 6.)

| Description                  | Test Conditions (See Note 1)           | Min            | Тур   | Max            | Unit | Note |

|------------------------------|----------------------------------------|----------------|-------|----------------|------|------|

| Gain accuracy, 4- to 2-wire  | 0 dBm, 1 kHz                           | -0.20          | 0     | +0.20          |      |      |

| Gain accuracy, 2- to 4-wire  | 0 dBm, 1 kHz                           | -9.64          | -9.54 | -9.44          |      |      |

| Gain accuracy, 4- to 2-wire  | On hook                                | -0.35          |       | +0.35          |      | 4    |

| Gain accuracy over frequency | 300 to 3.4 kHz<br>relative to 1 kHz    | -0.15          |       | +0.15          | dB   |      |

| Gain tracking                | +3 dBm to –55 dBm<br>relative to 0 dBm | -0.15          |       | +0.15          |      |      |

| Gain tracking<br>On hook     | 0 dBm to -37 dBm<br>+3 dBm to 0 dBm    | -0.15<br>-0.35 |       | +0.15<br>+0.35 |      |      |

| Group delay                  | 0 dBm, 1 kHz                           |                | 4     |                | μs   | 4, 7 |

# **Line Characteristics**

| Description                                     | Test Conditions (See Note 1)                                                 | Min               | Тур   | Max               | Unit | Note |

|-------------------------------------------------|------------------------------------------------------------------------------|-------------------|-------|-------------------|------|------|

| I <sub>L</sub> , Short Loops, Active state      | R <sub>LDC</sub> = 600 Ω                                                     | 26.4              | 30    | 33.6              |      |      |

| I <sub>L</sub> , Long Loops, Active state       | $R_{LDC}$ = 1930 Ω, BAT = -42.75 V,<br>$T_{A}$ = 25°C                        | 18                | 19    |                   | mA   |      |

| I <sub>L</sub> , Accuracy, Standby state        | $I_{L} = \left(\frac{ VBAT  - 3V}{(R_{L} + 5K)}\right), T_{A} = 25^{\circ}C$ | 0.7I <sub>L</sub> | ΙL    | 1.3l <sub>L</sub> | 11// |      |

| I <sub>L</sub> , Loop current, Disconnect state | R <sub>L</sub> = 0                                                           |                   |       | 100               | μΑ   |      |

| VAB, Open Circuit voltage                       | V <sub>BAT</sub> = -48 V                                                     | +38.3             | +40.3 |                   | V    |      |

# **Power Supply Rejection Ratio, Active Normal State**

| Description                   | Test Conditions (See Note 1)                                        | Min | Тур | Max | Unit | Note |

|-------------------------------|---------------------------------------------------------------------|-----|-----|-----|------|------|

| V <sub>CC</sub>               | 50 Hz to 3.4 kHzV <sub>RIPPLE</sub> = 100 mV <sub>rms</sub>         | 30  | 40  |     | dB   | 5    |

| $V_{BAT}$                     | $50 \text{ Hz to } 3.4 \text{ kHzV}_{RIPPLE} = 500 \text{ mV}_{PP}$ | 28  | 50  |     |      |      |

| Effective internal resistance | CAS pin to V <sub>BAT</sub>                                         | 85  | 170 | 255 | kΩ   | 4    |

# **Power Dissipation**

| Description Test Conditions (See Note 1)   |                                   | Min | Тур  | Max  | Unit | Note |

|--------------------------------------------|-----------------------------------|-----|------|------|------|------|

| On hook, Standby state (both Stdby)        |                                   |     | 40   | 100  |      |      |

| On hook, Active state (Active)             |                                   |     | 200  | 400  | mW   |      |

| Off hook, Active state (Active)            | $R_L$ = 300 Ω, $R_{TMG}$ = 1600 Ω |     | 1400 | 2000 |      |      |

| One channel, Active/<br>One channel, Stdby | $R_L$ = 300 Ω, $R_{TMG}$ = 1600 Ω |     | 720  | 1050 |      |      |

# **Supply Currents**

Battery = -48 V

| Description                                                   | Description Test Conditions (See Note 1) |      | Тур | Max | Unit  | Note |

|---------------------------------------------------------------|------------------------------------------|------|-----|-----|-------|------|

| I <sub>CC</sub> ,<br>On-hook V <sub>CC</sub> supply current   | Standby state (both Stdby)               |      | 4.4 |     |       |      |

|                                                               | Active state, BAT = -48 V (both active)  | 12.6 |     |     | mA    |      |

| 1                                                             | Standby state (both Stdby)               |      | 0.4 |     | 111/5 |      |

| I <sub>BAT</sub> ,<br>On-hook V <sub>BAT</sub> supply current | Active state, BAT = -48 V (both active)  |      | 5.6 |     |       |      |

# **RFI Rejection**

(See Figure 9.)

| Description  | Test Conditions                                                         | Min | Тур | Max | Unit  | Note |

|--------------|-------------------------------------------------------------------------|-----|-----|-----|-------|------|

| VTX1 or VTX2 | f = .01 MHz to 100 MHz<br>HF gen output = 1.5 Vrms<br>CAX = CBX = 33 nF |     |     | 1   | mVrms | 4    |

|              | CAX = CBX = 2.2 nF                                                      |     |     | 3   |       |      |

# **Logic Inputs**

(Applies to C11, C12, C21, and C22.)

| Description                          | Test Conditions | Min         | Тур | Max | Unit | Note |

|--------------------------------------|-----------------|-------------|-----|-----|------|------|

| V <sub>IH</sub> , Input High voltage |                 | 2.0         |     |     | V    |      |

| V <sub>IL</sub> , Input Low voltage  |                 |             |     | 8.0 | ]    |      |

| I <sub>IH</sub> , Input High current |                 | <b>–</b> 75 |     | 40  | μA   |      |

| I <sub>IL</sub> , Input Low current  |                 | -400        |     |     | μΛ   |      |

# **Logic Output**

(Applies to  $\overline{\text{DET1}}, \overline{\text{DET2}}, \text{CFLT1}, \text{ and CFLT2.})$

| Description                           | Test Conditions (See Note 1)                   | Min | Тур | Max  | Unit | Note |

|---------------------------------------|------------------------------------------------|-----|-----|------|------|------|

| V <sub>OL</sub> , Output Low voltage  | $I_{OUT}$ = 0.3 mA, 15 k $\Omega$ to $V_{CC}$  |     |     | 0.40 | V    |      |

| V <sub>OH</sub> , Output High voltage | $I_{OUT}$ = -0.1 mA, 15 k $\Omega$ to $V_{CC}$ | 2.4 |     |      | V    |      |

# **Ring-Trip Detector Input**

(Applies to DAC, DB1, and DB2.)

| Description    | Test Conditions (See Note 1) | Min  | Тур | Max | Unit | Note |

|----------------|------------------------------|------|-----|-----|------|------|

| Bias Current   |                              | -500 | -50 |     | nA   |      |

| Offset voltage | Source resistance = 2 MΩ     | -50  | 0   | +50 | mV   | 6    |

# CFLT1, CFLT2

| Description                 | Test Conditions (See Note 1) | Min | Тур | Max | Unit | Note |

|-----------------------------|------------------------------|-----|-----|-----|------|------|

| Sinking Current (ITrigger)  |                              |     | 60  |     | uА   |      |

| Sourcing Current (IRelease) |                              |     | 10  |     | μΛ   |      |

# **CFLT Toggle Range**

| Description Test Conditions (See Note 1) |  | Min | Тур | Max | Unit | Note |  |

|------------------------------------------|--|-----|-----|-----|------|------|--|

| Vth1                                     |  |     |     | 3.0 | 3.3  | \/   |  |

| Vth2                                     |  |     |     | 0.8 | 1.1  | V    |  |

# **Loop Detector**

10

| Description        |         | Test Conditions (See Note 1) | Min | Тур | Max  | Unit | Note |

|--------------------|---------|------------------------------|-----|-----|------|------|------|

| Off-hook threshold | Active  |                              | 9   |     | 11   |      |      |

| On-hook threshold  | Active  |                              | 8.5 |     | 10.5 |      |      |

| Off-hook threshold | Standby |                              | 4   |     | 6    | mA   |      |

| On-hook threshold  | Standby |                              | 3.8 |     | 5.8  |      |      |

| Hysteresis         |         |                              | 0   |     | 2    |      |      |

#### Note:

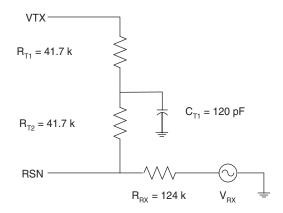

1. Unless otherwise noted, test conditions are BAT = -52 V;  $V_{CC}$  = +5 V;  $R_{L1}$ ,  $R_{L2}$  = 600  $\Omega$ ;  $R_{TMG1}$ ,  $R_{TMG2}$  = 1600  $\Omega$ ; no fuse resistors;  $C_{HP1}$ ,  $C_{HP2}$  = 100 nF;  $C_{DC1}$ ,  $C_{DC2}$  = 1.5  $\mu$ F;  $C_{CAS}$  = 0.33  $\mu$ F;  $R_{REF}$  = 15 K; two-wire AC input impedance is a 600  $\Omega$  resistance synthesized by the programming network shown below.

Figure 3. AC Input Impedance Programming Network

- 2. a. Z when THD = 1%.

- b. Overload level is defined when THD = 1.5%.

- Balance return signal is the signal generated at V<sub>TX</sub> by V<sub>RX</sub>. This specification assumes that the two-wire, AC-load impedance matches the programmed impedance.

- 4. Not tested in production. This parameter is guaranteed by characterization or correlation to other tests.

- 5. This parameter is tested at 1 kHz in production. Performance at other frequencies is guaranteed by characterization.

- 6. Tested with 0  $\Omega$  source impedance. 2 M $\Omega$  is specified for system design only.

- Group delay can be greatly reduced by using a Z<sub>T</sub> network such as that shown in Note 1. The network reduces the group delay to less than 2 μs and increases 2WRL. The effect of group delay on linecard performance also may be compensated for by synthesizing complex impedance with the QSLAC™ or DSLAC™ device.

- 8. Minimum current level guaranteed not to cause a false loop detect.

# **SLIC Decoding**

(For X, Channel = 1 or 2)

| State | C2x | C1x | Two-Wire Status   | DETx output        |

|-------|-----|-----|-------------------|--------------------|

| 0     | 0   | 0   | Disconnect        | Ring-Trip Detector |

| 1     | 0   | 1   | Active            | Loop Detector      |

| 2     | 1   | 1   | Polarity Reversed | Loop Detector      |

| 3     | 1   | 0   | Standby           | Loop Detector      |

# Legerity. PRELIMINARY User-Programmable Components

| $Z_{T} = 166.7(Z_{2WIN} - 2R_{F})$                                                                                                                           | $Z_T$ is connected between the VTX and RSN pins. The fuse resistors are $R_F$ , and $Z_{2WIN}$ is the desired 2-wire AC input impedance. When computing $Z_T$ , the internal current amplifier pole and any external stray capacitance between VTX and RSN must be taken into account. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $Z_{RX} = \frac{Z_L}{G_{42L}} \bullet \frac{500Z_T}{Z_T + 166.7(Z_L + 2R_F)}$                                                                                | $Z_{RX}$ is connected from VRX to RSN. $Z_{T}$ is defined above, and $G_{42L}$ is the desired receive gain.                                                                                                                                                                            |

| $R_{REF} = \frac{450}{I_{LOOP}}$ $C_{DC} = 1.5 \mu\text{F}$                                                                                                  | I <sub>LOOP</sub> is the desired loop current in the constant-current region.  Loop detect threshold is typically 1/3 of programmed Loop current.                                                                                                                                      |

| $C_{CAS} = \frac{1}{3.4 \cdot 10^5 \pi f_c}$                                                                                                                 | $C_{\text{CAS}}$ is the regulator filter capacitor and $f_{\text{c}}$ is the desired filter cut-off frequency.                                                                                                                                                                         |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                        |

| $I_{STANDBY} = \frac{ V_{BAT}  - 3 V}{5000\Omega + R_{L}}$                                                                                                   | Standby loop current (resistive region).                                                                                                                                                                                                                                               |

| Thermal Management Equations (Normal, Active, and                                                                                                            | Polarity Reverse States)                                                                                                                                                                                                                                                               |

| $R_{TMG} \ge \left( \frac{ V_{BAT}  - 6 V}{I_{LOOP}} - 70 \Omega \right)$                                                                                    | R <sub>TMG</sub> is connected from TMG to VBAT and limits power within the SLIC in Active and Off-Hook states.                                                                                                                                                                         |

| $P_{RTMG} = \frac{\left(\left V_{BAT}\right  - 6\;V - \left(I_{L} \bullet \;R_{L}\right)\right)^{2}}{\left(R_{TMG} + 70\;\Omega\right)^{2}} \bullet R_{TMG}$ | Power dissipated in the TMG resistor, $R_{\text{TMG}}$ during Active and Off-Hook states.                                                                                                                                                                                              |

| $P_{SLIC} =  V_{BAT}  \bullet I_L - P_{RTMG} - R_L(I_L)^2 + 0.12 W$                                                                                          | Power dissipated in the SLIC while in Active state.                                                                                                                                                                                                                                    |

# Legerity

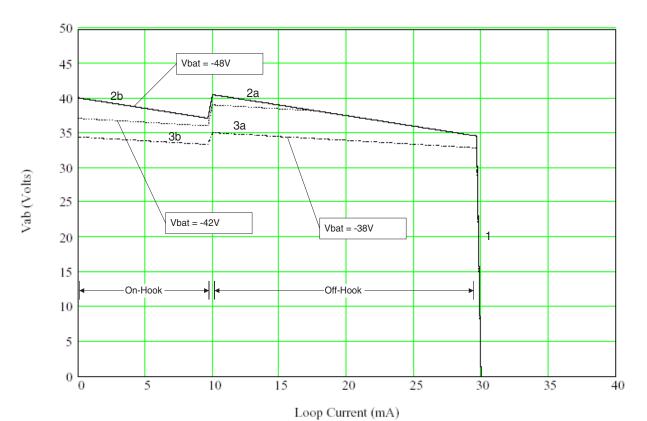

## **DC Feed Characteristics**

# Load Line (Typical)

$$I_{SWTH} = \frac{150}{R_{REF}}$$

$$R_{REF} = 15 K$$

Note:

$$V_{AB1} = I_L R_L' = \frac{(450)}{R_{REF}} R_L'$$

, where  $R_L' = R_L + 2R_F$

$$V_{AB2a} = 43.6 \text{ V} - I_L \frac{R_{FEED}}{88}$$

$$V_{AB2b} = V_{AB2a} - 3.5$$

$$V_{AB3a} = |V_{BAT}| - 1.8 - I_L \frac{R_{FEED}}{240}$$

$$V_{AB3b} = V_{AB3a} - 0.33 \cdot |V_{BAT}| + 10.8$$

Figure 4. Feed Programming

## Note:

14

To choose the correct value for  $R_{\rm DC}$ , please contact the manufacturer.

# **Test Circuits**

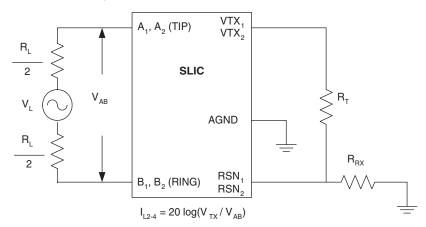

Figure 5. Two-to-Four Wire Insertion Loss

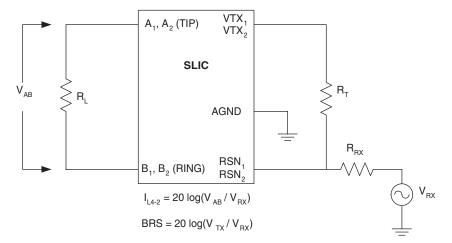

Figure 6. Four-to-Two Wire Insertion Loss and Balance Return Signals

Le57D11 Data Sheet

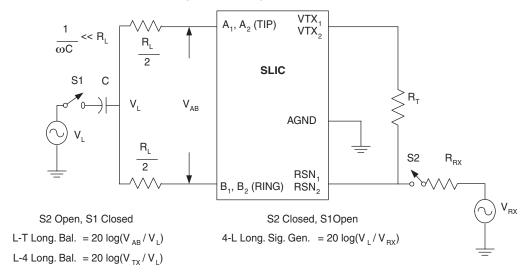

Figure 7. Longitudinal Balance

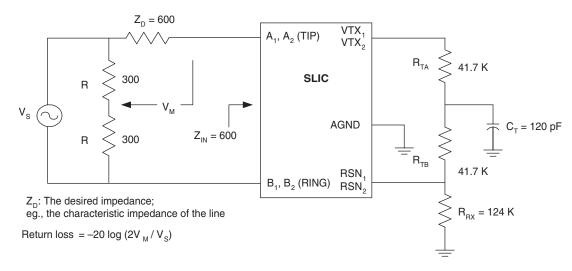

Figure 8. Two-Wire Return Loss Test Circuit

Figure 9. RFI Test Circuit

Figure 10. Le57D11 Test Circuit

16

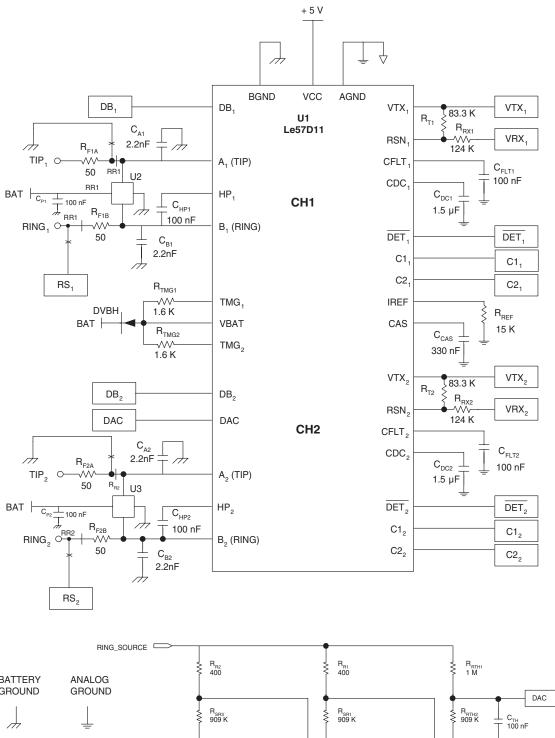

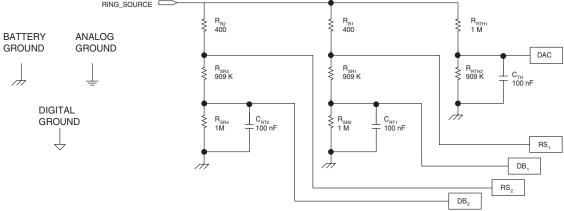

# **APPLICATION CIRCUIT**

# LINE CARD PARTS LIST

The following list defines the parts and part values required to meet target specification limits for channel i of the line card (i = 1,2).

| Item                                                                                                                                     | Quantity | Туре                      | Value   | Tol. | Rating | Comments | Note |

|------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------|---------|------|--------|----------|------|

| C <sub>A1</sub> , C <sub>B1</sub> , C <sub>A2</sub> ,<br>C <sub>B2</sub>                                                                 | 4        | Capacitor (X7R)           | 2200 pF | 20%  | 100 V  |          |      |

| C <sub>HP1</sub> , C <sub>HP2</sub> ,<br>C <sub>P1</sub> , C <sub>P2</sub> ,<br>C <sub>RT1</sub> , C <sub>RT2</sub> ,<br>C <sub>TH</sub> | 7        | Capacitor (X7R)           | 100 nF  | 20%  | 100 V  |          |      |

| C <sub>FLT1</sub> , C <sub>FLT2</sub>                                                                                                    | 2        | Capacitor (X7R)           | 100 nF  | 20%  | 16 V   |          |      |

| C <sub>DC1</sub> , C <sub>DC2</sub>                                                                                                      | 2        | Capacitor (X7R)           | 1.5 µF  | 10%  | 16 V   |          |      |

| R <sub>F1A</sub> , R <sub>F1B</sub> ,<br>R <sub>F2A</sub> , R <sub>F2B</sub>                                                             | 2        | Resistor Hybrid           | 50      | 1%   |        |          |      |

| R <sub>REF</sub>                                                                                                                         | 1        | SMT                       | 15 k    | 1%   | 1/10 W |          |      |

| R <sub>T1</sub> , R <sub>T2</sub>                                                                                                        | 2        | SMT                       | 83.3 k  | 1%   | 1/10 W |          |      |

| R <sub>RX1</sub> , R <sub>RX2</sub>                                                                                                      | 2        | SMT                       | 124 k   | 1%   | 1/10 W |          |      |

| DVBH                                                                                                                                     | 1        | MURS 120 (D0-41)<br>DIODE |         |      |        |          |      |

| R <sub>R1</sub> , R <sub>R2</sub>                                                                                                        | 2        | Resistor Hybrid           | 400     | 1%   |        |          |      |

| U2, U3                                                                                                                                   | 2        | TISP61089                 |         |      |        |          |      |

| R <sub>RTH1</sub> , R <sub>SR2</sub> ,<br>R <sub>SR4</sub>                                                                               | 3        | SMT                       | 1 M     | 1%   | 1/4 W  |          |      |

| R <sub>SR1</sub> , R <sub>SR3</sub> ,<br>R <sub>RTH2</sub>                                                                               | 3        | SMT                       | 909 k   | 1%   | 1/4 W  |          |      |

| U1                                                                                                                                       | 1        | Le57D11                   |         |      |        |          |      |

| R <sub>TMG1</sub> R <sub>TMG2</sub>                                                                                                      | 2        | SMT                       | 1.6 k   | 1%   | 2 W    |          |      |

| C <sub>CAS</sub>                                                                                                                         | 1        | Capacitor (X7R)           | 330 nF  | 20%  | 50 V   |          |      |

Le57D11 Data Sheet

18

# **PHYSICAL DIMENSIONS**

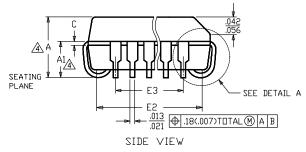

## **PL032**

N□TES: Dwg rev AH; 08/00

**PACKAGE** PΙ 032 JEDEC MD-052(A)AE SYMBOL MIN MAX .125 .140 Α Α1 .080 .095 D .485 .495 **D1** .447 .453 .390 D2 .430 **D**3 .300 REF Ε .585 .595 E1 .547 .553 E2 .490 .530 .400 REF  $\mathbb{C}$ .009 .015

1. ALL DIMENSIONS ARE IN INCHES.

DIMENSIONS "D" AND "E" ARE MEASURED FROM DUTERMOST POINT.

⚠ DIMENSIONS D1 AND E1 DO NOT INCLUDE CORNER MOLD FLASH. ALLOWABLE CORNER MOLD FLASH IS .010"

A DIMENSIONS "A", "A1", "D2" AND "E2" ARE

MEASURED AT THE POINTS OF CONTACT TO BASE PLANE LEAD SPACING AS MEASURED FROM CENTERLINE

TO CENTERLINE SHALL BE WITHIN ±.005".

J-LEAD TIPS SHOULD BE LOCATED INSIDE

THE "POCKET.

7. LEAD COPLANARITY SHALL BE WITHIN .004" AS MEASURED FROM SEATING PLANE, COPLANARITY IS MEASURED PER AMD 06-500.

8. LEAD TWEEZE SHALL BE WITHIN .0045" ON EACH SIDE AS MEASURED FROM A VERTICAL FLAT PLANE. TWEEZE IS MEASURED PER AMD 06-500.

LEAD POCKET MAY BE RECTANGULAR (AS SHOWN) OR OVAL.

IF CORNER LEAD POCKETS ARE CONNECTED THEN 5 MILS

MINIMUM CORNER LEAD SPACING IS REQUIRED.

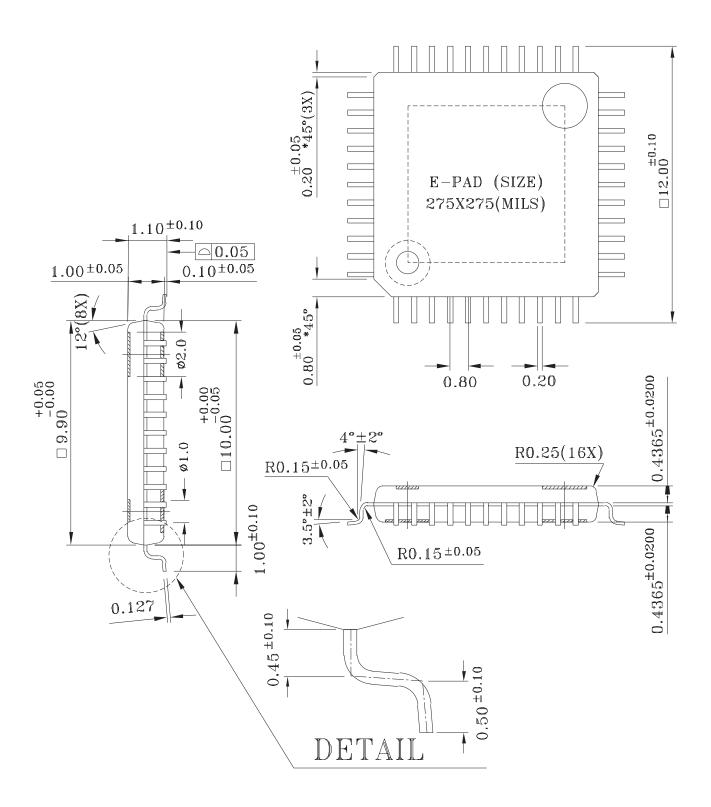

eTQFP

The contents of this document are provided in connection with Legerity, Inc. products. Legerity makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in Legerity's Standard Terms and Conditions of Sale, Legerity assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right. Legerity's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of Legerity's product could create a situation where personal injury, death, or severe property or environmental damage may occur. Legerity reserves the right to discontinue or make changes to its products at any time without notice.

© 2001 Legerity, Inc. All rights reserved.

## Trademarks

Legerity, the Legerity logo and combinations thereof, are trademarks of Legerity, Inc.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# Americas

#### **ATLANTA**

6465 East Johns Crossing, Suite 400 Duluth, GA USA 30097

MainLine: 770-814-4252 Fax: 770-814-4253

#### **AUSTIN**

4509 Freidrich Lane Austin, TX USA 78744-1812 MainLine: 512-228-5400 Fax: 512-228-5510

#### **BOSTON**

6 New England Executive Park Suite 400 Burlington, MA USA 01803

MainLine: 781-229-7320 Fax: 781-272-3706

#### **CHICAGO**

8770 W. Bryn Mawr, Suite 1300 Chicago, IL USA 60631 MainLine: 773-867-8034 Fax: 773-867-2910

#### **DALLAS**

4965 Preston Park Blvd., Suite 280 Plano, TX USA 75093 MainLine: 972-985-5474 Fax: 972-985-5475

## HUNTSVILLE

600 Boulevard South, Suite 104 Huntsville, AL USA 35802 MainLine: 256-705-3504 Fax: 256-705-3505

#### **IRVINE**

1114 Pacifica Court, Suite 250 Irvine, CA USA 92618 MainLine: 949-753-2712 Fax: 949-753-2713

#### **NEW JERSEY**

3000 Atrium Way, Suite 270 Mt. Laurel, NJ USA 08054 MainLine: 856-273-6912 Fax: 856-273-6914

## **OTTAWA**

600 Terry Fox Drive Ottawa, Ontario, Canada K26 4B6 MainLine: 613-599-2000

Fax: 613-599-200

## **RALEIGH**

2500 Regency Parkway, Suite 226 Cary, NC USA 27511 MainLine: 919-654-6843 Fax: 919-654-6781

## **SAN JOSE**

1740 Technology Drive, Suite 290 San Jose, CA USA 95110 MainLine: 408-573-0650 Fax: 408-573-0402

Mailing: P.O. Box 18200

Austin, TX 78760-8200 Shipping: 4509 Freidrich Lane Austin, TX 78744-1812

Telephone: (512) 228-5400 Fax: (512) 228-5510

North America Toll Free: (800) 432-4009

# Worldwide Sales Offices

# Europe

#### **BELGIUM**

Baron Ruzettelaan 27 8310 Brugge Belgium

MainLine: 32-50-28-88-10 Fax: 32-50-27-06-44

#### **FRANCE**

7, Avenue G. Pompidou Suite 402 92300 Levallois-Perret, France MainLine: 33-1-47-48-2206 Fax: 33-1-47-48-2568

#### **GERMANY**

Freisinger Str. 1 85737 Ismaning, Germany MainLine: 49-89-1893-99-0 Fax: 49-89-1893-99-44

#### ITALY

Via F. Rosselli 3/2 20019 Settimo Mse, Milano Italy MainLine: 39-02-3355521 Fax: 39-02-33555232

#### **SWEDEN**

Frösundaviks Allé 15, 4tr SE-16970 Solna Sweden

MainLine: 46-8-509-045-45 Fax: 46-8-509-046-36

#### UK

Regus House, Windmill Hill Business Park Whitehill Way

SN5 6QR Swindon Wiltshire UK

MainLine: 44-(0)1793-441408 Fax: 44-(0)1793-441608

# Asia

#### **HONG KONG**

Units 2401-2, 24th Floor Jubilee Centre, 18 Fenwick Street Wanchai, Hong Kong

MainLine: 852-2864-8300 Fax: 852-2866-1323

#### **KOREA**

135-090 18th Fl., Kyoung Am Bldg 157-26, Samsung-dong, Kangnam-ku

Seoul, Korea

MainLine: 82-2-565-5951 Fax: 82-2-565-3788

#### **SHENZHEN**

Room 703, Block D1 Fu Yuan Garden Futian Free Trade Zone Shenzhen, PR China 518031 MainLine: 86-755-3567-008 Fax: 86-755-3567-191

### **TOKYO**

Shinjuku NS Bldg. 5F 2-4-1 Nishi Shinjuku, Shinjuku-ku Tokyo, Japan 163-0805 MainLine: 81-3-5339-2011

Fax: 81-3-5339-2012

To download or order product literature, visit our website at www.legerity.com.

To order literature in North America, call: (800) 572-4859 or 512-349-3193

or email: americalit@legerity.com

To order literature in Europe or Asia, call: 44-0-1179-341607

or email: Europe — eurolit@legerity.com Asia — asialit@legerity.com