## 11 x 10-bit Image Filter

#### **FEATURES**

- ☐ 66 MHz Data and Coefficient Input and Computation Rate

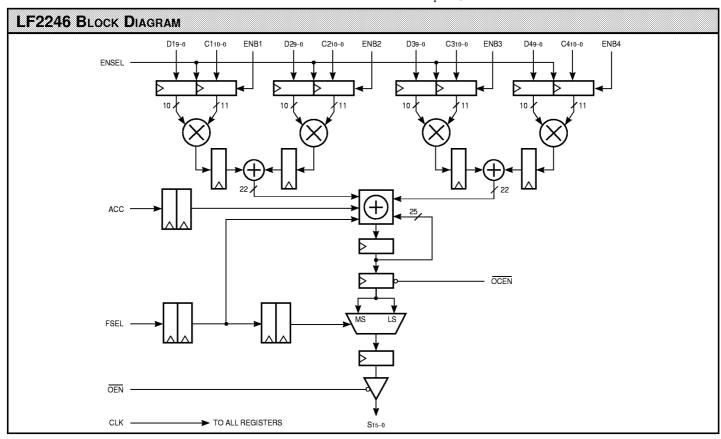

- ☐ Four 11 x 10-bit Multipliers with Individual Data and Coefficient Inputs and a 25-bit Accumulator

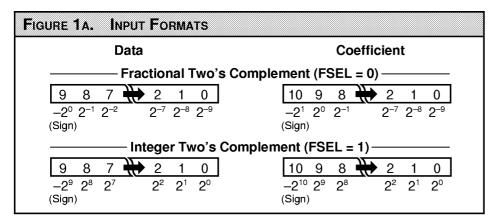

- ☐ User-Selectable Fractional or Integer Two's Complement Data Formats

- ☐ Fully Registered, Pipelined Architecture

- ☐ Input and Output Data Registers, with User-Configurable Enables

- ☐ Three-State Outputs

- ☐ Fully TTL Compatible

- ☐ Ideally Suited for Image Processing and Filtering Applications

- ☐ Replaces TRW/Raytheon TMC2246

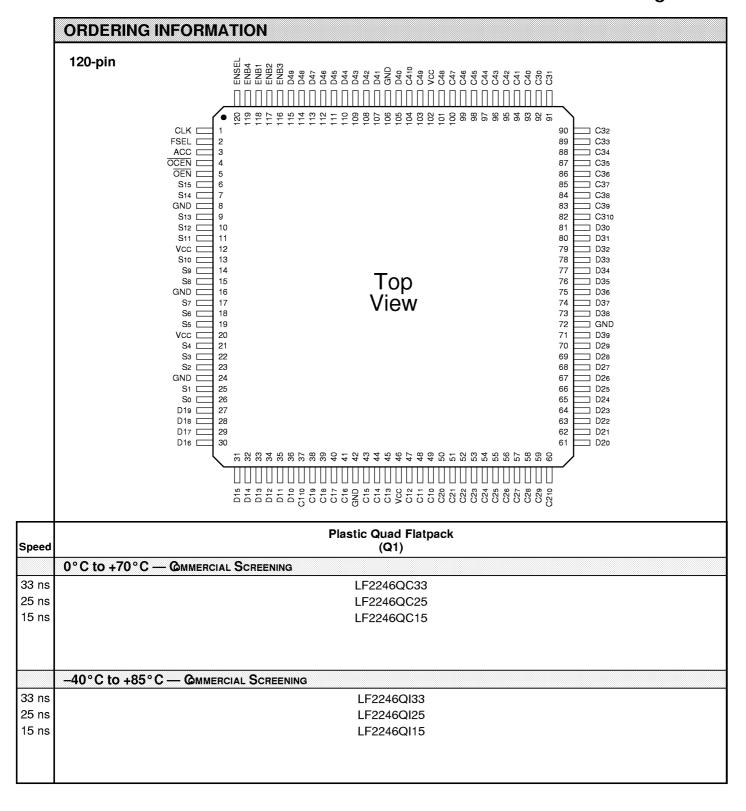

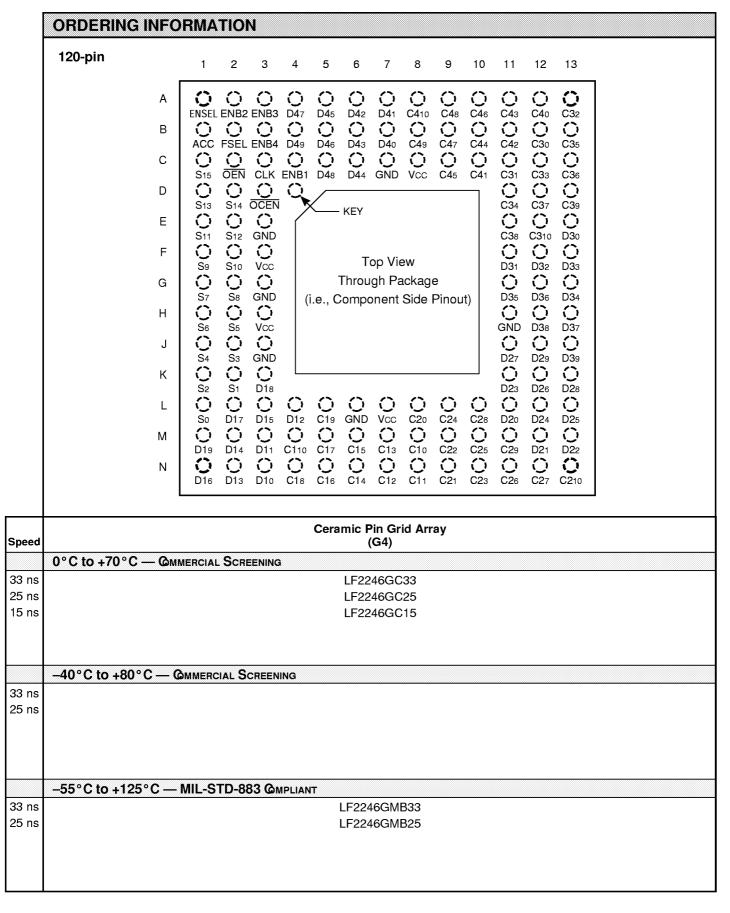

- ☐ Package Styles Available:

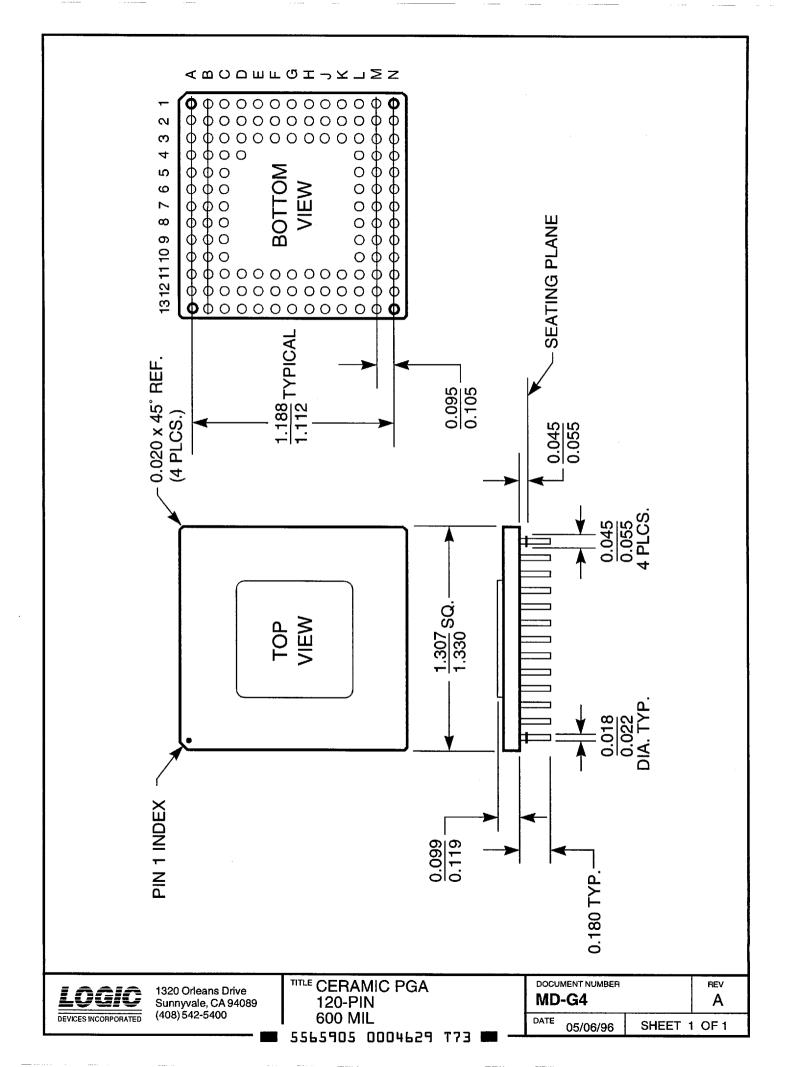

- 120-pin Pin Grid Array

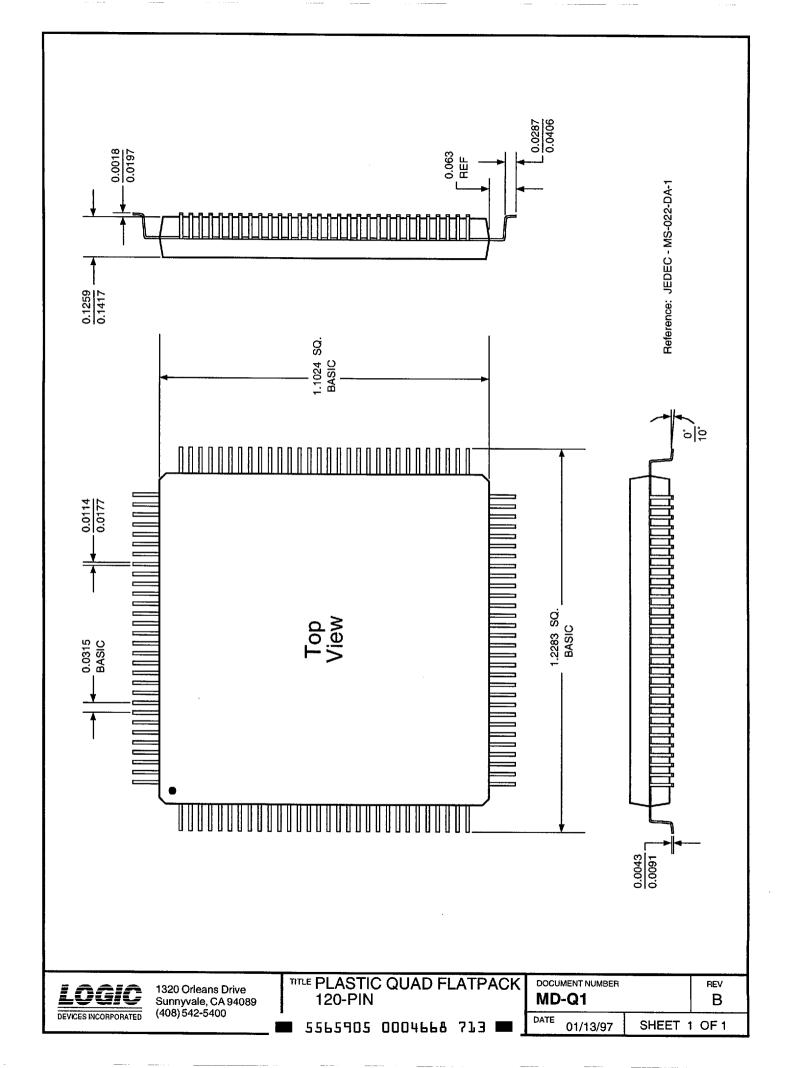

- 120-pin Plastic Quad Flatpack

#### DESCRIPTION

The LF2246 consists of an array of four 11 x 10-bit registered multipliers followed by a summer and a 25-bit accumulator. All multiplier inputs are user accessible and can be updated every clock cycle with either fractional or integer two's complement data. The pipelined architecture has fully registered input and output ports and an asynchronous three-state output enable control to simplify the design of complex systems. The pipeline latency for all inputs is five clock cycles.

Storage for mixing and filtering coefficients can be accomplished by holding the data or coefficient inputs over multiple clock cycles. A 25-bit accumulator path allows cumulative word growth which may be internally rounded to 16 bits. Output data is updated every clock cycle and may be held under user control. All inputs,

outputs, and controls are registered on the rising edge of clock, except for  $\overline{\text{OEN}}$ . The LF2246 operates at a clock rate of 66 MHz over the full temperature and supply voltage ranges.

The LF2246 is applicable for performing pixel interpolation in image manipulation and filtering applications. The LF2246 can perform a bilinear interpolation of an image (4-pixel kernels) at real-time video rates when used with an image resampling sequencer. Larger kernels or more complex functions can be realized by utilizing multiple devices.

Unrestricted access to all data and coefficient input ports provides the LF2246 with considerable flexibility in applications such as digital filters, adaptive FIR filters, mixers, and other similar systems requiring high-speed processing.

### 11 x 10-bit Image Filter

#### SIGNAL DEFINITIONS

#### **Power**

Vcc and GND

+5 V power supply. All pins must be connected.

#### Clock

CLK — Master Clock

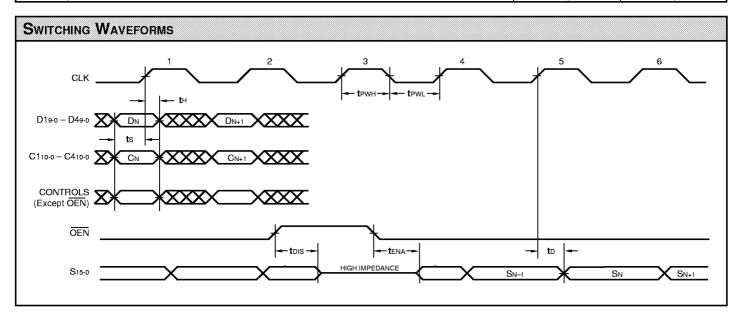

The rising edge of CLK strobes all enabled registers. All timing specifications are referenced to the rising edge of CLK.

#### **Inputs**

D19-0-D49-0 — Data Input

D1-D4 are 10-bit data input registers. The LSB is DN0 (Figure 1a).

C110-0-C410-0 — Coefficient Input

C1–C4 are 11-bit coefficient input registers. The LSB is CN0 (Figure 1a).

#### **Outputs**

S<sub>15-0</sub> — Data Output

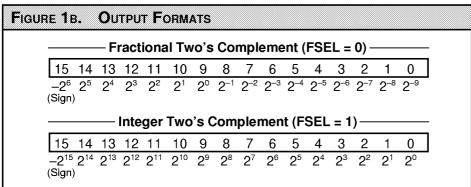

The current 16-bit result is available on the S<sub>15-0</sub> outputs (Figure 1b).

#### Controls

ENB1-ENB4 — Input Enable

The ENBN (N = 1, 2, 3, or 4) input allows either or both the DN and CN registers to be updated on each clock cycle. When ENBN is LOW, registers DN and CN are both strobed by the next rising edge of CLK. When ENBN is HIGH and ENSEL is LOW, register DN is strobed while register CN is held. If both ENBN and ENSEL are HIGH, register DN is held, and register CN is strobed (Table 1).

#### ENSEL — Enable Select

The ENSEL input in conjunction with the individual input enables ENB1–ENB4 determines whether the data or the coefficient input registers will be held on the next rising edge of CLK (Table 1).

#### <del>OEN</del> — Output Enable

When the  $\overline{\text{OEN}}$  signal is LOW, the current data in the output register is available on the S<sub>15-0</sub> pins. When  $\overline{\text{OEN}}$  is HIGH, the outputs are in a high-impedance state.

| TABLE 1. INPUT REGISTER CONTROL |       |                        |  |  |  |  |  |

|---------------------------------|-------|------------------------|--|--|--|--|--|

| ENB1-4                          | ENSEL | INPUT REGISTER<br>HELD |  |  |  |  |  |

| 1                               | 1     | Data 'n'               |  |  |  |  |  |

| 1                               | 0     | Coefficient 'N'        |  |  |  |  |  |

| 0                               | Х     | None                   |  |  |  |  |  |

X = "Don't Care"'N' = 1, 2, 3, or 4

<del>OCEN</del> — Clock Enable

When OCEN is LOW, data in the premux register (accumulator output) is loaded into the output register on the next rising edge of CLK. When OCEN is HIGH, data in the pre-mux register is held preventing the output register's contents from changing (if FSEL does not change). Accumulation continues internally as long as ACC is HIGH, despite the state of OCEN.

#### FSEL — Format Select

When the FSEL input is LOW, the data input during the current clock cycle is assumed to be in fractional two's complement format, and the upper 16 bits of the accumulator are presented at the output. Rounding of the accumulator result to 16 bits is performed if the accumulator control input ACC is LOW. When FSEL is HIGH, the data input is assumed to be in integer two's complement format, and the lower 16 bits of the accumulator are presented at the output. No rounding is performed when FSEL is HIGH.

#### ACC — Accumulator Control

The ACC input determines whether internal accumulation is performed on the data input during the current clock cycle. If ACC is LOW, no accumulation is performed, the prior accumulated sum is cleared, and the current sum of products is output. If FSEL is also LOW, one-half LSB rounding to 16 bits is performed on the result. This allows summations without propagating roundoff errors. When ACC is HIGH, the emerging product is added to the sum of the previous products, without additional rounding.

# 11 x 10-bit Image Filter

| Storage temperature                       | –65°C to +150°C      |

|-------------------------------------------|----------------------|

| Operating ambient temperature             | –55°Cto +125°C       |

| Vcc supply voltage with respect to ground | 0.5 V to +7.0 V      |

| Input signal with respect to ground       | 0.5 V to Vcc + 0.5 V |

| Signal applied to high impedance output   | 0.5 V to Vcc + 0.5 V |

| Output current into low outputs           | 25 mA                |

| Latchup current                           | > 400 mA             |

| OPERATING CONDITIONS To meet specified electrical and switching characteristics |                             |                              |  |  |  |  |

|---------------------------------------------------------------------------------|-----------------------------|------------------------------|--|--|--|--|

| Mode                                                                            | Temperature Range (Ambient) | Supply Voltage               |  |  |  |  |

| Active Operation, Commercial                                                    | 0°C to +70°C                | 4.75 V≤ <b>V</b> cc ≤ 5.25 V |  |  |  |  |

| Active Operation, Military                                                      | −55°C to +125°C             | 4.50 V≤ <b>V</b> cc ≤ 5.50 V |  |  |  |  |

| ELECTRICAL CHARACTERISTICS Over Operating Conditions (Note 4) |                        |                              |     |     |             |      |  |

|---------------------------------------------------------------|------------------------|------------------------------|-----|-----|-------------|------|--|

| Symbol                                                        | Parameter              | Test Condition               | Min | Тур | Max         | Unit |  |

| <b>V</b> OH                                                   | Output High Voltage    | Vcc = Min., IoH = −2.0 mA    | 2.4 |     |             | ٧    |  |

| <b>V</b> OL                                                   | Output Low Voltage     | VCC = Min., IOL = 4.0 mA     |     |     | 0.4         | V    |  |

| <b>V</b> IH                                                   | Input High Voltage     |                              | 2.0 |     | <b>V</b> cc | V    |  |

| <b>V</b> IL                                                   | Input Low Voltage      | (Note 3)                     | 0.0 |     | 0.8         | V    |  |

| lix                                                           | Input Current          | Ground ≤ Vin ≤ Vcc (Note 12) |     |     | ±10         | μΑ   |  |

| loz                                                           | Output Leakage Current | (Note 12)                    |     |     | ±40         | μΑ   |  |

| ICC1                                                          | Vcc Current, Dynamic   | (Notes 5, 6)                 |     |     | 100         | mA   |  |

| ICC2                                                          | Vcc Current, Quiescent | (Note 7)                     |     |     | 6           | mA   |  |

| CIN                                                           | Input Capacitance      | <b>T</b> A = 25°C, f = 1 MHz |     |     | 10          | pF   |  |

| Соит                                                          | Output Capacitance     | <b>T</b> A = 25°C, f = 1 MHz |     |     | 10          | pF   |  |

**SWITCHING CHARACTERISTICS**

# 11 x 10-bit Image Filter

| Commercial Operating Range (0°C to +70°C) Notes 9, 10 (ns) |                                            |         |     |     |     |     |     |  |

|------------------------------------------------------------|--------------------------------------------|---------|-----|-----|-----|-----|-----|--|

|                                                            |                                            | LF2246- |     |     |     |     |     |  |

|                                                            |                                            | 3       | 33  | 25  |     | 1   | 15  |  |

| Symbol                                                     | Parameter                                  | Min     | Max | Min | Max | Min | Max |  |

| tcyc                                                       | Cycle Time                                 | 33      |     | 25  |     | 15  |     |  |

| <b>t</b> PWL                                               | Clock Pulse Width Low                      | 15      |     | 10  |     | 7   |     |  |

| <b>t</b> PWH                                               | Clock Pulse Width High                     | 10      |     | 10  |     | 7   |     |  |

| ts                                                         | Input Setup Time                           | 10      |     | 8   |     | 5   |     |  |

| t⊢                                                         | Input Hold Time                            | 0       |     | 0   |     | 0   |     |  |

| <b>t</b> D                                                 | Output Delay                               |         | 15  |     | 13  |     | 11  |  |

| <b>t</b> DIS                                               | Three-State Output Disable Delay (Note 11) |         | 15  |     | 15  |     | 15  |  |

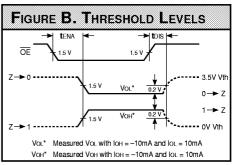

| <b>t</b> ENA                                               | Three-State Output Enable Delay (Note 11)  |         | 15  |     | 15  |     | 15  |  |

| MILITARY OPERATING RANGE (-55°C to +125°C) Notes 9, 10 (ns) |                                            |         |     |     |     |  |

|-------------------------------------------------------------|--------------------------------------------|---------|-----|-----|-----|--|

|                                                             |                                            | LF2246- |     |     |     |  |

|                                                             |                                            | 33 25   |     | :5  |     |  |

| Symbol                                                      | Parameter                                  | Min     | Max | Min | Max |  |

| tcyc                                                        | Cycle Time                                 | 33      |     | 25  |     |  |

| <b>t</b> PWL                                                | Clock Pulse Width Low                      | 15      |     | 10  |     |  |

| <b>t</b> PWH                                                | Clock Pulse Width High                     | 10      |     | 10  |     |  |

| ts                                                          | Input Setup Time                           | 10      |     | 8   |     |  |

| tн                                                          | Input Hold Time                            | 0       |     | 0   |     |  |

| <b>t</b> D                                                  | Output Delay                               |         | 15  |     | 13  |  |

| <b>t</b> DIS                                                | Three-State Output Disable Delay (Note 11) |         | 15  |     | 15  |  |

| <b>t</b> ENA                                                | Three-State Output Enable Delay (Note 11)  |         | 15  |     | 15  |  |

## 11 x 10-bit Image Filter

#### **NOTES**

- 1. Maximum Ratings indicate stress specifications only. Functional operation of these products at values beyond those indicated in the Operating Conditions table is not implied. Exposure to maximum rating conditions for extended periods may affect reliability.

- 2. The products described by this specification include internal circuitry designed to protect the chip from damaging substrate injection currents and accumulations of static charge. Nevertheless, conventional precautions should be observed during storage, handling, and use of these circuits in order to avoid exposure to excessive electrical stress values.

- 3. This device provides hard clamping of transient undershoot and overshoot. Input levels below ground or above VCC will be clamped beginning at  $-0.6\,\mathrm{V}$  and VCC +  $0.6\,\mathrm{V}$ . The device can withstand indefinite operation with inputs in the range of  $-0.5\,\mathrm{V}$  to  $+7.0\,\mathrm{V}$ . Device operation will not be adversely affected, however, input current levels will be well in excess of  $100\,\mathrm{mA}$ .

- 4. Actual test conditions may vary from those designated but operation is guaranteed as specified.

- 5. Supply current for a given application can be accurately approximated by:

$\frac{NCV^2F}{4}$

where

N = total number of device outputs

C = capacitive load per output

V = supply voltage

F = clock frequency

- 6. Tested with all outputs changing every cycle and no load, at a 30 MHz clock rate.

- 7. Tested with all inputs within 0.1 V of VCC or Ground, no load.

- 8. These parameters are guaranteed but not 100% tested.

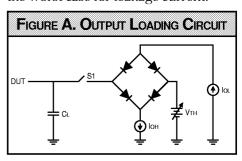

9. AC specifications are tested with input transition times less than 3 ns, output reference levels of 1.5 V (except tDIS test), and input levels of nominally 0 to 3.0 V. Output loading may be a resistive divider which provides for specified IOH and IOL at an output voltage of VOH min and VOL max respectively. Alternatively, a diode bridge with upper and lower current sources of IOH and IOL respectively, and a balancing voltage of 1.5 V may be used. Parasitic capacitance is 30 pF minimum, and may be distributed.

This device has high-speed outputs capable of large instantaneous current pulses and fast turn-on/turn-off times. As a result, care must be exercised in the testing of this device. The following measures are recommended:

- a. A 0.1  $\mu F$  ceramic capacitor should be installed between VCC and Ground leads as close to the Device Under Test (DUT) as possible. Similar capacitors should be installed between device VCC and the tester common, and device ground and tester common.

- b. Ground and Vcc supply planes must be brought directly to the DUT socket or contactor fingers.

- 10. Each parameter is shown as a minimum or maximum value. Input requirements are specified from the point of view of the external system driving the chip. Setup time, for example, is specified as a minimum since the external system must supply at least that much time to meet the worst-case requirements of all parts. Responses from the internal circuitry are specified from the point of view of the device. Output delay, for example, is specified as a maximum since worst-case operation of any device always provides data within that time.

- 11. For the tenal test, the transition is measured to the 1.5 V crossing point with datasheet loads. For the tDIS test, the transition is measured to the  $\pm 200 mV$  level from the measured steady-state output voltage with  $\pm 10 mA$  loads. The balancing voltage, VTH, is set at 3.5 V for Z-to-0 and 0-to-Z tests, and set at 0 V for Z-to-1 and 1-to-Z tests.

- 12. These parameters are only tested at the high temperature extreme, which is the worst case for leakage current.

### 11 x 10-bit Image Filter

03/02/98-LDS.2246-H

## 11 x 10-bit Image Filter