**Preliminary**

# D7002A

# Single-Chip Speech Compression IC for PC Voice/Telephony Applications

### **GENERAL DESCRIPTION**

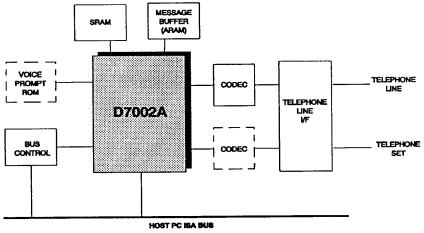

The D7002A chipset is a digital speech/signal processing subsystem that implements all the functions of speech compression, telephone line signal processing, memory management and voice data transfer between the HOST and the internal message buffer. Additional features include DIGITAL SPEAKER-PHONE<sup>TM</sup>, FLEXISPEECH<sup>TM</sup> variable-speed playback, and natural-sounding voice prompting for integrated PC applications. The D7002A is fully controlled by the PC through a simple interface protocol. The PC provides activation and control of all chipset functions.

The chipset's programmability enables a full range of PC Voice/Telephony features for the end user. The D7002A is a single-chip, digital signal processor that includes all of the necessary circuitry to interface with an external HOST, memory, and an analog front end.

### **FEATURES**

- High-quality speech compression of 6.8 kbits/second (9.4:1)

- Message buffer provides autonomous operation of PC's powered-down or operating state

- Efficient scheme for transferring voice messages between the message buffer and the host

- Complete set of telephone line monitoring and management with tone detection and generation

- FLEXISPEECH<sup>TM</sup> variable-speed playback

- DIGITAL SPEAKERPHONE<sup>TM</sup> high-quality hands-free telephone

- Voice/FAX Switchbers for speed dialing

- Suspend mode

- Simple host protocol for fast integration

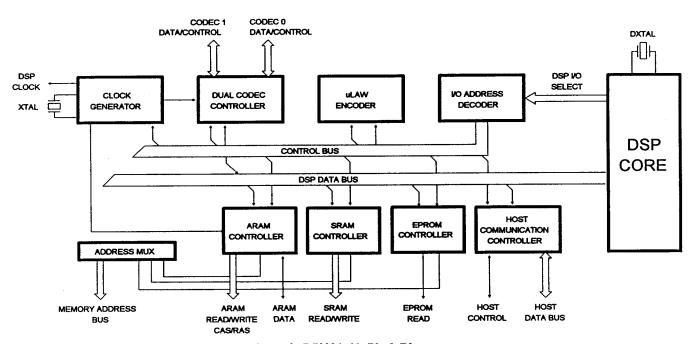

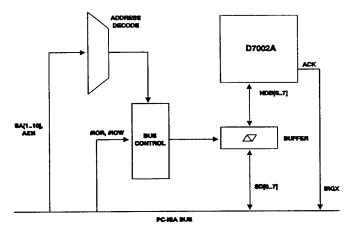

Figure 1. D7002A Block Diagram

All specifications are subject to change without prior notice

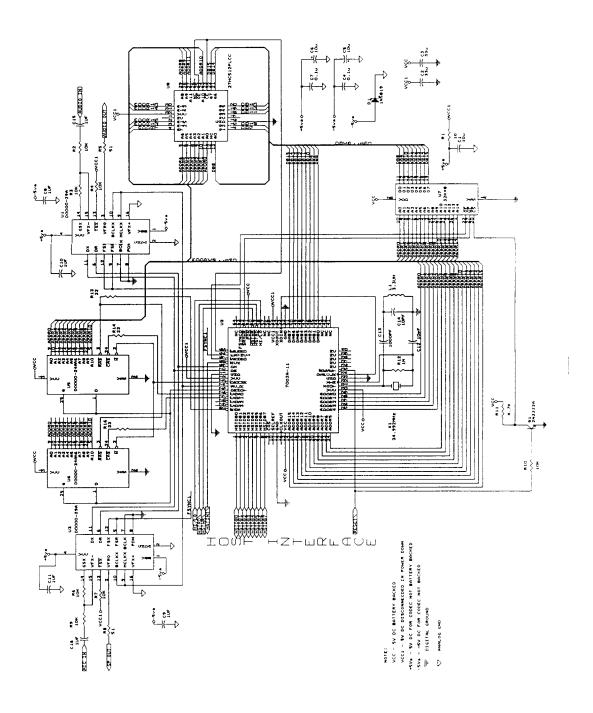

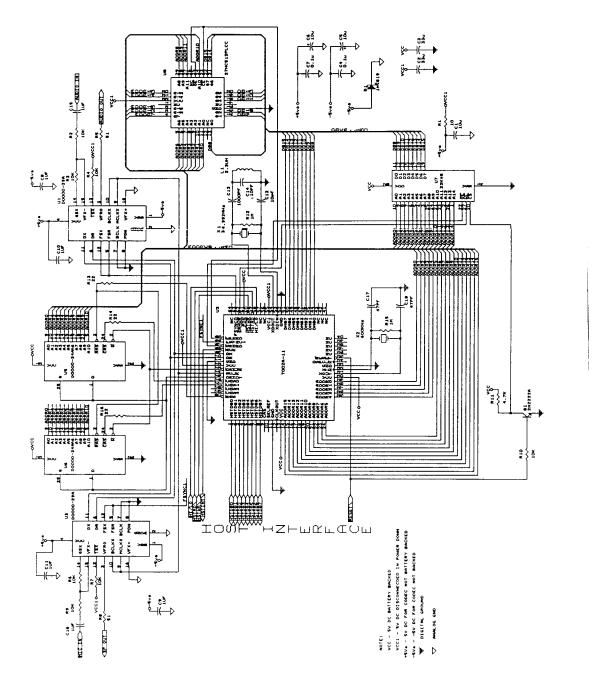

### **CHIPSET BASIC CONFIGURATION**

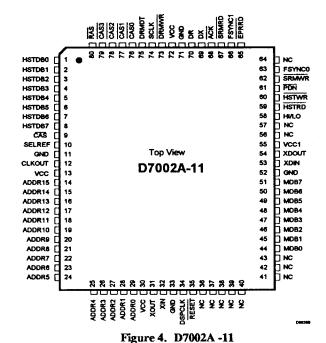

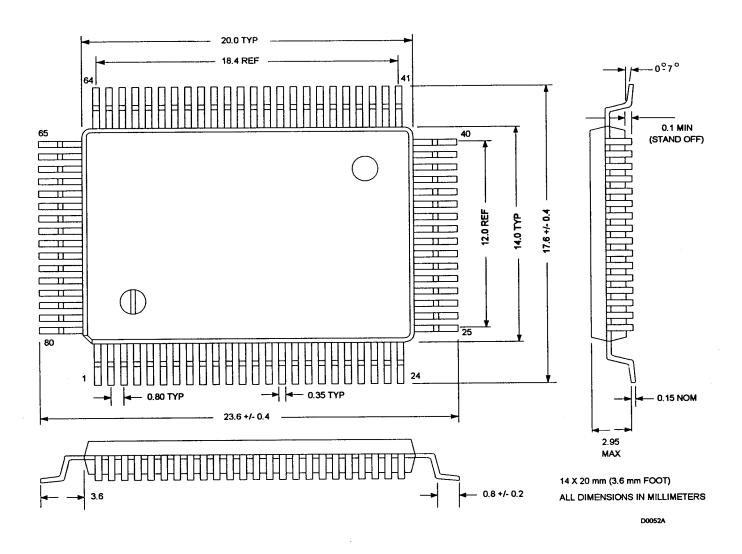

- D7002A-11 Digital Telephone Answering Device (TAD)

Processor (80-pin PQFP)—

1 each

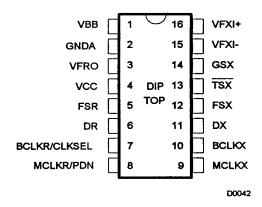

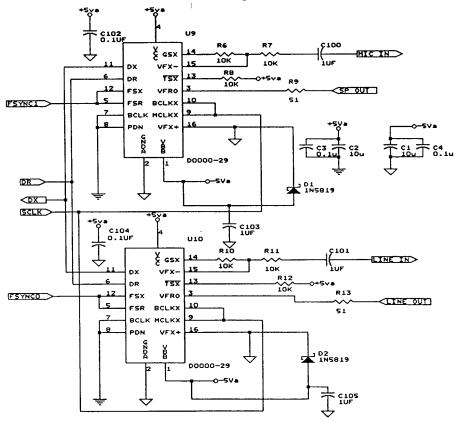

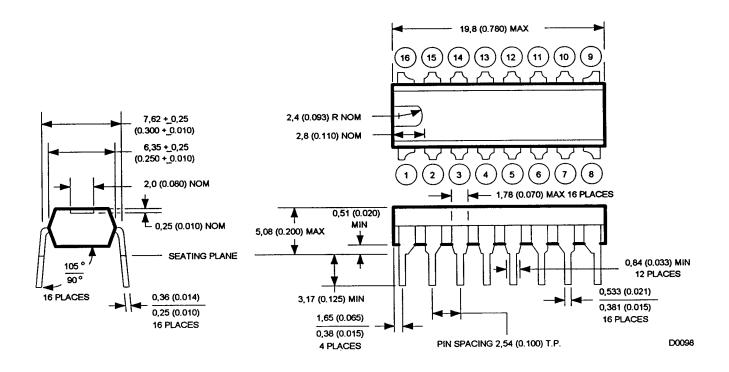

- D0000-29 Analog I/O Interface (16-pin DIP)—

1 each (2 for Speakerphone)

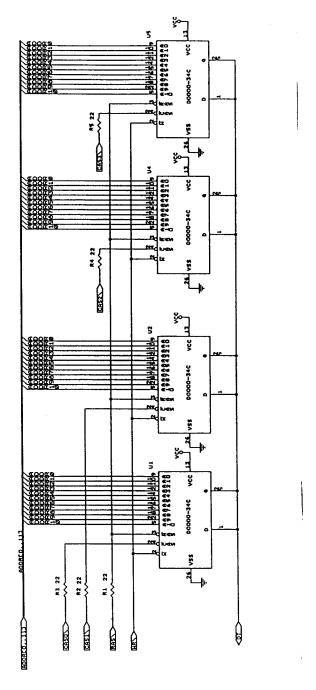

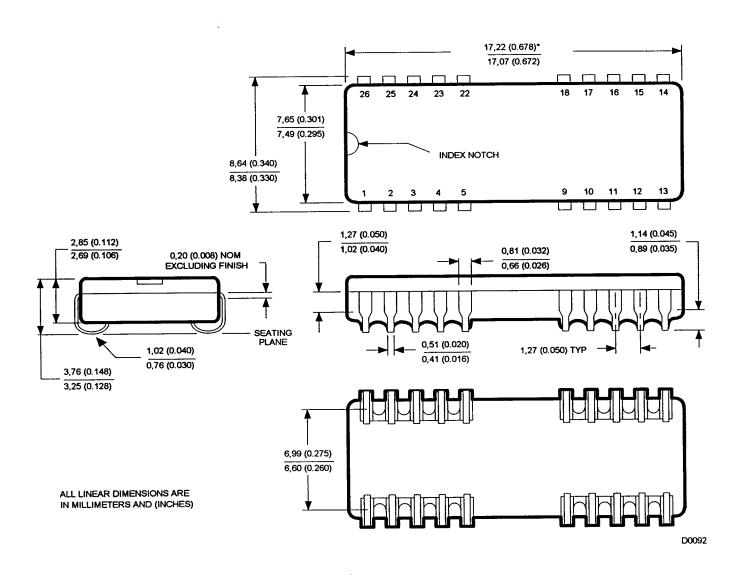

- D0000-34A 4-Mbit ARAM Message Memory (SOJ)— Up to four devices per chipset

Figure 2. D0000-29

### Notes:

- An 8K x 8 SRAM (access time is 100 ns) will be supplied by the customer for basic operation of the D7002A.

- A minimum of 16K x 8 SRAM is required for activation of FlexiSpeech.

- 3. For Voice Prompt storage an external EPROM/ROM (access time is 300 ns) is required. Each 8K x 8 block will support 9.5 seconds of voice prompts (up to 64K).

- 4. SRAM message storage will be supported for an SRAM size of 16K x 8 or more. Each additional 8 Kbytes increases the maximum length of the SRAM message by 9.5 seconds, in addition to the 5 seconds stored in the first 16 Kbytes.

Figure 3. D0000-34A (SOJ)

### PIN DESCRIPTIONS

| Pin          |     |        |                                                                                                                                                         |

|--------------|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name         | No. | I/O/Z* | Description                                                                                                                                             |

| HSTDB0 (LSB) | 1   | I/O/Z  | HOST DATA BUS. The HOST writes commands and reads status to/from the D6275A via this bus.                                                               |

| HSTDB1       | 2   | I/O/Z  | The HI/LO pin selects between the low byte and the high byte of the command/status. This bus is used                                                    |

| HSTDB2       | 3   | I/O/Z  | for input when HSTWR is low, and for output when HSTRD is low. It has high impedance when HSTWR and HSTRD are high or RESET is low.                     |

| HSTDB3       | 4   | I/O/Z  | HST WE also HSTED are might of RESET to low.                                                                                                            |

| HSTDB4       | 5   | I/O/Z  |                                                                                                                                                         |

| HSTDB5       | 6   | I/O/Z  | 1                                                                                                                                                       |

| HSTDB6       | 7   | I/O/Z  | <b>-</b>                                                                                                                                                |

| HSTDB7 (MSB) | 8   | I/O/Z  |                                                                                                                                                         |

| нисо         | 58  | I      | HIGH/LOW BYTE SELECT. When this signal is low, the HOST can read/write the low byte of the status/command. When high, the high byte is selected.        |

| HSTRD        | 59  | I      | HOST READ. When low, the HOST reads the low/high byte of the status word.                                                                               |

| HSTWR        | 60  | I      | HOST WRITE. When low the HOST writes commands to the D6275A via HSTDB 0-7.                                                                              |

| ACK          | 68  | 0      | HOST ACKNOWLEDGE. This pin goes low when the D6275A sends a status word to the HOST. It goes high when the HOST reads the high byte of the status word. |

| ADDR0 (LSB)  | 29  | 0      | EXTERNAL MEMORY ADDRESS BUS                                                                                                                             |

| ADDR1        | 28  | 0      |                                                                                                                                                         |

| ADDR2        | 27  | 0      |                                                                                                                                                         |

| ADDR3        | 26  | 0      |                                                                                                                                                         |

| ADDR4        | 25  | 0      |                                                                                                                                                         |

| ADDR5        | 24  | 0      |                                                                                                                                                         |

| ADDR6        | 23  | 0      |                                                                                                                                                         |

| ADDR7        | 22  | 0      |                                                                                                                                                         |

| ADDR8        | 21  | 0      |                                                                                                                                                         |

| ADDR9        | 20  | 0      |                                                                                                                                                         |

| ADDR10       | 19  | 0      |                                                                                                                                                         |

| ADDR11       | 18  | 0      |                                                                                                                                                         |

| ADDR12       | 17  | 0      |                                                                                                                                                         |

| ADDR13       | 16  | 0      |                                                                                                                                                         |

| ADDR14       | 15  | 0      |                                                                                                                                                         |

| ADDR15 (MSB) | 14  | 0      |                                                                                                                                                         |

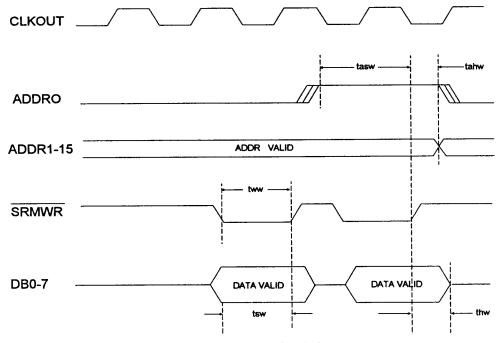

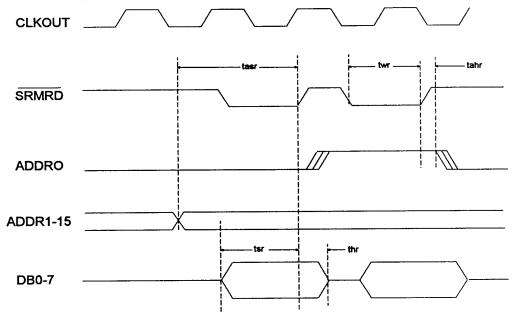

| SRMRD        | 67  | 0      | SRAM READ. (active low)                                                                                                                                 |

| SRMWR        | 62  | 0      | SRAM WRITE. (active low)                                                                                                                                |

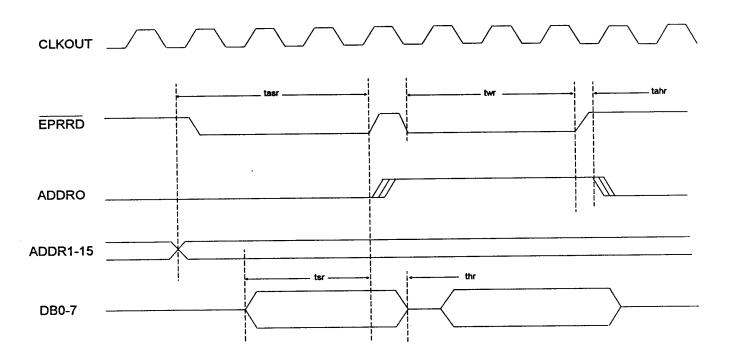

| EPRRD        | 65  | 0      | Voice prompt ROM/EPROM read (active low)                                                                                                                |

| MDB0 (LSB)   | 44  | I/O/Z  | External memory data bus.                                                                                                                               |

| MDB1         | 45  | I/O/Z  | _                                                                                                                                                       |

| MDB2         | 46  | I/O/Z  | _                                                                                                                                                       |

| MDB3         | 47  | I/O/Z  | _                                                                                                                                                       |

| MDB4         | 48  | I/O/Z  |                                                                                                                                                         |

| MDB5         | 49  | I/O/Z  | _                                                                                                                                                       |

| MDB6         | 50  | I/O/Z  |                                                                                                                                                         |

| MDB7 (MSB)   | 51  | I/O/Z  |                                                                                                                                                         |

| DRMDT        | 75  | I/O/Z  | ARAM DATA                                                                                                                                               |

| DRMWR        | 73  | 0      | ARAM WRITE (active low)                                                                                                                                 |

| CAS          | 9   | 0      | 16 MBIT ARAM CAS                                                                                                                                        |

| CAS0         | 76  | 0      | 4 Mbit ARAM CAS (0 for first ARAM, 1 for second ARAM, etc.)                                                                                             |

| CAS1_        | 77  | 0      |                                                                                                                                                         |

| CAS2         | 78  | 0      |                                                                                                                                                         |

# PIN DESCRIPTIONS (Continued)

| D7002A-11 | (DSP) |                                                  | •                                                                                                                                                                                           |

|-----------|-------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAS3      | 79    | 0                                                | 4 Mbit ARAM CAS (ARAM 4)                                                                                                                                                                    |

| RAS       | 80    | 0                                                | ARAM RAS                                                                                                                                                                                    |

| DR        | 70    | I                                                | Serial input for CODEC PCM data                                                                                                                                                             |

| DX        | 69    | 0                                                | Serial output for CODEC PCM data                                                                                                                                                            |

| FSYNC0    | 63    | 0                                                | Frame synchronization signal for CODEC 0                                                                                                                                                    |

| FSYNC1    | 66    | 0                                                | Frame synchronization signal for CODEC 1                                                                                                                                                    |

| SCLK      | 74    | 0                                                | Clock output to CODEC                                                                                                                                                                       |

| XIN       | 32    | I                                                | Crystal input pin for internal oscillator. The frequency must be 34.992 Mhz in single oscillator mode and 600 KHz +/-20% in dual oscillator mode.                                           |

| xour      | 31    | 0                                                | Crystal output pin for internal oscillator.                                                                                                                                                 |

| DSPCLK    | 34    | 0                                                | Crystal oscillator frequency output. This pin should be connected to XDIN when the D6275A is operating in single oscillator mode.                                                           |

| XDIN      | 53    | I                                                | Input pin from the crystal to the internal oscillator. When in dual oscillator mode, the crystal must be 34.99Mhz.  When in single oscillator mode, this pin should be connected to DSPCLK. |

| XDOUT     | 54    | 0                                                | rystal output pin for internal oscillator when in dual oscillator mode. When in single oscillator mode, this pin should be left unconnected.                                                |

| CLKOUT    | 12    | 0                                                | XDIN frequency divided by 4.                                                                                                                                                                |

| SELREF    | 10    | I                                                | ARAM refresh clock select. This pin should be left open when in single oscillator mode, and connected to GND in dual oscillator mode.                                                       |

| GND       | 52    | PWR                                              | GROUND PIN                                                                                                                                                                                  |

| GND       | 33    | PWR                                              | GROUND PIN                                                                                                                                                                                  |

| GND       | 11    | PWR                                              | GROUND PIN                                                                                                                                                                                  |

| GND       | 71    | PWR                                              | GROUND PIN                                                                                                                                                                                  |

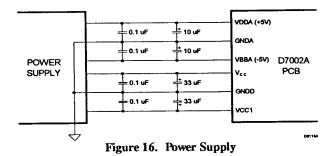

| Vcc       | 30    | PWR                                              | +5V battery backed-up power supply input. This power source should be connected to the ARAMs, SRAM and                                                                                      |

| Vcc       | 13    | PWR                                              | voice prompt ROM/EPROM.                                                                                                                                                                     |

| Vcc       | 72    | PWR                                              | 1                                                                                                                                                                                           |

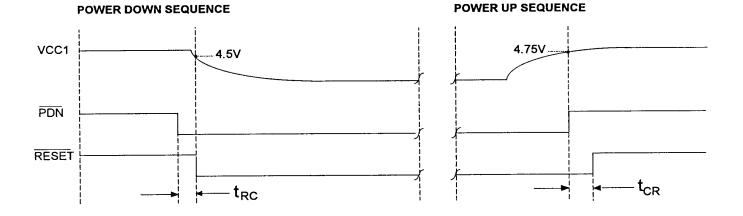

| VCC1      | 55    | PWR                                              | +5V non-backed-up power supply input.                                                                                                                                                       |

| PDN       | 61    | I                                                | VCC1 power fail sensor input. When a low level is detected on this pin, the D6275A enters power-down mode.                                                                                  |

| RESET     | 35    | I                                                | Reset input (active low)                                                                                                                                                                    |

| NC        | 56    | I                                                | These pins should be left unconnected.                                                                                                                                                      |

| NC        | 57    | I                                                |                                                                                                                                                                                             |

| NC        | 64    | I                                                | 1                                                                                                                                                                                           |

| NC        | 36    | I                                                | 1                                                                                                                                                                                           |

| NC        | 37    | I                                                | 1                                                                                                                                                                                           |

| NC        | 38    | ī                                                | 1                                                                                                                                                                                           |

| NC        | 39    | I                                                | 1                                                                                                                                                                                           |

| NC        | 40    | I                                                | 1                                                                                                                                                                                           |

| NC        | 41    | I                                                | 1                                                                                                                                                                                           |

| NC        | 42    | I                                                | 1                                                                                                                                                                                           |

| NC        | 43    | <del>                                     </del> | 4                                                                                                                                                                                           |

### PIN DESCRIPTIONS

| D0000-29 (A        | aalog I/O Int | terface) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|--------------------|---------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin                |               |          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Name               | No.           | I/O/Z*   | 2 de la constante de la consta |  |

| V <sub>BB</sub>    | 1             | PWR      | Negative power supply pin. VBB = -5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| GNDA               | 2             | PWR      | Analog ground. All signals are referenced to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| VFRO               | 3             | 0        | Analog output of the receive power amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Vcc                | 4             | PWR      | Positive power supply pin. VCC = +5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| FSR                | 5             | I        | Receive frame sync pulse which enables BCLKR to shift PCM data into DR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| DR                 | 6             | I        | Receive data input. PCM data is shifted into DR following the FSR leading edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| BCLKR/             | 7             | I        | Logic input which selects either 1.536 MHz/1.544 MHz or 2.048 MHz for master clock in synchronous mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| CLKSEL             |               |          | and BCLKX is used for both transmit and receive directions. This input should be tied to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| MCLKR/             | 8             | I        | Receive master clock. When MCLKR is connected continuously low, MCLKX is selected for all internal timing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| PDN                |               |          | When MCLKR is connected continuously high, the device is powered down.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| MCLKX              | 9             | I        | Transmit master clock. Must be 1.536 MHz, 1.544 MHz or 2.048 MHz. May be asynchronous with MCLKR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                    |               |          | Best performance is realized from synchronous operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| BCLKX              | 10            | I        | The bit clock which shifts out the PCM data on DX. May vary from 64 KHz to 2.048 MHz, but must be synchronous with MCLKx.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| DX                 | 11            | O/Z      | PCM data output which is enabled by FSX.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| FSX                | 12            | I        | Transmit frame sync pulse input which enables BCLKX to shift out the PCM data on DX. FSX is an 8 KHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                    |               |          | pulse train.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| TSX                | 13            | 0        | Open drain output which pulses low during the encoder time slot.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| GSX                | 14            | 0        | Analog output of the transmit input amplifier. Used to externally set gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| VF <sub>X</sub> I- | 15            | 1        | Inverting input of the transmit input amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| VFxI+              | 16            | ī        | Non-inverting input of the transmit input amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

### PIN DESCRIPTIONS

| Pin  |     | İ      |                                                                                                             |  |

|------|-----|--------|-------------------------------------------------------------------------------------------------------------|--|

| Name | No. | I/O/Z* | Description                                                                                                 |  |

| Α0   | 9   | I      | Row and column address bits. Row address bits are latched in the chip by the RAS signal. Column address bit |  |

| A1   | 10  | I      | are latched in by the CAS signal.                                                                           |  |

| A2   | 11  | I      |                                                                                                             |  |

| A3   | 12  | I      |                                                                                                             |  |

| A4   | 14  | I      | 1                                                                                                           |  |

| A5   | 15  | I      | 1                                                                                                           |  |

| A6   | 16  | I      |                                                                                                             |  |

| A7   | 17  | I      | 1                                                                                                           |  |

| A8   | 18  | I      | 1                                                                                                           |  |

| A9   | 22  | I      |                                                                                                             |  |

| A10  | 5   | I      | 1                                                                                                           |  |

| RAS  | 3   | I      | Row address strobe                                                                                          |  |

| CAS  | 24  | I      | Column address strobe                                                                                       |  |

| D    | 1   | I      | Data input                                                                                                  |  |

| Q    | 25  | 0      | Data output                                                                                                 |  |

| w    | 2   | I      | Write enable input which selects read or write mode                                                         |  |

| VCC  | 13  | T -    | +5V supply                                                                                                  |  |

| VSS  | 26  | -      | Ground                                                                                                      |  |

| TF   | 4   | I      | No connection                                                                                               |  |

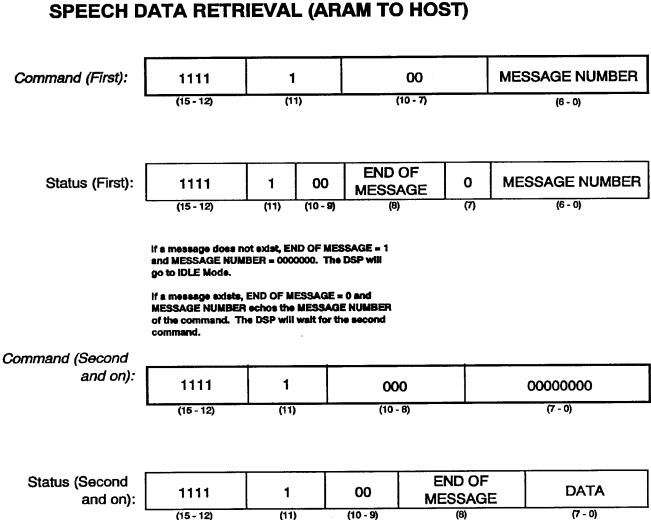

#### **FUNCTIONAL DESCRIPTION**

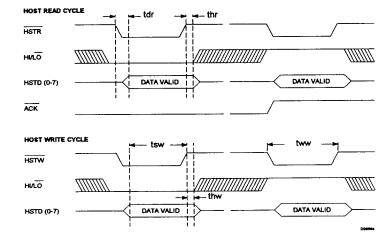

#### **HOST Interface**

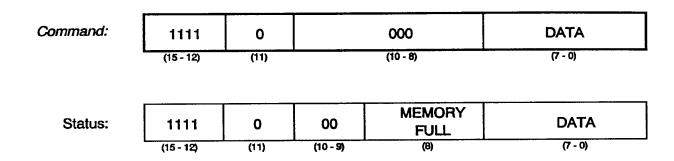

The host interface is an 8-bit parallel data port, used for control and status information transfer. The host controls the operation of the D7002A using a simple command protocol. D7002A status information is updated after each command.

The command and status protocol enables the host to have full control over the functions of the D7002A. The protocol is described in the next section.

### Voice Message Storage—Incoming and Outgoing Messages

The D7002A message storage uses a proprietary high-quality speech compression technique at a rate of 6.8 Kbps. The compression technique used is enhanced by an error correction algorithm that enables the use of ARAM memory without degradation in speech quality.

The D7002A chipset supports up to 40.8 minutes of voice storage. Voice messages are stored in 4-Mbit ARAMs up to a maximum of 16 Megabits. Each 4-Mbit ARAM has a storage capacity of 612 seconds. The chipset supports a total of up to 64 variable-length incoming and outgoing messages. Multiple outgoing messages are supported.

A single message can be compressed and stored in the upper part of the external SRAM. The SRAM message can be used as an OGM and, due to the lower power consumption of the SRAM, this message can be backed up for much longer periods. The SRAM message is not supported in an 8 Kbyte configuration. SRAM message recording will be stopped when there is no additional space in the SRAM. No message number will be allocated to the SRAM message; a new SRAM message is recorded over the old one.

During recording, the D7002A performs telephone line monitoring. The HOST can stop recording, and delete the last n\*0.9 seconds from the memory using a Record command with Tail Cut factor.

The D7002A is capable of reporting to the HOST the status of the currently available ARAM memory storage space, as well as the overall status of the ARAMs and SRAM, and the number of recorded messages.

# Digital Voice-Activated Recording (VOX)

Digital voice activity detection is implemented in the D7002A and activated only in Record mode. Compression and storage of the speech signal starts upon a positive result from the voice activity detector. The voice activity detector output is reported to the HOST via a status bit every 28 ms when in Record mode. The HOST reads this status information and decides whether to stop recording this message.

### Message Playback

The D7002A supports random access for playback of any recorded message. If SRAM size is 16 Kbytes or more, three playback speeds can be supported using the FLEXISPEECH technique: normal speed (x1), high speed (x1.3) and slow speed (x0.7). Playback from the beginning of a message or from a predefined offset time may be performed. During playback, the D7002A monitors the telephone line.

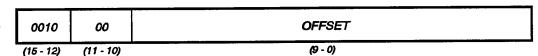

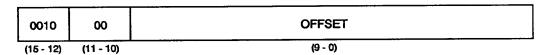

Message playback can be stopped by using the Pause command, which is initiated by the HOST. After Pause, playback may be resumed from the same point. Normally, during playback, the status word will contain information about the line and the playback status. If the Read Offset bit (bit 10) was set, the D7002A responds with a time offset, which corresponds to the time elapsed from the beginning of the current message.

### **Message Deletion**

The D7002A enables selective deletion of any prerecorded message from memory. After each deletion the message directory is updated accordingly. To improve memory utilization, the D7002A supports "Garbage Collection," which eliminates empty spaces in the message memory. No deletion of the SRAM message is supported.

### Message Time Stamp

The HOST may send a 16-bit time indication to the D7002A, which can be used for time stamping the recorded message. Time stamp for the SRAM message is not supported.

### **DTMF Detection**

DTMF detection is implemented by the D7002A in software. This function may be used for remote operation of the answering device. The identification code of one of 12 detected DTMF signals is transferred to the host for further processing.

### **Tone Generation**

16 DTMF tones and 15 other general-purpose tones can be generated by the D7002A. DTMF signals are generated in accordance with the requirements of EIA RS-470. Voice processing is disabled during tone generation. Each tone may be selected by a host controller command. Thus, the duration of the tone is controlled by the host. The host processor also controls the tone signal level.

### **Call Progress Tone Detection**

The D7002A monitors the line for incoming telephone line signals and detects the presence of call progress tones in a predefined frequency region. The D7002A supports call progress tone detection by utilizing one of two filter/detectors: a wide filter (330-650 Hz) and a narrow one (330-500 Hz). The filter is selected during initialization (Self Test). Indication of the presence of call progress tones is transferred to the HOST, and may be used for terminating recording.

### **FAX Calling Tone Detection**

The D7002A monitors the line for incoming telephone line signals and detects the presence of a FAX calling tone (CNG—1100Hz). Indication of CNG tone presence is transferred to the host and may be used for Voice-FAX switch implementation.

### Ringback Signal Generation

A ringback signal is generated in order to provide audio feedback to the FAX sending party. The ringback signal is a dual tone signal of 440 and 480 Hz to simulate a jingling sound.

### Speed Dial Telephone Number Storage

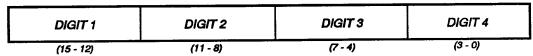

The host may store up to 32 telephone numbers, each with up to 16 digits, in the SRAM.

### Self Test and Parameter Initialization

The D7002A supports a self test function which is responsible for testing and mapping of both the ARAMs and the SRAM. The results of each device test are returned to the HOST. The initialization command can set the type of call progress tone filter, ARAM refresh mode and CODEC type.

### Voice Prompt Generation