# LH0082 Z80 CTC Counter Timer Circuit

# Description

The Z80 product line is a complete set of microcomputer components, development systems and support software. The Z80 microcomputer component set includes all of the circuits necessary to build high-performance microcomputer systems with virtually no other logic and a minimum number of low cost standard memory elements.

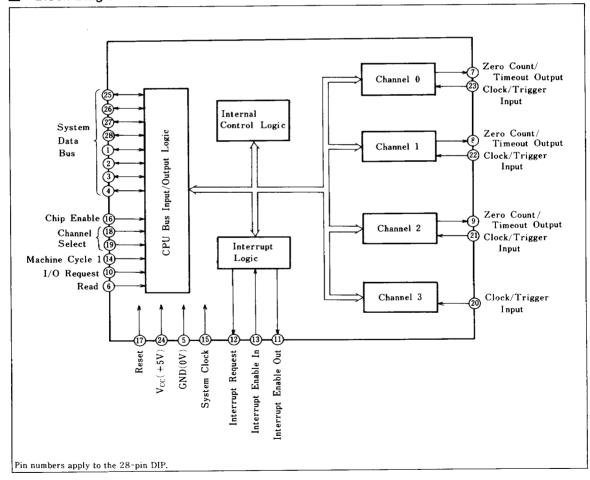

The LH0082 Z80 CTC (Z80 CTC for short below) is a programmable, four channel device that provides counting and timing functions for the Z80 CPU. The Z80 CPU configures the Z80 CTC's four independent channels to operate under various modes and conditions as required.

The LH0082A Z80A and LH0082B Z80B CTC are the high speed version which can operate at the 4MHz and 6MHz system clock, respectively.

### **Features**

- 1. Four independent programmable 8-bit counter/16-bit timer channels

- 2. N-channel silicon gate process

- 3. Each channel may be selected to operate in either a counter mode or timer mode

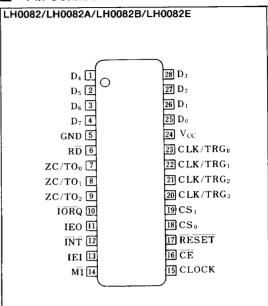

#### Pin Connections

#### LH0082U/LH0082AU/LH0082BU LH0082M/LH0082AM 32 31 30 29 NC 34 22 NC 39 NC GND[7 21 NC 0 NC 35 38 NC NC 8 INT 36 20 D<sub>7</sub> $_{37}\,\mathrm{V}_{\mathrm{CC}}$ RD 9 19 D<sub>6</sub> IE1 37 36 NC ZC/TO<sub>0</sub> 10 M1 38 18 D<sub>5</sub> 35 CLK/TRG<sub>0</sub> NC II 17 D₄ CLK 39 ZC/TO<sub>1</sub> 12 34 NC CE 40 16 D<sub>3</sub> 33 CLK/TRG<sub>1</sub> ZC/TO<sub>2</sub> 13 RESET 41 $15 D_2$ 32 CLK/TRG<sub>2</sub> IORQ 14 $\mathbb{I} \mathbf{I} D_1$ CSO 42 31 CLK/TRG₃ 13 NC NC 15 NC 43 30 NC 12 NC IEO 16 NC 44 29 CS<sub>1</sub> NC 17 CLK/TRG2 CLK/TRG1 GND CLK/TRG3 CLK/ Top View

\*The GND pins must be connected to the GND level.

SHARP -

- Programmable interrupts on counter or timer states

- 5. When the down-counter reaches the zero count the CTC reloads its time constant automatically and continues it's channel operation

- 6. Readable down counter

- 7. Selectable 16 or 256 clock prescaler for each timer channels

- 8. Selectable positive or negative trigger may initiate timer or counter operation

- Three channels have ZC/TO outputs capable of driving Darlington transistors

- 10. Vectored daisy chain priority interrupt logic included

- 11. Single +5V power supply and single phase clock

- 12. All inputs and outputs fully TTL compatible

- 13. 28-pin DIP (DIP28-P-600) 44-pin QFP (QFP44-P-1010A)

- 44-pin QFJ (QFJ44-P-S650)

### Ordering Information

| Product         | Z80 CTC | Z80A CTC | Z80B CTC | Z80E CTC | Package    | Operating                        |

|-----------------|---------|----------|----------|----------|------------|----------------------------------|

| Clock frequency | 2.5MHz  | 4MHz     | 6MHz     | 8MHz     | гаскаде    | temperature                      |

|                 | LH0082  | LH0082A  | LH0082B  | LH0082E  | 28-pin DIP | 0°C to + 70°C                    |

| Model No.       | LH0082M | LH0082AM |          |          | 44-pin QFP | 0°C to +60°C                     |

|                 | LH0082U | LH0082AU | LH0082BU |          | 44-pin QFJ | $0^{\circ}$ C to $+70^{\circ}$ C |

# Block Diagram

SHARP -

# Pin Description

| Pin                               | Meaning              | I/O                   | Function                                                                                                                                                                                                |

|-----------------------------------|----------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D <sub>0</sub> -D <sub>7</sub>    | Data bus             | Bidirectional 3-state | System data bus.                                                                                                                                                                                        |

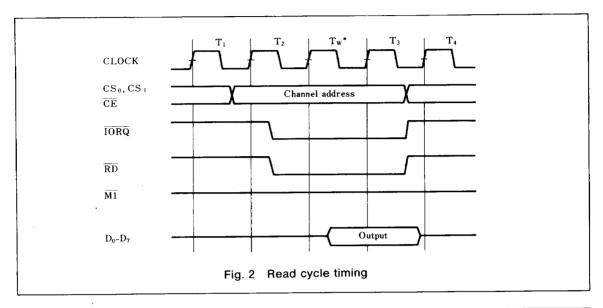

| CS <sub>0</sub> , CS <sub>1</sub> | Channel select       | I                     | Selects one of the four independent channels.                                                                                                                                                           |

| CE                                | Chip enable          | I                     | Active "Low". A Low enables the CPU to transmit and receive control words and data.                                                                                                                     |

| CLOCK                             | System clock         | I                     | Standard Z80 system clock used for internal synchronization signals.                                                                                                                                    |

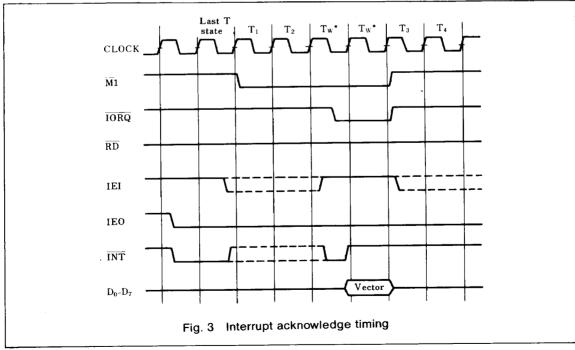

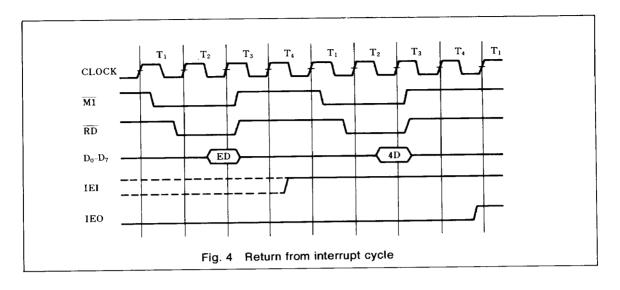

| <u>M1</u>                         | Machine cycle one    | I                     | Active "Low". Indicates that the CPU is acknowledging an interrupt, when both $\overline{\text{M1}}$ and $\overline{\text{IORQ}}$ are active.                                                           |

| ĪŌŖQ                              | I/O request          | I                     | Active "Low". Read operation when RD is active, and write operation when it is not active. Indicates the CPU is acknowledging an interrupt, when both $\overline{IORQ}$ and $\overline{M1}$ are active. |

| RD                                | Read cycle status    | I                     | Active "Low". Read operation when active.                                                                                                                                                               |

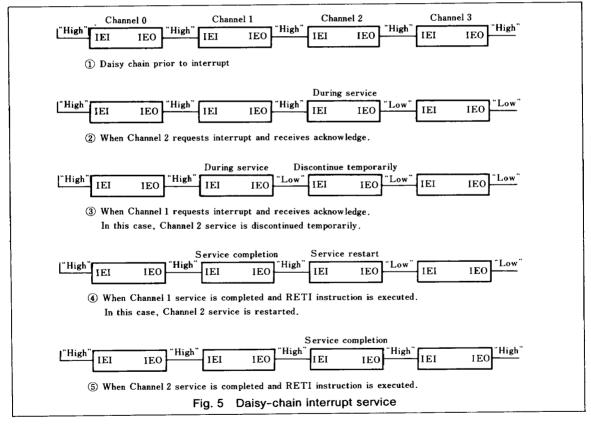

| IEI                               | Interrupt enable in  | I                     | Active "High". Forms a priority-interrupt daisy-chain.                                                                                                                                                  |

| IEO                               | Interrupt enable out | 0                     | Active "High". Forms a priority-interrupt daisy-chain.                                                                                                                                                  |

| ĪNT                               | Interrupt request    | Open drain, O         | Active "Low". Active when requesting an interrupt.                                                                                                                                                      |

| RESET                             | Reset                | I                     | Active "Low". Resets the interrupt bits.                                                                                                                                                                |

| CLK/TRG <sub>0</sub> -            | External clock/timer |                       | Counter/timer input for four independent channels.                                                                                                                                                      |

| CLK/TRG <sub>3</sub>              | trigger input        | I .                   | Counter/timer input for four independent channels.                                                                                                                                                      |

| ZC/TO <sub>0</sub> -              | External clock/timer | 0                     | Active "High". 0/1/2 output for four independent chan-                                                                                                                                                  |

| ZC/TO <sub>2</sub>                | trigger out          | 0                     | nels. No output terminal at channel 3.                                                                                                                                                                  |

# Absolute Maximum Ratings

| Parameter             | Symbol          | Ratings        | Unit            | Note |

|-----------------------|-----------------|----------------|-----------------|------|

| Input voltage         | V <sub>IN</sub> | -0.3 to $+7.0$ | V               |      |

| Output voltage        | $V_{OUT}$       | -0.3  to  +7.0 | V               |      |

| Operating temperature | Topr            | 0  to  +70     | ${\mathfrak C}$ | 1    |

| Storage temperature   | Tstg            | -65  to  +150  | $^{\circ}$ C    |      |

Note 1: Topr=0 to  $\pm 60$ °C for 44-pin QFP.

# DC Characteristics

$(V_{CC} = 5V \pm 5\%, Ta = 0 \text{ to } +70^{\circ}\text{C}^{\text{Note 1}})$

| Parameter                      | Symbol             | Conditions                             | MIN.           | TYP. | MAX.           | Unit    |

|--------------------------------|--------------------|----------------------------------------|----------------|------|----------------|---------|

| Clock input low voltage        | V <sub>ILC</sub>   |                                        | -0.3           |      | 0.45           | V       |

| Clock input high voltage       | VIHC               |                                        | $V_{cc} - 0.6$ |      | $V_{CC} + 0.3$ | V       |

| Input low voltage              | V <sub>IL</sub>    |                                        | -0.3           |      | 0.8            | V       |

| Input high voltage             | V <sub>IH</sub>    | · .                                    | 2.0            |      | $V_{cc}$       | V       |

| Output low voltage             | V <sub>OL</sub>    | $I_{OL} = 2 m A$                       |                |      | 0.4            | V       |

| Output high voltage            | V <sub>OH</sub>    | $I_{OH} = -250 \mu\text{A}$            | 2.4            |      |                | V       |

| Supply current                 | $I_{CC}$           | $t_c = 400 ns$                         |                |      | 120            | m A     |

| Input leakage current          | ILI                | $0 \le V_{IN} \le V_{CC}$              |                |      | 10             | μΑ      |

| 3-state output leakage current | I <sub>LOH</sub>   | $2.4V \leq V_{OUT} \leq V_{CC}$        |                |      | 10             | $\mu$ A |

| 3-state output leakage current | ILOL               | $V_{OUT} = 0.4 V$                      |                |      | 10             | μA      |

| Darlington drive current       | $I_{\mathrm{OHD}}$ | $V_{OH} = 1.5 V, R_{EXT} = 390 \Omega$ | -1.5           |      |                | m A     |

Note 1: Ta=0 to +60℃ for 44-pin QFP.

# Capacitance

$(f=1 \text{MHz}, Ta=25 ^{\circ}\text{C})$

|                    |                    |                          |      | r    |      |      |

|--------------------|--------------------|--------------------------|------|------|------|------|

| Parameter          | Symbol             | Conditions               | MIN. | TYP. | MAX. | Unit |

| Clock capacitance  | C <sub>CLOCK</sub> |                          | 1    |      | 20   | pF   |

| Input capacitance  | C <sub>IN</sub>    | Unmeasured pins returned |      |      | 5    | pF   |

| Output capacitance | COUT               | to ground                |      |      | 10   | pF   |

SHARP

321

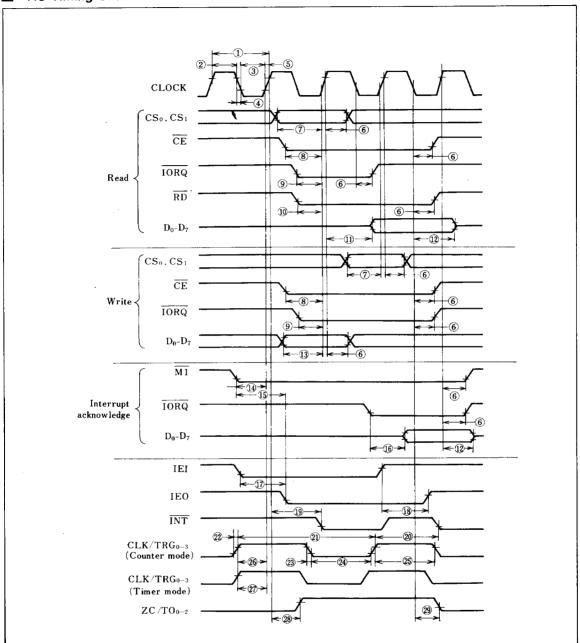

### **AC Characteristics**

$(V_{CC} = 5V \pm 5\%, Ta = 0 \text{ to} + 70^{\circ}\text{C})$

| No.   Parameter   Symbol   MIN.   MAX.   M |     | _                               | LH0082 LH0082A LH0082B |      | LH00         | )82E | Unit        | Note |            |      |          |     |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------|------------------------|------|--------------|------|-------------|------|------------|------|----------|-----|------|

| Clock width (high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | No. | Parameter                       | Symbol                 | MIN. | MAX.         | MIN. | MAX.        |      |            | MIN. | MAX.     | Omt | Note |

| Clock width (low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1   | Clock cycle time                | TcC                    | 400  | (Note 1)     | 250  | (Note 1)    | 165  | (Note 1)   | 125  | (Note 1) | ns  |      |

| Clock fall time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2   | Clock width (high)              | TwCh                   | 170  | 2000         | 105  | 2000        | 65   | 2000       | 55   | 2000     | ns  |      |

| 5         Clock rise time         TrC         30         30         20         10         ns           6         All hold times         Th         0         0         0         0         ns           7         CS to clock 1 setup time         TSCS (C)         250         160         100         80         ns           8         CE to clock 1 setup time         TSCE (C)         200         150         100         75         ns           9         IORQ 1 to clock 1 setup time         TSCD (C)         250         115         70         60         ns           10         RD 1 to clock 1 setup time         TSCD (C)         240         115         70         60         ns           11         Clock 1 to data out delay         TdC (DO)         240         115         70         60         ns           12         Clock 1 to data out delay         TdC (DO)         240         110         90         75         ns           13         Data in to clock 1 setup time         TSDI (C)         60         50         40         30         ns           14         Mi to look 1 setup time         TSDI (C)         20         10         130         10         ns<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3   | Clock width (low)               | TwCl                   | 170  | 2000         | 105  | 2000        | 65   | 2000       | 55   | 2000     | ns  |      |

| Stock   Sto  | 4   | Clock fall time                 | TfC                    |      | 30           |      | 30          |      | 20         |      | 10       | ns  |      |

| The first of the content of the co | 5   | Clock rise time                 | TrC                    |      | 30           |      | 30          |      | 20         |      | 10       | ns  |      |

| 8         CE to clock 1 setup time         TsCE (C)         200         150         100         75         ns           9         IORQ↑ to clock ↑ setup time         TsIO (C)         250         115         70         60         ns           10         RD↓ to clock ↑ setup time         TsRD (C)         240         115         70         60         ns           11         Clock ↑ to data out delay         TdC (DO2)         240         200         130         100         ns           12         Clock ↑ to data out float delay         TdC (DO2)         230         110         90         75         ns           13         Data in to clock ↑ setup time         TsDI (C)         60         50         40         30         ns           14         Mi to clock ↑ setup time         TsMI (C)         210         90         70         55         ns           15         Mi ↓ to IEO ↓ delay (interrupt immediately preceding MI)         TdMI (IEO)         300         190         130         90         ns         3           16         IORQ ↓ to data out delay (interrupt immediately preceding MI)         TdMI (IEO)         340         160         110         80         ns         3           18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6   | All hold times                  | Th                     | 0    |              | 0    |             | 0    |            | 0    |          | ns  |      |

| ORQ   to clock   setup time   TsIO (C)   250   1115   70   60   ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7   | CS to clock † setup time        | TsCS (C)               | 250  |              | 160  |             | 100  |            | 80   |          | ns  |      |

| 10   RD ↓ to clock ↑ setup time   TsRD (C)   240   115   70   60   ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8   | CE to clock † setup time        | TsCE (C)               | 200  |              | 150  |             | 100  |            | 75   |          | ns  |      |

| 11   Clock   10 data out delay   TdC (DO)   240   200   130   100   ns   2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9   | IORQ † to clock † setup time    | TsIO (C)               | 250  |              | 115  |             | 70   |            | 60   |          | ns  |      |

| 12   Clock   to data out float delay   TdC (DOz)   230   110   90   75   ns     13   Data in to clock   setup time   TsDI (C)   60   50   40   30   ns     14   Mi to clock   setup time   TsMI (C)   210   90   70   55   ns     15   Mi   to IEO   delay (interrupt immediately preceding MI)   TdMI (IEO)   300   190   130   90   ns   3     16   IORQ   to data out delay (INTA cycle)   TdIEI (IEOf)   190   130   100   80   ns   2     17   IEI   to IEO   delay   TdIEI (IEOf)   190   130   100   80   ns   3     18   IEI   to IEO   delay   TdIEI (IEOf)   220   160   110   80   ns   3     19   Clock   to INT   delay   TdC (INT)   TcC+200   TcC+140   TcC+120   TcC+100   ns   4     19   CLK/TRG   to INT   delay   tsCTR (C) satisfied   TdCLK (INT)   TcC+200   TcC+300   TcC+300   TcC+130   TcC+100   ns   5     20   CLK/TRG cycle time   TsCTR   2TcC   2TcC   2TcC   2TcC   ns   5     21   CLK/TRG frise time   TrCTR   50   50   40   35   ns     22   CLK/TRG frise time   TrCTR   50   50   40   35   ns     23   CLK/TRG width (high)   TwCTR1   200   200   120   100   ns     24   CLK/TRG   to clock   setup time for immediate count   CLK/TRG   to clock   setup time for immediate count   TsCTR (C)   210   210   150   110   ns   4     24   CLK/TRG   to clock   setup time for enabling of prescaler on following clock   TcC/TO   delay   TdC (ZC/TOr)   260   190   140   110   ns   4     25   CLK/TRG   to clock   setup time for enabling of prescaler on following clock   TdC/CZ/TOr   260   190   140   110   ns   4     26   Clock   to ZC/TO   tdelay   TdC (ZC/TOr)   260   190   140   110   ns   4                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10  | RD ↓ to clock ↑ setup time      | TsRD (C)               | 240  |              | 115  |             | 70   |            | 60   |          | ns  |      |

| 13   Data in to clock   setup time   TSDI (C)   60   50   40   30   ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11  | Clock to data out delay         | TdC (DO)               |      | 240          |      | 200         |      | 130        |      | 100      | ns  | 2    |

| 14 Mi to clock † setup time   TsMI (C)   210   90   70   55   ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 12  | Clock ↓ to data out float delay | TdC (DOz)              |      | 230          |      | 110         |      | 90         |      | 75       | ns  |      |

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13  | Data in to clock † setup time   | TsDI (C)               | 60   |              | 50   |             | 40   |            | 30   |          | ns  |      |

| Table   Tabl | 14  | MI to clock † setup time        | TsMl (C)               | 210  |              | 90   |             | 70   |            | 55   |          | ns  |      |

| Immediately preceding MI    Idah (IDS)   Idah (IDS)   Idah (IDRQ   to data out delay (INTA cycle)   TdIO (DOI)   340   160   110   80   ns   2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1.5 | MI ↓ to IEO ↓ delay (interrupt  | TAMI (IEO)             |      | 300          |      | 190         |      | 130        |      | 90       | ns  | 3    |

| Total   Tota | 15  | immediately preceding MI)       | Tawn (IEO)             |      | 300          |      | 150         |      | 100        |      |          |     |      |

| INTA cycle   Tallo (BOI)   Sto   Foot   Fo | 1.6 | IORQ ↓ to data out delay        | TAIO (DOI)             |      | 340          |      | 160         |      | 110        |      | 80       | ns  | 2    |

| Total   Tota | 10  | (INTA cycle)                    | Tulo (DOI)             |      | 340          |      |             |      |            |      |          |     |      |

| Table   Tabl | _17 | IEI ↓ to IEO ↓ delay            | TdIEI (IEOf)           |      | 190          |      | 130         |      | 100        |      | 80       | ns  | 3    |

| Classified   Cla | 1.0 | IEI ↑ to IEO ↑ delay            | Talel (IEOr)           |      | 220          |      | 160         |      | 110        |      | 80       | ns  | 3    |

| CLK/TRG   to INT   delay tsCTR (C) satisfied   TdCLK (INT)   tsCTR (C) not satisfied   TrCTR   TrCTR | 10  | (after ED decode)               | Tuibi (ibor)           |      |              |      | 100         |      |            |      |          | -   | ļ    |

| tsCTR (C) satisfied                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19  | Clock † to INT ↓ delay          | TdC (INT)              |      | TcC+200      |      | TcC+140     |      | TeC+120    |      | TcC+100  | ns  | 4    |

| tsCTR (C) satisfied         TdCLK (INT)         2πcC+330         25         2 cLK/TRG fall time         T mcCTR         50         50         40         35         ns           25         CLK/TRG width (high)         TwCTRh         200         200         120         100         ns         5           26         CLK/TRG ↑ to clock ↑ setup time for immediate count         TsCTR (Cs)         300         210         150         110         ns         5           27         time for enabling of prescaler on following clock ↑         TsCTR (Ct)         210         210         150         110         ns         4           28         Clock ↑ to Zc/TO ↑ delay         TdC (Zc/Tor)         260                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | CLK/TRG ↑ to INT ↓ delay        |                        |      | TeC+230      |      | TcC+160     |      | TeC+130    |      | TcC+110  | ns  | 5    |

| CLK/TRG   to INT   delay tsCTR (C) not satisfied   2TcC+530   2TcC+370   2TcC+280   2TcC+190   ns   5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20  | tsCTR (C) satisfied             | TACLK (INT)            |      | 100 1000     |      |             |      |            |      |          | 1   |      |

| tsCTR (C) not satisfied         TsCTR         2TcC         2TcC         2TcC         2TcC         2TcC         ns         5           22 CLK/TRG rise time         TrCTR         50         50         40         35         ns         5           23 CLK/TRG fall time         TfCTR         50         50         40         35         ns           24 CLK/TRG width (low)         TwCTRI         200         200         120         100         ns           25 CLK/TRG width (high)         TwCTRh         200         200         120         100         ns           26 CLK/TRG † to clock † setup time for immediate count         TsCTR (Cs)         300         210         150         110         ns         5           27 time for enabling of prescaler on following clock †         TsCTR (Ct)         210         210         150         110         ns         4           28 Clock † to ZC/TO † delay         TdC (ZC/TOr)         260         190         140         110         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20  | CLK/TRG ↑ to INT ↓ delay        | rucer (iii)            |      | 2TcC+530     |      | 2TcC + 370  |      | 2TcC ± 280 |      | 2TcC+190 | ns  | 5    |

| 22         CLK/TRG rise time         TrCTR         50         50         40         35         ns           23         CLK/TRG fall time         TfCTR         50         50         40         35         ns           24         CLK/TRG width (low)         TwCTRI         200         200         120         100         ns           25         CLK/TRG width (high)         TwCTRh         200         200         120         100         ns           26         CLK/TRG to clock t setup time for immediate count         TsCTR (Cs)         300         210         150         110         ns         5           27         time for enabling of prescaler on following clock t         TsCTR (Ct)         210         210         150         110         ns         4           28         Clock t to ZC/TO t delay         TdC (ZC/TOr)         260         190         140         110         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | tsCTR (C) not satisfied         |                        |      | 21001000     |      | -           | l    |            |      |          |     |      |

| 23         CLK/TRG fall time         TfCTR         50         50         40         35         ns           24         CLK/TRG width (low)         TwCTRI         200         200         120         100         ns           25         CLK/TRG width (high)         TwCTRh         200         200         120         100         ns           26         CLK/TRG to clock t setup time for immediate count         TsCTR (Cs)         300         210         150         110         ns         5           27         time for enabling of prescaler on following clock t         TsCTR (Ct)         210         210         150         110         ns         4           28         Clock t to ZC/TO t delay         TdC (ZC/TOr)         260         190         140         110         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21  | CLK/TRG cycle time              |                        | 2TcC |              | 2TcC |             | 2TcC | <u> </u>   | 2TcC |          |     | 5    |

| 24         CLK/TRG width (low)         TwCTRI         200         200         120         100         ns           25         CLK/TRG width (high)         TwCTRh         200         200         120         100         ns           26         CLK/TRG † to clock † setup time for immediate count         TsCTR (Cs)         300         210         150         110         ns         5           27         time for enabling of prescaler on following clock †         TsCTR (Ct)         210         210         150         110         ns         4           28         Clock † to ZC/TO † delay         TdC (ZC/TOr)         260         190         140         110         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _22 | CLK/TRG rise time               |                        |      | <del> </del> |      | <del></del> |      |            |      |          |     | ļ    |

| 25   CLK/TRG width (high)   TwCTRh   200   200   120   100   ns     26   CLK/TRG † to clock † setup time for immediate count   TsCTR (Cs)   300   210   150   110   ns   5     27   CLK/TRG † to clock † setup time for enabling of prescaler on following clock †   TsCTR (Ct)   210   210   150   110   ns   4     28   Clock † to ZC/TO † delay   TdC (ZC/TOr)   260   190   140   110   ns   4     29   Clock † to ZC/TO † delay   TdC (ZC/TOr)   260   190   140   110   ns   4     20   CLK/TRG † to clock †   TsCTR (Ct)   210   210   210   150   110   ns   4     20   CLK/TRG † to clock †   TsCTR (Ct)   210   210   150   110   ns   4     20   CLK/TRG † to clock †   TsCTR (Ct)   210   210   150   110   ns   4     21   CLK/TRG † to clock †   TsCTR (Ct)   210   210   150   110   ns   4     22   CLK/TRG † to clock †   TsCTR (Ct)   210   210   150   110   ns   4     23   CLK/TRG † to clock †   TsCTR (Ct)   210   210   150   110   ns   4     24   CLK/TRG † to clock †   TsCTR (Ct)   210   210   150   110   ns   4     25   CLK/TRG † to clock †   TsCTR (Ct)   210   210   150   110   ns   4     26   CLK/TRG † to clock †   TsCTR (Ct)   210   210   150   110   ns   4     26   CLK/TRG † to clock †   TsCTR (Ct)   210   210   150   110   ns   4     27   CLK/TRG † to clock †   TsCTR (Ct)   210   210   150   110   ns   4     28   Clock † to ZC/TO † delay   TdC (ZC/TOr)   260   190   140   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110   110  | 23  | CLK/TRG fall time               | TfCTR                  |      | 50           |      | 50          |      | 40         |      | 35       | ns  | -    |

| 26   CLK/TRG   to clock   setup time for immediate count   TsCTR (Cs)   300   210   150   110   ns   5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 24  | CLK/TRG width (low)             |                        |      | ļ            | -    |             |      | <u> </u>   |      |          |     |      |

| 26 time for immediate count         TsCTR (Cs)         300         210         150         110         is         3           CLK/TRG † to clock † setup         TsCTR (Ct)         210         210         150         110         ns         4           27 time for enabling of prescaler on following clock †         TsCTR (Ct)         210         210         150         110         ns         4           28 Clock † to ZC/TO † delay         TdC (ZC/TOr)         260         190         140         110         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25  | CLK/TRG width (high)            | TwCTRh                 | 200  |              | 200  | <u> </u>    | 120  |            | 100  | ļ        | ns  |      |

| time for immediate count  CLK/TRG ↑ to clock ↑ setup  time for enabling of prescaler on following clock ↑  28 Clock ↑ to ZC/TO ↑ delay  TdC (ZC/TOr)  20 150 110 ns  4 110 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26  | CLK/TRG † to clock † setup      | TsCTR (Cs)             | 300  |              | 210  |             | 150  |            | 110  |          | ns  | 5    |

| 27       time for enabling of prescaler on following clock ↑       TsCTR (Ct)       210       150       110       ns       4         28       Clock ↑ to ZC/TO ↑ delay       TdC (ZC/TOr)       260       190       140       110       ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | time for immediate count        | TSCTR (CS)             |      |              | 210  |             | 100  |            |      | ļ        | -   |      |

| on following clock †  28 Clock † to ZC/TO † delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     | CLK/TRG † to clock † setup      |                        |      |              |      |             |      |            |      |          |     |      |

| 28         Clock † to ZC/TO † delay         TdC (ZC/TOr)         260         190         140         110         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27  | time for enabling of prescaler  | TsCTR (Ct)             | 210  |              | 210  |             | 150  |            | 110  |          | ns  | 4    |

| 20 Olock to 20, 10 facility 1 ac (30, 101)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | on following clock †            |                        |      |              |      |             |      |            |      |          | L   |      |

| 29 Clock ↓ to ZC/TO ↓ delay TdC (ZC/TOf) 190 190 140 110 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28  | Clock † to ZC/TO † delay        | TdC (ZC/TOr)           |      | 260          |      | 190         |      |            |      | +        | ns  |      |