| - | SPEC No. | EL0  | 9 Y | 001  | _ |

|---|----------|------|-----|------|---|

|   | ISSUE:   | Nov. | 7.  | 1997 |   |

To;

|                     | REFERENCE                                                                                                                                                      |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | PECIFICATIONS                                                                                                                                                  |

|                     | LOTTION                                                                                                                                                        |

| Product Type        | 240 Output LCD Segment/Common Driver                                                                                                                           |

|                     |                                                                                                                                                                |

| Nodel No.           | LH1562F4                                                                                                                                                       |

|                     |                                                                                                                                                                |

| This specification  | ns contains 37 pages including the cover and appendix.                                                                                                         |

|                     | bjections, please contact us before issuing purchasing order.                                                                                                  |

|                     |                                                                                                                                                                |

|                     |                                                                                                                                                                |

|                     |                                                                                                                                                                |

| CUSTOMERS ACCEPTANC | Œ                                                                                                                                                              |

| DATE:               |                                                                                                                                                                |

| Dillo.              | <del></del>                                                                                                                                                    |

| BY:                 | PRESENTED                                                                                                                                                      |

|                     |                                                                                                                                                                |

|                     | $a = a \times a \times a$                                                                                                                                      |

|                     | BY: H. Nishioha                                                                                                                                                |

|                     | H. NISHIOKA                                                                                                                                                    |

|                     | BY: #. Nushioha<br>H. NISHIOKA<br>Dept. General Manager                                                                                                        |

|                     | H. NISHIOKA                                                                                                                                                    |

|                     | H. NISHIOKA                                                                                                                                                    |

|                     | H. NISHIOKA  Dept. General Manager  REVIEWED BY: PREPARED BY:                                                                                                  |

|                     | H. NISHIOKA  Dept. General Manager  REVIEWED BY: PREPARED BY:                                                                                                  |

|                     | H. NISHIOKA Dept. General Manager  REVIEWED BY: PREPARED BY:  A. Murahashu  ENGINEERING DEPARTMENT I                                                           |

|                     | H. NISHIOKA Dept. General Manager  REVIEWED BY: PREPARED BY:  A. Murahashu  ENGINEERING DEPARTMENT L  LOGIC IC ENGINEERING CENTER                              |

|                     | H. NISHIOKA Dept. General Manager  REVIEWED BY: PREPARED BY:  A. Murahashu  ENGINEERING DEPARTMENT I  LOGIC IC ENGINEERING CENTER TENRI IC DEVELOPMENT GROUP   |

|                     | H. NISHIOKA Dept. General Manager  REVIEWED BY: PREPARED BY:  A. Murahashu  ENGINEERING DEPARTMENT L  LOGIC IC ENGINEERING CENTER                              |

|                     | H. NISHIOKA  Dept. General Manager  REVIEWED BY: PREPARED BY:  A. Murahashu  ENGINEERING DEPARTMENT I  LOGIC IC ENGINEERING CENTER  TENRI IC DEVELOPMENT GROUP |

- Handle this document carefully for it contains material protected by international copyright law. Any reproduction, full or in part, of this material is prohibited without the express written permission of the company.

- When using the products covered herein, please observe the conditions written herein and the precautions outlined in the following paragraphs. In no event shall the company be liable for any damages resulting from failure to strictly adhere to these conditions and precautions.

- (1) The products covered herein are designed and manufactured for the following application areas. When using the products covered herein for the equipment listed in Paragraph (2), even for the following application areas, be sure to observe the precautions given in Paragraph (2). Never use the products for the equipment listed in Paragraph (3).

- Office electronics

- •Instrumentation and measuring equipment

- · Machine tools

- ·Audiovisual equipment

- ·Home appliances

- ·Communication equipment other than for trunk lines

- (2) Those contemplating using the products covered herein for the following equipment which demands high reliability, should first contact a sales representative of the company and then accept responsibility for incorporating into the design fail-safe operation, redundancy, and other appropriate measures for ensuring reliability and safety of the equipment and the overall system.

- •Control and safety devices for airplanes, trains, automobiles, and other transportation equipment

- · Mainframe computers

- •Traffic control systems

- •Gas leak detectors and automatic cutoff devices

- ·Rescue and security equipment

- •Other safety devices and safety equipment, etc.

- (3) Do not use the products covered herein for the following equipment which demands extremely high performance in terms of functionality, reliability, or accuracy.

- ·Aerospace equipment

- ·Communications equipment for trunk lines

- ·Control equipment for the nuclear power industry

- ·Medical equipment related to life support, etc.

- (4) Please direct all queries and comments regarding the interpretation of the above three Paragraphs to a sales representative of the company.

- •Please direct all queries regarding the products covered herein to a sales representative of the company.

#### Contents

| 1.  | Summary ·····                                                           | 2  |

|-----|-------------------------------------------------------------------------|----|

| 2.  | Features                                                                | 2  |

| 3.  | Block Diagram ·····                                                     | 3  |

| 4.  | Functional Operations of Each Block ·····                               | 3  |

| 5.  | Pin Configuration ·····                                                 | 5  |

| 6.  | Pin Descriptions ·····                                                  | 5  |

| 7.  | Description of Functional Operations ······                             | 8  |

| 8.  | Precaution ·····                                                        | 17 |

| 9.  | Absolute Maximum Ratings                                                | 18 |

| 10. | Recommended Operating Conditions                                        | 18 |

| 11. | Electrical Characteristics ······                                       | 19 |

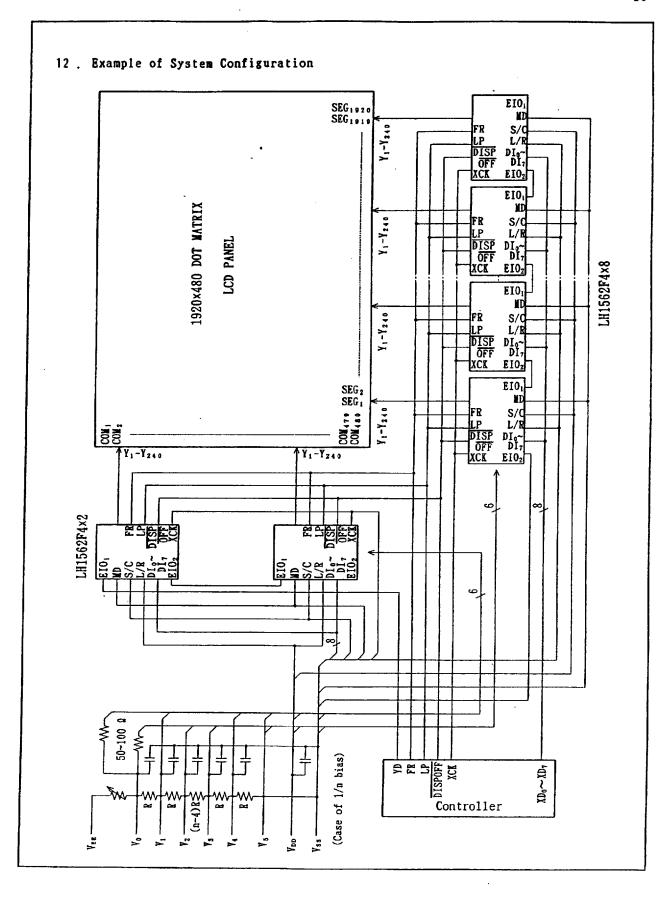

| 2.  | Example of System Configuration · · · · · · · · · · · · · · · · · · ·   | 26 |

| 3.  | Example of Typical Characteristic ·····                                 | 27 |

| 4.  | Package and Packing Specification · · · · · · · · · · · · · · · · · · · | 28 |

**81**80798 0027812 527 **888**

#### 1. Summary

The LH1562F4 is a 240 output segment/common driver LSI suitable for driving large scale dot matrix LC panels using as personal computers/work stations. Through the use of SST (Super Slim TCP) technology, it is ideal for substantially decreasing the size of the frame section of the LC module. The LH1562F4 is good both segment driver and common driver, and a low power consuming, high-precision LC panel display can be assembled. In case of segment mode, the data input is selected 4bit parallel input mode and 8bit parallel input mode by a mode(MD) pin. In case of common mode, data input/output pins are bidirectional, four data shift directions are pin-selectable.

#### 2. Features

(Segment mode)

- Shift Clock frequency : 20 MHz (Max.)  $(V_{DD}=+5 V\pm 10\%)$

- · Adopts a data bus system

- 4-bit/8-bit parallel input modes are selectable with a mode (MD) pin

- · Automatic transfer function of an enable signal

- Automatic counting function which, in the chip select mode, causes the internal clock to be stopped by automatically counting 240 of input data

- · Line latch circuit reset function when DISPOFF active

#### (Common mode)

- Shift clock frequency : 4.0 MHz (Max.)

- Built-in 240-bits bidirectional shift register (divisible into 120 bits x2)

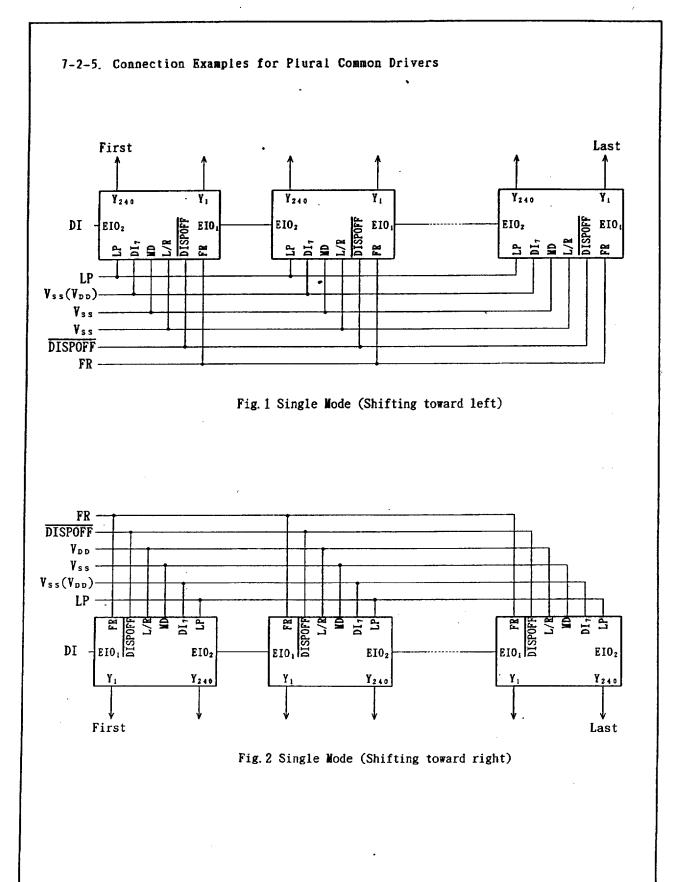

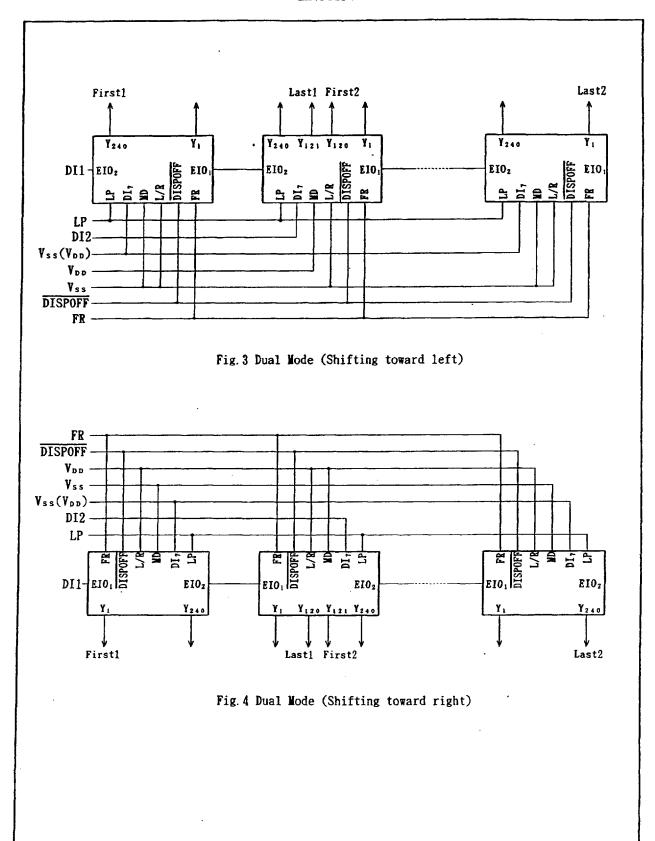

- Available in a single mode (240-bits shift register) or in a dual mode (120-bits shift register x2)

```

0 Y_1 \rightarrow Y_{240} Single mode

```

$\emptyset Y_{240} \rightarrow Y_1$

$\textcircled{9} \ Y_1 \qquad \rightarrow \ Y_{1\,2\,0} \ , \ Y_{1\,2\,1} \ \rightarrow \ Y_{2\,4\,0} \quad \mbox{Dual mode}$

$Q Y_{240} \rightarrow Y_{121}, Y_{120} \rightarrow Y_{1}$

The above 4 shift directions are pin-selectable

· Shift register circuit reset function when DISPOFF active

#### (Both segment mode and common mode)

- Supply voltage for LC drive : +15.0 to +42.0 V

- Number of LC drive outputs : 240

- · Low output impedance

- · Low power consumption

- Supply voltage for the logic system : +2.5 to +5.5 V

- CMOS silicon gate process(P-type Silicon Substrate)

- Package : 268pin TCP (Tape Carrier Package)

- · Not designed or rated as radiation hardened

## 3. Block Diagram

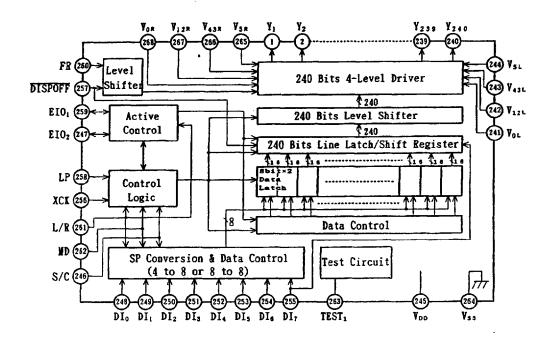

## 4. Functional Operations of Each Block

| Block          | Function                                                         |  |  |  |

|----------------|------------------------------------------------------------------|--|--|--|

| Active Control | In case of segment mode, controls the selection or deselection   |  |  |  |

|                | of the chip.                                                     |  |  |  |

|                | Following a LP signal input, and after the chip select signal is |  |  |  |

|                | input, a select signal is generated internally until 240 bits of |  |  |  |

|                | data have been read in.                                          |  |  |  |

|                | Once data input has been completed, a select signal for cascade  |  |  |  |

|                | connection is output, and the chip is deselected.                |  |  |  |

|                | In case of common mode, controls the input/output data of bidi-  |  |  |  |

|                | rectional pins.                                                  |  |  |  |

| SP Conversion  | In case of segment mode, keep input data which are 2 clocks of   |  |  |  |

| & Data Control | XCK at 4-bit parallel mode into latch circuit, or keep input     |  |  |  |

|                | data which are 1 clock of XCK at 8-bit parallel mode into latch  |  |  |  |

| J              | circuit, after that they are put on the internal data bus 8 bits |  |  |  |

|                | at a time.                                                       |  |  |  |

| Data Latch     | In case of segment mode, selects the state of the data latch     |  |  |  |

| Control        | which reads in the data bus signals. The shift direction is      |  |  |  |

|                | controlled by the control logic, for every 16 bits of data read  |  |  |  |

|                | in, the selection signal shifts one bit based on the state of    |  |  |  |

|                | the control circuit.                                             |  |  |  |

# 8180798 0027814 3TT **==**

| Block          | Function                                                              |

|----------------|-----------------------------------------------------------------------|

| Data Latch     | In case of segment mode, latches the data on the data bus. The        |

|                | latched state of each LC driver output pin is controlled by the       |

|                | control logic and the data latch control, 240 bits of data are        |

|                | read in 30 sets of 8 bits.                                            |

| Line Latch/    | In case of segment mode, all 240 bits which have been read into       |

| Shift Register | the data latch are simultaneously latched on the falling edge of      |

|                | the LP signal, and output to the level shifter block.                 |

|                | In case of common mode, shifts data from the data input pin on        |

|                | the falling edge of the LP signal.                                    |

| Level Shifter  | The logic voltage signal is level-shifted to the LC driver            |

|                | voltage level, and output to the driver block.                        |

| 4-Level Driver | Drives the LC driver output pins from the line latch/shift            |

|                | register data, selecting one of 4 levels $(V_0, V_{12}, V_{43}, V_5)$ |

|                | based on the S/C. FR and DISPOFF signals.                             |

| Control Logic  | Controls the operation of each block. In case of segment mode,        |

|                | when a LP signal has been input, all blocks are reset and the         |

|                | control logic waits for the selection signal output from the          |

|                | active control block.                                                 |

|                | Once the selection signal has been output, operation of the data      |

|                | latch and data transmission are controlled.240 bits of data are       |

|                | read in, and the chip is deselected.                                  |

|                | In case of common mode, controls the direction of data shift.         |

| Test Circuit   | The circuit for the test. During normal operation, it doesn't         |

| . [            | act.                                                                  |

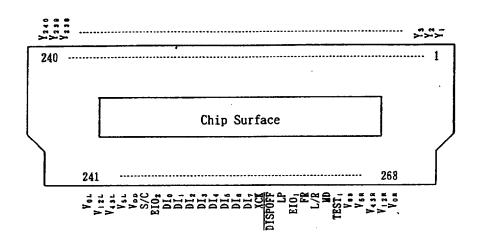

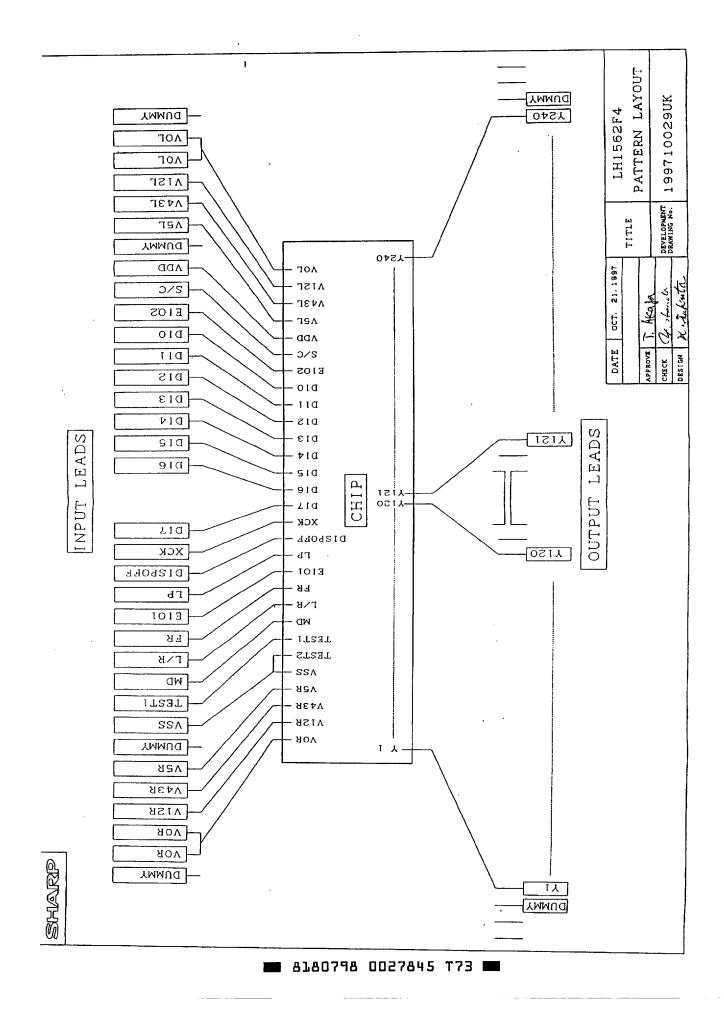

# 5. Pin Configuration

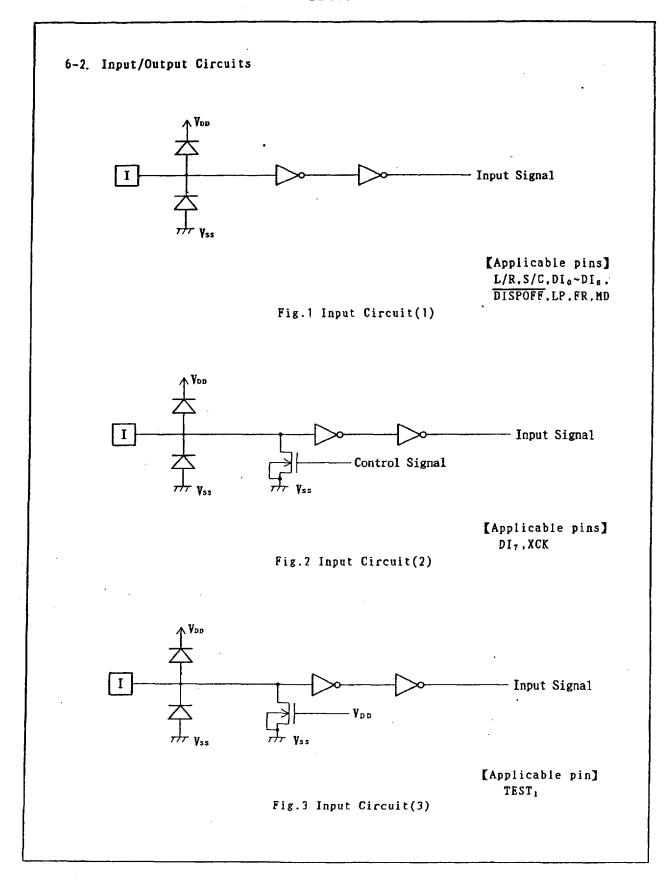

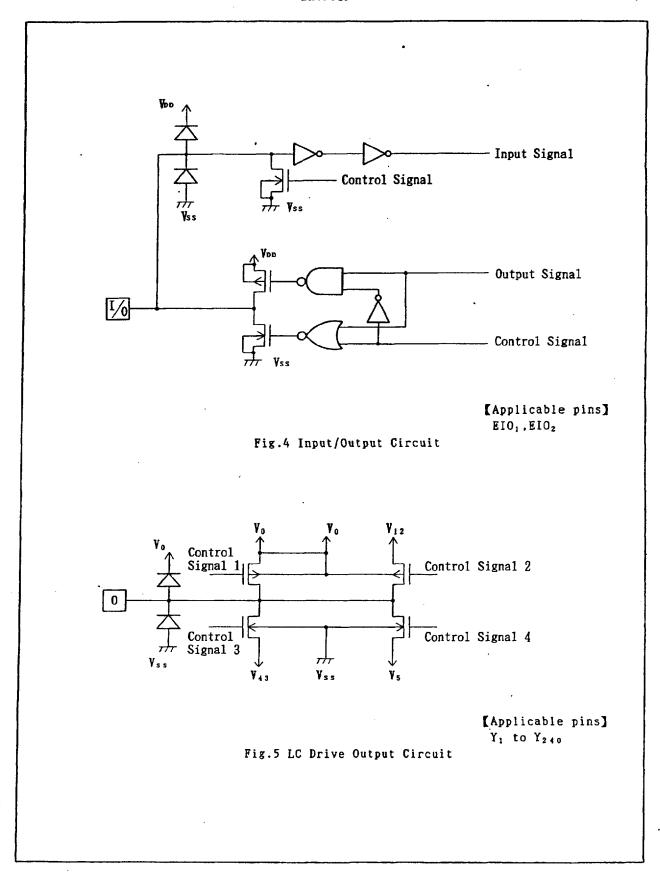

## 6. Pin Descriptions

## 6-1. Pin Designations

| Pin No.    | Symbol                              | I/0 | Designation                                      |  |

|------------|-------------------------------------|-----|--------------------------------------------------|--|

| 1 to 240   | Y1-Y240                             | 0   | LC drive output                                  |  |

| 241, 268   | Vol. Vor                            | _   | Power supply for LC drive                        |  |

| 242, 267   | V <sub>12L</sub> , V <sub>12R</sub> | -   | Power supply for LC drive                        |  |

| 243, 266   | V43L, V43R                          | -   | Power supply for LC drive                        |  |

| 244, 265   | V <sub>5L</sub> , V <sub>5R</sub>   | -   | Power supply for LC drive                        |  |

| 264        | V <sub>ss</sub>                     | -   | Ground(0 V)                                      |  |

| 245        | V <sub>D D</sub>                    | -   | Power supply for logic system(+2.5 to +5.5 V)    |  |

| 246        | S/C                                 | I   | Segment mode/common mode selection               |  |

| 247        | EIO <sub>2</sub>                    | 1/0 | Input/output for chip select or data of shift    |  |

|            |                                     |     | register                                         |  |

| 248 to 254 | DI <sub>0</sub> -DI <sub>6</sub>    | I   | Display data input for segment mode              |  |

| 255        | DI7                                 | 1   | Display data input for Segment mode/             |  |

|            |                                     |     | Dual mode data input                             |  |

| 256        | XCK                                 | I   | Display data shift clock input for segment mode  |  |

| 257        | DISPOFF                             | I   | Control input for deselect output level          |  |

| 258        | LP                                  | Ī   | Latch pulse input/shift clock input for shift    |  |

|            |                                     |     | register                                         |  |

| 259        | EIO <sub>1</sub>                    | 1/0 | Input/output for chip select or data of shift    |  |

|            |                                     |     | register                                         |  |

| 260        | FR                                  | I   | AC-converting signal input for LC drive waveform |  |

| 261        | L/R                                 | I   | Display data shift direction selection           |  |

| 262        | MD                                  | I   | Mode selection input                             |  |

| 263        | TEST,                               | I   | Test mode selection input                        |  |

■ 8180798 0027816 172 **■**

## 8180798 0027818 T45

# 7. Description of Functional Operations

# 7-1. Pin Functions

(Segment mode)

| Symbol                           | Function                                                                                                                            |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>D D</sub>                 | Logic system power supply pin connects to +2.5 to +5.5 V                                                                            |

| Vss                              | Ground pin connects to 0 V                                                                                                          |

| VOR, VOL                         | Power supply pin for LC driver voltage bias.                                                                                        |

| V12R.V12L                        | •Normally, the bias voltage used is set by a resistor divider.                                                                      |

| VASR. VASL                       |                                                                                                                                     |

| V <sub>5R</sub> ,V <sub>5L</sub> | -To further reduce the difference between the output waveforms of LC                                                                |

| 1                                | driver output pins $Y_1$ and $Y_{240}$ , externally connect $V_{iR}$ and $V_{iL}$                                                   |

|                                  | (i=0, 12, 43, 5).                                                                                                                   |

| DI <sub>0</sub> -DI <sub>7</sub> | Input Pin for display data                                                                                                          |

|                                  | -In 4-bit parallel input mode, input data into the 4 pins $\mathrm{DI_0-DI_3}$ .                                                    |

| İ                                | Connect DI <sub>4</sub> -DI <sub>1</sub> to $V_{ss}$ or $V_{DD}$ .                                                                  |

|                                  | •In 8-bit parallel input mode, input data into the 8 pins DI <sub>0</sub> -DI <sub>7</sub> .                                        |

| XCK                              | Clock input pin for taking display data                                                                                             |

|                                  | •Data is read on the falling edge of the clock pulse.                                                                               |

| LP                               | Latch pulse input pin for display data                                                                                              |

|                                  | •Data is latched on the falling edge of the clock pulse.                                                                            |

| L/R                              | Direction selection pin for reading display data                                                                                    |

|                                  | When set to $V_{ss}$ level "L", data is read sequentially from $Y_{240}$ to $Y_1$ .                                                 |

|                                  | •When set to $V_{DD}$ level "H", data is read sequentially from $Y_1$ to $Y_{240}$ .                                                |

|                                  | Control input pin for output deselect level                                                                                         |

|                                  | •The input signal is level-shifted from logic voltage level to LC                                                                   |

|                                  | drive voltage level, and controls LC drive circuit.                                                                                 |

|                                  | •When set to $V_{3.5}$ level "L", the LC drive output pins $(Y_1-Y_{2.40})$ are                                                     |

| DISPOFF                          | set to level $V_5$ .                                                                                                                |

|                                  | •While set to "L", the contents of the line latch are reset, but read the display data in the data latch regardless of condition of |

| 1                                | DISPOFF. When the DISPOFF function is canceled, the driver outputs                                                                  |

|                                  | deselect level $(V_{12} \text{ or } V_{43})$ , then outputs the contents of the date                                                |

|                                  | latch on the next falling edge of the LP. That time, if DISPOFF                                                                     |

|                                  | removal time can not keep regulation what is shown AC                                                                               |

|                                  | characteristics (Page 21), can not output the reading data correctly.                                                               |

| FR                               | AC signal input for LC driving waveform                                                                                             |

|                                  | •The input signal is level-shifted from logic voltage level to LC                                                                   |

|                                  | drive voltage level, and controls LC drive circuit.                                                                                 |

| <u> </u>                         | •Normally, inputs a frame inversion signal.                                                                                         |

|                                  | •The LC driver output pin's output voltage level can be set using                                                                   |

| 1                                | the line latch output signal and the FR signal.                                                                                     |

|                                  | Table of truth values is shown in 7-2-1.                                                                                            |

| MD                               | Mode selection pin                                                                                                                  |

| İ                                | ·When set to V <sub>ss</sub> level "L", 8-bit parallel input mode is set.                                                           |

|                                  | •When set to V <sub>DD</sub> level "H", 4-bit parallel input mode is set.                                                           |

|                                  | •The relationship between the display data and driver output pins is                                                                |

|                                  | shown in 7-2-2.                                                                                                                     |

8180798 0027819 981

| Symbol           | Function                                                              |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------|--|--|--|--|--|

| S/C              | Segment mode/common mode selection pin                                |  |  |  |  |  |

| '                | •When set to Vpp level "H", segment mode is set.                      |  |  |  |  |  |

| EIO <sub>1</sub> | Input/Output pin for chip selection                                   |  |  |  |  |  |

| EIO2             | •When L/R input is at Vss level "L". EIO, is set for output, and EIO, |  |  |  |  |  |

| ĺ                | is set for input.                                                     |  |  |  |  |  |

| ļ                | •When L/R input is at VDD level "H", EIO, is set for input, and EIO,  |  |  |  |  |  |

|                  | is set for output.                                                    |  |  |  |  |  |

|                  | •During output, set to "H" while LP*XCK is "H" and after 240-bits of  |  |  |  |  |  |

|                  | data have been read, set to "L" for one cycle (from falling edge to   |  |  |  |  |  |

|                  | falling edge of XCK), after which it returns to "H".                  |  |  |  |  |  |

|                  | •During input, after the LP signal is input, the chip is selected     |  |  |  |  |  |

| 1                | while BI is set to "L". After 240-bits of data have been read, the    |  |  |  |  |  |

| 1                | chip is deselected.                                                   |  |  |  |  |  |

| TEST             | Test mode select pin.                                                 |  |  |  |  |  |

|                  | During normal operation, tie to V <sub>ss</sub> level "L".            |  |  |  |  |  |

| Y1-Y240          | LC driver output pins                                                 |  |  |  |  |  |

| Į                | •Corresponding directly to each bit of the data latch, one level      |  |  |  |  |  |

|                  | $(V_0, V_{12}, V_{43}, or V_5)$ is selected and output.               |  |  |  |  |  |

|                  | Table of truth values is shown in 7-2-1.                              |  |  |  |  |  |

# (Common mode)

| Symbol                                                                    | Function                                                                               |  |  |  |

|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|

| V D D                                                                     | Logic system power supply pin connects to +2.5 to +5.5 V.                              |  |  |  |

| Υss                                                                       | Ground pin connects to 0 Y.                                                            |  |  |  |

| Vor, Vol                                                                  | Power supply pin for LC driver voltage bias.                                           |  |  |  |

| V <sub>12R</sub> ,V <sub>12L</sub>                                        | ·Normally, the bias voltage used is set by a resistor divider.                         |  |  |  |

| V43R, V43L                                                                | •Ensure that voltages are set such that $V_{ss} \le V_{s} < V_{43} < V_{12} < V_{0}$ . |  |  |  |

| V <sub>5R</sub> ,V <sub>5L</sub>                                          | •To further reduce the difference between the output waveforms of LC                   |  |  |  |

| ]                                                                         | driver output pins $Y_1$ and $Y_{240}$ , externally connect $V_{1R}$ and $V_{1L}$      |  |  |  |

|                                                                           | (i=0, 12, 43, 5).                                                                      |  |  |  |

| EIO                                                                       | Bidirectional shift register shift data input/output pin                               |  |  |  |

|                                                                           | -Output pin when $L/R$ is at $V_{ss}$ level "L", input pin when $L/R$ is at            |  |  |  |

|                                                                           | V <sub>DD</sub> level "H".                                                             |  |  |  |

|                                                                           | ·When EIO; is used as input pin, it will be pull-down.                                 |  |  |  |

|                                                                           | •When EIO; is used as output pin, it won't be pull-down.                               |  |  |  |

| EIO <sub>2</sub> Bidirectional shift register shift data input/output pin |                                                                                        |  |  |  |

| ]                                                                         | ·Input pin when L/R is at $V_{ss}$ level "L", output pin when L/R is                   |  |  |  |

| i .                                                                       | V <sub>DD</sub> level "H".                                                             |  |  |  |

|                                                                           | •When EIO <sub>2</sub> is used as input pin, it will be pull-down.                     |  |  |  |

|                                                                           | ·When EIO <sub>2</sub> is used as output pin, it won't be pull-down.                   |  |  |  |

| LP                                                                        | Bidirectional shift register shift clock pulse input pin                               |  |  |  |

|                                                                           | ·Data is shifted on the falling edge of the clock pulse.                               |  |  |  |

| L/R                                                                       | Bidirectional shift register shift direction selection pin                             |  |  |  |

|                                                                           | ·Data is shifted from $Y_{240}$ to $Y_1$ when set to $Y_{ss}$ level "L", and data      |  |  |  |

|                                                                           | is shifted from $Y_1$ to $Y_{240}$ when set to $V_{DD}$ level "H".                     |  |  |  |

## 8180798 0027820 6T3 W

|                                  | Control input pin for output deselect level                                                          |  |  |  |  |  |

|----------------------------------|------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                  | •The input signal is level-shifted from logic voltage level to LC                                    |  |  |  |  |  |

|                                  | drive voltage level, and controls LC drive circuit.                                                  |  |  |  |  |  |

|                                  | -When set to $V_{ss}$ level "L", the LC driver output pins $(Y_1-Y_{240})$ are                       |  |  |  |  |  |

| DISPOFF                          |                                                                                                      |  |  |  |  |  |

| 2101011                          | •While set to "L", the contents of the shift resister are reset not                                  |  |  |  |  |  |

|                                  | reading data. When the DISPOFF function is canceled, the driver                                      |  |  |  |  |  |

|                                  | outputs deselect level $(V_{12} \text{ or } V_{43})$ , and the shift data is reading                 |  |  |  |  |  |

|                                  | on the falling edge of the LP. That time, if DISPOFF removal time                                    |  |  |  |  |  |

|                                  | can not keep regulation what is shown AC characteristics (Page 25)                                   |  |  |  |  |  |

|                                  |                                                                                                      |  |  |  |  |  |

| 50                               | the shift data is not reading correctly.                                                             |  |  |  |  |  |

| FR                               | AC signal input for LC driving waveform                                                              |  |  |  |  |  |

|                                  | •The input signal is level-shifted from logic voltage level to LC                                    |  |  |  |  |  |

|                                  | drive voltage level, and controls LC drive circuit.                                                  |  |  |  |  |  |

|                                  | •Normally, input a frame inversion signal.                                                           |  |  |  |  |  |

|                                  | •The LC driver output pin's output voltage level can be set using                                    |  |  |  |  |  |

|                                  | the shift register output signal and the FR signal.                                                  |  |  |  |  |  |

|                                  | Table of truth values is shown in 7-2-1.                                                             |  |  |  |  |  |

| MD                               | Mode selection pin                                                                                   |  |  |  |  |  |

|                                  | •When set $V_{ss}$ level "L", Single Mode operation is selected, when se                             |  |  |  |  |  |

|                                  | to V <sub>DD</sub> level "H", Dual Mode operation is selected.                                       |  |  |  |  |  |

| DI <sub>7</sub>                  | Dual Mode data input pin                                                                             |  |  |  |  |  |

|                                  | ·According to the data shift direction of the data shift register,                                   |  |  |  |  |  |

|                                  | data can be input starting from the 121st bit.                                                       |  |  |  |  |  |

|                                  | When the chip is used as Dual Mode, DI, will be pull-down.                                           |  |  |  |  |  |

|                                  | When the chip is used as Single Mode, DI, won't pull-down.                                           |  |  |  |  |  |

| S/C                              | Segment mode/common mode selection pin                                                               |  |  |  |  |  |

|                                  | ·When set to V <sub>ss</sub> level "L", common mode is set.                                          |  |  |  |  |  |

| DI <sub>0</sub> -DI <sub>8</sub> | Not used                                                                                             |  |  |  |  |  |

|                                  | •Connect DI <sub>0</sub> -DI <sub>0</sub> to V <sub>ss</sub> or V <sub>DD</sub> . Avoiding floating. |  |  |  |  |  |

| XCK                              | Not used                                                                                             |  |  |  |  |  |

|                                  | •XCK is pull-down in common mode, so connect to V <sub>ss</sub> or open.                             |  |  |  |  |  |

| TEST,                            | Test mode select pins                                                                                |  |  |  |  |  |

|                                  | •During normal operation, tie to V <sub>s s</sub> level "L".                                         |  |  |  |  |  |

| Y1-Y240                          | LC driver output pins                                                                                |  |  |  |  |  |

|                                  | ·Corresponding directly to each bit of the shift register, one leve                                  |  |  |  |  |  |

|                                  | $(V_0, V_{12}, V_{43}, or V_5)$ is selected and output.                                              |  |  |  |  |  |

|                                  | Table of truth values is shown in 7-2-1.                                                             |  |  |  |  |  |

#### 7-2. Functional Operations

#### 7-2-1. Truth Table

#### (Segment Mode)

| FR | Latch Data | DISPOFF | Driver Output Voltage Level(Y1-Y240) |

|----|------------|---------|--------------------------------------|

| L  | L          | H       | V <sub>43</sub>                      |

| Ĺ  | H          | Н       | V <sub>5</sub>                       |

| H  | L.         | н       | V <sub>12</sub>                      |

| Н  | . Н        | н       | V <sub>o</sub>                       |

| X  | X          | L       | ν <sub>5</sub>                       |

Here,  $V_{55} \le V_5 < V_{45} < V_{12} < V_0$ , H:  $V_{DD} (+2.5 \text{ to } +5.5 \text{ V})$ , L:  $V_{55} (0 \text{ V})$ ,

x : Don't care

#### (Common Mode)

| FR | Latch Data |   | Driver Output Voltage Level $(Y_1-Y_{240})$ |

|----|------------|---|---------------------------------------------|

| L  | L          | Н | V <sub>4.3</sub>                            |

| L  | Н          | Н | ν <sub>0</sub>                              |

| Н  | L          | Н | Y <sub>12</sub>                             |

| Н  | Н          | Н | V <sub>5</sub>                              |

| х  | X          | L | ν <sub>5</sub>                              |

Here,  $V_{ss} \le V_5 < V_{43} < V_{12} < V_0$ , H:  $V_{DD} (+2.5 \text{ to } +5.5 \text{ V})$ , L:  $V_{ss} (0 \text{ V})$ .

x : Don't care

[Note] There are two kinds of power supply (logic level voltage, LC drive voltage) for LCD driver, please supply regular voltage which assigned by specification for each power pin.

That time "Don't care" should be fixed to "H" or "L", avoiding floating.

8180798 0027822 476

# 7-2-2. Relationship between the Display Data and Driver Output pins

(Segment Mode)

(a) 8-bit Parallel Mode

| HD | L/R | EIO,   | EIO2   | Data            | •                |                  | Figur            | e of C | lock             |                  |                  |

|----|-----|--------|--------|-----------------|------------------|------------------|------------------|--------|------------------|------------------|------------------|

|    |     |        |        | Input           | 30clock          | 29clock          | 28clock          | ••     | 3clock           | 2clock           | lclock           |

|    |     |        |        | DIo             | Y ı              | Y 9              | Y <sub>17</sub>  | ••     | Y <sub>217</sub> | Y <sub>225</sub> | Y <sub>233</sub> |

|    |     |        | -      | DI,             | Υ 2              | Y <sub>10</sub>  | Y <sub>18</sub>  | • •    | Y <sub>215</sub> | Y 2 2 8          | Y <sub>234</sub> |

| 1  |     | l      |        | DI2             | Υ 3              | Y <sub>11</sub>  | Y <sub>19</sub>  | ••     | Y <sub>219</sub> | Y <sub>227</sub> | Y <sub>235</sub> |

|    |     |        |        | DI,             | Υ 4              | Y 1 2            | Y 2 0            | • •    | Y 2 2 0          | Y 2 2 8          | Y <sub>236</sub> |

| L  | L   | Output | Input  | DI4             | Y 5              | Y <sub>13</sub>  | Y <sub>21</sub>  | ••     | Y 2 2 1          | Y <sub>229</sub> | Y <sub>237</sub> |

|    |     |        |        | DI <sub>5</sub> | Y 6              | Y <sub>14</sub>  | Y 2 2            | ••     | Y 2 2 2          | Y 2 3 0          | Y <sub>238</sub> |

|    |     |        |        | DIe             | Υ ,              | Y <sub>15</sub>  | Y 2 3            | • •    | Y 2 2 3          | Y <sub>231</sub> | Y <sub>239</sub> |

|    |     |        |        | DI7             | Y 8              | Y <sub>18</sub>  | Y 2 4            | • •    | Y 2 2 4          | Y <sub>232</sub> | Y 2 4 0          |

|    |     |        |        | DIo             | Y <sub>240</sub> | Y 2 3 2          | Y 2 2 4          | ••     | Y 2 4            | Y 1 6            | Υ ,              |

|    |     |        |        | DIı             | Y <sub>239</sub> | Y <sub>231</sub> | Y 2 2 3          | • •    | Y 2 3            | Y <sub>15</sub>  | Υ <sub>7</sub>   |

|    |     |        |        | DI <sub>2</sub> | Y <sub>238</sub> | Y <sub>230</sub> | Y 2 2 2          | • •    | Y 2 2            | Y <sub>14</sub>  | Υ 6              |

|    |     |        |        | DIa             | Y <sub>237</sub> | Y 2 2 9          | Y 2 2 1          | • •    | Y 2 1            | Y <sub>13</sub>  | Υ 5              |

| L  | H   | Input  | Output | DI4             | Y <sub>238</sub> | Y 2 2 8          | Y 2 2 0          | ••     | Y <sub>20</sub>  | Y <sub>12</sub>  | Υ .              |

|    |     |        |        | DIs             | Y <sub>235</sub> | Y <sub>227</sub> | Y <sub>219</sub> | ••     | Y <sub>19</sub>  | Υ <sub>11</sub>  | Y 3              |

|    |     |        |        | DIs             | Y <sub>234</sub> | Y 2 2 8          | Y <sub>218</sub> | ••     | Y <sub>18</sub>  | Υ <sub>10</sub>  | Y 2              |

|    |     |        |        | DI7             | Y <sub>233</sub> | Y <sub>225</sub> | Y <sub>217</sub> | ••     | Y <sub>17</sub>  | Υg               | Yı               |

(b) 4-bit Parallel Mode

| MD | L/R | EIO,   | EIO <sub>2</sub> | Data            | · · ·            |         | Figur           | e of ( | lock             |                  |                  |

|----|-----|--------|------------------|-----------------|------------------|---------|-----------------|--------|------------------|------------------|------------------|

|    |     |        |                  | Input           | 60clock          | 59clock | 58clcok         | • •    | 3clock           | 2clock           | lclock           |

|    |     |        | -                | DIo             | Yı               | Y 5     | Y g             | • •    | Y 2 2 9          | Y <sub>233</sub> | Y <sub>237</sub> |

|    |     |        |                  | DI              | Y 2              | Υß      | Y10             | • •    | Y 2 3 0          | Y234             | Y <sub>228</sub> |

| Н  | L   | Output | Input            | DI2             | Y 3              | Υ 7     | Y <sub>11</sub> |        | Y <sub>231</sub> | Y <sub>235</sub> | Y <sub>239</sub> |

|    |     |        |                  | DIa             | Y 4              | Y s     | Y 1 2           | • •    | Y 2 3 2          | Y 2 3 8          | Y 2 4 0          |

|    |     |        |                  | DIo             | Y 2 4 0          | Y236    | Y 2 3 2         | • •    | Y 1 2            | Y 8              | Υ 4              |

|    | •   |        |                  | , Id            | Y 2 3 9          | Y 2 3 5 | Y 2 3 1         | ••     | Y <sub>11</sub>  | Υ 7              | Υ 3              |

| Н  | H   | Input  | Output           | DI2             | Y 2 3 8          | Y 2 3 4 | Y 2 3 0         | ••     | Yie              | Υ 6              | Y z              |

|    |     |        |                  | DI <sub>3</sub> | Y <sub>237</sub> | Y 2 3 3 | Y 2 2 9         | ••     | Υg               | Y 5              | Υι               |

(Common Mode)

| MD       | L/R               | Data Transfer Direction           | EIO <sub>1</sub> | EIO2   | DI 7  |

|----------|-------------------|-----------------------------------|------------------|--------|-------|

| L        | L(shift to left)  | Y <sub>240</sub> → Y <sub>1</sub> | Output           | Input  | Х     |

| (Single) | H(shift to right) | $Y_1 \rightarrow Y_{240}$         | Input            | Output | X     |

|          | L(shift to left)  | $Y_{240} \rightarrow Y_{121}$     | Output           | Input  | Input |

| H        |                   | $Y_{120} \rightarrow Y_{1}$       |                  |        |       |

| (Dual)   | H(shift to right) | $Y_1 \rightarrow Y_{120}$         | Inpout           | Output | Input |

|          |                   | $Y_{121} \rightarrow Y_{240}$     |                  |        |       |

Here, L: $V_{ss}(0 \text{ V})$ , H: $V_{DD}(+2.5 \text{V} \text{ to } +5.5 \text{ V})$ , x:Don't Care

[Note] "Don't care" should be fixed to "H" or "L", avoiding floating.

#### **81**80798 0027823 302 **88**

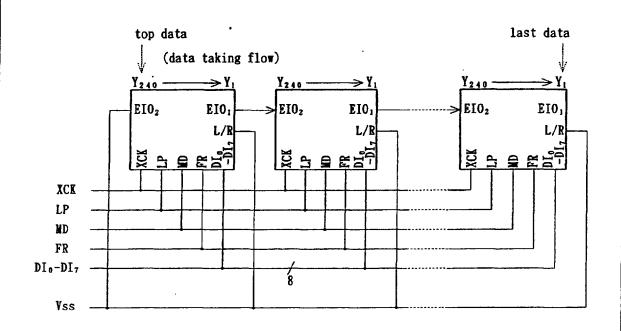

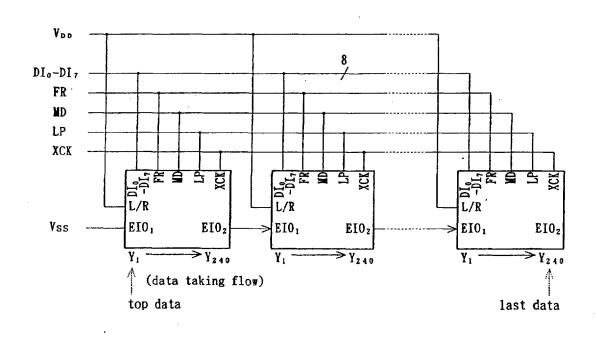

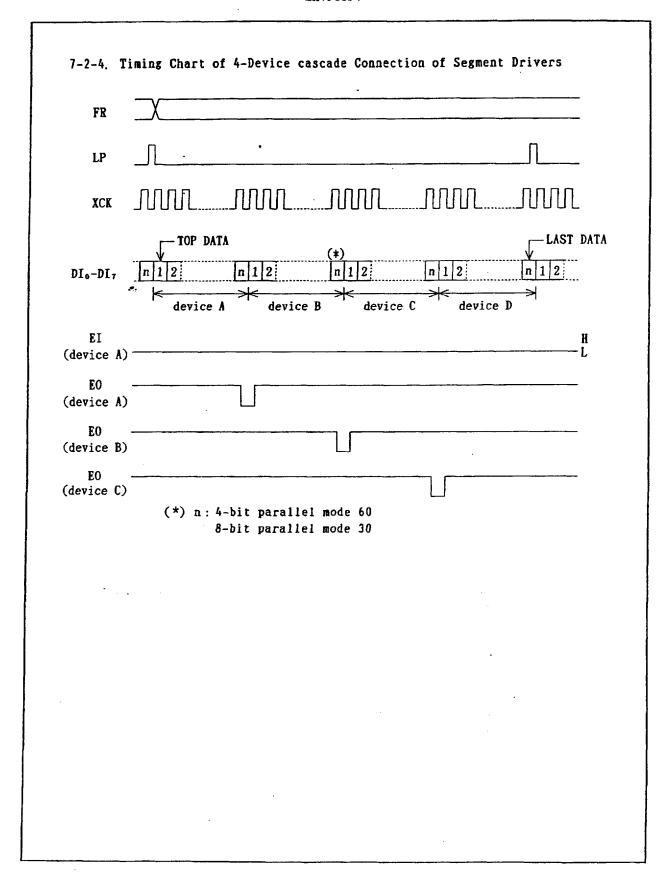

## 7-2-3. Connection Examples of Plural Segment Drivers

(a) Case of L/R=L

(b) Case of L/R≈"H"

B 8180798 0027824 249 B

#### 8180798 0027825 185

■ 8180798 0027827 T58 ■

#### 8. Precaution

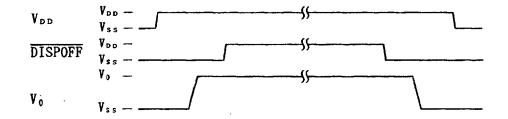

Offecaution when connecting or disconnecting the power

This LSI has a high-voltage LC driver, so it may be permanently damaged by

a high current which may flow if a voltage is supplied to the LC driver

power supply while the logic system power supply is floating.

The detail is as follows.

- •When connecting the power supply, connect the LC drive power after connecting the logic system power. Furthermore, when disconnecting the power, disconnect the logic system power after disconnecting the LC drive power.

- •We recommend you connecting the serial resistor( $50\sim100~\Omega$ ) or fuse to the LC drive power  $V_0$  of the system as a current limitter. And set up the suitable value of the resistor in consideration of LC display grade.

And when connecting the logic power supply, the logic condition of this LSI inside is insecurity. Therefore connect the LC drive power supply after resetting logic condition of this LSI inside on  $\overline{\text{DISPOFF}}$  function. After that, cancel the  $\overline{\text{DISPOFF}}$  function after the LC drive power supply has become stable. Furthermore, when disconnecting the power, set the LC drive output pins to level  $V_S$  on  $\overline{\text{DISPOFF}}$  function. After that, disconnect the logic system power after disconnecting the LC drive power.

When connecting the power supply, show the following recommend sequence.

8180798 0027828 994

#### 9. Absolute Maximum Ratings

| Parameter           | Symbol           | Conditions  | Applicable pins                     | Ratings                | Unit |

|---------------------|------------------|-------------|-------------------------------------|------------------------|------|

| Supply voltage (1)  | V <sub>D</sub> D | Ta=25 ፒ     | V <sub>DD</sub>                     | -0.3 to $+7.0$         | V    |

| Supply voltage (2)  | V <sub>o</sub>   | Referenced  | Vol. Von                            | -0.3 to +45.0          | V    |

|                     | V <sub>12</sub>  | to Vss(0 V) | V <sub>12L</sub> , V <sub>12R</sub> | $-0.3$ to $V_0+0.3$    | V    |

|                     | V43              |             | V43L, V43R                          | $-0.3$ to $V_0+0.3$    | V    |

|                     | V <sub>5</sub>   |             | V <sub>5L</sub> , V <sub>5R</sub>   | $-0.3$ to $V_0 + 0.3$  | V    |

| Input voltage       | V <sub>1</sub>   | ] .         | DI <sub>0-7</sub> .XCK,LP,L/R,FR    | $-0.3$ to $V_{DD}+0.3$ | V    |

|                     |                  |             | MD,S/C,EIO1,EIO2,                   |                        |      |

|                     |                  |             | DISPOFF, TEST,                      | ,                      |      |

| Storage temperature | T                |             |                                     | -45 to +125            | t    |

## 10. Recommended Operating Conditions

| Parameter             | Symbol          | Conditions               | Applicable pins  | Min.  | Typ. | Max.  | Unit |

|-----------------------|-----------------|--------------------------|------------------|-------|------|-------|------|

| Supply voltage (1)    | V <sub>DD</sub> | Referenced               | V <sub>D D</sub> | +2.5  |      | +5.5  | V    |

| Supply voltage (2)    | V <sub>e</sub>  | to V <sub>ss</sub> (0 V) | Vor, Vor         | +15.0 |      | +42.0 | V    |

| Operating temperature | T.,             |                          |                  | -20   |      | +85   | t    |

[Note]Ensure that voltages are set such that  $V_{5.5} \le V_5 < V_{4.3} < V_{1.2} < V_0$

**■ 8180798 0027829 820** ■

#### 11. Electrical Characteristics

11-1. DC Characteristics

(Segment Mode)

$(V_{ss}=V_{5}=0 \text{ V}, V_{pp}=+2.5 \text{ V to } +5.5 \text{ V}, V_{\bullet}=+15.0 \text{ to } +42.0 \text{ V}, Ta=-20 \text{ to } +85 \text{ T})$

| Parameter           | Symbol             | Conditions                     | Applicable pins               | Min.                 | Typ. | Max.   | Unit |

|---------------------|--------------------|--------------------------------|-------------------------------|----------------------|------|--------|------|

| Input voltage       | V 1 H              |                                | DI <sub>0-7</sub> ,XCK,LP,L/R | 0.8Ypp               |      |        | V    |

| -                   | . A <sup>1 r</sup> |                                | FR,MD,S/C,EIO,                |                      |      | 0.2Vpp | V    |

|                     |                    |                                | E102, DISPOFF                 |                      |      |        |      |

| Output voltage      | Von                | IoH=-0.4 mA                    | EIO1, EIO2                    | V <sub>DD</sub> -0.4 |      |        | V    |

|                     | VoL                | I <sub>oL</sub> =+0.4 mA       |                               |                      |      | +0.4   | ٧    |

| Input leakage       | ILIH               | Y 1 = Y D D                    | DI <sub>0-7</sub> ,XCK,LP,L/R |                      |      | +10.0  | μA   |

| current             | ILIL               | V = V s s                      | FR.MD.S/C.EIO1                |                      |      | -10.0  | μА   |

|                     |                    |                                | EIO2, DISPOFF                 |                      |      |        |      |

|                     |                    | AVon   Vo =+40.0               |                               |                      | 1.0  | 1.5    |      |

| Output resistance   | Ron                | $=0.5 \text{ V } V_0 = +30.0 $ | Y1-Y240                       |                      | 1.5  | 2.0    | kΩ   |

|                     |                    | $V_0 = +20.0$                  |                               |                      | 2.0  | 2.5    |      |

| Stand-by current    | Ista               | *1                             | V <sub>S S</sub>              |                      |      | 75.0   | μA   |

| Consumed current(1) | IDDI               | *2                             | V <sub>D D</sub>              |                      |      | 2.0    | mA   |

| (Deselection)       |                    | •                              |                               |                      |      |        |      |

| Consumed current(2) | IDD2               | *3                             | V <sub>D D</sub>              |                      |      | 12.0   | mA   |

| (Selection)         |                    |                                |                               |                      |      |        |      |

| Consumed current    | I <sub>0</sub>     | *4                             | V <sub>o</sub>                |                      |      | 1.5    | mΑ   |

#### [Note]

- \*1  $V_{DD} = +5.0 \text{ V}$ ,  $V_0 = +42.0 \text{ V}$ ,  $V_1 = V_{SS}$

- \*2  $V_{DD}$ =+5.0 V,  $V_{0}$ =+42.0 V,  $f_{XCK}$ =20 MHz, No-load, EI= $V_{DD}$ The input data is turned over by data taking clock(4-bit parallel input mode)

- \*3  $V_{DD}$ =+5.0 V,  $V_0$ =+42.0 V,  $f_{XCX}$ =20 MHz, No-load, EI= $V_{SS}$ The input data is turned over by data taking clock(4-bit parallel input mode)

- \*4  $V_{DD}$ =+5.0 V,  $V_{o}$ =+42.0 V,  $f_{xcx}$ =20 MHz,  $f_{LP}$ =41.6 kHz,  $f_{FR}$ =80 Hz, No-load The input data is turned over by data taking clock(4-bit parallel input mode)

🚃 8180798 DD27830 542 📟

# (Common Mode)

$(V_{ss}=V_{s}=0 \text{ V}, V_{op}=+2.5 \text{ V to } +5.5 \text{ V}, V_{o}=+15.0 \text{ to } +42.0 \text{ V}, Ta=-20 \text{ to } +85 \text{ T})$

| Parameter           | Symbol   | Conditions                              | Applicable pins                  | Min.                 | Typ. | Max.     | 110: |

|---------------------|----------|-----------------------------------------|----------------------------------|----------------------|------|----------|------|

|                     | <u> </u> | COHUICIONS                              |                                  |                      |      | пах.     |      |

| Input voltage       | VIH      |                                         | DI <sub>0-7</sub> , XCK, LP, L/F | 0.87                 |      |          | y    |

|                     | V: L     |                                         | FR,MD,S/C,EIO;                   | 1                    |      | 0.2700   | V    |

|                     |          | •                                       | EIO2.DISPOFF                     |                      |      | <u> </u> |      |

| Output voltage      | Voн      | I <sub>oH</sub> =-0.4 mA                | EIO1, EIO2                       | V <sub>DD</sub> -0.4 |      |          | y    |

|                     | YoL      | IoL=+0.4 mA                             |                                  |                      |      | +0.4     | V    |

| Input leakage       | ILTH     | $V_1 = V_{DD}$                          | DI <sub>0-6</sub> , LP, L/R, FR  |                      |      | +10.0    | μA   |

| current             |          |                                         | MD,S/C,DISPOFF                   |                      |      |          |      |

|                     | ILIL     | Y1 = Y5 5                               | DIO-7.XCK, LP, L/R               |                      |      | -10.0    | μΑ   |

|                     | i i      |                                         | FR,MD,S/C,EIO <sub>1</sub>       |                      |      |          |      |

|                     |          |                                         | EIO2, DISPOFF                    |                      |      |          |      |

| Input pull-down     | IPD      | Y 1 = Y D D                             | XCK, EIO1, EIO2                  |                      |      | 100.0    | μА   |

| current             |          |                                         | DI <sub>7</sub>                  |                      |      |          |      |

|                     |          | AVON   Vo =+40.0 Y                      |                                  | ,                    | 1.0  | 1.5      |      |

| Output resistance   | Ron      | $=0.5 \text{ V } V_0 = +30.0 \text{ V}$ | Y1-Y240                          |                      | 1.5  | 2.0      | kΩ   |

|                     |          | $Y_0 = +20.0 \text{ V}$                 |                                  |                      | 2.0  | 2.5      |      |

| Stand-by current    | Ista     | *1                                      | Vss                              |                      |      | 75.0     | μA   |

| Consumed current(1) | Ipp      | *2                                      | VDD                              |                      |      | 120.0    | μÁ   |

| Consumed current(2) | I o      | *2                                      | ٧,                               |                      |      | 240.0    | μA   |

| W W COW W           | 7.3 0 17 | 17 17                                   | 1                                |                      |      |          |      |

<sup>\*1</sup>  $V_{DD}=+5.0 \text{ V}, V_0=+42.0 \text{ V}, V_1=V_{SS}$

8180798 0027831 489

<sup>\*2</sup>  $V_{DD}$ =+5.0 V,  $V_{o}$ =+42.0 V,  $f_{LP}$ =41.6 kHz,  $f_{PR}$ =80 Hz case of 1/480 duty operation, No-load

# SHARP

## 11-2. AC Characteristics

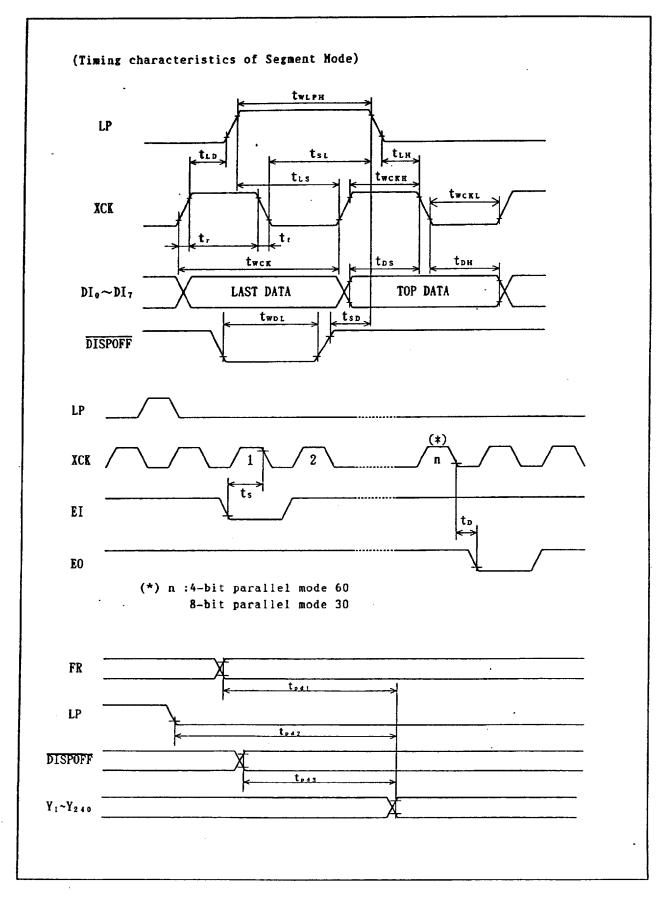

(Segment Mode 1)

$(Y_{ss}=Y_{s}=0 \text{ V}, Y_{pp}=+4.5 \text{ V to } +5.5 \text{ V}, Y_{0}=+15.0 \text{ to } +42.0 \text{ V}, Ta=-20 \text{ to } +85 \text{ V})$

| Parameter                   | Symbol           | Condition                             | Min. | Typ. | Max.   | Unit |

|-----------------------------|------------------|---------------------------------------|------|------|--------|------|

| Shift clock period *1       | twck             | t <sub>r</sub> ,t <sub>i</sub> ≤10 ns | 50   |      |        | ns   |

| Shift clock "H" pulse width | twckH            |                                       | 15   |      |        | ns   |

| Shift clock "L" pulse width | twcki            |                                       | 15   |      |        | ns   |

| Data setup time             | tos              |                                       | 10   |      |        | ns   |

| Data hold time              | t <sub>DR</sub>  |                                       | 12   |      |        | ns   |

| Latch pulse "H" pulse width | twlph            |                                       | 15   |      |        | ns   |

| Shift clock rise to         | tio              |                                       | 0    |      |        | ns   |

| Latch pulse rise time       |                  |                                       |      | İ    | !<br>; |      |

| Shift clock fall to         | tsi              |                                       | 30   |      |        | ns   |

| Latch pulse fall time       |                  |                                       |      |      |        |      |

| Latch pulse rise to         | tıs              |                                       | 25   | _    |        | ns   |

| Shift clock rise time       |                  |                                       |      |      |        |      |

| Latch pulse fall to         | t <sub>l H</sub> |                                       | 25   |      |        | ns   |

| Shift pulse fall time       |                  |                                       |      |      |        |      |

| Input signal rise time *2   | t,               |                                       |      |      | 50     | ns   |

| Input signal fall time *2   | t,               |                                       |      |      | 50     | ns   |

| Enable setup time           | t <sub>s</sub>   |                                       | 10   |      |        | ns   |

| DISPOFF removal time        | tsp              |                                       | 100  |      |        | ns   |

| DISPOFF "L" pulse width     | twor             |                                       | 1.2  |      |        | μs   |

| Output delay time (1)       | t <sub>p</sub>   | C <sub>1</sub> =15 pF                 |      |      | 30     | ns   |

| Output delay time (2)       | tpd1, tpd2       | C <sub>L</sub> =15 pF                 |      |      | 1.2    | μs   |

| Output delay time (3)       | tpd3             | C <sub>L</sub> =15 pF                 |      |      | 1.2    | μs   |

## [Note]

**3180798 0027832 315**

<sup>\*1</sup> Take the cascade connection into consideration.

<sup>\*2</sup>  $(t_{CK}-t_{WCKL})/2$  is maximum in the case of high speed operation.

#### (Segment Mode 2)

$(V_{ss}=V_{5}=0 \text{ V}, V_{DD}=+3.0 \text{ V to } +4.5 \text{ V}, V_{0}=+15.0 \text{ to } +42.0 \text{ V}, Ta=-20 \text{ to } +85 \text{ t})$

| (122-12-0 1) 100-1310       |                 |                       |      | · · · · |      |      |

|-----------------------------|-----------------|-----------------------|------|---------|------|------|

| Parameter                   | Symbol          | Condition             | Min. | Typ.    | Max. | Unit |

| Shift clock period *1       | twcx            | t.,t.≤10 ns           | 66   |         |      | ns   |

| Shift clock "H" pulse width | twckH           |                       | 23   |         |      | ns   |

| Shift clock "L" pulse width | twckL           |                       | 23   |         |      | ns   |

| Data setup time             | tos             |                       | 15   |         |      | ns   |

| Data hold time              | t <sub>DH</sub> |                       | 23   |         |      | ns   |

| Latch pulse "H" pulse width | twirm           |                       | 30   |         |      | ns   |

| Shift clock rise to         | tio             |                       | 0    |         |      | ns   |

| Latch pulse rise time       | Ì               |                       |      |         |      |      |

| Shift clock fall to         | tsi             |                       | 50   |         |      | ns   |

| Latch pulse fall time       |                 |                       |      |         |      |      |

| Latch pulse rise to         | tis             |                       | 30   |         |      | ns   |

| Shift clock rise time       |                 |                       |      |         |      |      |

| Latch pulse fall to         | t <sub>LH</sub> |                       | 30   |         |      | ns   |

| Shift pulse fall time       |                 |                       |      |         |      |      |

| Input signal rise time *2   | tr              |                       |      |         | 50   | ns   |

| Input signal fall time *2   | t,              |                       |      |         | 50   | ns   |

| Enable setup time           | ts              |                       | 15   |         |      | ns   |

| DISPOFF removal time        | tsp             |                       | 100  |         |      | ns   |

| DISPOFF "L" pulse width     | twol            |                       | 1.2  |         |      | μs   |

| Output delay time (1)       | t₽              | C <sub>L</sub> =15 pF |      |         | 41   | ns   |

| Output delay time (2)       | tpd1.tpd2       | C <sub>L</sub> =15 pF |      |         | 1.2  | μs   |

| Output delay time (3)       | tpd3            | C <sub>L</sub> =15 pF |      |         | 1.2  | μs   |

| [Note]                      |                 |                       |      |         |      |      |

#### [Note]

■ 8180798 0027833 251 **■**

<sup>\*1</sup> Take the cascade connection into consideration.

<sup>\*2</sup>  $(t_{c\kappa}-t_{wc\kappa H}-t_{wc\kappa L})/2$  is maximum in the case of high speed operation.

## (Segment Mode 3)

$(V_{ss}=V_{s}=0 \text{ V}, V_{pp}=+2.5 \text{ V} \text{ to } +3.0 \text{ V}, V_{0}=+15.0 \text{ to } +42.0 \text{ V}, Ta=-20 \text{ to } +85 \text{ C})$

| Parameter                   | Symbol          | Condition             | Min. | Typ. | Max. | Unit |

|-----------------------------|-----------------|-----------------------|------|------|------|------|

| Shift clock period *1       | twck            | t,,t,≤10 ns           | 82   |      |      | ns   |

| Shift clock "H" pulse width | twckH           |                       | 28   |      |      | ns   |

| Shift clock "L" pulse width | twork           |                       | 28   |      |      | ns   |

| Data setup time             | tos             |                       | 20   |      |      | ns   |

| Data hold time              | ton             |                       | 23   |      |      | ns   |

| Latch pulse "H" pulse width | twiph .         |                       | 30   |      |      | ns   |

| Shift clock rise to         | t <sub>LD</sub> |                       | 0    |      |      | ns   |

| Latch pulse rise time       |                 |                       |      |      |      |      |

| Shift clock fall to         | tsı             |                       | 65   |      |      | ns   |

| Latch pulse fall time       |                 |                       |      |      |      |      |

| Latch pulse rise to         | tis             |                       | 30   |      |      | ns   |

| Shift clock rise time       | :               |                       |      |      |      |      |

| Latch pulse fall to         | tun             |                       | 30   |      |      | ns   |

| Shift pulse fall time       |                 |                       |      |      |      |      |

| Input signal rise time *2   | t,              |                       |      |      | 50   | ns   |

| Input signal fall time *2   | tı              |                       |      |      | 50   | ns   |

| Enable setup time           | ts              |                       | 15   |      |      | ns   |

| DISPOFF removal time        | tsp             |                       | 100  |      |      | ns   |

| DISPOFF "L" pulse width     | twoL            |                       | 1.2  |      |      | μs   |

| Output delay time (1)       | tp              | C <sub>L</sub> =15 pF |      |      | 57   | ns   |

| Output delay time (2)       | tpd1.tpd2       | C <sub>L</sub> =15 pF |      |      | 1.2  | μs   |

| Output delay time (3)       | tpds            | C <sub>1</sub> =15 pF |      |      | 1.2  | μs   |

| Notal                       | •               | ·                     |      |      |      |      |

#### [Note]

8180798 0027834 198

<sup>\*1</sup> Take the cascade connection into consideration.

<sup>\*2</sup>  $(t_{cK}-t_{wcKH}-t_{wcKL})/2$  is maximum in the case of high speed operation.

**81**80798 0027835 024 **11**

# **SHARP**

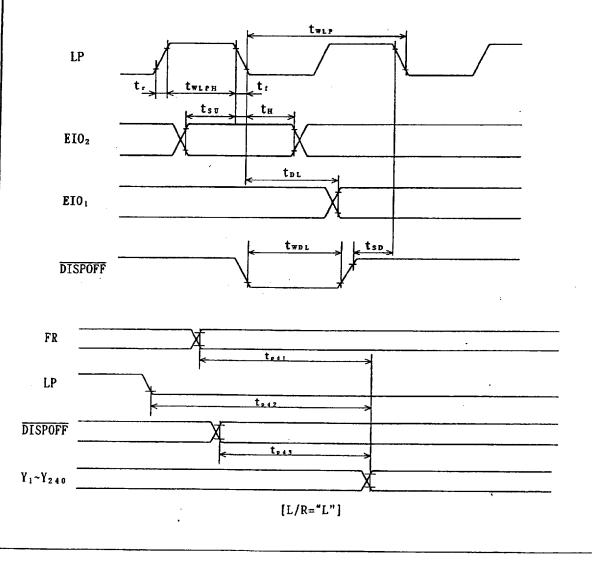

#### (Common Mode)

$(V_{ss}=V_{s}=0 \text{ V}, V_{pp}=+2.5 \text{ to } +5.5 \text{ V}, V0=15.0 \text{ to}+42.0 \text{ V}, Ta=-20 \text{ to } +85 \text{ t})$

| Parameter                   | Symbol         | Condition                     | Min. | Typ. | Max. | Unit |

|-----------------------------|----------------|-------------------------------|------|------|------|------|

| Shift clock period          | twip           | t,,t,≤20 ns                   | 250  |      |      | ns   |

| Shift clock "H" pulse width | twiph          | V <sub>DD</sub> =+5.0 V±10%   | 15   |      |      | ns   |

|                             |                | $V_{pp} = +2.5 V \sim +4.5 V$ | 30   |      |      | ns   |

| Data setup time .           | tsu            |                               | 30   |      |      | ns   |

| Data hold time              | t <sub>H</sub> |                               | 50   |      |      | ns   |

| Input signal rise time      | t,             |                               |      |      | 50   | ns   |

| Input signal fall time      | t.             |                               |      | "    | 50   | ns   |

| DISPOFF removal time        | tsp            |                               | 100  |      |      | ns   |

| DISPOFF "L" pulse width     | twoL           |                               | 1.2  |      |      | μз   |

| Output dalay time(1)        | tor            | C <sub>L</sub> =15 pF         |      |      | 200  | ns   |

| Output delay time(2)        | todi,tod2      | C <sub>L</sub> =15 pF         |      |      | 1.2  | μs   |

| Output dalay time(3)        | tpds           | C <sub>L</sub> =15 pF         |      |      | 1.2  | μs   |

## (Timing Characteristics of Common Mode)

# ■ 8180798 0027836 T60 ■

■ 8180798 0027837 9T7 **■**

# 13. Example of Typical Characteristic

| Parameter                  | Conditions                                                     | Min. | Typ. | Max. | Unit |

|----------------------------|----------------------------------------------------------------|------|------|------|------|

| Typical Fundamental Rating | $Ta=+25 \text{ °C}, V_{SS}=0 \text{ V}, V_{DD}=+5.0 \text{ V}$ |      | 10   |      | ns   |

| Propagation Delay Time     |                                                                |      |      |      |      |

■ EE8 8E87500 8P70818 ■

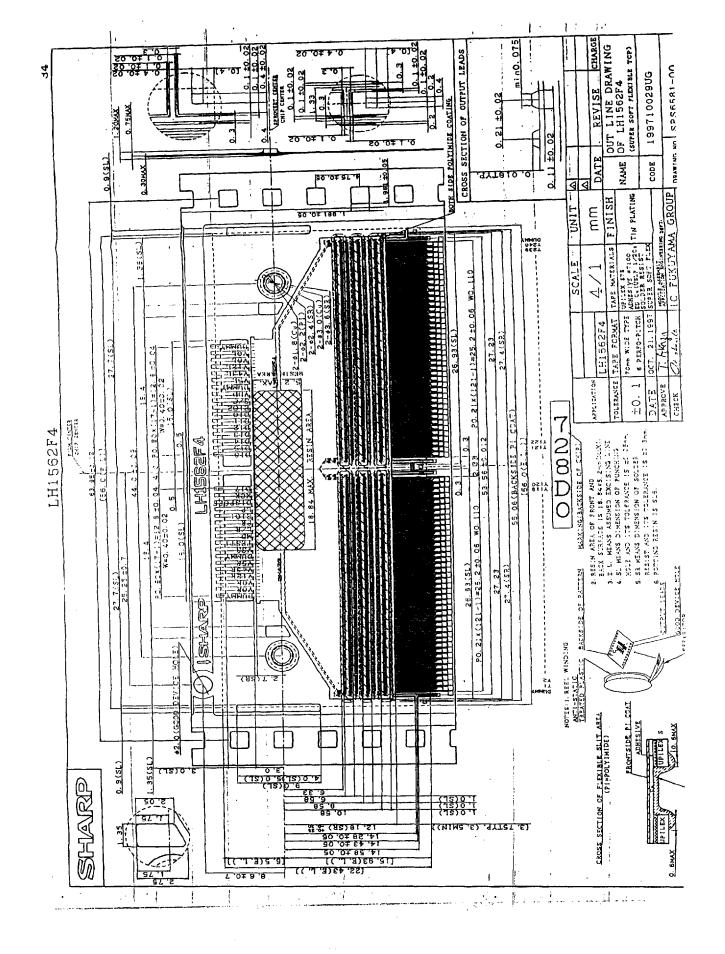

# 14. PACKAGE AND PACKING SPECIFICATION

1. Package Outline Specification

Refer to drawing No. SPS6581-00

2. Markings

The meanings of the device code printed on each tape carrier package are as follows.

(1) Date code (example) :  $\frac{7}{a}$   $\frac{28}{b}$   $\frac{D}{c}$   $\frac{0}{d}$

- a) denotes the last figure of Arino Domini (of production)

- b) denotes the week (of production)

- c) denotes factory code (of production)

- d) denotes the number of times of alteration

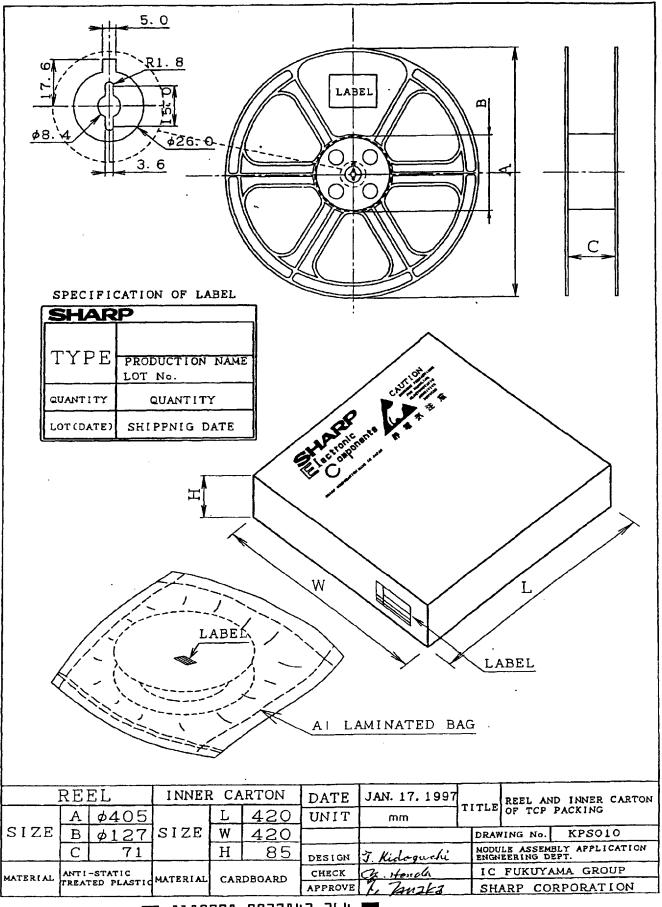

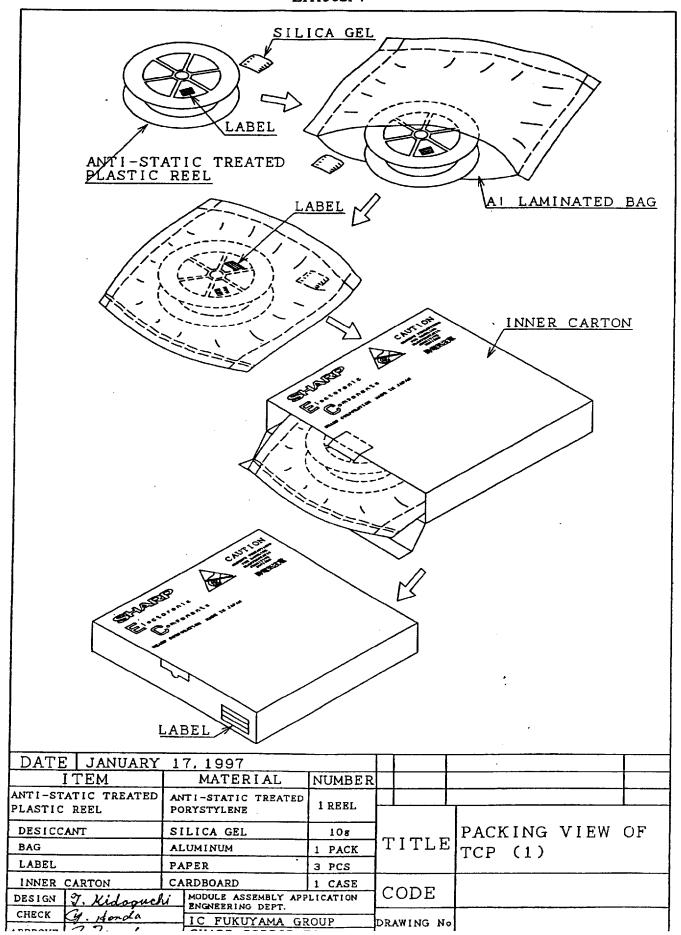

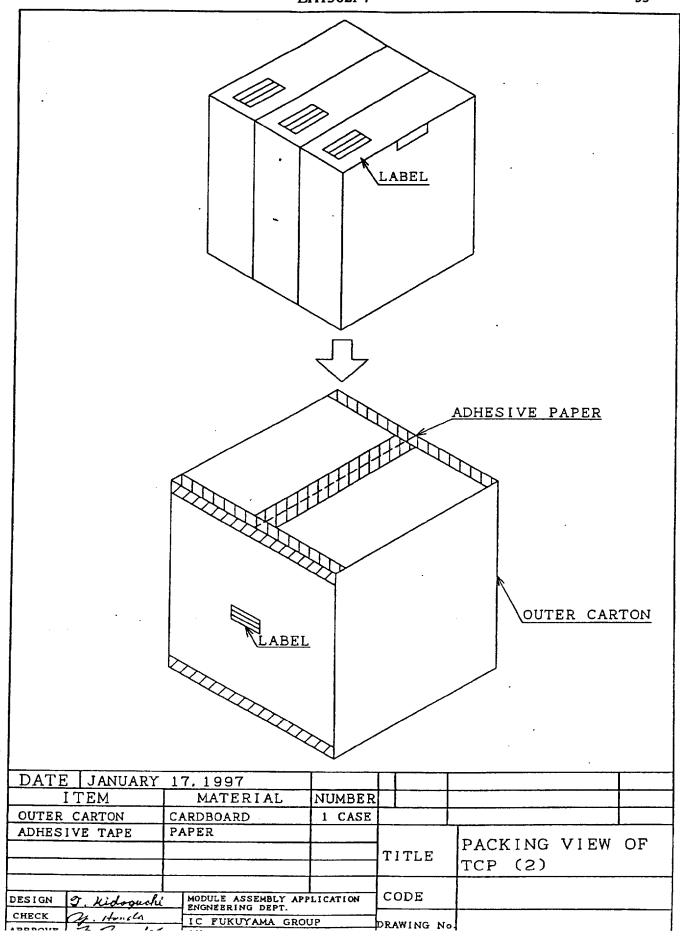

- 3. Packing Specifications

## 3-1 Packing Materials

| Item                   | Material                                  | Purpose                                                        |

|------------------------|-------------------------------------------|----------------------------------------------------------------|

| Reel                   | Anti-static treated plastic (405 mm dia.) | Packing of tape carrier package.                               |

| Separator              | Anti-static treated PET (188 μ mt)        | Protects device and prevents<br>ESD (Electro Static Discharge) |

| Aluminum laminated bag | (520×600 mm)                              | Moisture proof.                                                |

| Adhesive tape paper    |                                           | Fixing of tape carrier package and separator.                  |

| Label                  | Paper                                     | Indicates production name, lot.No., and quantity.              |

| Desiccant              | Silica gel                                | Drying of device                                               |

| Inner carton           | Cardboard( $420 \times 420 \times 85$ mm) | Contains a reel.                                               |

| Outer carton           | Cardboard(445×285×450mm)                  | Contains 3 inner cartons.                                      |

3-2 Packing Form

- a) Tape carrier package(TCP) is wound on a reel with separator and the ends of them are fixed with adhesive tape.

- b) A label indicating production name, lot number and quantity is stuck on one side of the reel.

- c) The reel and silica gel are put in a laminated aluminum bag. Nitrogen gas is enclosed in the bag and the bag is sealed. The same label(b) is affixed to the bag. The bag is put in a carton and the same label(b) is affixed to one side of the inner carton.

- \* Specification of label

- d) 3 inner cartons are put in an outer carton and the same label(b) is affixed to one side of the outer carton.

- 3-3 Other

- (1) The length of the TCP is typically 40 m per reel, but this may change in accordance with the inventory quantity.

- (2) Faulty devices is completely punched out at the part of the device.

- (3) The maximum number of continuous faulty devices is 9.

| ISSUE DATE   | NOV. 6, 1997 | APPROVE | T. Akaya   | (NOTE) |

|--------------|--------------|---------|------------|--------|

| ISSUE NUMBER | H9Y001       | CHECK   | at. Honola |        |

| S/C NUMBER   |              | DESIGN  | H. Frukuta |        |

🖿 8180798 0027839 77T 🖿

#### 4. Cautions concerning handling.

Although the strength of the device has been verified in accordance with the test method shown below, do not subject the resin parts or the slit terminals to any excessive bending or pressure.

| Test         | Test method                                                        |           | Rating                                                                                                                  |

|--------------|--------------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------|

| Flexure test | Front Output terminal Backside F F (Force): breaking strength (N). | Side view | Indicate as moment M. $M=F\times L (N\cdot m)$ $M=1.47\times 10^{-3} N\cdot m MAX.$ (for both $+\theta$ and $-\theta$ ) |

#### 5. Cautions concerning storage.

- · When storing the product, it is recommended that it be left in its shipping package. After the seal of the packing bag has been broken, store the products in a nitrogen atmosphere.

- · Storage conditions

| Storage state                            | Storage conditions                                |

|------------------------------------------|---------------------------------------------------|

| Unopened(less than 60 days)              | Temperature: 5 to 30°C, humidity: 80% RH or less. |

| A fter coal of broken(less than 30 days) | T 150 DU 1                                        |

- · Don't store in a location exposed to corrosive gas or excessive dust.

- · Don't store in a location exposed to direct sunlight or subject to sharp changes in temperature.

- Don't store the product such that it subjected to an excessive load weight, such as by stacking.

- Deterioration of the plating may occur after long-term storage, so special care is required.

- It is recommended that the products be inspected before use.

#### 6. Other cautions.

- Immediately after opening the moisture-proof packing, the measurement will shrink slightly. In order to return the measurements to those shown in the drawing, it is necessary to store the product for at least 48 hours at a temperature of 20 to 25°C and humidity of 50 to 60%.