# DAC-608, DAC-610, DAC-612 Microprocessor-Compatible, Double-Buffered D/A Converters

### **FEATURES**

- Microprocessor-compatible

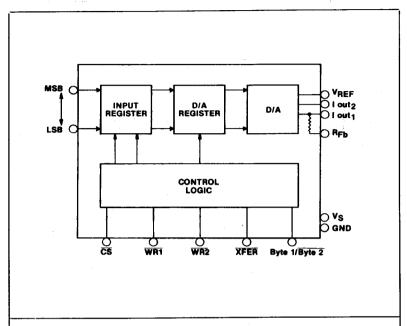

- Double-buffered inputs

- 8- 10- and 12-Bit resolution

- 500 Nanoseconds settling time— DAC-610

- 4-Quadrant multiplication

# **GENERAL DESCRIPTION**

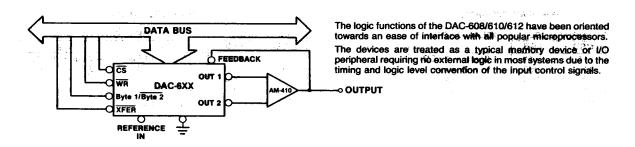

DAC-608. DATEL's DAC-610 DAC-612 are low cost monolithic 8-, 10-and 12-bit multiplying D/A converters designed to operate directly with most popular microprocessors. Double-buffered inputs allow the converters to output an analog voltage corresponding to one digital word while holding the next, permitting simultaneous updating of multiple D/A's via a common strobe signal. The converters appear as a memory location or I/O port to the microprocessor and thus do not require interfacing logic. All models will operate as normal D/A's for nonmicroprocessor based applications.

Excellent temperature tracking characteristics are provided by precision siliconchromium R-2R resistor ladder networks. Output settling time for a full-scale change to ½ LSB, is as low as 500 nanoseconds and the maximum linearity error on all models is ±½ LSB. Monotonicity is guaranteed over the full operating temperature range.

Other features include a low, 3 mV peak-to-peak, digital feedthrough error, 30 mW power dissipation and single supply operation. The reference input is selectable over a range of  $\pm$  10V and may also be used as the analog input for four quadrant multiplication applications.

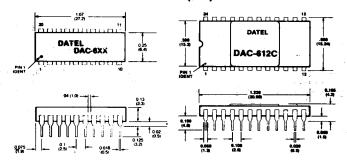

The DAC-612C is packaged in a 24-pin ceramic DIP. Models DAC-608 and DAC-610 are packaged in a 20-pin plastic DIP. All units are specified to operate over the commerical 0°C to +70°C temperature range. These devices are an ideal choice for innumerable applications involving industrial process control, programmable attenuators, audio signal processing and low frequency sine wave generation.

CAUTION: These devices contain CMOS circuits and should be handled with standard anti-static procedures.

# INPUT/OUTPUT CONNECTIONS

|     | DAC-608              |  |

|-----|----------------------|--|

| PIN | FUNCTION             |  |

| 1   | CS (CHIP SELECT)     |  |

| 2   | WR1 (WRITE 1)        |  |

| 3   | ANALOG GROUND        |  |

| 4   | DI3                  |  |

| 5   | DI2                  |  |

| 6   | DI1                  |  |

| 7   | DIO (LSB)            |  |

| 8   | REFERENCE IN         |  |

| 0   | FEEDBACK             |  |

| 10  | DIGITAL GROUND       |  |

| 11  | OUTPUT 1             |  |

| 12  | OUTPUT 2             |  |

| 13  | DI7 (MSB)            |  |

| 14  | DI6                  |  |

| 15  | DI5                  |  |

| 16  | DI4                  |  |

| 17  | XFER (Trans. Contl.) |  |

| 18  | WR2 (Write 2)        |  |

| 19  | ILE (In. Latch ENB)  |  |

| 20  | ٧ <sub>S</sub>       |  |

| PIN | FUNCTION         |  |

|-----|------------------|--|

| 1   | CS (CHIP SELECT) |  |

| 2   | WR (WRITE)       |  |

| 3   | BYTE 1/BYTE 2    |  |

| 4   | XFER             |  |

| 5   | DI5              |  |

| 6   | DI6              |  |

| 7   | DI7              |  |

| 8   | DI8              |  |

| 9   | DI9 (MSB)        |  |

| 10  | GROUND           |  |

| 11  | OUTPUT 2         |  |

| 12  | OUTPUT 1         |  |

| 13  | REFERENCE IN     |  |

| 14  | FEEDBACK         |  |

| 15  | DIO (LSB)        |  |

| 16  | DI1              |  |

| 17  | DI2              |  |

| 18  | DI3              |  |

| 19  | DI4              |  |

| 20  | v <sub>s</sub>   |  |

| PIN         FUNCTION           1         CS (CHIP SELECT)           2         WAT           3         ANALOG GROUND           4         DI5 | }  |

|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2 WR1<br>3 ANALOG GROUND                                                                                                                    | 1  |

| 3 ANALOG GROUND                                                                                                                             |    |

|                                                                                                                                             | ]  |

| 4 DI5                                                                                                                                       | ]  |

|                                                                                                                                             | ]  |

| 5 DI4                                                                                                                                       | ]  |

| 6 DI3                                                                                                                                       | ]  |

| 7 DI2                                                                                                                                       | ]  |

| 8 DI1                                                                                                                                       | ]  |

| 9 DIO (LSB)                                                                                                                                 | ]  |

| 10 REFERENCE IN                                                                                                                             | ]  |

| 11 FEEDBACK                                                                                                                                 | ]  |

| 12 DIGITAL GROUND                                                                                                                           | ]  |

| 13 OUTPUT 1                                                                                                                                 | ]  |

| 14 OUTPUT 2                                                                                                                                 | ]  |

| 15 DI11 (MSB)                                                                                                                               | ]  |

| 16 DI 10                                                                                                                                    | ]  |

| 17 DI9                                                                                                                                      | ]. |

| 18 DI8                                                                                                                                      | ]  |

| 19 DI7                                                                                                                                      | ]  |

| 20 DI6                                                                                                                                      | ]  |

| 21 XFER (Trans. Contl.)                                                                                                                     |    |

| 22 WR2 (Write 2)                                                                                                                            | 1  |

| 23 BYTE 1/BYTE 2                                                                                                                            | ]  |

| 24 VS                                                                                                                                       | ]  |

| ABSOLUTE MAXIMUM RATINGS                                                                             | DAC-608 | DAC-610                                                                             | DAC-612C |

|------------------------------------------------------------------------------------------------------|---------|-------------------------------------------------------------------------------------|----------|

| Power Supply Voltage Logic Input Voltage Reference tribut Voltage Output Voltage Package Dissipation | · .     | + 17V dc<br>V <sub>S</sub> to ground<br>± 25V<br>V <sub>S</sub> to 100 mV<br>500 mW |          |

### **FUNCTIONAL SPECIFICATIONS**

Typical at 25°C, 15V Supply, Reference In = +10V unless otherwise noted.

| INPUTS                                                 | DAC-608                                                                                                                                                                                            | DAC-610                                                                             | DAC-612                                                    |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------|

| Resolution                                             | 8 bits                                                                                                                                                                                             | 10 bits                                                                             | 12 bits                                                    |

| Coding, Unipolar operation                             |                                                                                                                                                                                                    | Straight Binary                                                                     |                                                            |

| Bipolar operation                                      |                                                                                                                                                                                                    | Offset Binary                                                                       | 100                                                        |

| input Logic Level,                                     | 0.004                                                                                                                                                                                              |                                                                                     |                                                            |

| nput Logic Level,<br>bit ON ("1")<br>nput Logic Level, | +2.24                                                                                                                                                                                              | minimum at + 10 μA r                                                                | RECURTURIT                                                 |

| bit OFF ("0")                                          | + 0.8V n                                                                                                                                                                                           | Aبر 200 – naximum at                                                                | maximum                                                    |

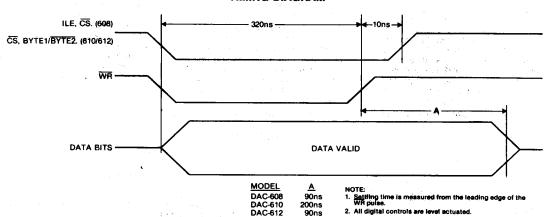

| CS (Chip Select)                                       | Active low state in<br>for Write 1 operationsec. CS must re<br>Write Pulse return                                                                                                                  | n combination with IL<br>tion. Minimum pulse o<br>smain low an addition<br>ts high. | E enables the D/A<br>Juration is 320<br>al 10 nsec. after  |

|                                                        | Active high state in combination with CS enables the D/A for Write 1 operation. Minimum Pulse duration is 320 nsec. ILE must remain high an additional 10 nsec. after Write Pulse returns high.    |                                                                                     |                                                            |

|                                                        | Active low state is<br>the input latch. A<br>update the input I<br>nsec.                                                                                                                           | s used to <u>load</u> the dig<br>high ON WR1, and a<br>latch. Minimum Pulse         | ital data bits into<br>high on ILE will<br>duration is 320 |

| WR2 (Write 2)                                          | Active low in combination with XFER transfers available data in the input latch to the D/A register. The data in the D/A register is latched when WR2 is high. Minimum Pulse Duration is 320 nsec. |                                                                                     |                                                            |

| Byte 1/Byte 2 (Byte Sequence                           |                                                                                                                                                                                                    |                                                                                     |                                                            |

|                                                        | control is high. W                                                                                                                                                                                 | e input latch are enal<br>hen low, only least si<br>uration is 320 nsec.            |                                                            |

| KFER (Transfer Control                                 | Ullabida. I gise D                                                                                                                                                                                 | uration is 020 1150c.                                                               |                                                            |

| Signai)                                                | Active low in com<br>available in the in                                                                                                                                                           | bination with WR2, w<br>put latch to the D/A r                                      | ill transfer the data<br>egister.                          |

| OUTPUTS                                                |                                                                                                                                                                                                    | · · · · · ·                                                                         | 1 1 1                                                      |

| Output Capacitance, Output 13                          | 70 pF                                                                                                                                                                                              | 60 pF                                                                               | 70 pF                                                      |

| Output 2 <sup>3</sup>                                  | 200 pF<br>200 pF                                                                                                                                                                                   | 250 pF                                                                              | 200 pF<br>200 pF                                           |

| Output 14                                              | 200 pF                                                                                                                                                                                             | 250 pF                                                                              | 200 pF                                                     |

| Output 24                                              | /0 p⊩                                                                                                                                                                                              | 250 pF<br>250 pF<br>60 pF                                                           | /U DF                                                      |

| Output 1, Current Ranges                               | VREF D                                                                                                                                                                                             | V <sub>REF</sub> D                                                                  | V <sub>REF</sub> D                                         |

| Julput I, Current nange                                | 15 kΩ 256                                                                                                                                                                                          | 15 kΩ 1024                                                                          | 15 kΩ 4096                                                 |

| Outros O Comment Descript                              | V <sub>REF</sub> 256-D                                                                                                                                                                             | V <sub>REF</sub> 1024-D                                                             | VREF 4006-D                                                |

| Output 2, Current Ranges                               | 15 kΩ 256                                                                                                                                                                                          | 15 kΩ 1024                                                                          | 15 kΩ 4096                                                 |

| eedthrough Error                                       | 3 mV P-P                                                                                                                                                                                           | 90 mV P-P                                                                           | 3 mV P-P                                                   |

| PERFORMANCE                                            |                                                                                                                                                                                                    |                                                                                     |                                                            |

| Linearity Error Maximum                                |                                                                                                                                                                                                    | ± ½ LSB                                                                             | - :                                                        |

| Maximum                                                |                                                                                                                                                                                                    | ±0.018% FSR                                                                         |                                                            |

| Monotonicity                                           | Over                                                                                                                                                                                               | operating temperature                                                               | e range                                                    |

| Sain Error                                             |                                                                                                                                                                                                    | Adjustable to Zero                                                                  | _                                                          |

| Zero Errore                                            | . 6                                                                                                                                                                                                | Adjustable to Zero                                                                  | . 0100                                                     |

| Sain Tempco Maximum                                    | ±6 ppm/°C                                                                                                                                                                                          | ± 10 ppm/°C                                                                         | ±6 ppm/°C                                                  |

| change to ± 1/2 LSB                                    | 1 μsec.<br>± 2 ppm/V                                                                                                                                                                               | 500 nsec.<br>± 30 ppm/V                                                             | 1 μsec.<br>± 3 ppm/V                                       |

| POWER REQUIREMENTS                                     |                                                                                                                                                                                                    |                                                                                     |                                                            |

|                                                        | <del> </del>                                                                                                                                                                                       |                                                                                     |                                                            |

|                                                        |                                                                                                                                                                                                    |                                                                                     |                                                            |

| Rated Power Supply Voltage Power Supply Voltage Range  |                                                                                                                                                                                                    | + 15V dc<br>- 4.7V dc to + 15.75V                                                   | مام                                                        |

Operating Temp.

0°C to 70°C

Storage Temperature -65°C to +150°C

20-pin plastic DIP DAC-612 . . . . 24-pin ceramic DIP

# FOOTNOTES:

- 1. DAC-608 only.

- 2. DAC-610/612 only.

- 3. All data inputs latched low. To achieve this low feedthrough on the DAC-612, the metal lid must be grounded. If the lid is left floating the feedthrough is typically 8 mV.

4. All data inputs latched high.

5. "D" stands for digital input.

- Using internal feedback resistor.

### **TECHNICAL NOTES**

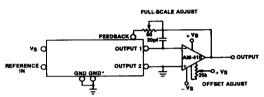

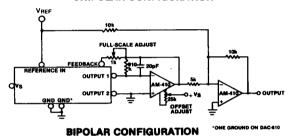

1. The output operational amplifier to be used should have as low a value of input bias current as possible. DATEL's AM-410 operational amplifiers are highly recommended for use with these devices.

In order to maintain the specified temperature tracking specifications, the D/A's internal feedback resistor should be used in the operational amplifier feedback loop.

- 2. The voltage at the current outputs must be as close to ground potential as possible so that the changes in the applied digital codes do not affect the output current linearity.

- 3. In fast data acquisition applications, the addition of a 10 to 22 pF capacitor (Cc) in parallel with the feedback resistor of the operational amplifier may be required to minimize overshoot and ringing at the output.

- 4. Due to the rapid switching of internal logic gates that respond to the input changes, a narrow spike could flow out from the current output terminals. In order to minimize this effect, the input register must always be used as the data latch. Reducing V<sub>S</sub> from +15V to +5V offers a factor of 5 improvement in the magnitude of the feedthrough, however, this causes a loss of internal switching speed. Also, increasing capacitor Cc (if being used) to a value consistent with the actual circuit bandwidth requirements, can provide a substantial damping effect on any output spikes.

- 5. For flow through operation, (operation with the buffers continuously enabled) CS, WR1, WR2 and XFER must be tied to ground and Byte 1/Byte 2 (ILE for DAC-608) must be high. This will allow

DATEL, Inc. 11 Cabot Boulevard, Mansfield, MA 02048-1194/TEL (508) 339-3000/TLX 174388/FAX (508) 339-6356

both internal registers to follow the applied digital inputs, directly affecting the device output.

- 6. For stand alone operation where control signals are generated by discrete logic, double buffering can be controlled by applying a logic "0" to CS and XFER and a logic "1" to ILE and pulling WR1 low to load data in the input latch. Pulling WR2 low will then update the analog output. A logic "1" on either of these lines will prevent the changing of the analog output.

- 7. All unused digital inputs should be tied

to  $V_S$  or ground in order to prevent damage to the chip from static discharge. If any of the digital inputs are inadvertently left floating, the D/A will interpret the pin as a logic "1".

- 8. The input registers of the DAC-610 and DAC-612 are arranged to accept a left justified data word from the microprocessor with 8 bits coming first and the lower bits second. Left-justified means that the binary point is assumed to be located to the left of the most significant bit.

- 9. The use of good circuit board layout

techniques are required for rated performance. Minimization of lead lengths around analog circuitry is recommended. It is important that a good ground be used. A single point ground distribution technique for analog signals and supply returns will prevent other devices in the system from affecting the output of the D/A's.  $V_S$  should be bypassed as close to the  $V_S$  pin as possible with a low inductance 1  $\mu F$  tantalum capacitor.

### **CODING AND CALIBRATION**

### CALIBRATION PROCEDURE

### UNIPOLAR

Zero Adjust—Set all data bits to logic "0" (logic "1" if using output 2) and adjust the OFFSET ADJUST pot on the external operational amplifier for 0.000V.

Full Scale—Set all data bits to logic "1" (logic "0" if using output 2) and set the FULL Scale ADJUST for an output equal to: Vout = - Vref (N - 1)/N, where "N" is equal to: 256 (DAC-608), 1024 (DAC-610) or 4096 (DAC-612).

### **BIPOLAR**

Zero Adjust—Set all data bits to logic "0" and adjust the OFF-SET ADJUST for an output voltage equal to Vref.

Full Scale—Set all data bits to logic "1" and adjust the FULL SCALE ADJUST for an output voltage equal to: Vout = Vref (N-X)/X where "N" is equal to: 255 (DAC-608), 1023 (DAC-610) or 4095 (DAC-612); and "X" is equal to: 128 (DAC-608), 512 (DAC-610) or 2048 (DAC-612).

### UNIPOLAR CONFIGURATION

### **OUTPUT CODING TABLES**

### **UNIPOLAR OPERATION**

| INPUT CODE | IDEAL OUTPUT               |

|------------|----------------------------|

| MSB LSB    |                            |

| 111111     | -(VREF. + 1 LSB)           |

| 110000     | -0.75 (V <sub>REF</sub> )  |

| 100000     | -0.5 (V <sub>REF)</sub>    |

| 010000     | - 0.25 (V <sub>REF</sub> ) |

| 000000     | 0`                         |

## **BIPOLAR OPERATION**

| INPUT | CODE | IDEAL OUTPUT              |                            |  |

|-------|------|---------------------------|----------------------------|--|

| MSB   | LSB  | + VREF                    | - VREF                     |  |

| 111   | 111  | + VREF - 1 LSB            | -VREF + 1 LSB              |  |

| 110   | 000  | 0.5 (+ V <sub>REF</sub> ) | 0.5 ( – V <sub>REF</sub> ) |  |

| 100   | 000  | 0                         | 0                          |  |

| 010   | 000  | 0.5 ( - VREF)             | 0.5 ( + V <sub>REF</sub> ) |  |

| 000   | 000  | - VREF                    | + VREF                     |  |

### TIMING AND PERFORMANCE

### TIMING DIAGRAM

### MECHANICAL DIMENSIONS INCHES (MM)

### **APPLICATIONS**

### Typical Connection to Popular Microprocessor Data Bus

2-22 DATEL, Inc. 11 Cabot Boulevard, Mansfield, MA 02048-1194/TEL (508) 339-3000/TLX 174386/FAX (508) 339-6356

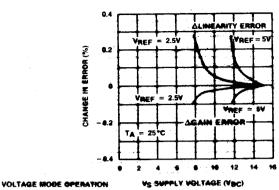

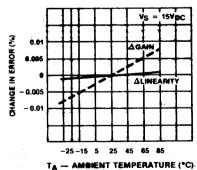

# DAC-608 Gain and Linearity Error Variation vs. Supply Vellage

DAC-608 Gain and Linearity Error Variation vs. Reference Voltage

1

.

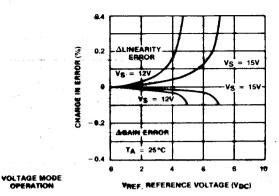

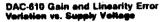

DAC-619 Gain and Linearity Error Variation vs. Reference Voltage

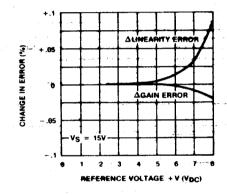

### DAC-612 Gain and Linearity Error Variation vs. Supply Voltage

DATEL, Inc. 11 Cabot Boulevard, Mansfield, MA 02048-1194/TEL (508) 339-3000/TLX 174388/FAX (508) 339-6356

arim etimologi

- 1 × 1 × 1

### **APPLICATIONS**

# **MULTIPLE D/A SYSTEM** FEEDBACK O **DAC 608** ANALOG OUTPUT 1 OUT 2 ILE XFER WR1 WR CS<sub>1</sub> ECODE **ADDRESS** CS(n) BUS FEEDBACK O OUT 1 **DAC 608** ANALOG OUTPUT 2 AM-410 OUT 2 ILE XFER WR1 WR2 FEEDBACK ( OUT 1 **DAC 608** ANALOG OUTPUT(n) OUT 2 ILE XFER WR1 WR2 SYSTEM WR O

# DATA BUS DATA VALID CS WR1 & WR2 INPUT LATCH UPDATED UPDATED ILE = LOGIC "1" D/A REGISTER LATCHED

For simultaneous updating of multiple D/A's, the  $\overline{\text{CS}}$  line of each device is decoded individually. However, the converter can share a common  $\overline{\text{XFER}}$ .

The ILE function is very useful in applications where more than one processor is being used. If another processor took control of the data bus and control lines using the same addresses as the first, a low on the ILE pin would latch the data in the input register holding the outputs at their present state.

| ORDERING INFORMATION |                                 |  |  |

|----------------------|---------------------------------|--|--|

| RESOLUTION           | OPERATING TEMP. RANGE           |  |  |

| 8 Bits               | 0°C to +70°C                    |  |  |

| 10 Bits              | 0°C to +70°C                    |  |  |

| 12 Bits              |                                 |  |  |

|                      | RESOLUTION<br>8 Bits<br>10 Bits |  |  |

\*TIE TO LOGIC 1 IF NOT NEEDED

2-24 DATEL, Inc. 11 Cabot Boulevard, Mansfield, MA 02048-1194/TEL (508) 339-3000/TLX 174388/FAX (508) 339-6356