## **Quad Comparator with Programmable Threshold**

#### General Description

The MAX516 combines four low-power, programmablethreshold comparators on a single CMOS IC. Separate 8-bit digital-to-analog converters (DACs) drive the comparator inverting (-) inputs so that individual trip thresholds can be digitally set. All noninverting (+) comparator inputs are brought out as analog inputs (AINO-AIN3). Each comparator output swings high when its analog input exceeds its digitally set threshold. All four DACs share a common reference input to optimize matching and eliminate external trims.

Digital inputs and comparator outputs are compatible with TTL and CMOS logic. A separate logic supply (VCC) allows comparator output levels to be set independently of VDD. The MAX516 operates conveniently from a single supply with VDD tied to VCC. Commercial, extended, and military temperature ranges are provided in 24-pin narrow DIP and wide SO packages.

#### **Applications**

Window Comparators

Power-Supply Monitors

Alarm Limit Detectors

**Battery Chargers**

Automated Test Equipment

Process Control

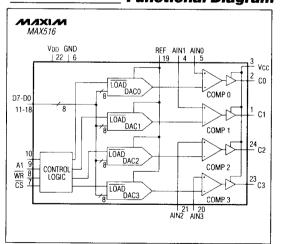

## Functional Diagram

#### Features

- 4 Comparators and 4 DACs

- **Digitally Set Threshold**

- ♦ Monotonic Over Temperature

- Parallel Microprocessor Interface

- ♦ +5V to +15V Supply Operation

### **Ordering Information**

| PART       | TEMP. RANGE     | PIN-PACKAGE           | ERROR<br>(LSBs) |

|------------|-----------------|-----------------------|-----------------|

| MAX516ACNG | 0°C to +70°C    | 24 Narrow Plastic DIP | ±1              |

| MAX516BCNG | 0°C to +70°C    | 24 Narrow Plastic DIP | ±2              |

| MAX516ACWG | 0°C to +70°C    | 24 Wide SO            | ±1              |

| MAX516BCWG | 0°C to +70°C    | 24 Wide SO            | ±2              |

| MAX516BC/D | 0°C to +70°C    | Dice*                 | ±2              |

| MAX516AENG | -40°C to +85°C  | 24 Narrow Plastic DIP | ±1              |

| MAX516BENG | -40°C to +85°C  | 24 Narrow Plastic DIP | ±2              |

| MAX516AEWG | -40°C to +85°C  | 24 Wide SO            | ±1              |

| MAX516BEWG | -40°C to +85°C  | 24 Wide SO            | ±2              |

| MAX516AMRG | -55°C to +125°C | 24 Narrow CERDIP**    | ±1              |

| MAX516BMRG | -55°C to +125°C | 24 Narrow CERDIP**    | ±2              |

- \* Contact factory for dice specifications.

- \*\* Contact factory for availability and processing to MIL-STD-883.

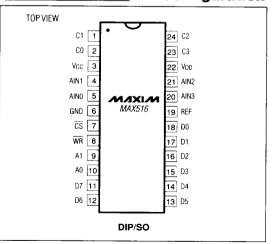

## Pin Configuration

ノレノノメノノレノ

Maxim Integrated Products 3-35

# Quad Comparator with Programmable Threshold

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND                                   | Operating Temperature Ranges:               |

|----------------------------------------------------------|---------------------------------------------|

| V <sub>CC</sub> to GND0.3V, V <sub>DD</sub> + 0.3V       | MAX516_ C                                   |

| V <sub>DD</sub> to V <sub>CC</sub>                       | MAX516_ E40°C to +85°C                      |

| Digital Input Voltage to GND0.3V, V <sub>DD</sub> + 0.3V | MAX516_ MRG55°C to +125°C                   |

| REF to GND0.3V, V <sub>DD</sub> + 0.3V                   | Storage Temperature Range65°C to +165°C     |

| Comparator Input to GND0.3V, V <sub>DD</sub> + 0.3V      | Lead Temperature (soldering, 10 sec) +300°C |

| C0-C3 to GND (Note 1) GND, V <sub>CC</sub> + 0.3V        | •                                           |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)    |                                             |

| Narrow Plastic DIP (derate 8.7mW/°C above +70°C) 480mW   |                                             |

| Wide SO (derate 11.8mW/°C above 170°C) 650mW             |                                             |

Note 1: The outputs may be shorted to GND or VDD, provided the package's power dissipation is not exceeded.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

Narrow CERDIP (derate 12.5mW/°C above +70°C) . 690mW

(VDD = VCC = +4.75V, REF = +1.25V or VDD = VCC = +16.5V, REF = +10V; GND = 0V; TA = TMIN to TMAX, unless otherwise noted.)

| PARAMETER                                      | SYMBOL                    | CONDITIONS                       |         | MIN  | TYP | MAX                   | UNITS  |  |

|------------------------------------------------|---------------------------|----------------------------------|---------|------|-----|-----------------------|--------|--|

| STATIC PERFORMANCE                             |                           |                                  |         |      |     |                       |        |  |

| Resolution                                     | N                         |                                  |         | 8    |     |                       | Bits   |  |

| Total Unadjusted Error                         | TUE                       | MAX516A                          |         |      |     | ±1                    |        |  |

| rotal Orladjusted Error                        | TUE                       | MAX516B                          |         |      |     | ±2                    | LSB    |  |

| Deletine Assurace                              | INL                       | MAX516A                          |         |      |     | ±0.5                  | LCD    |  |

| Relative Accuracy                              | IINL                      | MAX5                             | 16B     |      |     | ±1                    | LSB    |  |

| Differential Nonlinearity                      | DNL                       | Guaranteed monotonic             |         |      |     | ±1                    | LSB    |  |

| Full-Scale Error                               |                           | MAX516A<br>MAX516B               |         |      | -   | ±0.5                  | 1.00   |  |

| Full-Scale Error                               |                           |                                  |         |      |     | ±1                    | LSB    |  |

| Full-Scale Temperature<br>Coefficient          |                           | V <sub>DD</sub> = 15V, REF = 10V |         |      | ±5  |                       | ppm/°C |  |

|                                                |                           | T <sub>A</sub> = +25°C           | MANGICA |      |     | ±5                    |        |  |

| Zero-Code Error                                |                           | TA = TMIN to TMAX                | MAX516A |      |     | ±10                   |        |  |

| Zero-Code Error                                |                           | T <sub>A</sub> = +25°C           |         |      |     | ±10                   | mV     |  |

|                                                |                           | TA = TMIN to TMAX                | MAX516B |      | ±15 |                       |        |  |

| Zero-Code Temperature<br>Coefficient           |                           |                                  |         |      | ±30 |                       | μV/°C  |  |

| <b>REFERENCE INPUT</b> (4.75V ≤ V <sub>I</sub> | OD ≤ 16.5V)               |                                  |         |      |     |                       |        |  |

| Reference Input Range                          | REF                       |                                  |         | 1.25 |     | V <sub>DD</sub> -3.50 | V      |  |

| Reference Input Resistance                     | RREF                      | Worst-case code                  |         | 3.0  | 4.5 | -                     | kΩ     |  |

| Reference Input Capacitance                    | CREF                      | Worst-case code (Note 2)         |         |      | 100 | 250                   | рF     |  |

| COMPARATOR INPUT (4.75V s                      | ≤ V <sub>DD</sub> ≤ 16.5V | ′)                               |         |      |     |                       |        |  |

| Comparator Input Range                         | VAIN                      |                                  |         | 0    |     | V <sub>DD</sub>       | V      |  |

| Comporator Input Bios Compo                    |                           | T <sub>A</sub> = +25°C           |         |      | 50  | 300                   | nA     |  |

| Comparator Input Bias Current                  | lΒ                        | TA = TMIN to TMAX                |         |      | 100 | 100 400               |        |  |

# **Quad Comparator with Programmable Threshold**

## **ELECTRICAL CHARACTERISTICS (continued)**

(VDD = VCC = +4.75V, REF = +1.25V or VDD = VCC = +16.5V, REF = +10V; GND = 0V; TA = TMIN to TMAX, unless otherwise noted.)

| PARAMETER                             | SYMBOL          | CONDITIONS                               | MIN   | TYP | MAX     | UNITS |

|---------------------------------------|-----------------|------------------------------------------|-------|-----|---------|-------|

| DIGITAL INPUTS DO-D7, WR, CS, (       | 4.75V ≤ VD(     | ) ≤ 16.5V)                               |       |     |         |       |

| Input High Voltage                    | VINH            |                                          | 2.4   |     |         | ٧     |

| Input Low Voltage                     | VINL            |                                          |       |     | 0.8     | V     |

| Input Leakage Current                 | IIN             | VIN = 0V or VDD                          |       |     | ±1      | μА    |

| Input Capacitance                     | CIN             | (Note 2)                                 |       |     | 10      | pF    |

| DIGITAL OUTPUTS CO-C3 (VCC =          | 5V)             |                                          |       |     |         |       |

| Output High Voltage                   | Voн             | ISOURCE = 200µA                          | Vcc-1 |     |         | V     |

| Output Low Voltage                    | Vol             | ISINK = 1.6mA                            |       |     | 0.4     | V     |

| <b>DYNAMIC PERFORMANCE (1.25V</b>     | ≤ REF ≤ VDI     | o -3.5V, 0V ≤ AIN < V <sub>DD</sub> -2V) |       |     |         |       |

| Digital Input to Comparator Out Delay | tDCO            | (Note 3)                                 |       | 0.8 | 2.0     | μs    |

| Analog Input to Comparator Out Delay  | tACO            | (Note 4)                                 |       | 0.8 | 1.5     | μs    |

| TIMING CHARACTERISTICS                |                 |                                          |       |     |         |       |

| CS to WR Setup Time                   | tcs             |                                          | 0     |     |         | ns    |

| CS to WR Hold Time                    | tcH             |                                          | 0     |     |         | ns    |

| Address to WR Setup Time              | tas             |                                          | 50    | 30  |         | ns    |

| Address to WR Hold Time               | tah             |                                          | 5     | 0   |         | ns    |

| Data Valid to WR Setup Time           | tos             |                                          | 50    | 30  |         | ns    |

| Data Valid after WR Hold Time         | tDH             |                                          | 5     | 0   |         | ns    |

| WRITE Pulse Width                     | twn             |                                          | 120   | 50  |         | ns    |

| POWER SUPPLIES                        |                 |                                          |       |     |         |       |

| V <sub>DD</sub> Range                 | V <sub>DD</sub> |                                          | 4.75  |     | 16.5    | V     |

| VCC Range                             | Vcc             |                                          | 4.75  | V   | DD+0.30 | V     |

| Positive Supply Current               | loo             | Logic inputs < VIL or > VIH              |       |     | 10      | mA    |

| Logic Supply                          | Icc             |                                          |       |     | 10      | μА    |

Note 2:

Guaranteed by design. Not production tested.

VDD = 5.00V, differential comparator input voltage changes by 1.25V with 5mV overdrive. V<sub>IN</sub> must be 3.5V less than V<sub>DD</sub>, Note 3:

or longer propagation delays will result.

Note 4: Not tested, but guaranteed by correlation to tpco.

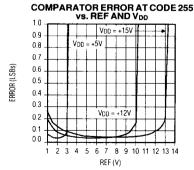

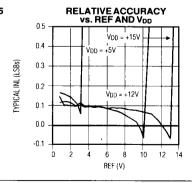

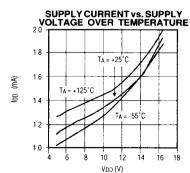

### **Typical Operating Characteristics**

/VI/IXI/VI

23. 24

C3. C2

# **Quad Comparator with Programmable Threshold**

#### **Pin Description**

|        |            | po.                      |

|--------|------------|--------------------------|

| PIN    | NAME       | FUNCTION                 |

| 1, 2   | C1, C0     | Comparator Outputs       |

| 3      | Vcc        | Comparator Output Supply |

| 4, 5   | AIN1, AIN0 | Comparator Analog Inputs |

| 6      | GND        | Ground                   |

| 7      | ĊŚ         | CHIP SELECT              |

| 8      | WR         | WRITE                    |

| 9, 10  | A1 , A0    | DAC Address Inputs       |

| 11-18  | D7-D0      | DAC Data Inputs, 8 bits  |

| 19     | REF        | Reference Input          |

| 20, 21 | AIN3, AIN2 | Comparator Analog Inputs |

| 22     | VDD        | Positive Supply Voltage  |

#### **Detailed Description**

The MAX516 contains four analog comparators and four matched 8-bit digital-to-analog converters (DACs). The voltage output of each DAC is expressed in the equation:

VDAC = REF x N/256.

Comparator Outputs

where N is the numerical equivalent of the 8-bit DAC input code (D0-D7). N ranges from 0 to 255 and may be set to a different level for each DAC (Table 1). The DAC output, VDAC, does not appear on an output pin of the MAX516 but is instead compared to an analog input signal by one of four internal comparators (see *Functional Diagram*). A comparator output is high when AIN is more positive than the comparator's digitally set threshold.

Table 1. Comparator Threshold vs. DAC Input Code

| DAC ( | CODE<br>LSB | COMPARATOR THRESHOLD                                |

|-------|-------------|-----------------------------------------------------|

| 1111  | 1111        | +REF $\left(\frac{255}{256}\right)$                 |

| 1000  | 0001        | +REF $\left(\frac{129}{256}\right)$                 |

| 1000  | 0000        | $+REF\left(\frac{128}{256}\right) = +\frac{REF}{2}$ |

| 0111  | 1111        | +REF $\left(\frac{127}{256}\right)$                 |

| 0000  | 0001        | +REF $\left(\frac{1}{256}\right)$                   |

| 0000  | 0000        | OV                                                  |

**NOTE:** 1LSB = (REF)  $(2^{-8})$  = +REF  $\left(\frac{1}{256}\right)$

#### Reference Input

Comparator trip thresholds vary digitally between 0V and 1LSB below REF. All DACs share the same reference input.

The input impedance of REF is code dependent. The lowest impedance, typically  $2k\Omega$ , occurs when 0101 0101 (HEX 55) is loaded into D0-D7 on all four DACs. When 0000 0000 is loaded into all DACs, REF appears as an open circuit. Because the input resistance at REF is code dependent, the reference source should have an output impedance of no more than  $4\Omega$  to maintain linearity. Input capacitance at REF is also code dependent and typically varies between 100pF and 250pF.

#### **Comparator Inputs**

The "+" input of each comparator is brought out to AIN0-AIN3. Comparator input bias current is typically 100nA. Analog source resistances below 1.25k $\Omega$  generate less than 250 $\mu$ V of bias-current induced comparator offset error.

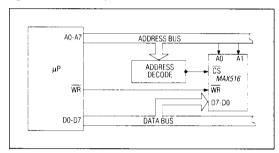

#### Digital Interface

The digital inputs (D0-D7,  $\overline{CS}$ ,  $\overline{WR}$ ) are both TTL and 5V CMOS logic compatible; however, the power-supply current, Ipp, depends on input logic levels. Supply currents will be highest with TTL levels (tested limits are with worst-case logic levels). Supply current is reduced when digital inputs are driven near GND and above 4V.

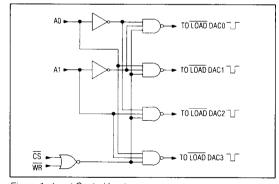

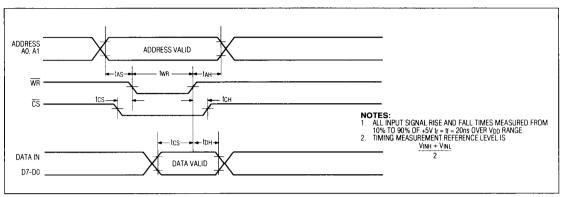

Address lines A0 and A1 select which DAC receives data from the input port. Because  $\overline{CS}$  and  $\overline{WR}$  are internally ORed, the write cycle begins only after both go low, but data is latched and transferred to a DAC when either input returns high. Figure 1 shows the input control logic, Table 2 lists DAC addresses, and Table 3 is the truth table for  $\overline{WR}$  and  $\overline{CS}$ . Figure 2 shows write-cyle timing.

Figure 1. Input Control Logic

# Quad Comparator with Programmable Threshold

Figure 2. Write-Cycle Timing

Table 2. DAC Addressing

|   |    |    | _                   |

|---|----|----|---------------------|

| - | \1 | A0 | SELECTED DAC        |

|   | 0  | 0  | DAC0 Input Register |

|   | 0  | 1  | DAC1 Input Register |

|   | 1  | 0  | DAC2 Input Register |

|   | 1  | 1  | DAC3 Input Register |

Table 3. Write-Cycle Truth Table

| ĊŚ | WR | FUNCTION                                                                                    |

|----|----|---------------------------------------------------------------------------------------------|

| 1  | ×  | No operation. The MAX516 is deselected. Existing register contents remain unchanged.        |

| 0  | 0  | DAC contents for selected address are loaded, but do not update the DAC until WR goes high. |

| 0  | 1  | Latch D0-D7 into input register of the selected DAC on rising edge.                         |

NOTES: X = Don't Care, ↑= Rising Edge

# Applications Information Power-Supply and Reference Operating Ranges

The MAX516 is fully specified to operate with VDD between +4.75V and +16.5V and is specified to operate with a reference input range of +1.25V to VDD -3.5V.

The comparator output supply, VCC, has a range of +4.5V to (VDD + 0.3V). This allows the comparators' logic-high output levels to be set independently from VDD. In most applications, simply connect VCC and VDD together.

Comparator outputs typically swing within 200mV of the supply rails when loaded with CMOS logic inputs.

#### Hysteresis

When analog input signals are slow moving or contain noise, comparator outputs may "chatter" near the threshold point. Be sure that proper power-supply bypass capacitors are in place (see *Grounds and Bypassing* section), because supply current rises when an output switches.

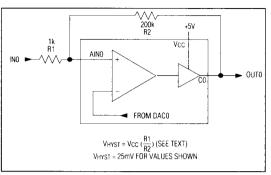

Hysteresis may be added to any or all comparators to further resist oscillation during output transitions. This is accomplished with two resistors, as shown in Figure 3. When hysteresis is added, the threshold point will shift slightly as a result of the voltage divider formed by R1 and R2. The amount of shift is described below:

$$\begin{split} V_{TH} &= V_T \left(\frac{R1}{R2} + 1\right) \\ V_{TL} &= V_T \left(\frac{R1}{R2} + 1\right) - V_{CC} \left(\frac{R1}{R2}\right) \\ V_{HYST} &= V_{TH} - V_{TL} \\ V_{HYST} &= V_{CC} \left(\frac{R1}{R2}\right) \end{split}$$

VT is the threshold voltage set by the internal DAC with no hysteresis connected. VTH is the shifted high-going threshold with hysteresis added. VTL is the shifted low-going threshold with hysteresis. VHYST is the total hysteresis and equals VTH - VTL. Note that VTL and VHYST change with VCC. With VCC = 5V, R1 = 1k $\Omega$ , and R2 = 200k $\Omega$ , VHYST = 25mV. Even though R1 is relatively small, the impedance seen by the signal source is large: R1 + R2. However, if R1 is large, input bias current (400nA

# Quad Comparator with Programmable Threshold

Figure 3. Adding Hysteresis to Any Comparator

max over temp.) may add offset error.  $1k\Omega \times 400nA = 0.4mV$  offset error is due to bias current.

#### Grounds and Bypassing

Careful PC-board layout significantly minimizes crosstalk among the reference input, comparator outputs, and digital inputs. Keep digital and analog lines separate, and use ground traces as shields between them where possible. Separate AIN0-AIN3 and REF from each other by running a ground trace between these pins.

Bypass both VDD and VCC to GND with a combination of a  $0.1\mu\text{F}$  low ESR and a  $4.7\mu\text{F}$  capacitor close to the device. If VDD and VCC are connected together, only one set of bypass capacitors is needed. If REF is not an AC input, it should be bypassed as well. Keep bypass-capacitor leads short for best supply noise rejection.

#### **Applications**

Threshold detection is often useful in automated test applications. Four individual thresholds can be independently altered under software control.

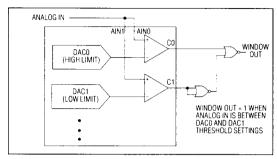

Figure 4 shows the connection for a hardware window comparison. DAC0 provides the upper trip point, DAC1 the lower trip point. The difference between the trip points is the window size. The AIN0 and AIN1 inputs are tied together. One logic output is inverted and then ORed with the noninverted comparator output. The window output goes high when the analog input sits between the thresholds set by DAC0 and DAC1. The external logic in Figure 4 can also be simulated in software, or use a single comparator to perform a window comparison by loading two threshold limits in succession and noting the comparator results of each (Figure 5).

Figure 4. Window Comparison

Figure 5. Microprocessor Interface

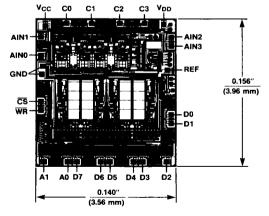

## Chip Topography

NOTE: Substrate connected to VDD

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.