# **DEM-PCM1800 INSTRUCTION MANUAL**

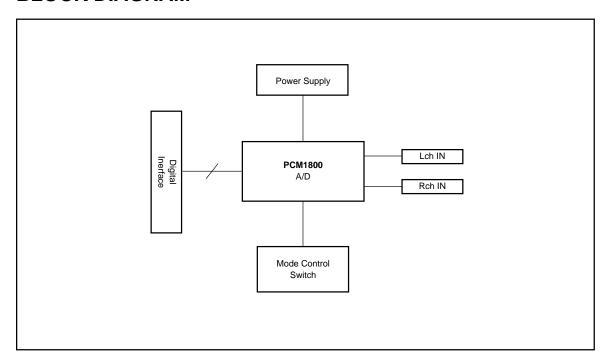

### DESCRIPTION

DEM-PCM1800 is an evaluation board for the PCM1800 20-bit stereo audio analog-to-digital converter. The board contains a 24-pin SSOP IC socket, mode control switch, and some bypass capacitors.

DEM-PCM1800 can be operated by connecting only a power supply and system clock (either of  $256f_S$  or  $384f_S$  or  $512f_S$ ). There are two kinds of operation modes: Master Mode, and Slave Mode for operation of the PCM1800.

In Master Mode, LRCK, BCK, FSYNC, and DATA, are outputs. In Slave Mode, DEM-PCM1800 requires LRCK, BCK, FSYNC inputs, and outputs DATA.

## **BLOCK DIAGRAM**

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111 Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

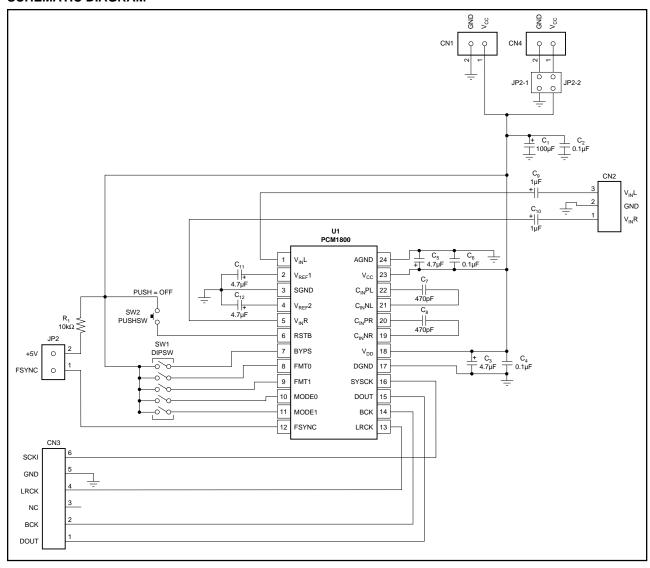

# DEM-PCM1800 BASIC CONNECTIONS AND OPERATION

- Power supply can be provided at +V<sub>CC</sub>, GND connector CN1

- Audio analog inputs are  $V_{IN}L,\,V_{IN}R$  connector CN2.

- Digital ground return to digital interface source should be connected at GND, connector CN3.

- System clock (either of 256f<sub>S</sub> or 384f<sub>S</sub> or 512f<sub>S</sub>) should be provided at SCLK, connector CN3.

- Operation Mode (master mode or slave mode) and selection of system clock can be controlled by switch MODE 0, MODE 1.

- The high pass filter function can be controlled by the switch bypass.

- Audio data format can be controlled by switch FMT0, FMT1.

- To enable the reset function push RESET (switch SW2).

#### **Master Mode Operation**

- LRCK, BCK, DATA, are outputs for PCM Audio data.

- LRCK, BCK, DATA, outputs are located at connector CN3.

#### **Slave Mode Operation**

- LRCK, BCK, DATA, are inputs for PCM Audio data. Synchronized timing between LRCK (f<sub>S</sub>) and system clock (256f<sub>S</sub>, 384f<sub>S</sub>, 512f<sub>S</sub>) is required.

- LRCK, BCK, DATA, inputs are located at connector CN3 and are selected by setting FSYNC = H connecting JP2.

#### **SCHEMATIC DIAGRAM**

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

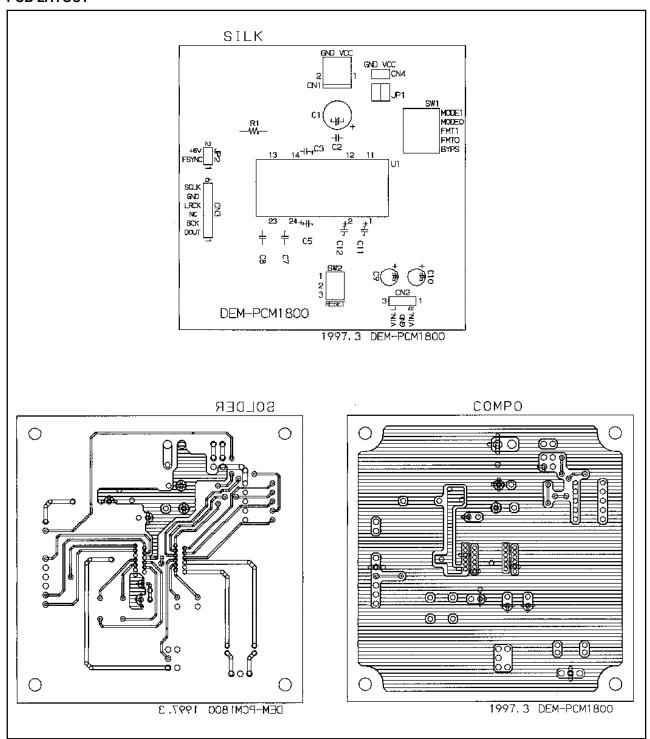

#### **PCB LAYOUT**