# National Semiconductor

# DH0034 High Speed Dual Level Translator

#### **General Description**

The DH0034 is a high speed level translator suitable for interfacing to MOS or junction FET analog switches. It may also be used as a universal logic level shifter capable of accepting TTL/DTL input levels and shifting to CML, MOS, or SLT levels.

#### **Features**

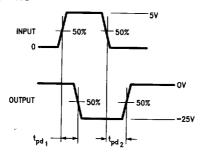

- Fast switching, t<sub>pd0</sub>: typically 15 ns; t<sub>pd1</sub>: typically 35 ns

- Large output voltage range: 25V

- Input is TTL/DTL compatible

- Low output leakage: typically 0.1 μA

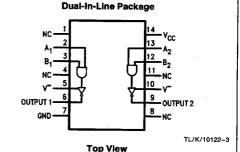

### **Schematic and Connection Diagrams**

Order Number DH0034D-MIL or DH0034CD See NS Package Number D14D

J

#### **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

V<sub>CC</sub> Supply Voltage 7.0V Negative Supply Voltage -30V

Positive Supply Voltage +25V

Differential Supply Voltage 25V

Maximum Output Current 100 mA

Maximum Output Current 100 mA

Power Dissipation (Note 4)

Input Voltage

Operating Temperature Range DH0034D-MIL DH0034CD

-55°C to +125°C 0°C to +85°C

Storage Temperature Range Lead Temperature (Soldering, 10 sec.) -65°C to 150°C 300°C

+ 5.5V

#### Electrical Characteristics (See Notes 1 and 2)

| Parameter                            | Conditions                                                                                                    | DH0034 |                                               |           | Units |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------|-----------|-------|

|                                      |                                                                                                               | Min    | Тур                                           | Max       |       |

| Logical "1"<br>Input Voltage         | V <sub>CC</sub> = 4.5V<br>V <sub>CC</sub> = 4.75V                                                             | 2.0    |                                               |           | ٧     |

| Logical "0"<br>Input Voltage         | $V_{CC} = 5.5V$ $V_{CC} = 5.25V$                                                                              |        |                                               | 0.8       | v     |

| Logical "1"<br>Input Current         | $V_{CC} = 5.5V, V_{IN} = 2.4V$<br>$V_{CC} = 5.25V, V_{IN} = 2.4V$                                             |        |                                               | 40        | μА    |

| Logical "1"                          | $V_{CC} = 5.5V, V_{IN} = 5.5V$<br>$V_{CC} = 5.25V, V_{IN} = 5.5V$                                             |        |                                               | 1.0       | + mA  |

| Logical "0"<br>Input Current         | $V_{CC} = 5.5V, V_{IN} = 0.4V$<br>$V_{CC} = 5.25V, V_{IN} = 0.4V$                                             |        |                                               | 1.6       | mA    |

| Power Supply Current Logic "0"       | V <sub>CC</sub> = 5.5V, V <sub>IN</sub> = 4.5V<br>V <sub>CC</sub> = 5.25V, V <sub>IN</sub> = 4.5V<br>(Note 3) |        | 30                                            | 38        | mA    |

| Power Supply<br>Current<br>Logic "1" | $V_{CC} = 5.5V, V_{IN} = 0V$ $V_{CC} = 5.25V, V_{IN} = 0V$ (Note 3)                                           |        | 37                                            | 48        | mA    |

| Logical "0"<br>Output Voltage        | $V_{CC} = 4.5V$ , $I_{OUT} = 100 \text{ mA}$<br>$V_{CC} = 4.5V$ , $I_{OUT} = 50 \text{ mA}$                   |        | V <sup>-</sup> + 0.50<br>V <sup>-</sup> + 0.3 | V- + 0.50 | v     |

| Output Leakage<br>Current            | $V_{CC} = 5.5V, V_{IN} = 0.8V$<br>$V^{+} - V^{-} = 25V$                                                       |        | 0.1                                           | 5.0       | μΑ    |

| Transition Time to Logical "0"       | $V_{CC} = 5.0V, V_3 = 0V, T_A = 25^{\circ}C$<br>$V^- = 25V, R_L = 510\Omega$                                  |        | 15                                            | 25        | ns    |

| Transition Time to Logical "1"       | $V_{CC} = 5.0V, T_A = 25^{\circ}C$<br>$V^{-} = -25V, R_L = 510\Omega$                                         |        | 35                                            | 75        | ns    |

Note 1: The specifications apply over the temperature range  $-55^{\circ}$ C to  $+125^{\circ}$ C for the DH0034D-MIL and over the temperature range  $-25^{\circ}$ C to  $+85^{\circ}$ C for DH0034CD with a 510Ω resistor connected between output and ground, and V<sup>-</sup> connected to -25V, unless otherwise specified.

Note 2: All typical values are for  $T_A = 25$ °C.

Note 3: Current measured is total drawn from  $V_{CC}$  supply.

Note 4: Power rating for the Cavity DIP based on a maximum junction temperature of 175°C and  $\theta_{JA} = 180$ °C/W.

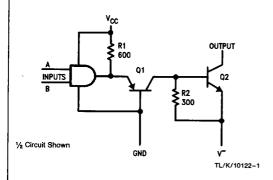

#### Theory of Operation

When both inputs of the DH0034 are raised to logic "1", the input AND gate is turned "on" allowing Q1's emitter to become forward biased. Q1 provides a level shift and constant output current. The collector current is essentially the same as the emitter which is given by

$$\frac{V_{CC} - V_{BE}}{R1}$$

Approximately 7.0 mA flows out of Q1's collector.

About 2 mA of Q1's collector current is drawn off by pull down resistor, R2. The balance, 5 mA, is available as base drive to Q2 and to charge its associated Miller capacitance. The output is pulled to within a VSAT of V-. When either (or both) input to the DH0034 is lowered to logic "0", the AND gate output drops to 0.2V turning Q1 off. Deprived of base drive Q2 rapidly turns off causing the output to rise to the V3 supply voltage. Since Q2's emitter operates between 0.6V and 0.2V, the speed of the DH0034 is greatly enhanced.

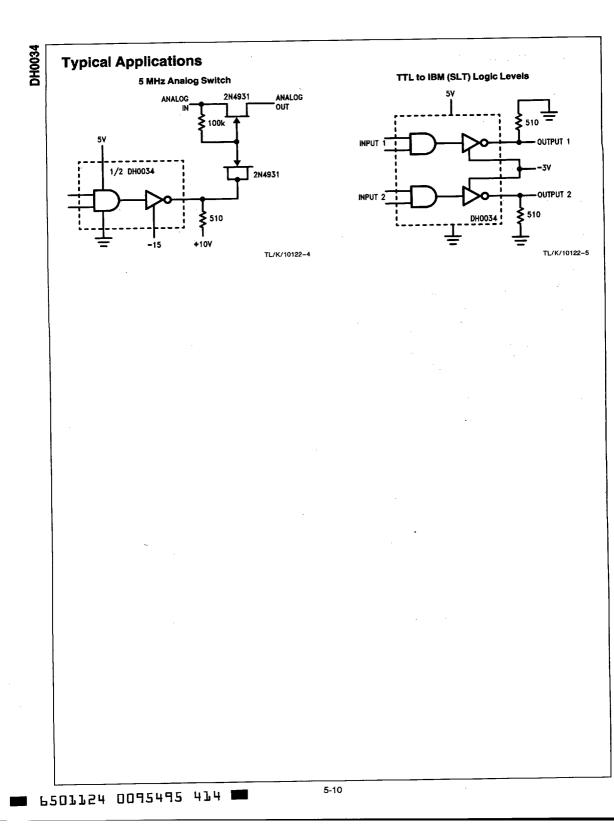

### **Applications Information**

#### 1. Paralleling the Outputs

The outputs of the DH0034 may be paralleled to increase output drive capability or to accomplish the "wire OR". In order to prevent current hogging by one output transistor or the other, resistors of  $2\Omega/100$  mA value should be inserted between the emitters of the output transistors and the minus supply.

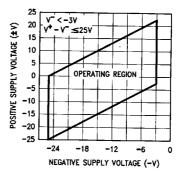

#### 2. Recommended Output Voltage Swing

The graph shows boundary conditions which govern proper operation of the DH0034. The range of operation for the negative supply is shown on the X axis and must be between -3V and -25V. The allowable range for the positive supply is governed by the value chosen for V-. V+ may be selected by drawing a vertical line through the selected value for V - and terminated by the boundaries of the operating region. For example, a value of V- equal to -6V would dictate values of V+ between -5V and +19V. In general, it is desirable to maintain at least 5V difference between the supplies.

TL/K/10122-6

## **Switching Time Waveforms**

TL/K/10122-7

5-9