# Am73/8303 • Am73/8304B

Octal Three-State Bidirectional Bus Transceivers

## DISTINCTIVE CHARACTERISTICS

- 8-bit bidirectional data flow reduces system package count

- 3-state inputs/outputs for interfacing with bus-oriented systems

- · PNP inputs reduce input loading

- V<sub>CC</sub> -1.15V V<sub>OH</sub> interfaces with TTL, MOS and CMOS

- 48mA, 300pF bus drive capability

- Am73/8303 inverting transceivers

- Am73/8304B noninverting transceivers

- Transmit/Receive and Chip Disable simplify control logic

- 20-pin ceramic and molded DIP package

- Low power 8mA per bidirectional bit

- Advanced Schottky processing

- Bus port stays in hi-impedance state during power up/down

- 100% product assurance screening to MIL-STD-883 requirements

#### **FUNCTIONAL DESCRIPTION**

The Am73/8303 and Am73/8304B are 8-bit 3-State Schottky transceivers. They provide bidirectional drive for bus-oriented microprocessor and digital communications systems. Straight through bidirectional transceivers are featured, with 16mA drive capability on the A ports and 48mA bus drive capability on the B ports. PNP inputs are incorporated to reduce input loading.

One input, Transmit/Receive determines the direction of logic signals through the bidirectional transceiver. The Chip Disable input disables both A and B ports by placing them in a 3-state condition. Chip Disable is functionally the same as an active LOW chip select.

The output high voltage (V<sub>OH</sub>) is specified at V<sub>CC</sub> -1.15V minimum to allow interfacing with MOS, CMOS, TTL, ROM, RAM, or microprocessors.

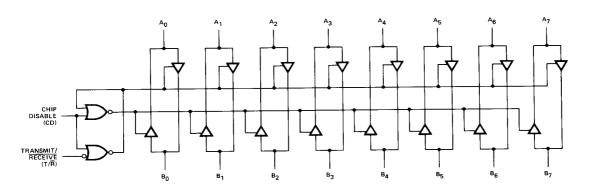

### Am73/8304B LOGIC DIAGRAM

Am73/8303 has inverting transceivers

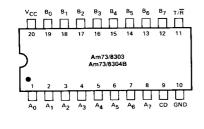

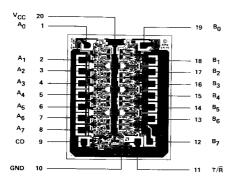

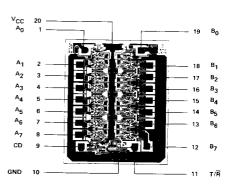

# CONNECTION DIAGRAM Top View

Note: Pin 1 is marked for orientation.

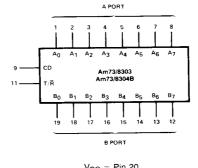

## LOGIC SYMBOL

$V_{CC} = Pin 20$ GND = Pin 10

12-17

# ABSOLUTE MAXIMUM RATINGS (Above which the useful life may be impaired)

| Storage Temperature                      | 05.4- 4500    |

|------------------------------------------|---------------|

| Supply Voltage                           | -65 to +150°C |

| Input Voltage                            | 7.0V          |

|                                          | 5.5V          |

| Output Voltage                           | 5.5V          |

| Lead Temperature (Soldering, 10 seconds) | 300°C         |

|                                          |               |

### **ELECTRICAL CHARACTERISTICS**

The Following Conditions Apply Unless Otherwise Noted:

MIL COM'L

$T_A = -55 \text{ to } +125^{\circ}\text{C}$  $T_A = 0 \text{ to } +70^{\circ}\text{C}$   $V_{CC}$  MIN = 4.5V  $V_{CC}$  MIN = 4.75V

$V_{CC}$  MAX = 5.5V

$V_{CC}$  MAX = 5.25V DC ELECTRICAL CHARACTERISTICS over operating temperature range Тур **Parameters** Description **Test Conditions** Min (Note 1) Max Units A PORT (A<sub>0</sub>-A<sub>7</sub>) VIH Logical "1" Input Voltage  $CD = V_{IL} MAX, T/\overline{R} = 2.0V$ 2.0 Volts  $\frac{\text{CD}}{\text{T/R}} = \text{V}_{\text{IL}} \text{ MAX},$   $\frac{\text{T/R}}{\text{R}} = 2.0 \text{V}$ VIL COMIL Logical "0" Input Voltage 0.8 Volts MIL  $V_{OH}$  $\frac{CD}{T/R} = V_{IL} MAX,$  T/R = 0.8VLogical "1" Output Voltage  $l_{OH} = -0.4mA$ V<sub>CC</sub>-1.15 V<sub>CC</sub>-0.7 Volts  $I_{OH} = -3.0 \text{mA}$ 3.95 I<sub>OL</sub> = 8mA VOL Logical "0" Output Voltage  $\frac{\text{CD}}{\text{T/R}} = V_{\text{IL}} \text{ MAX},$   $\frac{\text{T/R}}{\text{R}} = 0.8 \text{V}$ 0.3 0.4 Volts COM'L I<sub>OL</sub> = 16mA 0.35 0.50  $CD = V_{IL} MAX, T/\overline{R} = 0.8V, V_O = 0V, V_{CC} = MAX, Note 2$ los Output Short Circuit Current -10-38 -75 mA Ιн Logical "1" Input Current CD =  $V_{IL}$  MAX,  $T/\overline{R}$  = 2.0V,  $V_{I}$  = 2.7V 0.1 80 μА ų Input Current at Maximum Input Voltage CD = 2.0V, VCC MAX, VI = VCC MAX mΑ I<sub>I</sub>L Logical "0" Input Current  $CD = V_{IL} MAX, T/\overline{R} = 2.0V, V_I = 0.4V$ -70 -200 μA V<sub>C</sub> Input Clamp Voltage  $CD = 2.0V, I_{IN} = -12mA$ -0.7-1.5 Volts lop Output/Input 3-State Current  $V_0 = 0.4V$ CD = 20V-200 μΑ  $V_0 = 4.0V$ 80 B PORT (B<sub>0</sub>-B<sub>7</sub>) VIH Logical "1" Input Voltage CD = VIL MAX, T/R = VIL MAX 2.0 Volts  $\begin{array}{l} C\underline{D} = \text{V}_{IL} \text{ MAX,} \\ T/\overline{R} = \text{V}_{IL} \text{ MAX} \end{array}$  $V_{IL}$ COMI Logical "0" Input Voltage 0.8 Volts Mit 0.7  $I_{OH} = -0.4mA$ V<sub>CC</sub>-1.15 V<sub>CC</sub>-0.8 VOH  $\frac{CD}{T/R} = V_{IL} MAX,$   $\frac{D}{T/R} = 2.0V$ Logical "1" Output Voltage  $I_{OH} = -5.0 mA$ 2.7 3.9 Volts I<sub>OH</sub> = -10mA 2.4 3.6 VOL  $\frac{CD}{T/R} = V_{IL} MAX$  $I_{OL} = 20mA$ Logical "0" Output Voltage 0.3 0.4 Volts l<sub>OL</sub> = 48mA 0.5  $CD = V_{IL} MAX, T/\overline{R} = 2.0V, V_{O} = 0V$   $V_{CC} = MAX, Note 2$ los Output Short Circuit Current -25 -50-150mΑ Logical "1" Input Current ш  $CD = V_{iL} MAX, T/\overline{R} = V_{iL} MAX, V_i = 2.7V$ 0.1 80 иA ł Input Current at Maximum Input Voltage CD = 2.0V,  $V_{CC} = MAX$ ,  $V_I = V_{CC} MAX$ mA Ι<sub>ΙL</sub> Logical "0" Input Current  $CD = V_{IL} \text{ MAX, T/$\overline{R}$} = V_{IL} \text{ MAX, V}_{I} = 0.4V$ -70 -200 μA V<sub>C</sub> Input Clamp Voltage  $CD = 2.0V, I_{1N} = -12mA$ -0.7-1.5 Volts lop Output/Input 3-State Current  $V_O = 0.4V$ CD = 2.0V-200 μА  $V_0 = 4.0V$ 200 CONTROL INPUTS CD, T/R  $V_{IH}$ Logical "1" Input Voltage 2.0 Volts  $V_{\rm IL}$ Logical "0" Input Voltage COMI 0.8 Volts MIL 0.7 Logical "1" Input Current Ιн  $V_1 = 2.7V$ 0.5 20 щA ų Input Current at Maximum Input Voltage V<sub>CC</sub> = MAX, V<sub>I</sub> = V<sub>CC</sub> MAX 1.0 mA 1<sub>IL</sub> T/R Logical "0" Input Current -0.1  $V_I = 0.4V$ -0.25CD -0.1 -0.25 Vc Input Clamp Voltage  $I_{JN} = -12mA$ -0.8-1.5Volts **POWER SUPPLY CURRENT**  $CD = V_1 = 2.0V, V_{CC} = MAX$ Am73/8303 70 100 mΑ CD = 0.4V,  $V_{INA} = T/\overline{R} = 2.0V$ ,  $V_{CC} = MAX$ lcc Power Supply Current 100 150  $CD = 2.0V, V_I = 0.4V, V_{CC} = MAX$ Am73/8304B 70 100 mΑ  $CD = V_{INA} = 0.4V$ ,  $T/\overline{R} = 2.0V$ ,  $V_{CC} = MAX$ 90 140

Tvp

|                    |                                                                              |                                                                                                                                                            | Тур      |     |       |

|--------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|-------|

| arameters          | Description                                                                  | Test Conditions                                                                                                                                            | (Note 1) | Max | Units |

|                    | A PORT DATA/M                                                                | ODE SPECIFICATIONS                                                                                                                                         |          |     |       |

| <sup>t</sup> PDHLA | Propagation Delay to a Logical "0" from B Port to A Port                     | CD = 0.4V, $T/\overline{R}$ = 0.4V (Figure 1)<br>R <sub>1</sub> = 1k, R <sub>2</sub> = 5k, C <sub>1</sub> = 30pF                                           | 8        | 12  | ns    |

| <sup>†</sup> PDLHA | Propagation Delay to a Logical "1" from B Port to A Port                     | CD = 0.4V, $T/\overline{R}$ = 0.4V (Figure 1)<br>R <sub>1</sub> = 1k, R <sub>2</sub> = 5k, C <sub>1</sub> = 30pF                                           | 11       | 16  | ns    |

| <sup>t</sup> PLZA  | Propagation Delay from a Logical "0" to 3-State from CD to A Port            | $B_0$ to $B_7 = 2.4V$ , $T/\overline{R} = 0.4V$ (Figure 3) $S_3 = 1$ , $R_5 = 1k$ , $C_4 = 15pF$                                                           | 10       | 15  | ns    |

| <sup>t</sup> PHZA  | Propagation Delay from a Logical "1" to 3-State from CD to A Port            | $B_0$ to $B_7 = 0.4V$ , $T/\overline{R} = 0.4V$ (Figure 3) $S_3 = 0$ , $R_5 = 1k$ , $C_4 = 15pF$                                                           | 8        | 15  | ns    |

| <sup>†</sup> PZLA  | Propagation Delay from 3-State to a Logical "0" from CD to A Port            | $B_0$ to $B_7 = 2.4V$ , $T/\overline{R} = 0.4V$ (Figure 3) $S_3 = 1$ , $R_5 = 1$ k, $C_4 = 30$ pF                                                          | 20       | 30  | ns    |

| <sup>†</sup> PZHA  | Propagation Delay from 3-State to a Logical "1" from CD to A Port            | $B_0$ to $B_7 = 0.4V$ , $T/\overline{R} = 0.4V$ (Figure 3)<br>$S_3 = 0$ , $R_5 = 5k$ , $C_4 = 30pF$                                                        | 19       | 30  | ns    |

|                    | B PORT DATA/N                                                                | IODE SPECIFICATIONS                                                                                                                                        |          |     |       |

| t <sub>PDHLB</sub> | Propagation Delay to a Logical "0" from                                      | CD = 0.4V, $T/\overline{R}$ = 2.4V (Figure 1) $R_1 = 100\Omega, R_2 = 1k, C_1 = 300pF$                                                                     | 12       | 18  | ns    |

|                    | A Port to B Port                                                             | $R_1 = 667\Omega$ , $R_2 = 5k$ , $C_1 = 45pF$                                                                                                              | 7        | 12  | ns    |

| <sup>t</sup> PDLHB | Propagation Delay to a Logical "1" from<br>A Port to B Port                  | CD = 0.4V, $T/\overline{R}$ = 2.4V (Figure 1) $R_1 = 100\Omega, R_2 = 1k, C_1 = 300pF$                                                                     | 15       | 20  | ns    |

| ,                  |                                                                              | $R_1 = 667\Omega$ , $R_2 = 5k$ , $C_1 = 45pF$                                                                                                              | 9        | 14  | ns    |

| <sup>t</sup> PLZB  | Propagation Delay from a Logical "0" to 3-State from CD to B Port            | $A_0$ to $A_7 = 2.4V$ , $T/\overline{R} = 2.4V$ (Figure 3)<br>$S_3 = 1$ , $R_5 = 1k$ , $C_4 = 15pF$                                                        | 13       | 18  | ns    |

| <sup>†</sup> PHZB  | Propagation Delay from a Logical "1" to 3-State from CD to B Port            | $A_0$ to $A_7 = 0.4$ V, $T/\overline{R} = 2.4$ V (Figure 3)<br>$S_3 = 0$ , $R_5 = 1$ k, $C_4 = 15$ pF                                                      | 8        | 15  | ns    |

| t <sub>PZLB</sub>  | Propagation Delay from 3-State to a Logical "0" from CD to B Port            | A <sub>0</sub> to A <sub>7</sub> = 2.4V, $T/\overline{R}$ = 2.4V (Figure 3)<br>S <sub>3</sub> = 1, R <sub>5</sub> = 100 $\Omega$ , C <sub>4</sub> = 300pF  | 25       | 35  | ns    |

|                    |                                                                              | $S_3 = 1$ , $R_5 = 667\Omega$ , $C_4 = 45pF$                                                                                                               | 16       | 25  | ns    |

| tрzнв              | Propagation Delay from 3-State to a Logical "1" from                         | A <sub>0</sub> to A <sub>7</sub> = 0.4V, $T/\overline{R}$ = 2.4V (Figure 3)<br>S <sub>3</sub> = 0, R <sub>5</sub> = 1k, C <sub>4</sub> = 300pF             | 22       | 35  | ns    |

|                    | CD to B Port                                                                 | $S_3 = 0$ , $R_5 = 5k$ , $C_4 = 45pF$                                                                                                                      | 14       | 25  | ns    |

|                    | TRANSMIT RECEIV                                                              | E MODE SPECIFICATIONS                                                                                                                                      |          |     |       |

| <sup>t</sup> TRL   | Propagation Delay from Transmit Mode to Receive a Logical "0", T/R to A Port | CD = 0.4V (Figure 2)<br>$S_1 = 1$ , $R_4 = 100\Omega$ , $C_3 = 5pF$<br>$S_2 = 1$ , $R_3 = 1k$ , $C_2 = 30pF$                                               | 23       | 35  | ns    |

| <sup>t</sup> TRH   | Propagation Delay from Transmit Mode to Receive a Logical "1", T/R to A Port | CD = 0.4V (Figure 2)<br>$S_1 = 0$ , $R_4 = 100\Omega$ , $C_3 = 5pF$<br>$S_2 = 0$ , $R_3 = 5k$ , $C_2 = 30pF$                                               | 22       | 35  | ns    |

| t <sub>RTL</sub>   | Propagation Delay from Receive Mode to Transmit a Logical "0", T/R to B Port | CD = 0.4V (Figure 2)<br>$S_1 = 1$ , $R_4 = 100\Omega$ , $C_3 = 300pF$<br>$S_2 = 1$ , $R_3 = 300\Omega$ , $C_2 = 5pF$                                       | 26       | 35  | ns    |

| <sup>t</sup> RTH   | Propagation Delay from Receive Mode to Transmit a Logical "1", T/R to B Port | CD = 0.4V (Figure 2)<br>S <sub>1</sub> = 0, R <sub>4</sub> = 1k, C <sub>3</sub> = 300pF<br>S <sub>2</sub> = 0, R <sub>3</sub> = 300Ω, C <sub>2</sub> = 5pF | 27       | 35  | ns    |

Notes: 1. All typical values given are for  $V_{\rm CC}=5.0{\rm V}$  and  ${\rm T_A}=25{\rm ^{o}C}$ . 2. Only one output at a time should be shorted.

# **FUNCTION TABLE**

| Inputs           | Conditions |     |      |

|------------------|------------|-----|------|

| Chip Disable     | 0          | 0   | 1    |

| Transmit/Receive | 0          | 1   | х    |

| A Port           | Out        | ln  | HI-Z |

| B Port           | In         | Out | HI-Z |

# AC ELECTRICAL CHARACTERISTICS (V<sub>CC</sub> = 5.0V, T<sub>A</sub> = 25°C)

| Parameters         | Description                                                                  | Test Conditions                                                                                                                                            | Typ<br>(Note 1) | Max | Unite    |

|--------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|----------|

|                    | A PORT DATA/                                                                 | MODE SPECIFICATIONS                                                                                                                                        |                 |     | _        |

| <sup>t</sup> PDHLA | Propagation Delay to a Logical "0" from<br>B Port to A Port                  | CD = 0.4V, $T/\overline{R}$ = 0.4V (Figure 1)<br>R <sub>1</sub> = 1k, R <sub>2</sub> = 5k, C <sub>1</sub> = 30pF                                           | 14              | 18  | ns       |

| <sup>t</sup> PDLHA | Propagation Delay to a Logical "1" from B Port to A Port                     | CD = 0.4V, $T/\overline{R}$ = 0.4V (Figure 1)<br>R <sub>1</sub> = 1k, R <sub>2</sub> = 5k, C <sub>1</sub> = 30pF                                           | 13              | 18  | ns       |

| <sup>t</sup> PLZA  | Propagation Delay from a Logical "0" to 3-State from CD to A Port            | $B_0$ to $B_7 = 0.4V$ , $T/\overline{R} = 0.4V$ (Figure 3)<br>$S_3 = 1$ , $R_5 = 1k$ , $C_4 = 15pF$                                                        | 11              | 15  | ns       |

| t <sub>PHZA</sub>  | Propagation Delay from a Logical "1" to 3-State from CD to A Port            | $B_0$ to $B_7 = 2.4V$ , $T/\overline{R} = 0.4V$ (Figure 3)<br>$S_3 = 0$ , $R_5 = 1k$ , $C_4 = 15pF$                                                        | 8               | 15  | ns       |

| t <sub>PZLA</sub>  | Propagation Delay from 3-State to a Logical "0" from CD to A Port            | $B_0$ to $B_7 = 0.4V$ , $T/\overline{R} = 0.4V$ (Figure 3)<br>$S_3 = 1$ , $R_5 = 1k$ , $C_4 = 30pF$                                                        | 27              | 35  | ns       |

| <sup>t</sup> PZHA  | Propagation Delay from 3-State to a Logical "1" from CD to A Port            | $B_0$ to $B_7 = 2.4$ V, $T/\overline{R} = 0.4$ V (Figure 3)<br>$S_3 = 0$ , $R_5 = 5$ k, $C_4 = 30$ pF                                                      | 19              | 25  | ns       |

|                    | B PORT DATA/                                                                 | MODE SPECIFICATIONS                                                                                                                                        |                 |     | <u> </u> |

| t <sub>PDHLB</sub> | Propagation Delay to a Logical "0" from<br>A Port to B Port                  | CD = 0.4V, $T/\overline{R}$ = 2.4V (Figure 1) $R_1 = 100\Omega, R_2 = 1k, C_1 = 300pF$                                                                     | 18              | 23  | ns       |

|                    |                                                                              | $R_1 = 667\Omega$ , $R_2 = 5k$ , $C_1 = 45pF$                                                                                                              | 11              | 18  | ns       |

| <sup>†</sup> PDLHB | Propagation Delay to a Logical "1" from A Port to B Port                     | CD = 0.4V, $T/\overline{R}$ = 2.4V (Figure 1) $R_1 = 100\Omega, R_2 = 1k, C_1 = 300pF$                                                                     | 16              | 23  | ns       |

|                    |                                                                              | $R_1 = 667\Omega$ , $R_2 = 5k$ , $C_1 = 45pF$                                                                                                              | 11              | 18  | ns       |

| t <sub>PLZB</sub>  | Propagation Delay from a Logical "0" to 3-State from CD to B Port            | A <sub>0</sub> to A <sub>7</sub> = 0.4V, $T/\overline{R}$ = 2.4V (Figure 3)<br>S <sub>3</sub> = 1, R <sub>5</sub> = 1k, C <sub>4</sub> = 15pF              | 13              | 18  | ns       |

| <sup>†</sup> PHZB  | Propagation Delay from a Logical "1" to 3-State from CD to B Port            | $A_0$ to $A_7 = 2.4V$ , $T/\overline{R} = 2.4V$ (Figure 3)<br>$S_3 = 0$ , $R_5 = 1k$ , $C_4 = 15pF$                                                        | 8               | 15  | ns       |

| <sup>t</sup> PZLB  | Propagation Delay from 3-State to a Logical "0" from CD to B Port            | A <sub>0</sub> to A <sub>7</sub> = 0.4V, $T/\overline{R}$ = 2.4V (Figure 3)<br>S <sub>3</sub> = 1, R <sub>5</sub> = 100 $\Omega$ , C <sub>4</sub> = 300pF  | 32              | 40  | ns       |

|                    |                                                                              | $S_3 = 1$ , $R_5 = 667\Omega$ , $C_4 = 45pF$                                                                                                               | 16              | 22  | ns       |

| <sup>t</sup> PZHB  | Propagation Delay from 3-State to a Logical "1" from CD to B Port            | A <sub>0</sub> to A <sub>7</sub> = 2.4V, $T/\overline{R}$ = 2.4V (Figure 3)<br>S <sub>3</sub> = 0, R <sub>5</sub> = 1k, C <sub>4</sub> = 300pF             | 26              | 35  | ns       |

|                    |                                                                              | $S_3 = 0$ , $R_5 = 5k$ , $C_4 = 45pF$                                                                                                                      | 14              | 22  | ns       |

|                    | TRANSMIT RECEIV                                                              | E MODE SPECIFICATIONS                                                                                                                                      |                 |     |          |

| t <sub>TRL</sub>   | Propagation Delay from Transmit Mode to Receive a Logical "0", T/R to A Port | CD = 0.4V (Figure 2)<br>$S_1 = 0$ , $R_4 = 100\Omega$ , $C_3 = 5pF$<br>$S_2 = 1$ , $R_3 = 1k$ , $C_2 = 30pF$                                               | 30              | 40  | ns       |

| <sup>t</sup> TRH   | Propagation Delay from Transmit Mode to Receive a Logical "1", T/R to A Port | CD = 0.4V (Figure 2)<br>$S_1 = 1$ , $R_4 = 100\Omega$ , $C_3 = 5pF$<br>$S_2 = 0$ , $R_3 = 5k$ , $C_2 = 30pF$                                               | 28              | 40  | ns       |

| <sup>t</sup> RTL   | Propagation Delay from Receive Mode to Transmit a Logical "0", T/R to B Port | CD = 0.4V (Figure 2)<br>$S_1 = 1$ , $R_4 = 100\Omega$ , $C_3 = 300pF$<br>$S_2 = 0$ , $R_3 = 300\Omega$ , $C_2 = 5pF$                                       | 31              | 40  | ns       |

| <b>Р</b> ЕТТН      | Propagation Delay from Receive Mode to Transmit a Logical "1", T/R to B Port | CD = 0.4V (Figure 2)<br>S <sub>1</sub> = 0, R <sub>4</sub> = 1k, C <sub>3</sub> = 300pF<br>S <sub>2</sub> = 1, R <sub>3</sub> = 300Ω, C <sub>2</sub> = 5pF | 28              | 40  | ns       |

Notes: 1. All typical values given are for  $V_{CC} = 5.0 V$  and  $T_A = 25 ^{\circ} C$ .

2. Only one output at a time should be shorted.

# **DEFINITION OF FUNCTIONAL TERMS**

Ag-Ag A port inputs/outputs are receiver output drivers when T/R is LOW and are transmit inputs when T/R is HIGH.

**B<sub>0</sub>-B<sub>7</sub>** B port inputs/outputs are transmit output drivers when  $T/\overline{R}$  is HIGH and receiver inputs when  $T/\overline{R}$  is LOW.

Chip Disable forces all output drivers into 3-state when HIGH (same function as active LOW chip select,  $\overline{CS}$ ).

Transmit/Receive direction control determines whether A port or B port drivers are in 3-state. With  $T/\overline{R}$  HIGH A port is the input and B port is the output. With  $T/\overline{R}$  LOW A port is the output and B port is the input.

CD

T/R

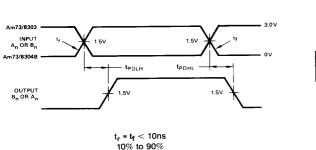

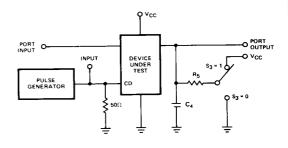

# SWITCHING TIME WAVEFORMS AND AC TEST CIRCUITS

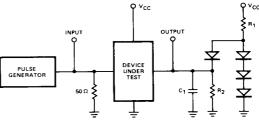

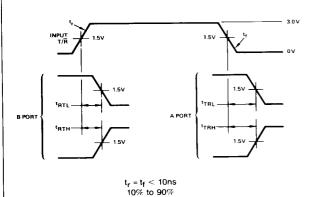

Note: C<sub>1</sub> includes test fixture capacitance.

Figure 1. Propagation Delay from A Port to B Port or from B Port to A Port.

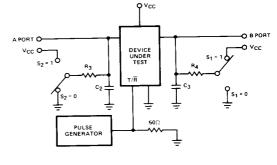

Note: C2 and C3 include test fixture capacitance.

Figure 2. Propagation Delay from  $T/\overline{R}$  to A Port or B Port.

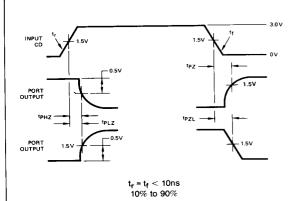

Note: C<sub>4</sub> includes test fixture capacitance. Port input is in a fixed logical condition.

Figure 3. Propagation Delay from CD to A Port or B Port.

### Metallization and Pad Layouts

#### Am73/8303

Am73/8304B

DIE SIZE .069" X .089"

DIE SIZE .069" X .089"

### **ORDERING INFORMATION**

Order the part number according to the table below to obtain the desired package, temperature range, and screening level.

| Am73/8303<br>Order Number | Am73/8304B<br>Order Number | Package Type<br>(Note 1) | Operating (Note 2) | Screening Level (Note 3)                       |

|---------------------------|----------------------------|--------------------------|--------------------|------------------------------------------------|

| DP7303J                   | DP7304BJ                   | D-20                     | M                  | C-3                                            |

| DP7303JB                  | DP7304BJB                  | D-20                     | М                  | B-3                                            |

| DP8303J                   | DP8304BJ                   | D-20                     | С                  | C-1                                            |

| DP8303JB                  | DP8304BJB                  | D-20                     | C                  | B-1                                            |

| DP8303N                   | DP8304BN                   | P-20                     | С                  | C-1                                            |

| DP8303NB                  | DP8304BNB                  | P-20                     | C                  | B-1                                            |

| AM7303X<br>AM8303X        | AM7304BX<br>AM8304BX       | Dice<br>Dice             | M<br>C             | Visual inspection to MIL-STD-883 Method 2010B. |

#### Notes:

- 1. P = Molded DIP, D = Hermetic DIP, F = Flat Pak. Number following letter is number of leads.

2. C = 0 to 70°C, V<sub>CC</sub> = 4.75 to 5.25V, M = -55 to +125°C, V<sub>CC</sub> = 4.50 to 5.50V.

3. Levels C-1 and C-3 conform to MIL-STD-883, Class C. Level B-3 conforms to MIL-STD-883, Class B.