# DP8341/NS32441 IBM 3270 Protocol Receiver/Decoder

## **General Description**

The DP8341/NS32441 provides complete decoding of data for high speed serial data communications. In specific, the DP8341/NS32441 recognizes serial data that conforms to the IBM 3270 Information Display System Standard and converts it into ten (10) bits of parallel data. Although this standard covers biphase serial data transmission over a coax line, this device easily adapts to generalized high speed serial data transmission on other than coax lines at frequencies either higher or lower than the IBM 3270 standard.

The DP8341/NS32441 receiver and its complementary chip, the DP8340 transmitter, are designed to provide maximum flexibility in system designs. The separation of transmitter and receiver functions allows addition of more receivers at one end of the biphase line without the necessity of adding unused transmitters. This is advantageous specifically in control units where typically biphase data is multiplexed over many biphase lines and the number of receivers generally outnumber the number of transmitters. The separation of transmitter and receiver function provides an additional advantage in flexibility of data bus organization. The data bus outputs of the receiver are TRI-STATE®, thus enabling the bus configuration to be organized as either a common transmit/receive (bi-directional) bus or as separate transmit and receive busses for higher speed.

#### **Features**

- DP8341/NS32441 receivers ten (10) bit data bytes and conforms to the IBM 3270 Interface Display System Standard

- Separate receiver and transmitter provide maximum system design flexibility

- Even parity detection

- High sensitivity input on receiver easily interfaces to coax line

- Standard TTL data input on receiver provides generalized transmission line interface and also provides hysteresis

- Data holding register

- Multi-byte or single byte transfers

- TRI-STATE receiver data outputs provide flexibility for common or separated transmit/receive data bus operation

- Data transmission error detection or receiver provides for both error detection and error type definition

- Bi-polar technology provides TTL input/output compatibility with excellent drive characteristics

- Single +5V power supply operation

#### Connection Diagrams Plastic Chip Carrier **Dual-In-Line Package** RECEIVER DISABLE VCC +AMPLIFIER INPUT 23 D011 -AMPLIFIER INPUT 22 D016 DATA (TTL) 21 D09 DATA CONTROL 20 00a CLOCK 19 DO 2 DATA (TTL) - nn a RECEIVER ACTIVE 18 006 DATA CONTROL - DO 8 ERADR 17 005 CLOCK 23 - DO 7 REGISTER READ 16 004 22 DATA AVAILABLE -10 15 DOa RECEIVER ACTIVE -21 DO 6 OUTPUT CONTROL ERROR -20 - DO 5 11 DQ2 REGISTER READ DO 4 13 **OUTPUT ENABLE** TL/F/5238-2 ATA AVAILABLE — ENABLE ŝ 몽 **JUTPUT CONTROL Top View** Order Number DP8341J or DP8341N See NS Package Number J24A or N24A TL/F/5238-1 Order Number DP8341V or NS32441V See NS Package Number V28A FIGURE 1

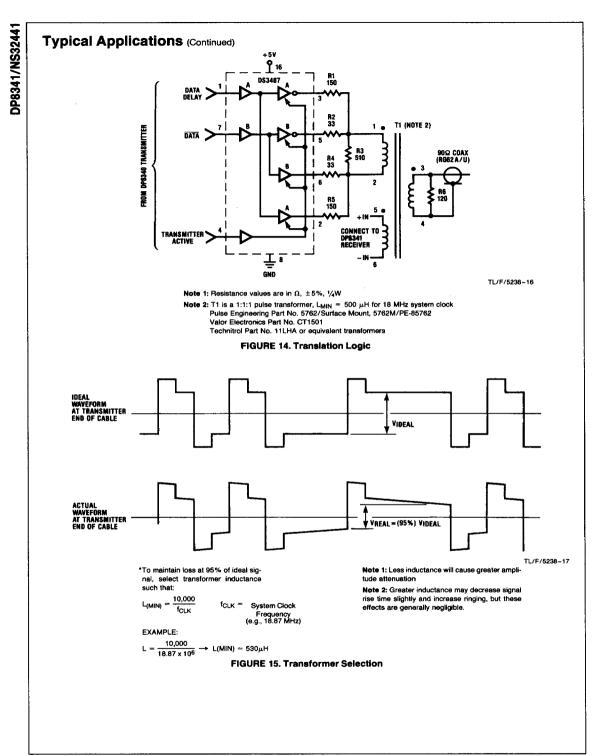

### **Block Diagram**

FIGURE 2. DP8341/NS32441 Serial Bi-Phase Receiver/Decoder Block Diagram

# Block Diagram Functional Description

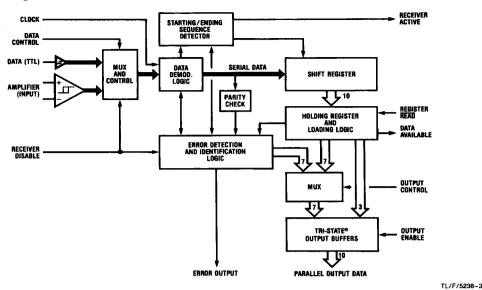

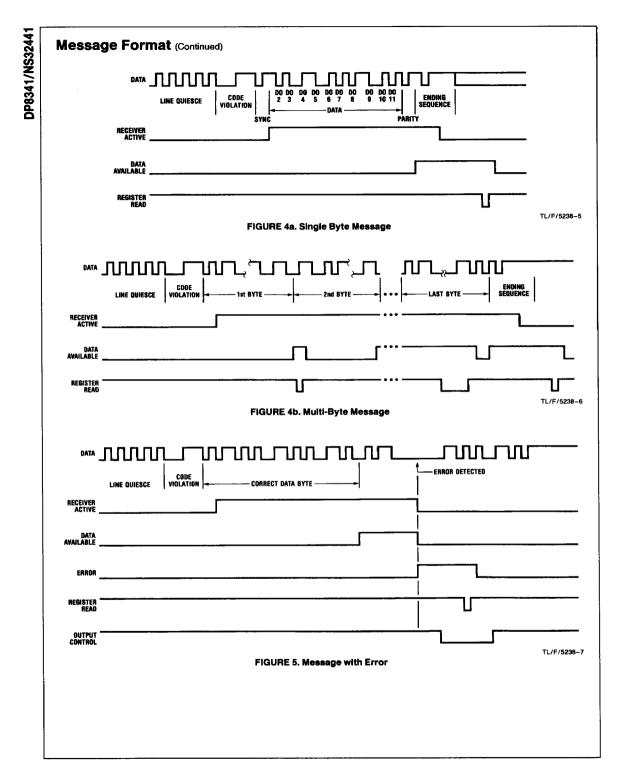

Figure 2 is a block diagram of the DP8341/NS32441. This chip is essentially a serial in/parallel out shift register. However, the serial input data must conform to a very specific format (see Figures 3-5). The message will not be recognized unless the format of the starting sequence is correct. Deviations from the format in the data, sync bit, parity or ending sequence will cause an error to be detected, terminating the message.

Data enters the receiver through the differential input amplifier or the TTL Data input. The differential amplifier is a high sensitivity input which may be used by connecting it directly to a transformer coupled coax line, or other transmission medium. The TTL Data input provides 400 mV of hysteresis and recognizes TTL logic levels. The data then enters the demodulation block.

The data demodulation block samples the data at eight (8) times the data rate and provides signals for detecting the starting sequence, ending sequence, and errors. Detection of the starting sequence sets the Receiver Active output high and enables the input shift register.

As the ten bits of data are shifted into the shift register, the receiver will verify that even parity is maintained on the data bits and the sync bit. After one complete data byte is received, the contents of the input shift register is parallel loaded to the holding register, assuming the holding register is empty, and the Data Available output is set. If the holding register is full, this load will be delayed until that register has been read. If another data byte is received when the shift

register and the holding register are full a Data Overflow Error will be detected, terminating the message. Data is read from the holding register through the TRI-STATE Output Buffers. The Output Enable input is the TRI-STATE control for these outputs and the Register Read input signals the receiver that the read has been completed.

When the receiver detects an ending sequence the Receiver Active output will be reset to a logic "0" indicating the message has been terminated. A message will also terminate when an error is detected. The Receiver Active output used in conjunction with the Error output allows quick response to the transmitting unit when an error free message has been received.

The Error Detection and Identification block insures that valid data reaches the outputs of the receiver. Detection of an error sets the Error output to a logic "1" and resets the Receiver Active output to a logic "0" terminating the message. The error type may be read from the data bus outputs by setting the Output Control input to logic "0" and enabling the TRI-STATE outputs. The data bit outputs have assigned error definitions (see error code definition table). The Error output will return to a logic "0" when the next starting sequence is received, or when the error is read (Output Control to logic "0" and a Register Read performed).

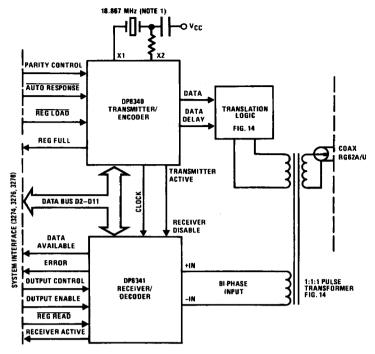

The Receiver Disable input is used to disable both the amplifier and TTL Data receiver inputs. It will typically be connected directly to the Transmitter Active output of the DP8340 transmitter circuit (see Figure 12).

# **Detailed Functional Pin Description**

#### RECEIVER DISABLE

This input is used to disable the receiver's data inputs. The Receiver Disable input will typically be connected to the Transmitter Active output of the DP8340. However, at the system controller it is necessary for both the transmitter and receiver to be active at the same time in the loop-back check condition. This variation can be accomplished with the addition of minimal external logic.

Truth Table

| Receiver Disable | Data Inputs |  |  |  |  |

|------------------|-------------|--|--|--|--|

| Logic "0"        | Active      |  |  |  |  |

| Logic "1"        | Disabled    |  |  |  |  |

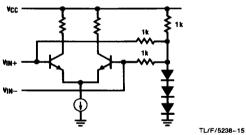

#### **AMPLIFIER INPUTS**

The receiver has a differential input amplifier which may be directly connected to the transformer coupled coax line. The amplifier may also be connected to a differential type TTL line. The amplifier has 20 mV of hysteresis.

#### **DATA INPUT**

This input can be used either as an alternate data input or as a power-up check input. If the system designer prefers to use his own amplifier, instead of the one provided on the receiver, then this TTL input may be used. Using this pin as an alternate data input allows self-test of the peripheral system without disturbing the transmission line.

#### DATA CONTROL

This input is the control pin that selects which of the inputs are used for data entry to the receiver.

**Truth Table**

| Data Control | Data input To    |

|--------------|------------------|

| Logic "0"    | Data Input       |

| Logic "1"    | Amplifier Inputs |

**Note:** This input is also used for testing. When the input voltage is raised to 7.5V the chip resets.

#### **CLOCK INPUT**

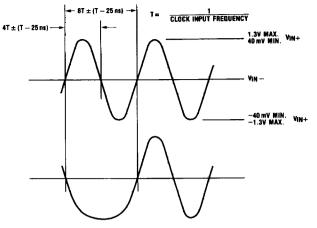

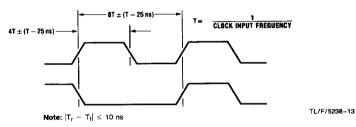

The input is the internal clock of the receiver. It must be set at eight (8) times the line data bit rate. For the IBM 3270 Standard, this frequency is 18.87 MHz or a data bit rate of 2.358 MHz. The crystal-controlled oscillator provided in the

DP8340 transmitter also operates at this frequency. The Clock Output of the transmitter is designed to directly drive the receiver's Clock Input. In addition, the receiver is designed to operate correctly to a data bit rate of 3.5 MHz.

#### RECEIVER ACTIVE

The purpose of this output is to inform the external system when the DP8341/NS32441 is in the process of receiving a message. This output will transition to a logic "1" state after the receipt of a valid starting sequence and transition to logic "0" when a valid ending sequence is received or an error is detected. This output combined with the Error output will inform the operating system of the end of an error free data transmission.

#### ERROR

The Error output transitions to a logic "1" when an error is detected. Detection of an error causes the Receiver Active and the Data Available outputs to transition to a logic "0". The Error output returns to a logic "0" after the error register has been read or when the next starting sequence is detected.

#### REGISTER READ

The Register Read input when driven to the logic "0" state signals the receiver that data in the holding register is being read by the external operating system. The data present in the holding register will continue to remain valid until the Register Read input returns to the logic "1" condition. At this time, if an additional byte is present in the input shift register it will be transferred to the holding register, otherwise the data will remain valid in the holding register. The Data Available output will be in the logic "0" state for a short interval while a new byte is transferred to the holding register after a register read.

#### **DATA AVAILABLE**

This output indicates the existence of a data byte within the output holding register. It may also indicate the presence of a data byte in both the holding register and the input shift register. This output will transition to the logic "1" state as soon as data is available and return to the logic "0" state after each data byte has been read. However, even after the last data byte has been read and the Data Available output has assumed the logic "0" state, the last data byte read from the holding register will remain until new data has been received.

## **Detailed Functional Pin Description (Continued)**

#### **OUTPUT CONTROL**

The Output Control input determines the type of information appearing at the data outputs. In the logic "1" state data will appear, in the logic "0" state error codes are present.

**Truth Table**

| 112111         |              |  |  |  |

|----------------|--------------|--|--|--|

| Output Control | Data Outputs |  |  |  |

| Logic "0"      | Error Codes  |  |  |  |

| Logic "1"      | Data         |  |  |  |

#### **OUTPUT ENABLE**

The Output Enable input controls the state of the TRI-STATE Data outputs.

#### **Truth Table**

| Output Enable | TRI-STATE<br>Data Outputs |

|---------------|---------------------------|

| Logic "0"     | Disabled                  |

| Logic "1"     | Active                    |

#### **DATA OUTPUTS**

The DP8341 has a ten (10) bit TRI-STATE data bus. Seven bits are multiplexed with error bits. The error bits are de-

fined in the table below. The Output Control input is the multiplexer control for the Data/Error bits.

#### **Error Code Definition**

| Data Bit | Error Type                                                                                                                         |

|----------|------------------------------------------------------------------------------------------------------------------------------------|

| DO2      | Data Overflow (Byte not removed from holding register when it and the input shift register are both full and new data is received) |

| DO3      | Parity Error (Odd parity detected)                                                                                                 |

| DO4      | Transmit Check conditions<br>(existence of errors on any or all<br>of the following data bits: DO3,<br>DO5, and DO6                |

| DO5      | An invalid ending sequence                                                                                                         |

| DO6      | Loss of mid-bit transition<br>detected at other than normal<br>ending sequence time                                                |

| DO7      | New starting sequence detected<br>before data byte in holding<br>register has been read                                            |

| DOB      | Receiver disabled during receiver active mode                                                                                      |

## **Message Format**

#### Single Byte Transmission

#### Multi-Byte Transmission

FIGURE 3. IBM 3270 Message Format

TL/F/5238-4

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage,  $V_{CC}$  7V Input Voltage + 5.5V

Output Voltage 5.25V Storage Temperature Range -65°C to +150°C

Lead Temperature (Soldering, 10 seconds) 300°C

Maximum Power Dissipation\* at 25°C

Cavity Package 2040 mW

Dual-In-Line Package 2237 mW

Plastic Chip Carrier 1690 mW

\*Derate cavity package 13.6 mW/\*C above 25°C; derate PCC package 13.5 mW/\*C above 25°C; derate Dual-In-Line package 17.9 mW/\*C above 25°C.

# **Operating Conditions**

| -                                  | Min  | Max  | Units |

|------------------------------------|------|------|-------|

| Supply Voltage, (V <sub>CC</sub> ) | 4.75 | 5.25 | ٧     |

| Ambient Temperature, (TA)          | 0    | + 70 | °C    |

## Electrical Characteristics (Notes 2, 3, and 5)

| Symbol                                   | Parameter                          | Conditions                                              | Min | Тур  | Max  | Units |

|------------------------------------------|------------------------------------|---------------------------------------------------------|-----|------|------|-------|

| V <sub>IH</sub>                          | Input High Level                   |                                                         | 2.0 |      |      | ٧     |

| V <sub>IL</sub>                          | Input Low Level                    |                                                         |     |      | 0.8  | ٧     |

| V <sub>IH</sub> -V <sub>IL</sub>         | Data Input Hysteresis (TTL, Pin 4) |                                                         | 2.0 | 0.4  |      | ٧     |

| VCLAMP                                   | Input Clamp Voltage                | $I_{\text{IN}} = -12 \text{ mA}$                        |     | -0.8 | -1.2 | ٧     |

| I <sub>IH</sub>                          | Logic "1" Input Current            | $V_{CC} = 5.25V, V_{IN} = 5.25V$                        |     | 2    | 40   | μΑ    |

| I <sub>I</sub> L                         | Logic "0" Input Current            | $V_{CC} = 5.25V, V_{IN} = 0.5V$                         |     | -20  | -250 | μΑ    |

| V <sub>OH</sub> Logic "1" Output Voltage | I <sub>OH</sub> = -100 μA          | 3.2                                                     | 3.9 |      | ٧    |       |

|                                          |                                    | $I_{OH} = -1 \text{ mA}$                                | 2.5 | 3.2  |      | ٧     |

| V <sub>OL</sub>                          | Logic "0" Output Voltage           | I <sub>OL</sub> = 5 mA                                  |     | 0.35 | 0.5  | ٧     |

| los                                      | Output Short Circuit Current       | V <sub>CC</sub> = 5V, V <sub>OUT</sub> = 0V<br>(Note 4) | -10 | -20  | -100 | mA    |

| loz                                      | TRI-STATE Output Current           | $V_{CC} = 5.25V, V_{O} = 2.5V$                          | -40 | 1    | + 40 | μА    |

|                                          |                                    | $V_{CC} = 5.25V, V_{O} = 0.5V$                          | -40 | -5   | + 40 | μΑ    |

| A <sub>HYS</sub>                         | Amplifier Input Hysteresis         |                                                         | 5   | 20   | 30   | mV    |

| lcc                                      | Power Supply Current               | V <sub>CC</sub> = 5.25V                                 |     | 160  | 250  | mA    |

# Timing Characteristics (Notes 2, 6, 7, and 8)

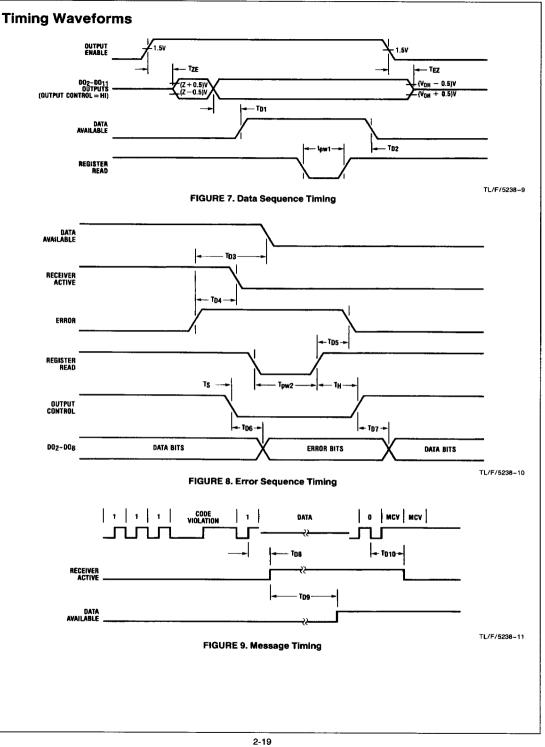

| Symbol          | Parameter                                                      | Conditions | Min | Тур            | Max | Units |

|-----------------|----------------------------------------------------------------|------------|-----|----------------|-----|-------|

| T <sub>D1</sub> | Output Data to Data Available<br>Positive Edge                 |            | 5   | 20             | 40  | ns    |

| T <sub>D2</sub> | Register Read Positive Edge to Data<br>Available Negative Edge |            | 10  | 25             | 45  | ns    |

| T <sub>D3</sub> | Error Positive Edge to Data Available<br>Negative Edge         |            | 10  | 30             | 50  | ns    |

| T <sub>D4</sub> | Error Positive Edge to Receiver Active<br>Negative Edge        |            | 5   | 20             | 40  | ns    |

| T <sub>D5</sub> | Register Read Positive Edge to Error<br>Negative Edge          |            | 20  | 45             | 75  | ns    |

| T <sub>D6</sub> | Delay from Output Control to Error Bits from Data Bits         |            | 5   | 20             | 50  | ns    |

| T <sub>D7</sub> | Delay from Output Control to Data Bits from Error Bits         |            | 5   | 20             | 50  | ns    |

| T <sub>D8</sub> | First Sync Bit Positive Edge to Receiver Active Positive Edge  |            |     | 3.5 × T<br>+70 |     | ns    |

| Symbol           | Parameter                                                                           | Conditions     | Min | Тур              | Max | Units  |

|------------------|-------------------------------------------------------------------------------------|----------------|-----|------------------|-----|--------|

| T <sub>D9</sub>  | Receiver Active Positive Edge to First Data<br>Available Positive Edge              |                |     | 92 × T           |     | ns     |

| T <sub>D10</sub> | Negative Edge of Ending Sequence to<br>Receiver Active Negative Edge                |                |     | 11.5 × T<br>+ 50 |     | ns     |

| <sup>‡</sup> D11 | Data Control Set-Up Multiplexer Time Prior to Receiving Data through Selected Input |                | 40  | 30               |     | ns     |

| T <sub>PW1</sub> | Register Read (Data) Pulse Width                                                    |                | 40  | 30               |     | ns     |

| T <sub>PW2</sub> | Register Read (Error) Pulse Width                                                   |                | 40  | 30               |     | ns     |

| T <sub>PW3</sub> | Data Available Logic "0" State between<br>Data Bytes                                |                | 25  | 45               |     | ns     |

| T <sub>S</sub>   | Output Control Set-Up Time Prior to<br>Register Read Negative Edge                  |                | 0   | -5               |     | ns     |

| T <sub>H</sub>   | Output Control Hold Time After the<br>Register Read Positive Edge                   |                | 0   | -5               |     | ns     |

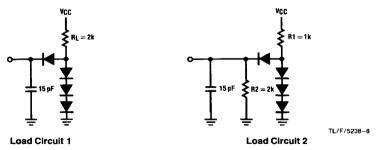

| T <sub>ZE</sub>  | Delay from Output Enable to Logic "1" or<br>Logic "0" from High Impedance State     | Load Circuit 2 |     | 25               | 35  | ns     |

| T <sub>EZ</sub>  | Delay from Output Enable to High Imped-<br>ance State from Logic "1" or Logic "0"   | Load Circuit 2 |     | 25               | 35  | ns     |

| F <sub>MAX</sub> | Data Bit Frequency (Clock Input must be 8 × the Data Bit Frequency)                 | (Note 9)       | DC  |                  | 3.5 | MBits/ |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 2: Unless otherwise specified, min./max. limits apply across the 0°C to +70°C temperature range and the 4.75V to 5.25V power supply range. All typical values are for  $T_A = 25$ °C and  $V_{CC} = 5.0$ V.

Note 3: All currents into device pins are shown as positive; all currents out of device pins are shown as negative; all voltages are referenced to ground, unless otherwise specified. All values shown as max. or min. are so classified on absolute value basis.

Note 4: Only one output at a time should be shorted.

Note 5: Input characteristics do not apply to amplifier inputs (pins 2 and 3).

Note 6: Unless otherwise specified, all AC measurements are referenced to the 1.5V level of the input to the 1.5V level of the output and load circuit 1 is used.

Note 7: AC tests are done with input pulses supplied by generators having the following characteristics:  $Z_{OUT}=50\Omega$  and  $T_r\leq 5$  ns,  $T_f\leq 5$  ns.

Note 8: T = 1/(clock input frequency), units for "T" should be ns.

Note 9: 28 MHz clock frequency corresponds to 3.75% jitter when referenced to Figure 10.

FIGURE 6. Test Load Circuits

# Timing Waveforms (Continued)

FIGURE 10. Data Waveform Constraints: Amplifier inputs

TL/F/5238-12

FIGURE 11. Data Waveform Constraints: Data Input (TTL)

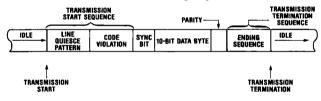

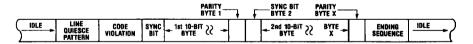

# **Typical Applications**

TL/F/5238-14

Note 3: Crystal manufacturers: Midland Ross Corp.

NEL Unit Part No. NE18A (C2560N) @ 18.867 MHz

The Viking Group Part No. VXB-46NS @ 18,867 MHz. Located in San Jose, CA.

FIGURE 12. Typical Application for IBM 3270 Interface

FIGURE 13. Equivalent Circuit for DP8341/NS32441 Input Amplifier