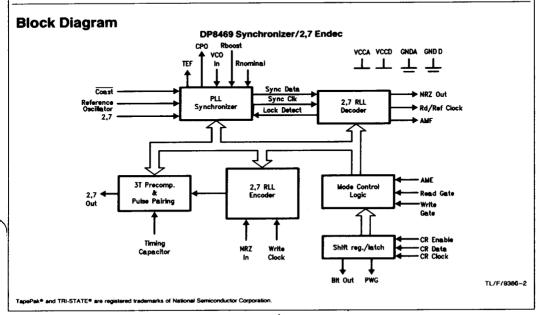

## DP8469 Synchronizer/2,7 Endec

## **General Description**

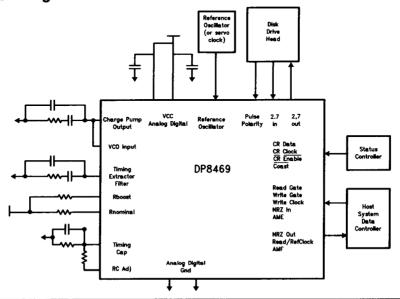

The DP8469 data synchronizer/2,7 endec is intended for use in magnetic disk, optical disk, or tape drives during reading and writing operations. The device utilizes a fully integrated PLL to synchronize 2,7 serial code and convert data between one of several hard and soft sectored versions of 2,7 RLL (Run Length Limited) and serial NRZ code format. The DP8469 synchronizer/endec incorporates both the DP8459 synchronizer and the DP8463 2,7 code endec functions together in a 28-pin PCC package.

In the read mode, the device receives 2,7 RLL coded data from the drive's pulse detector, resynchronizes it, and then decodes the data to NRZ format for output to the controller.

In the write mode, the device receives NRZ data from the disk controller, encodes it in one of nine different 2,7 RLL hard/soft sectored formats, and then sends the data out to the drive with optional 3T precompensation adjustments.

The device generates and recognizes the following 2,7 address mark formats; ESDI, ESDI noise tolerant, SMD, SMD noise tolerant, ST506(A), hard sector and three variations of ESDI, IBM, & ST506(B) optimized for the DP8466 controller. The address mark format is selected by 4 bits in a control register. A user defined variable-length preamble pattern can be used with any of the address mark modes. The pattern type, 3T or 4T, is set with one control register bit, and the preamble length is defined by the input NRZ data.

The synchronizer provides a dual gain phase locked loop which offers a high bandwidth mode for preamble lock

acquisition and a low bandwidth mode for reading data. Two ports are provided for the PLL filter to enable use of higher order filter designs. The synchronizer has a Zero-Phase-Start feature which helps to minimize acquisition time in both read and write modes. A PHASE COMPARATOR TEST function is also provided for observation of PLL loop dynamics and determination of average media bit shift. The 2,7 OUTPUT pin provides the logical OR of the phase comparator's pump up and down outputs when programmed for Test Mode 1 operation. (Continued)

#### **Features**

- NRZ to 2,7 RZ RLL encoding/decoding

- 3T and 4T preamble generation/detection

- 1.5 Mbit/s to 24 Mbit/s data rates

- User specified preamble length

- ESDI, SMD, and ST506 soft sectoring Hard sectoring

- Fully integrated dual-gain PLL

- Zero-Phase-Start lock sequence

- Digitally controlled window strobe

- Digital write precompensation

- TTL compatible inputs and outputs

- +5V supply

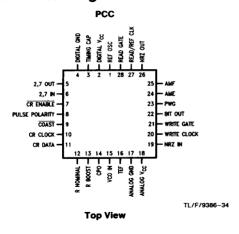

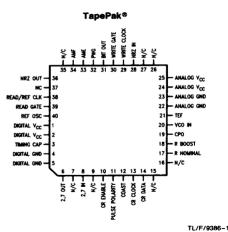

- Packaging availability:

- 28-pin Plastic Chip Carrier (PCC)

- 40-pin TapePak

© 1989 National Semiconductor Corporation

TL/F/9386

RRD-B20M79/Printed in U. S. A

## **Connection Diagrams**

**Top View**

## General Description (Continued)

A precise synchronization window is provided on chip using a self-aligned silicon delay line which remains accurate independent of temperature, power supply, external components and IC process variations. A strobe early/late function is provided which allows the synchronization window to be digitally adjusted to allow for error recovery or margin testing. The window can be shifted up to 20% in steps of 1.25% by 5 bits in a control register.

The synchronizer's data rate range is 1.5 Mbit/s to 24 Mbit/s. This range is divided into four operating regions each providing a 2 to 1 span in VCO frequency. Selection of one of the four data rate regions is controlled by two bits in a control register.

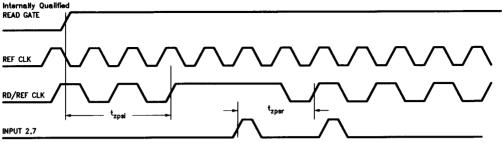

The READ/REFERENCE CLOCK provides both a read and write clock source for the controller. In read mode, once READ GATE has gone active and the Zero-Phase-Start sequence has been completed, the READ/REFERENCE CLOCK outputs the VCO divided by two. In the non-read mode, READ/REFERENCE CLOCK outputs REFERENCE OSCILLATOR divided by two. The circuitry incorporates a non-glitching multiplexer to ensure no erroneous clock pulses occur during the switch between input sources.

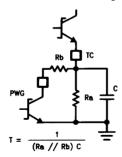

A digital precompensation feature is provided for write operations to compensate for bit shift due to data crowding on the media. The device will precompensate 3T code which is adjacent to greater than 3T code by selecting 1 of 6 bit shifted steps determined externally on the TC pin with an RC time constant set by the user.

The BIT-OUT output directly follows the logic level programmed in Control Register bit #10. By connecting BIT-OUT to the TC pin through a resistor, it is possible to have the controller select different pre-comp ranges via the control register.

## **Pin Descriptions**

**POWER SUPPLIES**

ANALOG V<sub>CC</sub>: Analog positive 5V supply, ±5%.

DIGITAL V<sub>CC</sub>: Digital positive 5V supply, ±5%.

ANALOG GND: Analog negative supply pin.

DIGITAL GND: Digital negative supply pin.

#### INPUTS FROM CONTROLLER

NRZ IN (NRZI): NRZI input from the controller. Data is encoded and written to the disk in 2,7 format on the positive edge of WRITE CLOCK. NRZI is held LOW during the Preamble and Address fields, and transitioned HI at the start of data encoding.

Non-ST506 modes: NRZI must remain LOW throughout the address mark field and transition HI for a minimum of two NRZ bits to terminate preamble and start the controller sync byte.

ST506 modes: NRZI must remain LOW through both the address mark and preamble fields, and then transition HI for a minimum of one NRZ bit to start the controller sync byte.

WRITE CLOCK: Clock input from the controller synchronized with the NRZ IN data.

WRITE GATE (WG): A mode control input from the controller which allows the writing of header and data to the disk when active HI and prohibits writing of header or data when LOW.

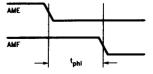

ADDRESS MARK ENABLE (AME): AME must be held HI while writing an Address Mark. During an ESDI or SMD read operation, the AME pin must be held HI to search for an address mark. Termination of the AME HI level will reset AMF to the LOW state. The AME logic is not relevant during non ESDI and SMD read operations.

## Pin Descriptions (Continued)

#### INPUTS FROM CONTROLLER (Continued)

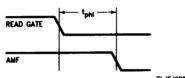

READ GATE (RG): A mode control input from the disk controller. In ESDI and IBM modes, RG should not be transitioned HI until AMF is active HI. In SMD and ST506 modes, RG is qualified to the synchronizer internally as follows:

ST506: device must recognize 4 consecutive 3T or 4T preamble patterns.

SMD: AMF goes active HI.

In Hard Sector mode, RG should not be transitioned HI until the Index Sector Gap is found. After RG goes HI, the synchronizer locks to the 2,7 INPUT data rate using a Zero Phase Start frequency lock routine. When RG goes LOW, the synchronizer locks to the Reference Oscillator (REG OSC) using a Zero Phase Start frequency lock routine. RG timing is allowed to be fully asynchronous.

#### **OUTPUTS TO CONTROLLER**

ADDRESS MARK FOUND (AMF): An active HI output for the controller to indicate the first 2,7 pulse beyond a valid address mark has been found. In the ESDI and SMD modes, AMF remains HI until AME transitions LOW. In the ST506A mode, AMF stays HI until RG is deasserted. In the DP8466 modes, ESDI, IBM and ST506B, AMF returns LOW after the second 2,7 pulse is encountered.

NRZ OUTPUT (NRZO): Decoded output data for the controller that is strobed on the positive transition of READ REF CLK. Control register bit 11 selects either TRI-STATE® or totem pole output. Bit 11 = LOW sets NRZO to active totem pole output, and Bit 11 = HI sets NRZO to TRI-STATE output.

READ REF CLK (R/RCLK): This supplies the controller clock source. In read mode, after the Zero Phase Start sequence is completed, R/RCLK issues the VCO divided by two signal. The NRZO is synchronized with this clock. In the non-read mode, R/RCLK will issue the REF CLK input signal divided by two.

#### INPUTS/OUTPUTS TO DRIVE

2,7 OUTPUT: Output 2,7 Return-to-Zero (RZ) data for recording onto the storage media. Each positive edge represents a single recorded code bit. The 2,7 OUTPUT active transition edge can be shifted by specific controllable time steps by setting control register bits 7,6,5. Only certain minimum 3T patterns are affected.

2,7 INPUT: Incoming data derived from the storage media, issued from a pulse detector circuit. Each positive edge represents a single recorded bit.

PULSE POLARITY (PP): Input derived from DP8464/8 pulse detector's channel polarity output telling the pulse pairing circuitry which pulse to shift.

#### **EXTERNAL SOURCES**

REFERENCE OSCILLATOR (REF OSC): A reference frequency input *required* for DP8469 operation. The signal must be crystal or servo derived (accurate and highly stable), and at a frequency approximately equal to the 2,7 code rate (i.e., twice the NRZ data rate).

CR ENABLE (CRE): When active LOW, CRE permits the loading of mode information via CRD and CRC. Data is latched into the part when CRE is transitioned HI. This input is also used to set test mode conditions as described in the Test Mode Operation section.

COAST (CST): The control input for a coast function which may be activated when RG is either HI or LOW. When the CST input is LOW, the phase comparator is disabled and held in a cleared state, allowing the VCO to coast regardless of the 2,7 code input or reference oscillator activity. No other circuit functions are disturbed. When the CST is inactive HI, the synchronizer operates normally.

CR CLOCK (CRC): Positive edge triggered clock for the 24bit control register. This input is also used to set test mode conditions as described in the Test Mode Operation section.

CR DATA (CRD): Data input for the 24 bit control register that selects the strobe window, precompensation and pulse pairing bit shift, data rate range, and address mark modes. This input is also used to set test mode conditions as described in the Test Mode Operation section.

#### **ANALOG SIGNAL PINS**

**RNOMINAL** (R<sub>NOM</sub>): A resistor is tied from this pin to V<sub>CC</sub> to set the *nominal* operating current. The current is internally multipled by 2 for charge pump use. This pin is also used to load the test modes as described in the Test Mode Operating section.

**RBOOST** (R<sub>BST</sub>): A resistor is tied from this pin to  $V_{CC}$  to set the chrage pump *boost* (or adder) current, which is multiplied by 2 internally for use by the charge pump. The R<sub>BST</sub> resistor is electrically paralleled with the R<sub>NOM</sub> resistor until either RG is passed to the synchronizer, or preamble lock is acquired. This selection is made with control bit 18;

Bit 18 = HI: forces synchronizer switch to Low Gain on assertion of RG.

Bit 18 = LOW: forces synchronizer switch to Low Gain when preamble lock is acquired.

**RBOOST (R<sub>BST</sub>)** (Continued): ST506 operating modes are special in that the switch to Low Gain is forced on the assertion of RG regardless of the state of bit 18. If no boost current is desired, a high value resistor must be tied to this pin to ensure its level is not allowed to drop below  $V_{\rm IH}=2V$  and activate the production test mode circuitry. This pin is also used for the test modes as described in the Test Mode Operating section.

CHARGE PUMP OUT (CPO): The output of the high-speed bi-directional current source switching circuitry of the charge pump. The external, passive PLL filter network is established between this pin, the VCO Input and ground.

VCO IN (VCOI): The high-impedance control voltage input to the voltage controlled oscillator (VCO). The external, passive PLL filter network is established between this pin, CPO pin and ground.

## Pin Descriptions (Continued)

#### ANALOG SIGNAL PINS (Continued)

TIMING EXTRACTOR FILTER (TEF): Connection pin for external, passive components employed to stabilize the delay line timing extraction circuitry.

Note: The delay line accuracy is not a function of external component values or tolerances

#### OTHER OUTPUTS

RC ADJ: An open collector Bipolar output which can be used to adjust the precompensation or pulse pairing external RC time constants. By connecting a resistor between the RC ADJ pin and the TC pin, a different RC timing constant can be used between precompensation and pulse pairing. RC ADJ is the logical true or complement of WG depending on the state of register bit 8:

Bit 8 = HI: RC ADJ is inverted from WG.

Bit 8 = LOW: RC ADJ follows WG.

BIT OUT: An undedicated open collector Bipolar output whose state is set using bit 10 in the control register. This output can be used for any purpose, including adding extra RC ranges to the precompensation and pulse pairing circuitry. Window strobe adjustments can be performed by connecting a resistor between BIT OUT and the CPO output pin.

## **Circuit Operation**

#### **CONTROL REGISTER OPERATION**

The DP8469 is initialized by loading the desired mode selections, such as address mark format and 3T/4T Preamble pattern, via the CR DATA (CRD), CR CLOCK (CRC) and CR ENABLE (CRE) inputs. Loading is accomplished by taking CRE active LOW, and clocking in the mode selection data on the positive going edge of CRC. The modes are latched in when CRE is transitioned HI. The selections are indicated in the 24-Bit Control Register section. The test modes are also loaded using CRD, CRE, CRC as explained in the special Test Mode Operation section.

#### SYNCHRONIZER OPERATION

In non-read mode, the DP8469 PLL is locked to the REFER-ENCE OSCILLATOR signal (REF OSC). This permits the VCO to remain at a frequency very close to the media bitrate while the PLL is "idling" and thus will minimize the frequency step and associated lock time requirement encountered at the initiation of lock to 2,7 INPUT data. When READ GATE is transitioned LOW to terminate the Read mode, a Zero-Phase-Start and frequency acquisition sequence is employed to insure lock. The REF OSC signal is also used during this time to set the time delay of the internal delay line. Note that this requires the REF OSC signal to be present at all times at a stable and accurate frequency for proper DP8469 operation.

In non-ST506 modes of operation, after the assertion of READ GATE (fully asynchronous, with no timing requirements), and following the completion of two subsequent VCO cycles, the DP8469 VCO is stopped momentarily. The VCO is then restarted in accurate phase alignment with the second data bit which arrives subsequent to the VCO pause. This minimization of phase misalignment between the 2,7 READ DATA and the VCO (referred to as Zero-Phase-Start or ZPS) significantly reduces the data lock accurations are responsible.

The DP8469 incorporates a preamble-specific acquisition feature which is employed for all non-ST506 modes of operation where READ GATE is asserted only within a preamble. In these modes, after READ GATE is asserted HI, the device will be forced to lock to the exact 3T or 4T selected preamble frequency. The frequency discriminating action of the PLL provided in these modes produces a lock-in range equivalent to the available VCO operating range and thus eliminates the possibility of fractional-harmonic lock. Windowing (pulse-gate action; see Pulse Gate section) is prevented. (Application Note AN-414 has an explanation of typical false lock modes.)

In the ST506 modes of operation, at the assertion of READ GATE, the 2,7 IN data pattern is first sampled asynchronously and the synchronizer ZPS lock-on sequence is prevented until eight preamble patterns are recognized. The synchronizer only operates Low Bandwidth Gain, and in a phase lock mode (pulse gate action) during the ST506 operation.

In the non-ST506 modes, the user is provided, the option of an elevated PLL bandwidth during preamble acquisition for an extended capture range. An R<sub>BOOST</sub> pin is provided to allow for an increase in charge pump gain over and above the level set by the R<sub>NOMINAL</sub> pin. The net current through either R<sub>NOMINAL</sub> or R<sub>BOOST</sub>//R<sub>NOMINAL</sub> is multipled internally by 2 for use by the charge pump. The user should connect a high value resistor to R<sub>BOOST</sub> if an elevated PLL bandwidth is not desired to ensure the pin does not fall below the 2V test inactive HI logic threshold.

The READ/REFERENCE CLOCK (R/R CLK) issues a waveform derived from the REF OSC input during the non-read mode (i.e., READ GATE inactive). In the read mode, following the assertion of READ GATE, the completion of the ZPS sequence, and in the case of ST506 modes, the recognition of a short 3T or 4T preamble pattern, R/R CLK issues a waveform derived from the VCO signal. Once data lock is achieved in the read mode and the first bit of the controller Byte Sync field is encountered, the NRZ OUT and R/R CLK outputs are held in a fixed, specified timing relationship. The R/R CLK output switches between input sources without glitches.

The DP8469 provides a COAST control input which serves to clear the phase comparator and disable charge pump action whenever taken to an active, logical-zero level. This function is made available to allow the PLL to be set to free-

### Circuit Operation (Continued)

run, undisturbed, while a detectable defect is being read from the media in a region where re-initiation of the lock procedure is impractical (e.g., data field). External data controller circuitry is responsible for the detection of the defect and issuance of the COAST command. For a more detailed explanation of the synchronizer, and loop filter design. please see the DP8459 datasheet.

#### ENDEC OPERATION

Address Field

2.7 Encoder: The data encoding path is responsible for generating an address field, preamble field, and the data field. This allows synchronous generation of preamble and data in all cases, insuring the fastest possible PLL lock during readback. The encoder has two modes of operation. ST506 and non-ST506 mode. The primary difference between these two modes is the placement of the fields:

| Preamble Field | Address Field                               | Data Field |  |  |  |  |  |  |  |

|----------------|---------------------------------------------|------------|--|--|--|--|--|--|--|

| ST-506 Mode (S | ST-506 Mode (Synchronous Type Address Mark) |            |  |  |  |  |  |  |  |

Data Field

Preamble Field Non ST-506 Mode (Gap Type Address Mark)

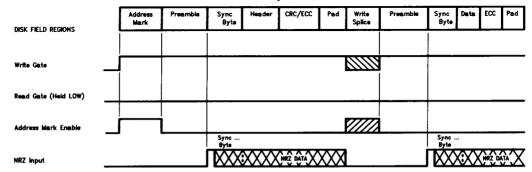

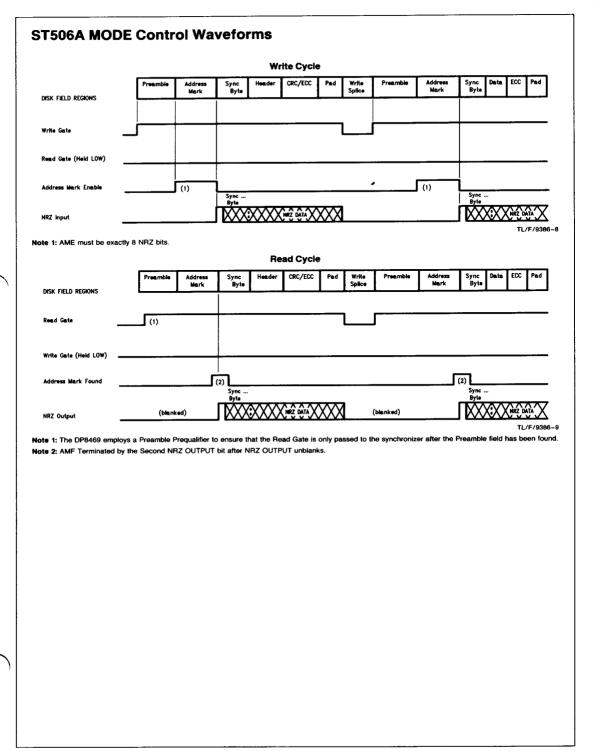

In the ST506 modes, the controller issues a WRITE GATE (WG) command to begin the preamble generation. During the Preamble and Address Mark fields, NRZ IN is blanked. Preamble length is user defined since the ENDEC will continue to generate preamble until Address Mark Enable (AME) is asserted. Assertion of AME terminates the preamble, generates a Phase Sync (for decoding), and begins the N7V address mark. In both ST506 modes, the AME input must be held high for exactly one Byte (8 bits). The N7V address mark is one byte in length, does not violate the 2.7 code rules, and cannot be generated by the encoder. Immediately following the completion of the Address Mark, NRZ IN is unblanked, and encoded as data. This data must be the controller's sync byte. If the controller requires more then one byte of AME, then both AME and NRZ IN must be held LOW during the second byte to insure that during readback the first non-zero data presented to the controller will be a valid Sync Byte. The Sync Byte must begin with a leading "1", however the user has total freedom of the last 7 bits (1----). The encoder continues to encode the data according to the 2.7 code rules until WG is deasserted.

In non-ST506 modes, the controller issues WG to begin the header generation. Normally AME is also issued at the same time. If there is a delay between the assertion of WG and AME, the encoder will begin generating a preamble pattern. Assertion of AME generates the address gap. ESDI and SMD address marks require 3 bytes of AME while the IBM mark only requires 2 bytes of AME. Immediately upon the deassertion of AME, the encoder will begin generating the preamble field. NRZ IN is blanked while AME is asserted. The first non-zero NRZ data following the deassertion of AME must be the controller's Sync Byte as any NRZ IN data presented to the encoder after deassertion of AME terminates the preamble, and is encoded. The Sync Byte restrictions are as follows:

> 3T: 1. - - - - -

4T: 11----- For 3T preamble, the Customer has total freedom of the last 7 bits of the Sync Byte, however in the 4T preamble, the Customer has total freedom of only the last 6 bits.

NRZ IN data is internally blanked while AME is asserted as the DP8469 generates its own address mark data depending upon the type of address mark selected in control register bits 15 to 12. In the ST506 case, NRZ data presented to the DP8469 immediately after deassertion of AME will be encoded as data, while in the non-ST506 modes, the encoder will return to preamble generation until the first nonzero NRZ data following deassertion of AME. The preamble pattern is selected in control register bit 9; HIGH for 3T and OW for 4T. Once the pattern is selected, it is transparent

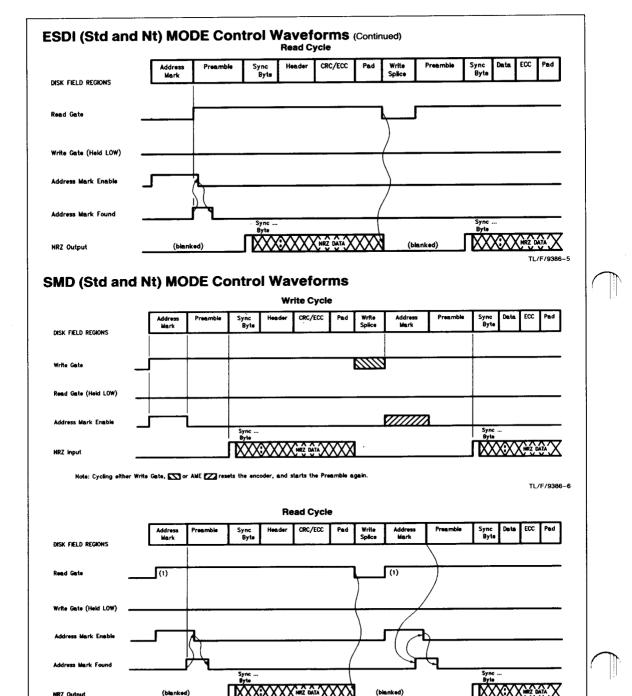

2,7 Decoder: The data readback path is responsible for detecting the address field, preamble field, and finally the data field. The controller issues an active READ GATE (RG) to initiate clock synchronization and 2.7 decoding.

In ST506 mode, the controller first issues RG for the detection of the preamble field. The DP8469 employs a two phase preamble prequalifier on the internal RG. The prequalifier must first find several bytes of valid preamble pattern before it passes RG to the synchronizer and enables the standard preamble detector. In the event there is enough valid looking data to qualify as a preamble, the synchronizer is switched into phase-only low gain mode on the assertion of RG to guarantee that it can pass through any subsequent Write Splice without problems. The synchronizer employs a Zero Phase Start circuit to minimize its lock

Once preamble has been located (thirty-one 3T patterns or fifteen 4T patterns) the decoder begins searching for the N7V address mark. Phase-sync and address mark detection are accomplished at the same time, and the decoder then unblanks the NRZ OUT at the start of Controller's Sync

The non-ST506 modes (commonly called "Gap Type") breakdown into two groups:

- a) ESDI and IBM modes where the controller does not assert RG until after AMF signifies the start of the Preamble.

- b) SMD mode where the controller asserts RG prior to AMF, and the ENDEC is responsible for blocking RG to the synchronizer until the Preamble field has been found.

In both cases, the address mark precedes the preamble field. The controller instructs the DP8469 to search for the address mark, a 2 NRZ byte gap, transitionless ESDI and SMD gaps and an IBM gap with 3 specific transitions. Once the gap has been located, the AMF output signals the controller, and the controller responds with assertion of RG in ESDI and IBM. In the SMD mode, RG is internally qualified with AMF, providing the same function.

Once RG has been passed to the synchronizer, the same thirty-one 3T or fifteen 4T preamble pattern requirements must be met before the decoder can look for the Phase Sync, and unblank. The first non-zero NRZ OUT data is the controller's Sync Byte.

#### Circuit Operation (Continued)

Both the encoder and decoder follow the encoding rules as shown in the table below:

|     |   |   | IBN | 1 2,7    | Conv | ersi | on Ta | ble |   |   |   |

|-----|---|---|-----|----------|------|------|-------|-----|---|---|---|

| NRZ |   |   |     | 2,7 Code |      |      |       |     |   |   |   |

|     | 0 | 0 | 0   |          |      | 0    | 0     | 0   | 1 | 0 | 0 |

|     |   | 1 | 0   |          |      |      |       | 0   | 1 | 0 | 0 |

|     | 0 | 1 | 0   |          |      | 1    | 0     | 0   | 1 | 0 | 0 |

| 0   | 0 | 1 | 0   | 0        | 0    | 1    | 0     | 0   | 1 | 0 | 0 |

|     |   | 1 | 1   |          |      |      |       | 1   | 0 | 0 | 0 |

|     | 0 | 1 | 1   |          |      | 0    | 0     | 1   | 0 | 0 | 0 |

| 0   | 0 | 1 | 1   | 0        | 0    | 0    | 0     | 1   | 0 | 0 | 0 |

- 2 = Minimum # of Zeros between adjacent Ones

- 7 = Maximum # of Zeros between adjacent Ones

- 1 = NRZ bits for relative conversion ratio

- 2 = Code bits for relative conversion

- 3 = # of different length code words

## **Precompensation**

The Precomp circuitry uses the same basic delay-line technique to provide controllable time-delay steps. The user applies the necessary external RC components to the TC pin to provide the desired time step sizes. By using the BIT OUT and PWR outputs, different RC values can be used for different circumstances ... Programming Bit 8 = LOW sets the PWG output to follow WRITE GATE, while programming Bit 8 = HI sets PWG to the logical inverse of WRITE GATE. This allows complete freedom in setting the precomp time constants independently for different Write channel anomolies such as inner vs outer track recording densities.

TL/F/9386-14

Bit-crowding on the disk results in a maximum frequency pattern (3T) timing error to the data written on the disk. Whenever the 3T pattern is adjacent to a non-3T pattern, the two 3T bits are pushed apart, resulting in a time skew during readback. The precompensation feature allows the user to adjust the 3T pattern on a cycle-by-cycle basis to correct for this problem.

#### **Precompensation Bit Patterns**

| Bit<br>t-3 | Bit<br>t-2 | Bit<br>t – 1 | Target<br>Bit t | Bit<br>t+1 | Bit<br>t+2 | Bit<br>t+3 |

|------------|------------|--------------|-----------------|------------|------------|------------|

| 0          | 0          | 0            | No Shift        | 0          | 0          | 0          |

| 1          | 0          | 0            | No Shift        | 0          | 0          | 1          |

| 1          | 0          | 0            | Shift Early     | 0          | 0          | 0          |

| 0          | 0          | 0            | Shift Late      | 0          | 0          | 1          |

## **Test Mode Operation**

The DP8469 provides 7 special test modes. With the exception of the Phase Comparator Test (PCT), SYNC DATA and SYNC CLK, these special test modes are used for production testing. The PCT data is the logical OR'ing between charge Pump Up and charge Pump Down, and can be used to examine the locking action of the PLL. The SYNC DATA and SYNC CLK outputs allow window strobe measurements. All together, they will allow the user to fine tune the application to insure minimum jitter during readback. The PCT function is present on the AMF output in test mode 1 (load 001, MSB first). SYNC DATA and SYNC CLK are present in test mode 7 (load 111, MSB first) on the READ/REF CLK and OUTPUT 2,7 outputs respectively.

The test modes are set by a 3 bit test register that is accessed via the RBOOST and RNOMINAL inputs. In an application, both Recost and RNOMINAL are held above the 2V threshold clearing the test register to mode 0, and allowing both HI and LOW gain PLL action. This insures that the device will always power-up in the normal operating mode. By pulling R<sub>BOOST</sub> below the 2V threshold, the test register can now accept 3 bits of data that will decode to one of seven test modes (the eighth mode, 000, is normal operation). The R<sub>NOMINAL</sub> input is used to select between loading the 24 bit control register and the 3 bit test register; R<sub>NOMINAL</sub> = HI sends the data to the 24 bit register while R<sub>NOMINAL</sub> = LOW sends the data to the 3 bit test register. The test register is then loaded using CRE, CRC. and CRD. After loading the test register, first return CRE = HI to protect the data in both the Control Register, as well as the data in the Test Register. It is required to set CRE = HI before changing the state of any other control input (including both RNOMINAL and RBOOST) in order to prevent any internal switching from generating false clocks and changing the state of any register data. Next, return RNOMINAL HI to allow normal synchronizer operation. Maintain Recost LOW to preserve the test mode. This combination will only allow low gain PLL action during testing. CRD and CRC must also be returned LOW, and held there during testing as they are used as special testing inputs.

The action of pulling R<sub>NOMINAL</sub> low disables the charge pump, and drives the VCO to the lower clamp limit. For any test where the PLL loop needs to run, such as window strobe tests, the test mode must be loaded before the loop is locked. First, load the test register and return CRE HI, and then R<sub>NOMINAL</sub> HI. Then reload the control register, and return CRE HI. Finally, exercise the device starting with RG deasserted, and running the device through the complete Read cycle. Note that for the device to remain in test mode, RBOOST must be held low, and this eliminates the high gain mode of operation for the synchronizer. To observe the synchronizer in a high gain mode, replace RNOMINAL with a resistor equivalent to the parallel combination of RNOMINAL and RNOMINAL. Do not exceed the 1 mA maximum total input current specification for the RNOMINAL pin.

## **DP8469 24 Bit Control Register**

| MSB  | Control Register is Loaded MSB (Bit 23) First, and LSB (Bit 0) Last. |        |       |   |              |               |              |    |   |                |   |                 |            |             |           |   |                        |   |                |               |               |             |     |

|------|----------------------------------------------------------------------|--------|-------|---|--------------|---------------|--------------|----|---|----------------|---|-----------------|------------|-------------|-----------|---|------------------------|---|----------------|---------------|---------------|-------------|-----|

| 23 M | 23                                                                   | 5      | 8     | 6 | 8            | 12            | 92           | 15 | 4 | 5              | 2 | =               | 유          | a           | ∞         | 7 | 9                      | ĸ | 4              | 6             | 8             | -           | 570 |

|      | Wind                                                                 | low Si | trobe |   | Gain Control | VCO Frequency | Range Select |    |   | ss Ma<br>Selec |   | NRZ Hi-Z Enable | Bit Out Hi | 3T Preamble | RC Adjust |   | recoi<br>Ster<br>Selec | Ò | Invert 2,7 Out | Edge Polarity | Pulse Pairing | Step Select |     |

| F   | ulse l | airing            | Dela       | y Steps      |

|-----|--------|-------------------|------------|--------------|

| P   |        | Pairing<br>rty/La | Delay Step |              |

| ÷   | ~      | _                 | 0          | / Dit 011111 |

| ×   | 0      | 0                 | 0          | Bypassed     |

| Х   | 0      | 0                 | 1          | 0.0          |

| 0/1 | 0      | 1                 | 0          | ± 2.5*       |

| 0/1 | 0      | 1                 | 1          | ± 5.0*       |

| 0/1 | 1      | 0                 | 0          | ± 7.5*       |

| 0/1 | 1      | 0                 | 1          | ± 10.0*      |

| 0/1 | 1      | 1                 | 0          | ± 12.5*      |

| 0/1 | 1      | 1                 | 1          | ± 15.0*      |

\*Bit 3 selects which flux change from the Pulse Detector is Pulse Pairing Corrected.

| Control Register Bit Definitions<br>for Bits 4, 8, 9, 10, 11, 18 |             |   |             |  |  |  |  |

|------------------------------------------------------------------|-------------|---|-------------|--|--|--|--|

| 4                                                                | 2.7 Output  | 0 | True        |  |  |  |  |

| ă                                                                | z,/ Output  | 1 | Inverted    |  |  |  |  |

| 80                                                               | RC ADJ      | 0 | WRT GATE    |  |  |  |  |

| ä                                                                | Follows     | 1 | WRT GATE    |  |  |  |  |

| 0                                                                | 3T/4T       | 0 | 4T          |  |  |  |  |

| BIT 9                                                            | Preamble    | 1 | ЗТ          |  |  |  |  |

| Bit 10                                                           | BIT OUT     | 0 | Active LOW  |  |  |  |  |

| ä                                                                | Bit OUT     | 1 | Inactive HI |  |  |  |  |

| F                                                                | NRZ OUT     | 0 | Totem Pole  |  |  |  |  |

| B# 11                                                            | 14112 001   | 1 | TRI-STATE   |  |  |  |  |

| 12                                                               | PLL Switch  | 0 | READ GATE   |  |  |  |  |

| Ħ                                                                | to Low Gain | 1 | LOCK DETECT |  |  |  |  |

|   | Precomp Delay Steps |            |             |  |  |  |  |  |  |  |  |

|---|---------------------|------------|-------------|--|--|--|--|--|--|--|--|

|   | Precom<br>arly/La   | Delay Step |             |  |  |  |  |  |  |  |  |

| ~ | -                   | 0          | % Bit Shift |  |  |  |  |  |  |  |  |

| 0 | 0                   | 0          | Bypassed    |  |  |  |  |  |  |  |  |

| 0 | 0                   | 1          | 0.0         |  |  |  |  |  |  |  |  |

| 0 | 1                   | 0          | ± 2.5*      |  |  |  |  |  |  |  |  |

| 0 | 1                   | 1          | ± 5.0*      |  |  |  |  |  |  |  |  |

| 1 | 0                   | 0          | ± 7.5*      |  |  |  |  |  |  |  |  |

| 1 | 0                   | 1          | ± 10.0*     |  |  |  |  |  |  |  |  |

| 1 | 1                   | 0          | ± 12.5*     |  |  |  |  |  |  |  |  |

| 1 | 1                   | 1          | ± 15.0*     |  |  |  |  |  |  |  |  |

|              | Cor<br>Regis | Address<br>Mark |   |         |

|--------------|--------------|-----------------|---|---------|

| <del>5</del> | 4            | 5               | 5 | Mode    |

| 0            | 0            | 0               | 0 | ESDI    |

| 0            | 0            | 0               | 1 | SMD     |

| 0            | 0            | 1               | 0 | ESDI*   |

| 0            | 0            | 1               | 1 | N/A     |

| 0            | 1            | 0               | 0 | ST506A  |

| 0            | 1            | 0               | 1 | ST506B  |

| 0            | 1            | 1               | 0 | HARD    |

| 0            | 1            | 1               | 1 | IBM*    |

| 1            | 0            | 0               | 0 | ESDI NT |

| 1            | 0            | 0               | 0 | SMD NT  |

\*DP8466 Compatible

|    | VCO Freq Range |             |  |  |  |  |  |  |  |  |  |

|----|----------------|-------------|--|--|--|--|--|--|--|--|--|

| В  | its            | Freq Range  |  |  |  |  |  |  |  |  |  |

| 15 | 7              | (Mbits/sec) |  |  |  |  |  |  |  |  |  |

| 0  | 0              | 1.5-3       |  |  |  |  |  |  |  |  |  |

| 0  | 1              | 3-6         |  |  |  |  |  |  |  |  |  |

| 1  | 0              | 6-12        |  |  |  |  |  |  |  |  |  |

| 1  | 1              | 12-24       |  |  |  |  |  |  |  |  |  |

|   |     | ont |      |    |            | Typical                          |

|---|-----|-----|------|----|------------|----------------------------------|

| F | leg | ist | er : | #  | Strobe     | Window                           |

| ន | 22  | 5   | 8    | \$ | Word       | Strobe                           |

| 0 | 1   | 1   | 1    | 1  | -15        | -0.270×T <sub>vco</sub>          |

| 0 | 1   | 1   | 1    | 0  | 14         | $1-0.252 \times T_{\text{ucol}}$ |

| 0 | 1   | 1   | 0    | 1  | -13        | -0.234×Tuco                      |

| 0 | 1   | 1   | 0    | 0  | -12        | I – 0.216×Tvcd                   |

| 0 | 1   | 0   | 1    | 1  | -11        | -0.198×T <sub>vco</sub>          |

| 0 | 1   | 0   | 1    | 0  | -10        | -0.180×T <sub>vco</sub>          |

| 0 | 1   | 0   | 0    | 1  | -9         | -0.162×T <sub>vco</sub>          |

| 0 | 1   | 0   | 0    | 0  | -8         | -0.144×T <sub>vco</sub>          |

| 0 | 0   | 1   | 1    | 1  | -7         | -0.126×T <sub>vco</sub>          |

| 0 | 0   | 1   | 1    | 0  | -6         | -0.108×T <sub>vco</sub>          |

| 0 | 0   | 1   | 0    | 1  | -5         | $-0.090 \times T_{VCO}$          |

| 0 | 0   | 1   | 0    | 0  | -4         | -0.072×T <sub>vco</sub>          |

| 0 | 0   | 0   | 1    | 1  | _ <b>3</b> | -0.054×T <sub>vco</sub>          |

| 0 | 0   | 0   | 1    | 0  | -2         | -0.036×T <sub>vco</sub>          |

| 0 | 0   | 0   | 0    | 1  | -1         | -0.018×T <sub>vco</sub>          |

| 0 | 0   | 0   | 0    | 0  | 0          | 0                                |

| 1 | 0   | 0   | 0    | 0  | 0          | 0                                |

| 1 | 0   | 0   | 0    | 1  | 1          | 0.018×T <sub>vco</sub>           |

| 1 | 0   | 0   | 1    | 0  | 2          | 10.036×Tu∞                       |

| 1 | 0   | 0   | 1    | 1  | 3          | 10.054×Tuco                      |

| 1 | 0   | 1   | 0    | 0  | 4          | 10.072×Tvcc                      |

| 1 | 0   | 1   | 0    | 1  | 5          | 10.090×T <sub>vco</sub>          |

| 1 | 0   | 1   | 1    | 0  | 6          | 0.108×T <sub>vco</sub>           |

| 1 | 0   | 1   | 1    | 1  | 7          | 0.126×T <sub>vcn</sub>           |

| 1 | 1   | 0   | 0    | 0  | 8          | 0.144×Tvcc                       |

| 1 | 1   | 0   | 0    | 1  | 9          | 0.162×Tvcc                       |

| 1 | 1   | 0   | 1    | 0  | 10         | 0.180×T <sub>vco</sub>           |

| 1 | 1   | 0   | 1    | 1  | 11         | 0.198×T <sub>vco</sub>           |

| 1 | 1   | 1   | 0    | 0  | 12         | 0.216×T <sub>vco</sub>           |

| 1 | 1   | 1   | 0    | 1  | 13         | 0.234×T <sub>vco</sub>           |

| 1 | 1   | 1   | 1    | 0  | 14         | 0.252×Tvco                       |

| 1 | 1   | 1   | 1    | 1  | 15         | 0.270×T <sub>VCO</sub>           |

## **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required. please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage Inputs (Note 1) -0.5V to +7.0V

TTI

CMOS

Outputs (Note 1)

TTI

-0.5V to +7.0V-0.5V to +5.5V

CMOS

Input Current Maximum (R<sub>NOMINAL</sub>, R<sub>BOOST</sub>, CPO, VCOI, TEF)

+ 2 mA

-0.5V to +7.0V-0.5V to +5.5V Storage Temperature Operating Temperature Range -65°C to +150°C 0°C to +70°C

**ESD Susceptibility**

1500V

## **Recommended Operating Conditions**

| Symbol             | Parameter                                      |                  | Conditions               | Min  | Тур  | Max  | Units |

|--------------------|------------------------------------------------|------------------|--------------------------|------|------|------|-------|

| Vcc                | Supply Voltage                                 |                  |                          | 4.75 | 5.00 | 5.25 | ٧     |

| TA                 | Ambient Temperature                            |                  |                          | 0    | 25   | 70   | •c    |

| V <sub>IH</sub> .  | High Logic Level<br>Input Voltage              |                  |                          | 2.0  |      |      | V     |

| VIL                | Low Logic Level<br>Input Voltage               |                  |                          |      |      | 0.8  | v     |

| Юн                 | High Logic Level                               | I <sub>OH1</sub> | 2,7 Output               |      |      | -400 | μΑ    |

|                    | Output Current                                 | I <sub>OH2</sub> | AMF, NRZ OUT, RD/REF CLK |      |      | -2.0 | mA    |

|                    |                                                | I <sub>OH3</sub> | AMF, NRZ OUT, RD/REF CLK |      |      | -20  | μΑ    |

| loL                | Low Logic Level                                | I <sub>OL1</sub> | 2,7 Output               |      |      | 20   | mA    |

|                    | Output Current                                 | I <sub>OL2</sub> | RC ADJ, BITOUT           |      |      | 8.0  | mA    |

|                    |                                                |                  | AMF, NRZ OUT, RD/REF CLK |      |      | 4.0  | mA    |

|                    |                                                | I <sub>OL3</sub> | AMF, NRZ OUT, RD/REF CLK |      |      | 20   | μΑ    |

| IRC ADJ            | Pulse-Pairing/Pre-Com<br>Maximum External Load | 0.0              |                          | -16  | mA   |      |       |

| f <sub>NRZ</sub>   | Operating Data Rate Range                      |                  |                          |      |      | 24   | Mb/   |

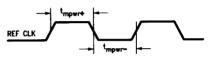

| trnpwr             | Minimum Pulse Width o                          | f REF CLK,       | HIGH or LOW              | 10   |      |      | ns    |

| t <sub>mpwi</sub>  | Minimum Pulse Width o                          | f INPUT 2,7      | , HIGH                   | 20   |      |      | ns    |

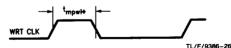

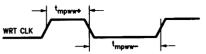

| t <sub>mpww</sub>  | Minimum Pulse Width o                          | f WRT CLK,       |                          | 20   |      |      | ns    |

| t <sub>mpwcc</sub> | Minimum Pulse Width o                          | f CRC,           |                          | 40   |      |      | ns    |

| t <sub>mpwc</sub>  | CONTROL REGISTER Minimum Pulse Width H         |                  | V (Note 2)               | 40   |      |      | ns    |

| t <sub>scec</sub>  | CONTROL REGISTER Setup-Time with respec        |                  | ote 2)                   | 80   |      |      | ns    |

| t <sub>hcec</sub>  | CONTROL REGISTER Hold-Time with respect        |                  | te 2)                    | 80   |      |      | ns    |

| t <sub>scdc</sub>  | CONTROL REGISTER Setup-Time with respec        |                  | ote 2)                   | 40   |      |      | ns    |

| thodo              | CONTROL REGISTER Hold-Time with respect        |                  | te 2)                    | 40   |      |      | ns    |

| ICPIN              | Combined R <sub>NOM</sub> and R                | BOOST Inpu       | t Current                |      |      | 1000 | μΑ    |

Note 1: Bipolar Inputs: REF CLK, COAST, RNOM, RBOOST Bipolar Outputs: TC, 2,7 OUT, RC ADJ, BITOUT

CMOS Inputs: 2,7 IN, CRE, CRD, CRC, PULSE POL, NRZ IN, WRT CLK, WRT GATE, AME, READ GATE

CMOS Outputs: AMF, NRZ OUT, RD/REF CLK

Analog Inputs: TEF, CPO, VCO IN

Note 2: Parameter guaranteed by correlation to characterization data. No outgoing test performed.

| Symbol                     | Parameter                              | Conditions                                                          | Min                    | Тур                    | Max                 | Units    |

|----------------------------|----------------------------------------|---------------------------------------------------------------------|------------------------|------------------------|---------------------|----------|

| V <sub>IC</sub>            | Input Clamp Voltage<br>(All Inputs)    | $V_{CC} = Min, I_{I} = -18 \text{ mA}$                              |                        |                        | 1.5                 | ٧        |

| V <sub>OH1</sub>           | High Level Output Voltage              | V <sub>CC</sub> = Min, I <sub>OH</sub> = I <sub>OH1</sub>           | V <sub>CC</sub> - 2V   | V <sub>CC</sub> - 1.6V |                     | ٧        |

|                            |                                        | V <sub>CC</sub> = Min, I <sub>OH</sub> = I <sub>OH2</sub>           | 3.5                    |                        |                     | ٧        |

|                            |                                        | $V_{CC} = Min, I_{OH} = I_{OH3}$                                    | V <sub>CC</sub> - 0.1V |                        |                     | ٧        |

| V <sub>OL1</sub>           | Low Level Output Voltage               | $V_{CC} = Min, I_{OL} = I_{OL1}$                                    |                        |                        | 0.5                 | ٧        |

|                            |                                        | $V_{CC} = Min, I_{OL} = I_{OL2}$                                    |                        |                        | 0.4                 | <u> </u> |

| ·····                      |                                        | $V_{CC} = Min, I_{OL} = I_{OL3}$                                    |                        |                        | 0.1                 |          |

| loz                        | Maximum TRI-STATE Leakage (Note 1)     | $V_{CC} = Max, 0.4V \le V_O \le 2.7V$                               |                        |                        | ± 2.0               | μА       |

| ICEX                       | Open-Collector Leakage<br>(Note 2)     | $V_{CC} = Max, V_O = Max$                                           |                        |                        | -100                | μА       |

| lн                         | High Level Input Current (Note 3)      | V <sub>CC</sub> = Max, V <sub>I</sub> = 2.7V                        |                        |                        | 20                  | μΑ       |

| I <sub>IL</sub>            | Low Level Input Current (Note 3)       | $V_{CC} = Max, V_I = 0.4V$                                          |                        |                        | -200                | μΑ       |

| I <sub>IN</sub>            | Maximum Input Current (Note 4)         | $V_{CC} = Max, V_{IN} = V_{CC} \text{ or GND}$                      | -1                     |                        | +1                  | μΑ       |

| I <sub>O</sub><br>(Note 5) | Output Drive Current OUTPUT 2,7        | V <sub>CC</sub> = Max, V = 2.125V                                   | -12                    |                        | -110                | mA       |

|                            | TC Pin (Note 6)                        | V <sub>CC</sub> = Max, V = 2.125V                                   | -36                    |                        |                     | mA       |

| ICPO                       | Charge Pump Output<br>Current (K1)     | 100 ≤ I <sub>RP</sub> ≤ 1000<br>(Note 7)                            | 1.7 l <sub>RP</sub>    | 2.0 I <sub>RP</sub>    | 2.5 I <sub>RP</sub> | μΑ       |

| CPO-OFF                    | Charge Pump Output<br>Inactive Current | 100 ≤ I <sub>RP</sub> ≤ 1000<br>(Note 7)                            | -0.85                  |                        | + 0.85              | μΑ       |

| lycoi                      | VCOI Input Leakage Current             | VCOI Voltage 1.5V                                                   | -0.25                  |                        | + 0.25              | μΑ       |

| VRNOM                      | Voltage Across R-NOM Resistor          | $1.2 \text{ k}\Omega \leq R_{\text{NOM}} \leq 12 \text{ k}\Omega$   | Typ - 18%              | 0.26 V <sub>CC</sub>   | Typ + 18%           | ٧        |

| V <sub>RBST</sub>          | Voltage Across R-BOOST Resistor        | $1.2 \text{ k}\Omega \leq R_{\text{BOOST}} \leq 12 \text{ k}\Omega$ | Typ - 18%              | 0.26 V <sub>CC</sub>   | Typ + 18%           | ٧        |

| lcc1                       | Supply Current,                        | V <sub>CC</sub> = Max (Note 8)                                      |                        |                        | 190                 | mA       |

Note 1: Applies to the TRI-STATE output NRZ OUT with CTRL BIT 11 set HI, and WRT GATE HI.

Note 2: Applies to the Bipolar outputs: RC ADJ, BITOUT.

Nominal Strobe

Supply Current,

Early Strobe

Note 3: Applies to the Bipolar inputs: REF CLK, COAST, RNOM, RBOOST

Note 4: Applies to the CMOS inputs: INPUT 2,7, CRE, CRD, CRC, PULSE POL, NRZ IN, WRT CLK, WRT GATE, AME, READ GATE.

V<sub>CC</sub> = Max, (Note 9)

Note 5: This represents approximately one-half of the true short-circuit output current, I.

Note 6: This only applies to the TC Open Emitter output. Do not exceed 100 mA for more than 0.1 sec.

Note 7: IRP = INOM + IBOOST

lCC2

Note 8: I<sub>CC1</sub> is measured with the window strobe set at nominal timing (Register Bits 23 through 19 = 0,0,0,0,0); VCO operating at the maximum allowed frequency within any given range selection.

TBD

mΑ

Note 9:  $I_{CC2}$  is measured with the window strobe set to the maximum early timing (Register Bits 23 through 19 = 0,1,1,1,1); VCO operating at the maximum allowed frequency within any given range selection.

| _       |             |           |

|---------|-------------|-----------|

| Fyterna | l Component | Selection |

| Symbol                                                                        | Parameter                                                             | Min  | Тур | Max   | Units |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------|------|-----|-------|-------|

| R <sub>NOM</sub>                                                              | Charge Pump Nominal Operating<br>Current Setting Resistor<br>(Note 1) | 1.2  |     | 12    | kΩ    |

| R <sub>BOOST</sub>                                                            | Charge Pump Boost Current Setting Resistor (Note 1)                   |      |     | 80    | kΩ    |

| C <sub>NOM</sub> R <sub>NOM</sub> Bypass Capacitor (Note 2)                   |                                                                       | 0.01 |     |       | μF    |

| C <sub>BOOST</sub> R <sub>BOOST</sub> Bypass Capacitor (Note 2)               |                                                                       | 0.01 |     |       | μF    |

| R <sub>TC</sub> Pre-Comp/Pulse Pairing Timing Resistor (Note 3)               |                                                                       | 0.33 |     | 10    | kΩ    |

| C <sub>TC</sub> Pre-Comp/Pulse Pairing Timing Capacitor (Note 3)              |                                                                       | 33   |     | 10000 | pF    |

| R <sub>RC ADJ</sub> Secondary Pre-Comp/Pulse Pairing Timing Resistor (Note 4) |                                                                       | 0.33 |     | 10    | kΩ    |

| R <sub>BIT OUT</sub>                                                          | Secondary Pre-Comp/Pulse Pairing Timing Resistor (Note 4)             | 0.33 |     | 10    | kΩ    |

Note 1: The minimum allowed value for the parallel combination of  $R_{NOM}$  and  $R_{BOOST}$  is 1.2 k $\Omega$ .

Note 2: C<sub>NOM</sub> and C<sub>BOOST</sub> should be high quality, high frequency type.

Note 3:  $R_{TC}$  and  $C_{TC}$  are both used to establish Pulse-Pairing and Pre-Comp timing on the TC pin.

Note 4: R<sub>RC</sub> ADJ and R<sub>BIT</sub> OUT modify the external timing on the TC pin for Read vs Write and inner track adjustability.

## **AC Electrical Characteristics**

| Symbol                              | Parameter                                                                                                           | Min                | Тур                   | Max                | Units     |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|--------------------|-----------|

| <sup>t</sup> STOP                   | READ/REF CLK Positive Transitions after READ GATE until Data Lock ZPS Sequence Begins (VCO Freezes) (Notes 1, 2)    |                    | 2<br>(Note 4)         | 3<br>(Note 4)      | _         |

| <sup>†</sup> RESTART                | Positive 2,7 INPUT Transitions following VCO Freeze until the VCO Restarts (Note 2)                                 |                    | 2                     | 3                  | _         |

| <sup>†</sup> READ ABORT             | Number of REF CLOCK Cycles following READ GATE<br>Deactivation until REF CLOCK Lock ZPS Sequence begins<br>(Note 2) |                    |                       | 4                  | _         |

| t <sub>T</sub>                      | Window Truncation (Half Window Loss); 10 and 20 Mbit/s at Strobe Position M = -2 (Note 3)                           |                    | 4% × T <sub>VCO</sub> |                    | ns        |

| φ Linearity                         | Phase Range for Charge Pump Linearity (wrt VCO) (Note 2)                                                            |                    | ± π                   |                    | Radians   |

| K <sub>VCO</sub>                    | VCO Gain Constant (Note 6)                                                                                          | 1.0 ω <sub>ο</sub> | 1.2 ω <sub>ο</sub>    | 1.7 ω <sub>ο</sub> | rad/sec V |

| fMAX VCO                            | VCO Maximum Frequency; Control Bits 17,16 = 11                                                                      | 70                 |                       |                    | MHz       |

| <sup>t</sup> ZPSR                   | Zero Phase Start Trigger Bit Targeting Accuracy, READ GATE Activation (READ) (Note 5)                               |                    | 2                     |                    | ns        |

| Δf <sub>VCO</sub> /f <sub>RFC</sub> | Automatic f <sub>VCO</sub> Range Limiting (Note 2)                                                                  |                    | 50                    |                    | %         |

| <sup>t</sup> RRCH                   | RD/REF CLK Rest Period at Assertion or Deassertion of READ GATE (Note 2)                                            | 1/2                |                       | 3                  | Tvco      |

| Encoder Delay                       | Serial Delay Time in REF CLK Cycles + ns Delay (Note 7)                                                             |                    |                       | 10 + 100           | Cyc + ns  |

| Decoder Delay                       | Serial Delay Time in REF CLK Cycles + ns Delay                                                                      |                    |                       | 8 + 100            | Cyc + ns  |

### AC Electrical Characteristics (Continued)

| Symbol                                                   | Parameter                                                                                         | Min         | Тур | Max                              | Units |           |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------|-----|----------------------------------|-------|-----------|

| t <sub>plh</sub> AMF<br>Assertion Time                   | ST506A and B; After REF CLK following Address D<br>(ESDI, SMD, and IBM Gap Type Address are Async | 50          |     | 100                              | ns    |           |

| t <sub>phi</sub> AMF                                     | ESDI and SMD (Spec & Noise Tolerant); Falling Edge of AME                                         |             |     |                                  | 100   | ns        |

| Deassertion Time                                         | DP8466 Compatible (ESDI and IBM); 2nd input 2,7                                                   | 50_         |     | 100                              | ns    |           |

|                                                          | ST506A: 2nd input 2,7 Pulse                                                                       |             |     |                                  | 100   | ns        |

| ST506B; Next REF CLK Positive Edge after Falling RD GATE |                                                                                                   |             |     |                                  | 100   | ns        |

| t <sub>mpw</sub>                                         | REF CLK Minimum Pulse Width tmpwr+ tmpwr-                                                         | 5           |     |                                  | ns    |           |

| •                                                        | INPUT 2,7 Minimum Input Pulse Width tmpwi+                                                        |             |     |                                  |       | ns        |

|                                                          | WRT CLK Minimum Input Pulse Widths tmpww+ t                                                       | 10          |     |                                  | ns    |           |

| t <sub>s1/0</sub>                                        | REF CLK Setup and Hold Times to WRT CLK                                                           |             |     | 10                               | ns    |           |

| t <sub>h1/0</sub>                                        | WRT CLK Setup and Hold Times to AME, NRZ IN, WRT GATE, READ GATE                                  |             |     | 20                               | ns    |           |

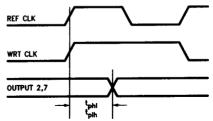

| t <sub>plh</sub> , t <sub>phl</sub>                      | Propagation Delay from REF CLK to OUTPUT 2,7                                                      |             |     |                                  | 100   | ns        |

| t <sub>rfc-rrc</sub>                                     | Propagation Delay from REF CLOCK to RD/REF CLK, READ GATE LOW                                     |             |     |                                  | 50    | ns        |

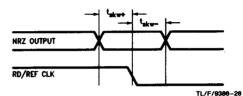

| t <sub>skw ±</sub>                                       | RD/REF CLK Negative Edge to NRZ OUTPUT Transition                                                 |             |     |                                  | ±5    | ns        |

| L <sub>PDT</sub>                                         | Length of Valid Preamble Pattern Required for Internal PREAMBLE DETECTED (Note 2)                 | 3T Preamble | 31  | 32                               | 33    | 2,7 Input |

|                                                          |                                                                                                   | 4T Preamble | 15  | 16                               | 17    | Pulses    |

| t <sub>Str</sub>                                         | Window Strobe Time Step (M = Hex Value of Bits 22-19 in CONTROL REGISTER; Bit 23 = Sign Bit       |             |     | M × (1.8%)<br>× T <sub>RFC</sub> |       | ns        |

Note 1: ST506 and SMD modes utilize a Preamble Prequalification routine to guarantee that the synchronizer only locks to data during a valid Preamble Field. This adds a prequalification time to the T<sub>STOP</sub> time parameters as follows:

ST506: Adds 8 full preamble fields PRIOR to the T<sub>STOP</sub> parameter

SMD: Adds the time it takes to locate a valid Address Mark, and output a valid AMF

Note 2: Limits are guaranteed by design or correlation to characterization data; no outing testing is performed.

Note 3: The preliminary DP8469 static window specification, IT, applies only to the factory-tested data rates of 10 Mb/s (Control Bits 17, 16 = 01) and 20 Mb/s (17,16 = 10), with the component values as listed for each corresponding data rate in Figures 7 and 12, test configuration as shown in Figure 24, test procedure as shown in Figure 25, and data rates is not expected.

Note 4: tzpsR (ZPS Read) gauges the accuracy with which the ZPS circuitry aligns the VCO to the triggering 2,7 INPUT bit internally (i.e., initial phase step) at the completion of a ZPS operation following READ GATE assertion.

Note 5:  $I_{IN} = V_{CC}/(4 \times R_{IN})$ .  $R_{IN} = R_{NOM}$  (HGD High) or  $R_{NOM} \|R_{BOOST}$  (HGD Low).

**Note 6:** Specification for 25°C only. Temperature coefficient = -0.4%/°C.

Note 7: Encoder Serial Delay specified for Pre-Comp set to Bypass Mode (bits 2,1,0 = 000). Non-Bypass Pre-Comp adds 5 REF CLK cycles plus 50 ns.

## **DP8469 Loop Filter Component Values**

| Preamble             | 10 Mbit/Sec |       | 20 Mbit/Sec |       | Units  |

|----------------------|-------------|-------|-------------|-------|--------|

| Туре                 | 3T          | 4T    | 3Т          | 4T    | Onno   |

| Ref Clk Frequency    | 20          | 20    | 40          | 40    | MHz    |

| NRZ Data Rate        | 10          | 10    | 20          | 20    | Mbit/s |

| Sync Field Frequency | 20          | 20    | 40          | 40    | MHz    |

| ζ Min                | 20          | 20    | 40          | 40    | None   |

| ζ Max                | 20          | 20    | 40          | 40    | None   |

| ζ Sync               | 20          | 20    | 40          | 40    | None   |

| Sync Field Frequency | 6.7         | 5     | 13.3        | 10    | MHz    |

| ω Sync               | 20          | 20    | 40          | 40    | Krad/s |

| C1 (Main Loop)       | 0.018       | 0.018 | 0.0082      | 0.082 | μF     |

| R1 (Main Loop)       | 150         | 150   | 150         | 150   | Ω      |

| C2 (Main Loop)       | 510         | 510   | 200         | 200   | μF     |

| CT1 (TEF)            | 0.056       | 0.056 | 0.0027      | 0.027 | μF     |

| RT1 (TEF)            | 68          | 68    | 68          | 68    | Ω      |

| TEF Settling Time    | 9.6         | 9.6   | 4.6         | 4.6   | μs     |

## **Loop Filter Component Values**

Preamble Sync natural frequency has been chosen to yield phase error  $\leq 0.063$  radians (i.e.,  $1\% \times 2\pi$ ) at sync field end, given a 1% frequency step at READ GATE assertion.  $R_{NOM} = R_{BOOST} = 2.4k$  for all loop filter selections. These values apply for Bit 18 = HI, device switches to LOW Gain on assertion of READ GATE.

The TEF settling times are given which indicate time required for the DP8469 to accommodate a change of Strobe

setting from nominal selection to either extreme (early/late), or vice versa, to within approximately 1% of final value.

The values listed in the Loop Filter Component Values table are the approximate filter values that are used for Static Window Truncation testing. These values represent a simple solution, yielding only average circuit behavior. Please see National Semiconductor's DP8459 datasheet for a more thorough discussion on loop filter component selection.

TL/F/9386-3

## **Application Diagram**

## **Encoder Serial Delay Times**

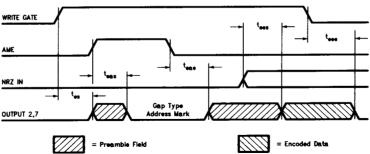

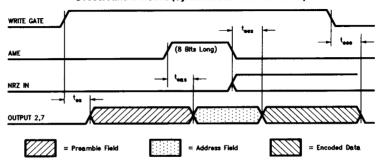

#### **Encoder Delay Time Parameter Definitions**

tes = Encoder Start time from WRT GATE

toes = Encoder Encyrption Start time from first NRZ IN bit

tes = Encoder Address Mark Start time from assertion of AME

t<sub>eee</sub> = Encoder Encryption End time from deassertion of WRT GATE

tess = Encoder Address Mark End time from deassertion of AME

#### ESDI/SMD/IBM Modes (Gap Type Address Marks)

TL/F/9386-15

#### ST506A and B Modes (Synchronous Address Marks)

TI /F/9386-16

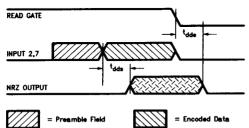

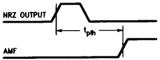

## **Decoder Serial Delay Times**

#### **Decoder Delay Time Parameter Definitions**

t<sub>dds</sub> = Decoder Decryption Start time from INPUT 2,7 data

t<sub>dde</sub> = Decoder Decryption End Time from deassertion of READ GATE

# AMF Assertion Delay Times by Mode

#### **ESDI/SMD Spec and Noise Tolerant Modes**

TL/F/9386-18

AMF deasserts on the FALLING edge of READ GATE.

= NRZ OUTPUT Data

TL/F/9386-17

This parameter defines the time delay for a specific INPUT 2,7 pattern to enter the device, and its resulting NRZ output to be present at the NRZ OUTPUT pin.

# AMF Assertion Delay Times by Mode (Continued)

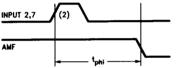

## DP8466 Compatible Modes (ESDI and IBM)

TL/F/9386-19

AMF deasserts on the SECOND INPUT 2.7 pulse after assertion

#### IBM and All ESDI/SMD Modes

TL/F/9386-20

AMF asserts on the FIRST INPUT 2,7 pulse after valid Address Mark

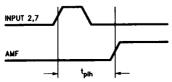

#### ST506 A and B Modes

TI /F/9386\_22

AMF asserts on the FIRST NRZ OUTPUT pulse after valid Address Mark

#### **ESDI/SMD Spec and Noise Tolerent Modes**

# ST506A Mode

AMF deasserts on the SECOND NRZ OUTPUT pulse after assertion.

#### ST506B Mode

TL/F/9386-23

AMF deasserts on the FALLING edge of READ GATE.

## **Input Minimum Pulse Widths**

#### REF CLK Min Pulse Widths

TL/F/9386-24

REF CLK requires minimum input positive and negative pulse width times; including both mpw+ and t<sub>mpw</sub>-

#### Input 2.7 Min Pulse Widths

INPUT 2,7 requires a minimum positive pulse width:  $t_{\text{mpwi}+}$ ; there is no minimum negative pulse width spec.

#### WRT CLK Minimum Pulse Widths

TL/F/9386-27

WRT CLK Input Minimum Positive and Negative Pulse Widths,  $t_{mpww\,+}$  and  $t_{mpww\,-}$

## **Output Propagation Delay Times**

## REF CLK to OUTPUT 2,7 Propagation Delay Time

TL/F/9386-25

REF CLK to OUTPUT 2,7 for  $t_{plh}$  and  $t_{phl}$ . Delay time is specified in both REF CLK cycles and ns of detay. WRT CLK edges coincident with REF CLK.

## NRZ OUTPUT vs RD/REF CLK T<sub>skew</sub>

T<sub>skw+</sub> defines data changing prior to the clock.

T<sub>skw</sub> defines data changing after the clock.

## **Input Setup and Hold Times**

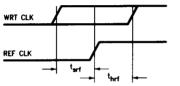

Setup and Hold Times (test and test)

from REF CLK to WRT CLK.

**REF CLK Setup and Hold Times**

TL/F/9386-29

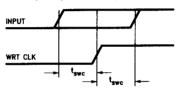

WRT CLK Setup and Hold Times

NRZ IN, AME, WRT GATE, READ GATE

TI /E/0286\_30

Setup and Hold Times ( $t_{\text{swc}}$  and  $t_{\text{swc}}$ ) for the four inputs: AME, WG, RG and NRZ IN.

## **Zero Phase Start Timing Sequence**

**ZPS Stop and Restart Delay Time**

TI /F/9386\_31

ZPS Delay Time measures the number of REF CLK cycles that pass from the time READ GATE is passed to the Synchronizer, until Zero Phase Start interrupts the VCO and stops RD/REF CLK. READ GATE is internally qualified in all SMD and ST506 modes to prevent the Synchronizer from attempting to lock when there is no data present (outside the Preamble Field). The basic t<sub>Zpsi</sub> and t<sub>Zpsi</sub> delay times are listed for the ESDI and IBM modes, while the SMD and ST506 modes have prequalifier adders. Delay times t<sub>Zpsi</sub> measures the time to interrupt the VCO, and t<sub>dzpsi</sub> measures the time to Restart the VCO.

| Address<br>Mode | RG<br>Qualified On: | t <sub>dzpsi</sub> (in REF CLK)<br>Cycles) | t <sub>dzpsr</sub>   |

|-----------------|---------------------|--------------------------------------------|----------------------|

| All ESDI Modes  | N/A                 | ≤3                                         | ≤ 4 after Falling RG |

| All SMD Modes   | AMF Assertion       | ≤3 + AMF Detection                         | ≤ 4 after Falling RG |

| All ST506 Modes | Preamble            | ≤3 + 12 Preamble Patterns                  | ≤ 4 after Falling RG |

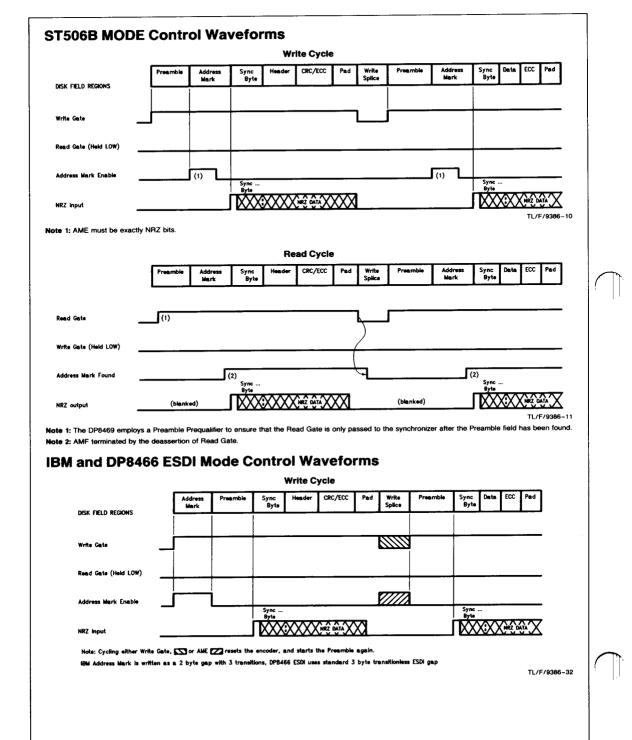

## **ESDI (Std and Nt) MODE Control Waveforms**

#### Write Cycle

Note: Cycling either Write Gate, or AME resets the encoder, and starts the Preamble again.

TL/F/9386-4

TL/F/9386-7

Note 1: Read Gate to the Synchronizer is internally qualified with AMF.

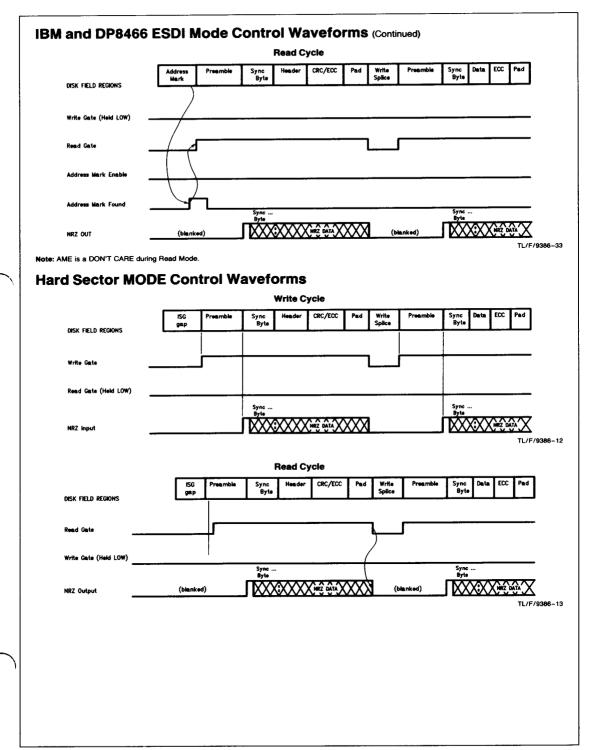

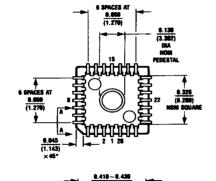

## Physical Dimensions inches (millimeters)

Lit. # 103078

Plastic Chip Carrier (V) Order Number DP8469V NS Package Number V28A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive P.O. Box 58090 Santa Clara, CA 95052-8090 Tel: (408) 721-5000 TWX: (910) 339-8240

GmbH Westendstrasse 193-195 D-8000 Munchen 21 West Germany Tal: (089) 5 70 95 01 Telex: 522772 NS Japan Ltd. Sanseido Bldg. 5F 4-15 Nishi Shinjuku Shinjuku-Ku, Tokyo 160, Japan Tel: 3-298-7001 FAX: 3-299-7000 National Semiconductor Hong Kong Like Southeest Asia Marketing Austin Tower, 4th Floor 22-28A Austin Avenue Tsimshatsui, Kowloon, H.K. Tel: 3-7231290, 3-7243845 Cable: NSSEAMRTG

National Semicondulores Do Brael Lida. Av. Brig. Faria Lima, 830 8 Ander 01452 Sao Paulo, SP. Braell Tel: (55/11) 212-5066 Telex: 391-1131931 NSBR BR National Semiconductor (Australia) PTY, Ltd. 21/3 High Street Bayswater, Victoria 3153 Australia Tel: (03) 729-8333 Telex: AA32096

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice

013339