# 4 Channel 5Gbps USB 3.0 Signal Repeater

## 89HP0504UB Data Sheet

#### **Device Overview**

The IDT 89HP0504UB (P0504UB) is a 5Gbps USB 3.0 Repeater device featuring IDT EyeBoost™ technology that compensates for cable and board trace attenuations and ISI jitter, thereby extending connection reach. The device is optimized for USB 3.0 high speed serial data streams and contains four data channels, each able to process 5Gbps transmission rates. Each channel consists of an input equalizer and amplifier, signal detection with glitch filter, as well as programmable output swing and de-emphasis. Allowing for application specific optimization, the P0504UB, with its configurable receiver and transmitter features, is ideal for USB 3.0 applications using a wide combination of cables and board trace materials.

All modes of active data transfer are designed with minimized power consumption. In full shutdown mode, the part consumes less than 40mW in worst case environmental conditions.

## **Applications**

- Notebook PCs

- Desktop PCs and workstations

- USB3 cable attached devices

- USB3 host adapter cards

- Active cables and port dongles

#### **Features**

- Compensates for cable and PCB trace attenuation and ISI jitter

- Programmable receiver equalization up to 24db

- Programmable transmitter swing and de-emphasis

- Recovers data stream even when the differential signal eve is completely closed due to trace attenuation and ISI jitter

- Full USB 3.0 protocol support

- Configurable via external pins

- ◆ Leading edge power minimization in active and shutdown modes

- ◆ No external bias resistors or reference clocks required

- Channel mux mode, demux mode, 1 to 2 channels multicast, and Z-switch function mode

- ◆ Available in a 36-pin QFN package (4.0 x 7.5mm with 0.5mm pitch)

#### **Benefits**

- Extends maximum cable length to over 8 meters and trace length over 48 inches in USB 3.0 applications

- Minimizes BER

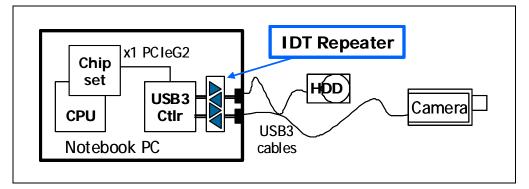

## **Typical Application**

Figure 1 IDT Repeaters in Notebook PCs

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc.

## **USB 3.0 Compliance**

The device was designed to provide end users with features needed to comply with USB 3.0 system application requirements:

- Receiver Detection Support, USB 3.0 LFPS Support

- Receiver supports high impedance I/O for power reduction

- Jitter, eye opening, and all other key AC and DC specifications.

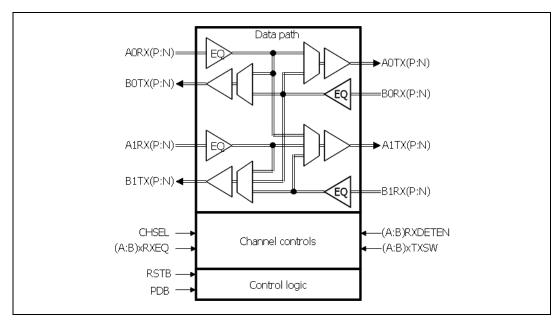

## **Block Diagram**

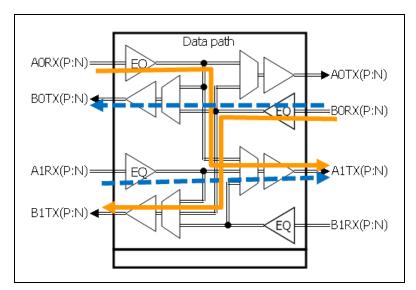

The P0504UB contains four high speed channels as shown in Figure 2. Each channel can be routed to different outputs. Depending on user configuration via mode selections, input traffic can be muxed or demuxed. Powerdown (PDB) and Receiver Detection Reset (RSTB) are provided for state and channel control.

Figure 2 Block Diagram

## **Table of Contents**

| Device Overview                       | 1   |

|---------------------------------------|-----|

| Applications                          | 1   |

| Features                              | 1   |

| Benefits                              | 1   |

| Typical Application                   | 1   |

| USB 3.0 Compliance                    | 2   |

| Block Diagram                         | 2   |

| Functional Description                | 5   |

| Power-Up                              | 6   |

| Power Sequencing                      | 6   |

| IDT EyeBoost™ Technology              | . 6 |

| Eye Diagram Parameters                | . 7 |

| Receiver Impedance                    | . 7 |

| Transmitter Impedance                 | 8   |

| USB 3.0 Receiver Detection Support    | 8   |

| Modes of Operation                    | . 9 |

| Channel Muxing                        |     |

| Electrical Specifications             | 14  |

| Absolute Maximum Ratings              | 14  |

| Recommended Operating Conditions      |     |

| Power Consumption                     |     |

| Package Thermal Considerations        |     |

| DC Specifications                     |     |

| AC Specifications                     |     |

| Pin Description                       | 21  |

| Package Pinout — 36-QFN Signal Pinout | 23  |

| Pin Diagram                           |     |

| QFN Package Dimension                 |     |

| Revision History                      |     |

| Ordering Information                  |     |

## **Functional Description**

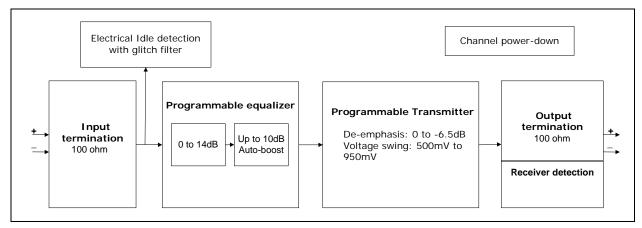

The P0502UB has 4 channels, each with the individually programmable features listed below. Figure 3 diagrams the channel and Table 1 summarizes key configuration options.

Figure 3 Channel Block Diagram with Channel Features

- Per-channel programmable features used at the Receive side.

- Input equalization with 3 levels: 2 to 14dB compensation for high frequency signal attenuation due to cables and board traces. Additionally, up to 10dB boost is added automatically by the equalizer for applications using long cables. The total equalization range is between 2dB and 24dB.

- Input high impedance control via channel enable: disabled (active mode) and hi-Z (power-down).

- Per-channel programmable features used at the Transmit side.

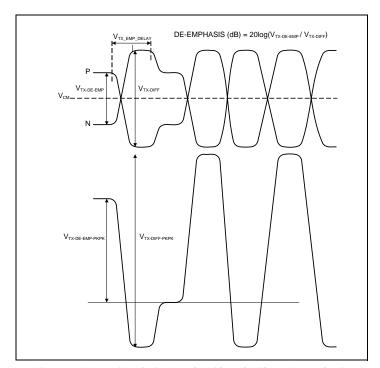

- Output de-emphasis with 3 levels: 0dB, -3.5dB, and -6.5dB. The de-emphasis boosts the magnitude of higher frequencies sent by the transmitter to compensate for high frequency losses travelling through output side cable or output side board traces. This ensures that the final received signal has a wider eye opening.

- Output differential swing with 3 levels: 0.5V, 0.8V, and 0.95V (peak-to-peak).

- Receiver detection: enable or disable. This function is activated following an RSTB pulse.

- With receiver detection enabled, if A0 and A1 channels do not detect at least one receiver, then the P0502UB on-chip Rx termination on A0 and A1 is set to hi-Z as shown in Table 2.

- With receiver detection enabled, if B0 and B1 channels do not detect at least one receiver, then the P0502UB on-chip Rx termination on B0 and B1 is set to hi-Z as shown in Table 2.

- Electrical idle detection: When the incoming differential peak-peak amplitude falls below 110mV, the device enters electrical idle mode and the corresponding transmitter stops toggling, maintains its common mode voltage level, and meets all electrical idle specifications described in the AC Specifications section of this data sheet.

In addition, the device contains global configuration of the data path:

- Transfer modes: direct connect, cross-connect, and multicast.

#### Power-Up

After the power supplies reach their minimum required levels, the P0502UB powers up by setting all input and output pins to known states:

- All the device's input configuration pins are set internally to VSS or VDD for 2-level pins and to VDD/2 for 3-level pins.

- High speed differential input and output pins depend on various conditions described below:

- High speed differential input and output pins are in high impedance if any of the following conditions is true:

- Powerdown is set (PDB pin = 0V) or

- No receiver termination was detected at TX outputs

In all other cases, high speed differential input and output pins are set to 50 ohms per pin, with 100 ohms differential impedance. Also refer to Table 4, Power Reducing Modes, Table 2, Receiver Impedance, and Table 3, Transmitter Impedance.

The power ramp up time for the P0502UB should be less than 1ms.

#### **Power Sequencing**

There are no power sequencing requirements for the P0502UB.

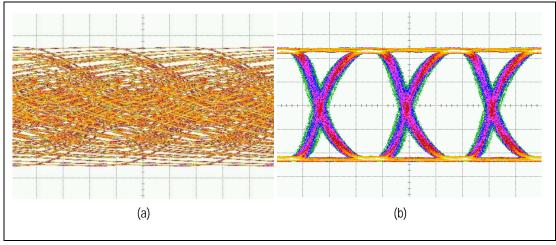

#### **IDT EyeBoost™ Technology**

IDT EyeBoost™ technology is a method of data stream recovery even when the differential signal eye is completely closed due to cable or trace attenuation and ISI jitter. With IDT EyeBoost™, the system designer can both recover the incoming data and retransmit it to target device with a maximized eye width and amplitude. An example of IDT EyeBoost™ technology usage in a system application and eye diagram results are shown in Figure 4. In this figure, the (a) diagram shows incoming differential signal (closed eye) after 62 inch FR4 connection from signal source and the (b) diagram shows differential signal at the output of repeater maximized eye opening with IDT EyeBoost™ technology.

Figure 4 Eye Diagram

## **Eye Diagram Parameters**

| Feature                                                                | Feature Type          | Parameter Names for<br>Programming via Pins                                                                           |

|------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------|

| Input equalization                                                     | Main eye optimization | A0RXEQ, A1RXEQ, B0RXEQ, B1RXEQ<br>Range: 0dB to 14dB (plus additional auto-<br>boost up to 10dB for long connections) |

| Output differential signal swing (peak-to-peak) and output de-emphasis | Main eye optimization | A0TXSW, A1TXSW, B0TXSW, B1TXSW<br>Range: 0.5V to 0.95V for swing<br>Range: 0 to -6.5dB for de-emphasis                |

Table 1 Quick Reference: Parameters Used for Eye Optimization

#### **Receiver Impedance**

The table below shows how the receiver impedance changes based on input and output pin states.

| Mode                  |     | Control Input | s    | Rx           | Description                                                                                  |

|-----------------------|-----|---------------|------|--------------|----------------------------------------------------------------------------------------------|

| Wode                  | PDB | [A,B]RXDETEN  | RSTB | Terminations | Description                                                                                  |

| Full IC<br>Power-down | 0   | Х             | Х    | Hi-Z         | Receiver terminations placed in Hi-Z.                                                        |

| Channel Disabled      | 1   | 1             | 0    | Hi-Z         | Receiver detect in reset.<br>Receiver terminations placed in Hi-Z.                           |

| Channel<br>Enabled    | 1   | 0             | 1    | 50Ω          | Receiver detect disabled. Receiver terminations set to $50\Omega$ .                          |

| Channel Disabled      | 1   | 1             | 1    | Hi-Z         | Receiver detect enabled. No far-end receiver detected. Receiver terminations placed in Hi-Z. |

| Channel<br>Enabled    | 1   | 1             | 1    | 50Ω          | Receiver detect enabled. Valid receiver detected. Receiver terminations set to $50\Omega$ .  |

Table 2 Receiver Impedance

#### **Transmitter Impedance**

The table below shows how the transmitter impedance changes based on input and output pin states.

| Mode                               | Control Ir   | nputs | Tx Termina- | Description                                                                                                                                      |

|------------------------------------|--------------|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| iviode                             | [A,B]RXDETEN | RSTB  | tions       | Description                                                                                                                                      |

| Full IC<br>Power-down              | Х            | Х     | 1kΩ         | Receiver terminations placed in Hi-Z.                                                                                                            |

| Channel<br>Enabled                 | 0            | 1     | 50Ω         | Rx signal not detected.<br>Receiver detect disabled.<br>Receiver terminations set to Hi-Z.                                                       |

| Channel<br>Enabled                 | 0            | 1     | 50Ω         | Rx signal detected. Receiver detect disabled. Receiver terminations set to $50\Omega$ .                                                          |

| Channel<br>Disabled                | 1            | 0     | 1kΩ         | Receiver detect reset.<br>Receiver terminations placed in<br>Hi-Z.                                                                               |

| Channel<br>Disabled                | 1            | 1     | 1kΩ         | TX output pulled up to VDD. Receiver detect enabled. No receiver detected. Receiver terminations placed in Hi-Z.                                 |

| Channel<br>Enabled but<br>inactive | 1            | 1     | 50Ω         | TX output is squelched. A valid receiver was detected. Receiver terminations set to $50\Omega$ . Output common-mode is held at its active value. |

| Channel<br>Enabled and<br>active   | 1            | 1     | 50Ω         | TX output is active. A valid receiver was detected. Receiver terminations set to $50\Omega$ .                                                    |

Table 3 Transmitter Impedance

#### **USB 3.0 Receiver Detection Support**

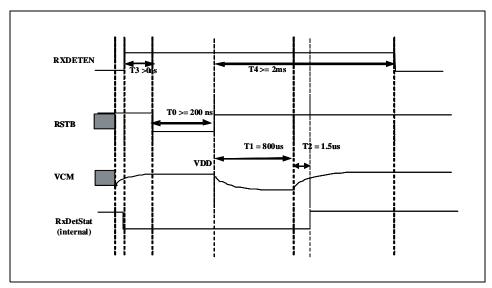

The P0502UB transmitter fully supports USB 3.0 Receiver Detection requirements. Receiver detection is enabled for channels A0 and A1 by asserting pin ARXDETEN and for channels B0 and B1 by asserting pin BRXDETEN. For receiver detection to occur, a low pulse (minimum 200ns) must be applied at pin RSTB. The rising edge of the RSTB signal starts the receiver detection procedure. Neither ARXDETEN nor BRXDETEN can be toggled during the receiver detection procedure, i.e., they must be kept high for at least 200ns before the RSTB rising edge and they cannot go to low sooner than 2ms from the time the RSTB goes high.

Figure 5 Receiver Detection Timing

#### **Modes of Operation**

The device supports several data transfer modes, electrical idle mode, and several power reducing modes.

#### **Electrical Idle Mode**

In electrical idle mode, the transmitter stops toggling and maintains its common-mode voltage level. The device enters electrical idle mode when the envelope of the incoming signal on a given channel has fallen below a programmable threshold level.

#### **Power Reducing Modes**

The Repeater supports five power-down states and one active state as shown in Table 4. The user can choose between full chip power-down, channel based power-down, and electrical idle modes. Power reducing modes can be selected via PDB and RSTB.

|                                                                          | -                         | ed Signal<br>lues           |                                                                                                                                                                                 |

|--------------------------------------------------------------------------|---------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power<br>Reducing Mode                                                   | Power-<br>Down<br>Control | Receiver<br>Detect<br>Start | State Description                                                                                                                                                               |

|                                                                          | PDB                       | RSTB                        |                                                                                                                                                                                 |

| Full IC power-down                                                       | 0                         | Х                           | All channels are powered-down Receiver detect reset Rx termination is set to Hi-Z Tx termination is set to $1 \text{k}\Omega$ Tx common-mode is at VDD                          |

| Individual channel power-down                                            | Х                         | Х                           | Receiver detect reset Rx termination is set to Hi-Z Tx termination is set to $1k\Omega$ Tx common-mode is at VDD                                                                |

| Receiver Detect reset                                                    | 1                         | 0                           | Receiver detect state machine Receiver terminations placed in Hi-Z Tx termination is set to $1k\Omega$ Tx common-mode is at VDD                                                 |

| Channel enabled but inactive (electrical idle). Rx and Tx set to hi-Z    | 1                         | 1                           | Tx output is squelched No receiver was Detected Receiver terminations placed in Hi-Z Tx termination is set to $1k\Omega$ Tx common-mode is at VDD                               |

| Channel enabled but inactive (electrical idle). Rx and Tx set to 50 Ohms | 1                         | 1                           | Tx output is squelched A valid receiver was detected Receiver terminations set to $50\Omega$ Output common-mode is held at its active value Tx termination is set to $50\Omega$ |

| Channel enabled and active. No power-down                                | 1                         | 1                           | Tx output is active A valid receiver was detected Receiver terminations set to $50\Omega$ Transmitter terminations set to $50\Omega$                                            |

Table 4 Power Reducing Modes

#### **Channel Muxing**

The P0502UB repeater permits a variety of muxing, demuxing, and switching configurations. These configurations require the selection of specific pins for input and output ports. In the following sections, each configuration is described in terms of pin connectivity to external upstream and downstream devices. The configurations shown are those often used in system designs:

- Uni-directional 2:1 Mux (1 or 2 instances)

- Uni-directional 1:2 De-Mux (1 or 2 instances)

- Bi-directional 2:1 Mux/De-Mux

- Bi-directional Z-function (also called Partial Cross Function)

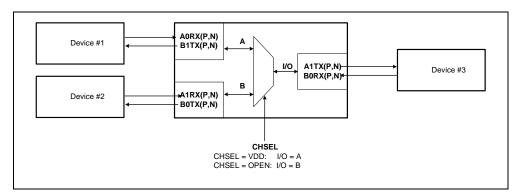

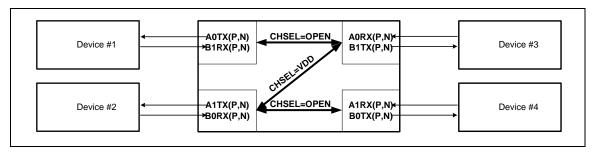

The P0502UB supports channel muxing in both upstream and downstream channel directions via the CHSEL pin, as shown below. Figure 6 shows the channel/reference muxing modes and Table 5 shows how CHSEL (Channel transfer selection) pin allows for various modes of data transfers: Multicast mode, Direct-connect, and Cross-connect. Both Direct-connect, and Cross-connect modes are used to build uni-directional and bi-directional 2:1 mux and Z-switch functions.

Figure 6 Diagram of Channel/Reference Muxing Modes

| Input Pins                             |           |           |           | Output Pins |           |           |           |           |

|----------------------------------------|-----------|-----------|-----------|-------------|-----------|-----------|-----------|-----------|

| CHSEL                                  | AORX[P,N] | A1RX[P,N] | BORX[P,N] | B1RX[P,N]   | AOTX[P,N] | A1TX[P,N] | BOTX[P,N] | B1TX[P,N] |

| CHSEL=VSS<br>(Multicast Mode)          | A0 DATA   | Х         | B0 DATA   | Х           | A0 DATA   | A0 DATA   | B0 DATA   | B0 DATA   |

| CHSEL=Open<br>(Direct-Connect<br>Mode) | A0 DATA   | A1 DATA   | B0 DATA   | B1 DATA     | A0 DATA   | A1 DATA   | B0 DATA   | B1 DATA   |

| CHSEL=VDD<br>(Cross-Connect<br>Mode)   | A0 DATA   | Х         | B0 DATA   | Х           | Squelched | A0 DATA   | Squelched | B0 DATA   |

Table 5 Description of Channel Muxing/De-Muxing Functionality

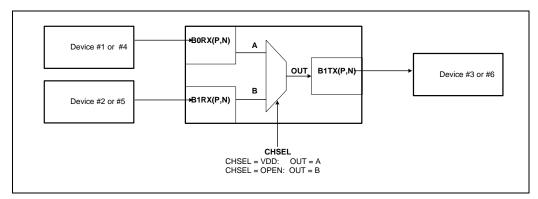

#### Uni-directional 2:1 Mux or Two Instances of Unidirectional 2:1 Mux

This function can be achieved by using the CHSEL pin as a mux control signal. CHSEL should be set to either VDD or OPEN. The ports should be configured as shown in Figure 7.

Figure 7 Implementation of Unidirectional 2:1 Mux

As an alternative, different chip channels can also be selected as shown in Figure 8. This solution can be combined with the previous one to obtain two instances of Uni-directional 2:1 Mux.

Figure 8 Implementation of Second Instance of Unidirectional 2:1 Mux

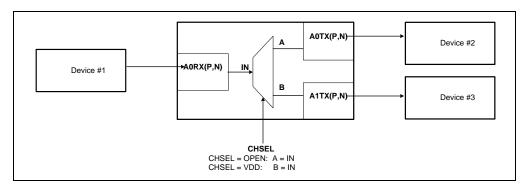

#### Uni-directional 1:2 De-Mux or Two Instances of Unidirectional 1:2 De-Mux

This function can be achieved by using CHSEL pin as a de-mux control signal. CHSEL should be set to either VDD or OPEN. The ports should be configured as shown in Figure 9.

Figure 9 Implementation of Unidirectional 1:2 De-Mux

As an alternative, different chip channels can also be selected as shown in Figure 10. This solution can be combined with the previous one to obtain two instances of Uni-directional 1:2 De-Mux.

Figure 10 Implementation of Second Instance of Unidirectional 1:2 De-Mux

#### Bi-directional 2:1 Mux/De-Mux

The bi-directional Mux and De-Mux function can also be achieved by using the CHSEL pin as a mux control signal. CHSEL should be set to either VDD or OPEN. The ports should be configured as shown in Figure 11.

Figure 11 Implementation of Bi--directional 2:1 Mux/De-Mux

#### **Bi-directional Z-function (also called Partial Cross Function)**

This function can also be achieved by using the CHSEL pin as a flow control signal. CHSEL should be set to either VDD or OPEN. The ports should be configured as shown in Figure 12.

Figure 12 Implementation of Z-function

## **Electrical Specifications**

#### **Absolute Maximum Ratings**

Note: All voltage values, except differential voltages, are measured with respect to ground pins.

| Parameter                                                     | Value             | Unit |

|---------------------------------------------------------------|-------------------|------|

| Supply voltage range VDD                                      | -0.5 to 1.35      | V    |

| Voltage range Differential I/O                                | -0.5 to VDD +0.5  | V    |

| Control I/O                                                   | -0.5 to VDD + 0.5 | V    |

| ESD requirements: Electrostatic discharge<br>Human body model | ±2000             | V    |

| ESD requirements: Charged-Device Model (CDM)                  | ±500              | V    |

| ESD requirements: Machine model                               | ±125              | V    |

| Storage ambient temperature                                   | -55 to 150        | °C   |

Table 6 Absolute Maximum Ratings

Warning: Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **Recommended Operating Conditions**

| Parameter                | Notes                                                  | Min  | Typical | Max  | Unit |

|--------------------------|--------------------------------------------------------|------|---------|------|------|

| Power Supply Pin         |                                                        |      |         |      |      |

| VDD                      | 1.2V DC analog supply voltage (specified at bump pins) | 1.14 | 1.2     | 1.26 | V    |

| Temperature Requirements |                                                        |      |         |      |      |

| TA                       | Ambient operating temperature - Commercial             | 0    | _       | 70   | °C   |

|                          | Ambient operating temperature - Industrial             | -40  | _       | 85   | °C   |

| TJUNCTION                | Junction operating temperature                         | 0    | _       | 125  | °C   |

**Table 7 Operating Conditions**

#### **Power Consumption**

Table 8 below lists power consumption values under typical and maximum operating conditions.

| Parameter         | Notes                          | Min | Typical | Max | Unit |

|-------------------|--------------------------------|-----|---------|-----|------|

| Active Mode       |                                | •   | •       |     | •    |

| I <sub>VDD</sub>  | Current into VDD supply        | _   | 330     | 500 | mA   |

| P <sub>D</sub>    | Full chip power <sup>1</sup>   |     | 400     | 600 | mW   |

| P <sub>D-ch</sub> | Power per channel <sup>1</sup> |     | 100     | 150 | mW   |

| Standby Mode      | Full chip standby              |     | 30      | 40  | mW   |

**Table 8 Power Consumption**

#### Package Thermal Considerations

The data in Table 9 below contains information that is relevant to the thermal performance of the 36-pin QFN package.

| Parameter              | Description                                       | Value                                    | Conditions                            | Units |

|------------------------|---------------------------------------------------|------------------------------------------|---------------------------------------|-------|

| T <sub>J(max)</sub>    | Junction Temperature                              | 125                                      | Maximum                               | °C    |

| T <sub>A(max)</sub>    | Ambient Temperature                               | 70 Maximum for commercial-rated products |                                       | оС    |

|                        |                                                   | 85                                       | Maximum for industrial-rated products | оС    |

|                        |                                                   | 41.8                                     | Zero air flow                         | °C/W  |

|                        | Effective Thermal Resistance, Junction-to-Ambient | 36.1                                     | 1 m/S air flow                        | °C/W  |

| 0                      |                                                   | 35.3                                     | 2 m/S air flow                        | °C/W  |

| $\theta$ JA(effective) |                                                   | 34.3                                     | 3 m/S air flow                        | °C/W  |

|                        |                                                   | 33.7                                     | 4 m/S air flow                        | °C/W  |

|                        |                                                   | 33.2                                     | 5 m/S air flow                        | °C/W  |

| $\theta_{JB}$          | Thermal Resistance, Junction-to-Board             | 14.5                                     | NA                                    | °C/W  |

| $\theta_{JC}$          | Thermal Resistance, Junction-to-Case              | 37.2                                     | NA                                    | °C/W  |

Table 9 Thermal Specifications for P0502UB, 4.0x7.5mm 36-QFN Package

**Note**: It is important for the reliability of this device in any user environment that the junction temperature not exceed the  $T_{J(max)}$  value specified in Table 9. Consequently, the effective junction to ambient thermal resistance ( $\theta_{JA}$ ) for the worst case scenario must be maintained below the value determined by the formula:

$$\theta_{JA} = (T_{J(max)} - T_{A(max)})/P$$

Given that the values of  $T_{J(max)}$ ,  $T_{A(max)}$ , and P are known, the value of desired  $\theta_{JA}$  becomes a known entity to the system designer. How to achieve the desired  $\theta_{JA}$  is left up to the board or system designer, but in general, it can be achieved by adding the effects of  $\theta_{JC}$  (value provided in Table 9), thermal resistance of the chosen adhesive ( $\theta_{CS}$ ), that of the heat sink ( $\theta_{SA}$ ), amount of airflow, and properties of the circuit board (number of layers and size of the board).

Maximum power under all conditions. Power is reduced by selecting smaller de-emphasis settings (closer or equal to 0dB).

## **DC Specifications**

| Parameter               | Description                                                         | Min           | Тур | Max          | Unit  |

|-------------------------|---------------------------------------------------------------------|---------------|-----|--------------|-------|

| V <sub>IL</sub>         | Digital Input Signal Voltage Low Level <sup>1</sup>                 | -0.3          | _   | 0.25*VDD-0.1 | V     |

| V <sub>IM</sub>         | Digital Input Signal Voltage Mid Level <sup>2</sup>                 | 0.25*VDD+ 0.1 |     | 0.75*VDD-0.1 | V     |

| V <sub>IH</sub>         | Digital Input Signal Voltage High Level <sup>1</sup>                | 0.75*VDD+ 0.1 |     | VDD+ 0.3     | V     |

| V <sub>HYS</sub>        | Hysteresis of Schmitt Trigger Input                                 | 0.1           |     | _            | V     |

| I <sub>IL</sub>         | Input Current <sup>3</sup>                                          | _             |     | 100          | μΑ    |

| I <sub>IH</sub>         | Input Current <sup>4</sup>                                          | _             |     | 100          | μΑ    |

| I <sub>IL1</sub>        | Input Current <sup>2</sup>                                          | _             |     | 180          | μΑ    |

| I <sub>IH1</sub>        | Input Current <sup>2</sup>                                          | _             |     | 180          | μA    |

| R <sub>WEAK_PD_2L</sub> | Internal weak pull-down resistor at 2-level input pads <sup>4</sup> | 11            |     | _            | K ohm |

| R <sub>WEAK_PU_2L</sub> | Internal weak pull-up resistor at 2-level input pads <sup>3</sup>   | 11            |     | _            | K ohm |

| R <sub>WEAK_PD_3L</sub> | Internal weak pull-down resistor at all 3-level input pads          | 6.3           |     | _            | K ohm |

| R <sub>WEAK_PU_3L</sub> | Internal weak pull-up resistor at all 3-level input pads            | 6.3           |     | _            | K ohm |

Table 10 DC Specification

## **AC Specifications**

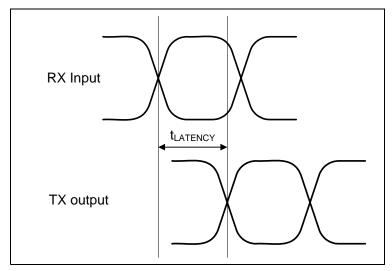

#### **Latency Specification**

| Parameter | Description                               | Min | Typical | Max | Unit |

|-----------|-------------------------------------------|-----|---------|-----|------|

| Latency   | Input to output signal propagation device | 1   | 300     |     | ps   |

Table 11 Latency Specification

<sup>1.</sup> Applies to all input pins.

<sup>&</sup>lt;sup>2.</sup> Applies to all 3-level input pins.

<sup>&</sup>lt;sup>3.</sup> Applies only to 2-level input pins with default values set to VDD in the Pin Description table (Table 14).

<sup>&</sup>lt;sup>4.</sup> Applies only to 2-level input pins with default values set to VSS in the Pin Description table (Table 14).

## **Receiver Specifications**

| Parameter                                     | Description                                                                                     | Min   | Typical | Max | Unit |  |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------|-------|---------|-----|------|--|

| Receiver Input Jitter Specification           |                                                                                                 |       |         |     |      |  |

| T <sub>RX-DJ-DD</sub>                         | Maximum RX inherent deterministic timing error                                                  |       |         | >1  | UI   |  |

| T <sub>RX-TJ</sub>                            | Receive Input Signal Total Jitter                                                               | _     | _       | >1  | UI   |  |

| T <sub>RX-EYE</sub>                           | Receiver eye time opening (can recover from closed eye due to trace attenuation and ISI jitter) | 0     | _       | _   | UI   |  |

| Receiver Input Eye                            | Specification                                                                                   |       | 1       |     | •    |  |

| V <sub>RX-DIFF-PP</sub>                       | Receiver Differential Peak-Peak Voltage <sup>1</sup>                                            | 0     | _       | _   | mV   |  |

| V <sub>RX-CM-DC</sub>                         | Receiver DC Common Mode Voltage                                                                 | _     | 0       | _   | mV   |  |

| V <sub>RX-CM-AC-P</sub>                       | Receiver AC Common Mode Voltage                                                                 | _     | _       | 150 | mV   |  |

| Receiver Return Lo                            | oss                                                                                             |       | 1       |     | •    |  |

| C <sub>RX-CAPACITANCE</sub>                   | Receiver Input Capacitance for Return Loss                                                      | _     | _       | 1.1 | pF   |  |

| Receiver DC Imped                             | lance                                                                                           |       |         |     | •    |  |

| R <sub>RX-DC</sub>                            | Receive Impedance (DC, common mode)                                                             | 40    | 50      | 60  | Ohm  |  |

| Z <sub>RX-DIFF-DC</sub>                       | DC differential impedance                                                                       | 80    | 100     | 120 | Ohm  |  |

| Z <sub>RX-HIGH-IMP-DC-POS</sub>               | DC Input Common-Mode Receive High Impedance for Input Voltage >0 during reset or power-down     | 50k — |         | _   | Ohm  |  |

| Z <sub>DIFF-HIZ-POS</sub>                     | Differential Receive High Impedance for Input Voltage from 0V to 200mV                          | 200k  | _       | _   | Ohm  |  |

| Receiver Electrical                           | Idle                                                                                            |       | -1      |     | L    |  |

| V <sub>RX-CM-DC-ACTIVE-IDLE-</sub><br>DELTA-P | RX AC Common Mode Voltage during the U1 to U0 transition                                        | _     | _       | 200 | mV   |  |

| T <sub>SIGDET-ATTACK</sub>                    | Signal Detect Valid Signal Attack Time (Turn-on time)                                           | _     | _       | 15  | ns   |  |

| T <sub>SIGDET-DECAY</sub>                     | Signal Detect Valid Signal Decay Time (Turn-off time)                                           | _     | _       | 15  | ns   |  |

| T <sub>SIGDET-ATT-DECAY-MIS</sub>             | Signal Detect Attack / Decay Time Mismatch                                                      | _     | _       | 5   | ns   |  |

Table 12 Receiver Electrical Specifications

## **Transmitter Specifications**

| Parameter                                   | Description                                                              | Min        | Typical    | Max         | Unit |

|---------------------------------------------|--------------------------------------------------------------------------|------------|------------|-------------|------|

| Output Eye and Common Voltage Specification |                                                                          |            |            |             |      |

| V <sub>TX-DIFF-PP</sub>                     | Differential Transmitter swing [A:B]xTXSW=1 [A:B]xTXSW=open              | 800<br>700 | 950<br>800 | 1100<br>950 | mV   |

| V <sub>TX-DIFF-PP-LOW</sub>                 | Low power differential p-p Transmitter swing [A:B]xTXSW=0                | 400        | 500        | 650         | mV   |

| D <sub>TX-DEEMP</sub>                       | Output De-emphasis. Defined as $20log(V_{TX-DE-EMP} / V_{TX-DIFF})$ [dB] | -6.5       | _          | 0           | dB   |

Table 13 Transmitter Electrical Requirements (Part 1 of 2)

$<sup>^{\</sup>rm 1.}$  The minimum value of 0 mV represents the case when Eye is completely closed.

Table 13 Transmitter Electrical Requirements (Part 2 of 2)

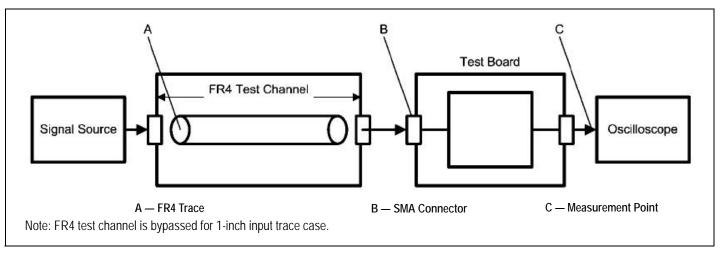

<sup>1.</sup> Refer to Figure 13.

Figure 13 Residual Jitter Characterization Test Setup

Figure 14 Transmitter Swing Levels With and Without De-emphasis

**Note:**  $V_{TX-DIFF-PKPK}$  Peak to Peak voltage is twice as large as voltage difference between P pins and N pins of differential pairs. For example, if the P pin swings from 0.8V to 1.4V while the N pin swings from 1.4V to 0.8V, then: $V_{TX-DIFF-PKPK} = 2*(1.4-0.8)=1.2V$ .

Figure 15 Definition of Latency Timing

## **Pin Description**

**Note:** Unused pins can be left floating.

| Pin Name                                                                                 | Pin #                | Description                                                                                                                                                                                                                                                                                                                                             | Input/<br>Output/<br>Power<br>2 or 3<br>Level |

|------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Power                                                                                    | •                    |                                                                                                                                                                                                                                                                                                                                                         |                                               |

| VDD                                                                                      | 5, 8, 11, 21, 24, 27 | 1.2V (typ) Power supply for Repeater high speed channels and internal logic. Each VDD pin should be connected to the VDD plane through a low inductance path, with a via located as close as possible to the landing pad of VDD pins. It is recommended to have a 0.01 µF or 0.1 µF, X7R, size-0402 bypass capacitor from each VDD pin to ground plane. | Power                                         |

| VSS                                                                                      | Center Pad           | VSS reference. VSS should be connected to the ground plane through a low inductance path, with a via located as close as possible to the landing pad.                                                                                                                                                                                                   | Power                                         |

| Data Signals                                                                             |                      |                                                                                                                                                                                                                                                                                                                                                         |                                               |

| AORXN<br>AORXP                                                                           | 4 3                  | Channel A0 Receive Data Ports                                                                                                                                                                                                                                                                                                                           | Input                                         |

| AOTXN<br>AOTXP                                                                           | 28<br>290            | Channel A0 Transmit Data Ports                                                                                                                                                                                                                                                                                                                          | Output                                        |

| BORXN<br>BORXP                                                                           | 25<br>26             | Channel B0 Receive Data Ports                                                                                                                                                                                                                                                                                                                           | Input                                         |

| BOTXN<br>BOTXP                                                                           | 7<br>6               | Channel B0 Transmit Data Ports                                                                                                                                                                                                                                                                                                                          | Output                                        |

| A1RXN<br>A1RXP                                                                           | 10<br>9              | Channel A1 Receive Data Ports                                                                                                                                                                                                                                                                                                                           | Input                                         |

| A1TXN<br>A1TXP                                                                           | 22<br>23             | Channel A1 Transmit Data Ports                                                                                                                                                                                                                                                                                                                          | Output                                        |

| B1RXN<br>B1RXP                                                                           | 19<br>20             | Channel B1 Receive Data Ports                                                                                                                                                                                                                                                                                                                           | Input                                         |

| B1TXN<br>B1TXP                                                                           | 13<br>12             | Channel B1 Transmit Data Ports                                                                                                                                                                                                                                                                                                                          | Output                                        |

| Channel Control and                                                                      | Status               |                                                                                                                                                                                                                                                                                                                                                         |                                               |

| A0RXEQ (Channel A0)<br>B0RXEQ (Channel B0)<br>A1RXEQ (Channel A1)<br>B1RXEQ (Channel B1) | 15<br>17<br>36<br>33 | Receiver Equalization. Programming of channel A0 via pins is shown below. To program other channels, use pins for those channels.  A0RXEQ Setting VSS 2dB Open 6dB (Default) VDD 14dB                                                                                                                                                                   | Input - 3<br>level                            |

Table 14 Pin Description (Part 1 of 2)

| Pin Name                                                                        | Pin #               | Description                                                                                                                                                                                                                                                                                                                             | Input/<br>Output/<br>Power<br>2 or 3<br>Level |

|---------------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| A0TXSW (Channel A0) B0TXSW (Channel B0) A1TXSW (Channel A1) B1TXSW (Channel B1) | 1<br>32<br>14<br>18 | Transmitter Voltage Swing (pk-pk). Programming of channel A0 via pins is shown below. To program other channels, use pins for those channels.  A0TXSW Swing De-Emphasis VSS 0.5Vdiff-pkpk 0dB Open 0.8Vdiff-pkpk (Default) -3.5dB VDD 0.95Vdiff-pkpk -6.5dB                                                                             | Input - 3<br>level                            |

| Other Control Signals                                                           | 0.5                 | Dawe daw Fashia                                                                                                                                                                                                                                                                                                                         | In and O                                      |

| PDB                                                                             | 35                  | Power-down Enable.  PDB Setting  VSS Powerdown IC. RX terminations are in Hi-Z,  TX is disabled  VDD Normal operation (internal 11K ohm minimum pull-up applied)                                                                                                                                                                        | Input - 2<br>level                            |

| RSTB                                                                            | 34                  | Receiver Detection Start.  RSTB Setting  VSS Resets Channel Receiver Detection State Machine  VDD Normal operation (internal 11K ohm minimum pull-up applied)  Note: the rising edge of RSTB will start the receiver detection.                                                                                                         | Input - 2<br>level                            |

| ARXDETEN<br>BRXDETEN                                                            | 16<br>31            | Output Channel Receiver Detect Enable Input. Programming of channel ARXDETEN via pins is shown below. To program BRXDETEN, use pins for that channel.  ARXDETEN Setting VSS Receiver Detection is disabled for A0 and A1 channels (internal 11K ohm minimum pulldown applied)  VDD Receiver Detection is enabled for A0 and A1 channels | Input - 2<br>level                            |

| CHSEL                                                                           | 30                  | Channel Transfer Mode.  CHSEL Setting  VSS Multi-cast mode  Open Direct-connect mode (default)  VDD Cross-connect mode                                                                                                                                                                                                                  | Input - 3<br>level                            |

| RSVD                                                                            | 2                   | Reserved. Do not connect.                                                                                                                                                                                                                                                                                                               |                                               |

Table 14 Pin Description (Part 2 of 2)

## Package Pinout — 36-QFN Signal Pinout

Table 15 lists the pin numbers and signal names for the P0502UB device.

| Function | Pin | Function | Pin | Function | Pin |

|----------|-----|----------|-----|----------|-----|

| AORXEQ   | 15  | ARXDETEN | 16  | B1TXSW   | 18  |

| AORXN    | 4   | BORXEQ   | 17  | BRXDETEN | 31  |

| AORXP    | 3   | BORXN    | 25  | CHSEL    | 30  |

| AOTXN    | 28  | B0RXP    | 26  | PDB      | 35  |

| AOTXP    | 29  | BOTXN    | 7   | RSTB     | 34  |

| AOTXSW   | 1   | BOTXP    | 6   | RSVD     | 2   |

| A1RXEQ   | 36  | BOTXSW   | 32  | VDD      | 5   |

| A1RXN    | 10  | B1RXEQ   | 33  | VDD      | 8   |

| A1RXP    | 9   | B1RXN    | 19  | VDD      | 11  |

| A1TXN    | 22  | B1RXP    | 20  | VDD      | 21  |

| A1TXP    | 23  | B1TXN    | 13  | VDD      | 24  |

| A1TXSW   | 14  | B1TXP    | 12  | VDD      | 27  |

Table 15 Alphabetical Pin List

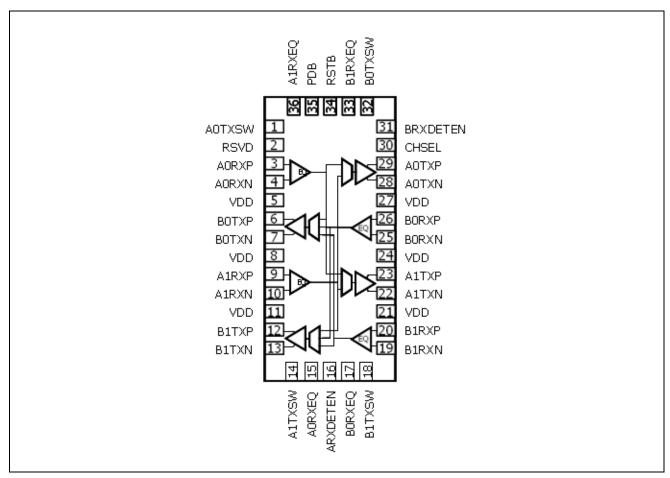

## Pin Diagram

The following figure lists the pin numbers and the signal names for the 36-QFN package.

Figure 16 Pin Diagram — Top View

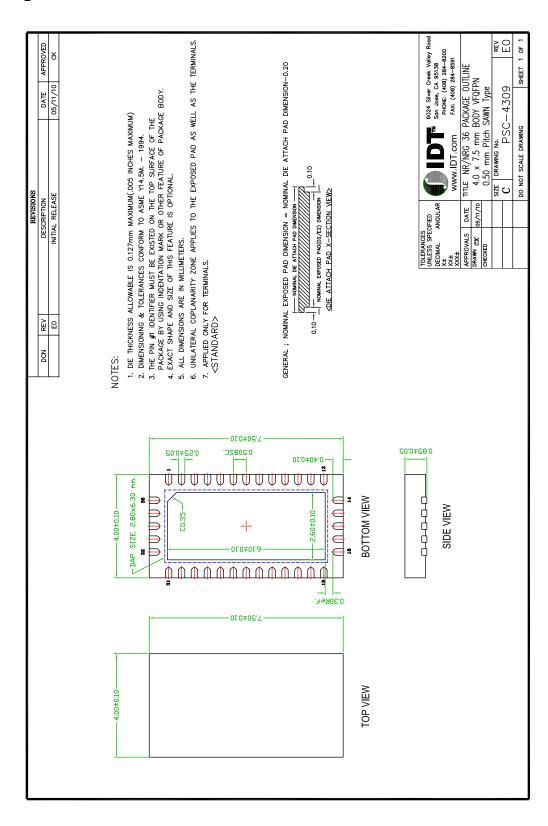

## **QFN Package Dimension**

## **Revision History**

November 2, 2010: Initial publication of final datasheet.

February 8, 2011: Removed black packaging options from Order page.

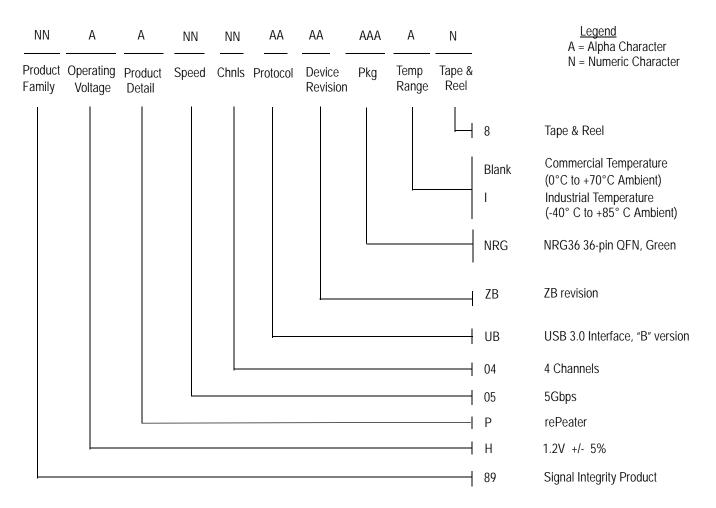

## **Ordering Information**

#### Valid Combinations

89HP0502UBZBNRG / 89HP0502UBZBNRG8 36-pin Green QFN package, Commercial Temperature 89HP0502UBZBNRGI / 89HP0502UBZBNRGI8 36-pin Green QFN package, Industrial Temperature

#### CORPORATE HEADQUARTERS

6024 Silver Creek Valley Road San Jose, CA 95138

#### for SALES:

800-345-7015 or 408-284-8200 fax: 408-284-2775

www.idt.com

for Tech Support:

email: <a href="mailto:siphelp@idt.com">siphelp@idt.com</a> phone: 408-284-8208

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDT's sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitiented to the suitiented to, the suitiented to, the suitiented to the suitiented to, the suitiented to, the suitiented to, the suitiented to the suitiented to the suitiented to.

IDT's products are not intended for use in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are registered trademarks of IDT. Other trademarks and service marks used herein, including protected names, logos and designs, are the property of IDT or their respective third party owners. Copyright 2011. All rights reserved.