# INCLER LXT310 T1 CSU/ISDN PRI Transceiver

#### Datasheet

The LXT310 is the first fully integrated transceiver for T1 CSU and ISDN Primary Rate Interface (ISDN PRI) applications at 1.544 Mbps. This transceiver operates over 6,000 feet of 22 AWG twisted-pair cable without any external components. To compensate for shorter lines, 7.5 dB, 15 dB, and 22.5 dB frequency-dependent transmit Line Build-Outs (LBOs) are provided.

The device offers selectable B8ZS encoding/decoding, and unipolar or bipolar data I/O. The LXT310 also provides jitter attenuation in either the transmit or receive direction starting at 6 Hz, and incorporates a serial interface (SIO) for microprocessor control.

The LXT310 offers a variety of diagnostic features including loopbacks and loss of signal monitoring. It uses an advanced double-poly, double-metal CMOS process and requires only a single 5-volt power supply.

# **Applications**

- ISDN Primary Rate Interface (PRI) (ANSI T1.408)

- CSU Interface to T1 Service (Pub 62411)

- DS1 Metallic Interface (ANSI T1.403)

- T1 LAN bridge

### **Product Features**

- Fully integrated transceiver comprising: on-chip equalizer; timing recovery/control; data processor; receiver; and transmitter with Line Build-Out and digital control

- Meets or exceeds ANSI and ITU specifications including T1.403, T1.408, and AT&T Pub 62411

- Selectable Receiver Sensitivity. Fully restores the received signal after transmission through a cable with attenuation of either 0 to 26 dB, or 0 to 36 dB @ 772 kHz

- Selectable Unipolar or Bipolar data I/O

- Selectable B8ZS encoding/decoding

- CPU to CPU Channel Extenders

- Digital Loop Carrier Subscriber Carrier Systems

- T1 Mux

- Channel Banks

- Line attenuation indication output

- 138 UI jitter tolerance at 1 Hz

- Output short circuit current limit protection

- On-line idle mode for redundant systems

- 7.5 dB, 15 dB, and 22.5 dB transmit LBOs

- Local, remote and inband network loopback functions

- Receive monitor with Loss of Signal (LOS) output

- Jitter attenuation starting at 6 Hz, switchable to transmit or receive path

- Microprocessor controllable

# intel

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The LXT310 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Third-party brands and names are the property of their respective owners.

# int<sub>el</sub>。 Contents

| 1.0 | Pin / | Assignments and Signal Descriptions                |  |  |  |

|-----|-------|----------------------------------------------------|--|--|--|

| 2.0 | Fund  | ctional Description                                |  |  |  |

|     | 2.1   | Power Requirements                                 |  |  |  |

|     |       | 2.1.1 Initialization and Reset Operations          |  |  |  |

|     | 2.2   | Receiver                                           |  |  |  |

|     | 2.3   | Transmitter10                                      |  |  |  |

|     |       | 2.3.1 Idle Mode10                                  |  |  |  |

|     |       | 2.3.2 Short Circuit Limit11                        |  |  |  |

|     |       | 2.3.3 Line Code11                                  |  |  |  |

|     | 2.4   | Jitter Attenuation11                               |  |  |  |

|     | 2.5   | Operating Modes12                                  |  |  |  |

|     |       | 2.5.1 Host Mode Operation12                        |  |  |  |

|     |       | 2.5.2 Hardware Mode Operation13                    |  |  |  |

|     |       | 2.5.3 Diagnostic Mode Operation14                  |  |  |  |

|     |       | 2.5.3.1 Transmit All Ones14                        |  |  |  |

|     |       | 2.5.3.2 Local Loopback14                           |  |  |  |

|     |       | 2.5.3.3 Remote Loopback14                          |  |  |  |

|     |       | 2.5.3.4 Network Loopback14                         |  |  |  |

| 3.0 | Арр   | lication Information15                             |  |  |  |

|     | 3.1   | 3.1 LATN Decoding Circuits and External Components |  |  |  |

|     |       | 3.1.1 Host Mode Applications16                     |  |  |  |

|     | 3.2   | LXT310 Hardware Mode Applications18                |  |  |  |

| 4.0 | Test  | Specifications                                     |  |  |  |

| 5.0 | Мес   | hanical Specification25                            |  |  |  |

# **Figures**

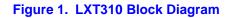

|   | 1  | LXT310 Block Diagram                        | 5  |

|---|----|---------------------------------------------|----|

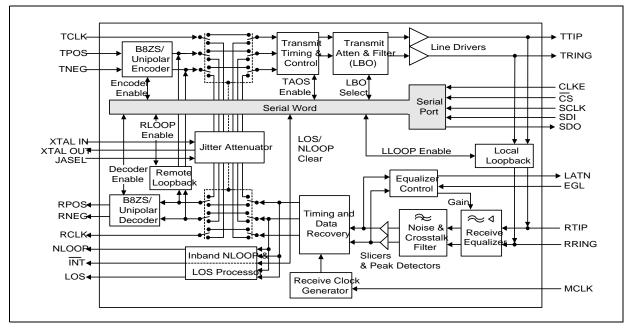

|   | 2  | LXT310 Pin Assignments and Package Markings |    |

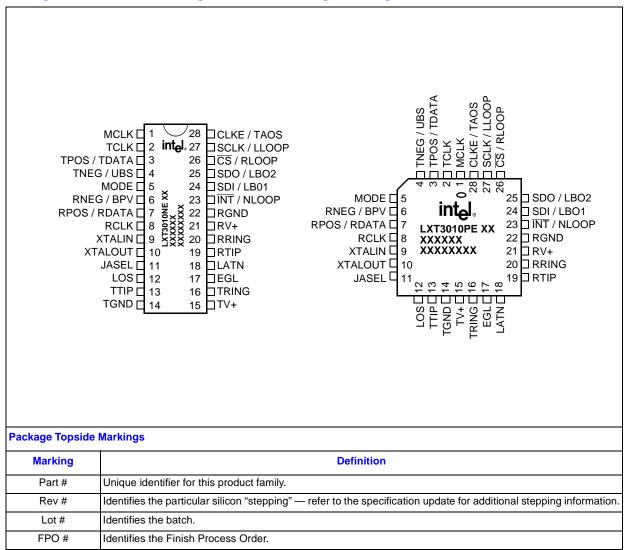

|   | 3  | LATN Pulse Width Encoding                   | 10 |

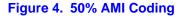

|   | 4  | 50% AMI Coding                              | 11 |

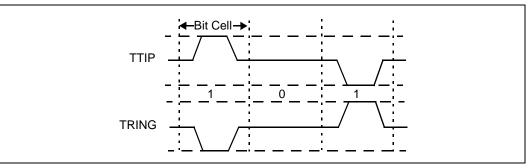

| ; | 5  | LXT310 Serial Interface Data Structure      | 13 |

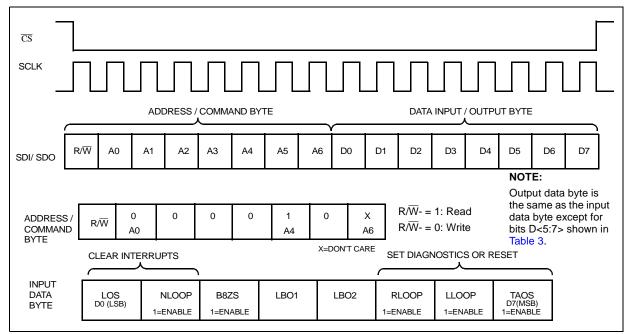

|   | 6  | Typical LATN Decoding Circuit               | 15 |

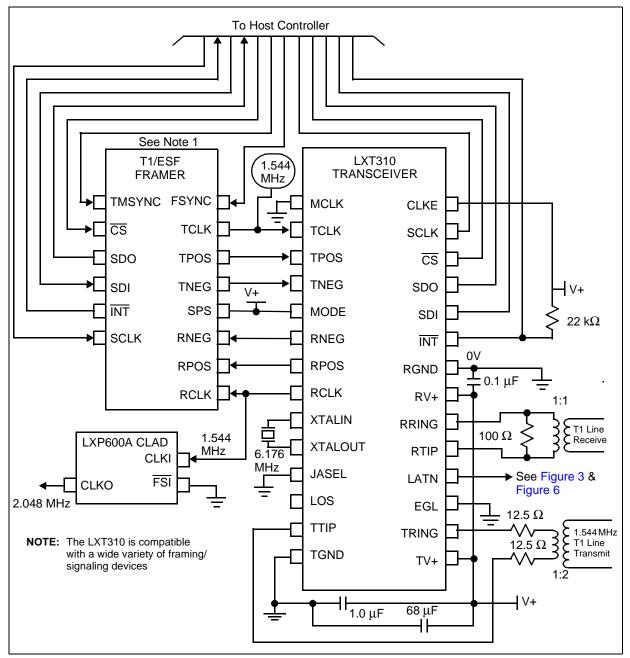

|   | 7  | Typical LXT310 Host Mode T1/CSU Application | 18 |

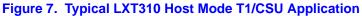

|   | 8  | Typical LXT310 Hardware Mode Application    | 19 |

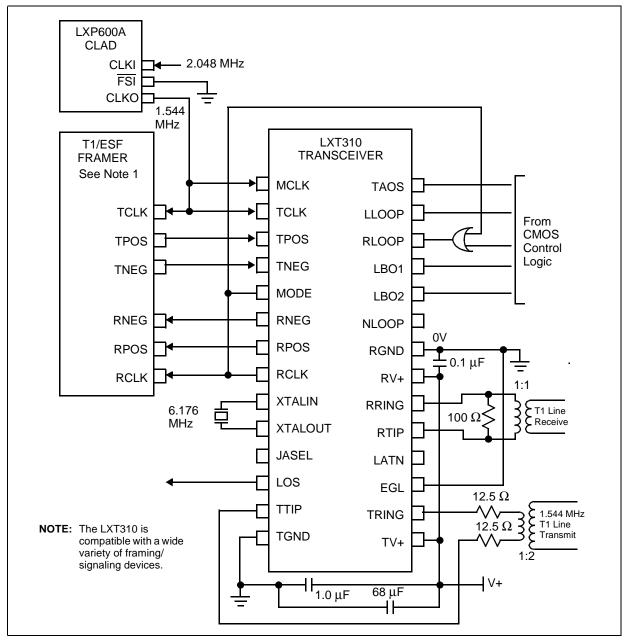

| 1 | 9  | 1.544 Mbps DS1 Pulse Mask (T1.403 - 1995)   | 21 |

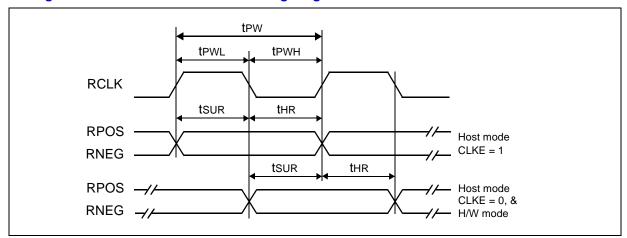

|   | 10 | LXT310 Receive Clock Timing Diagram         | 22 |

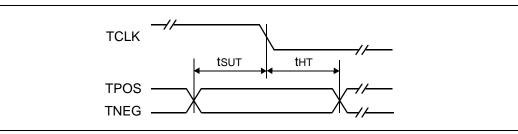

|   | 11 | LXT310 Transmit Clock Timing Diagram        | 23 |

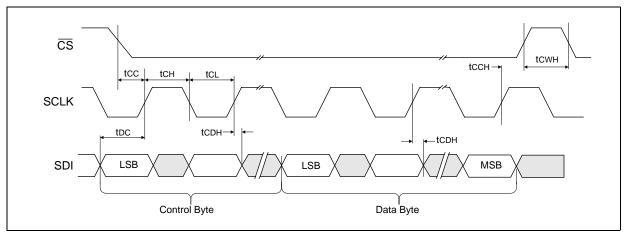

|   | 12 | LXT310 Serial Data Input Timing Diagram     | 24 |

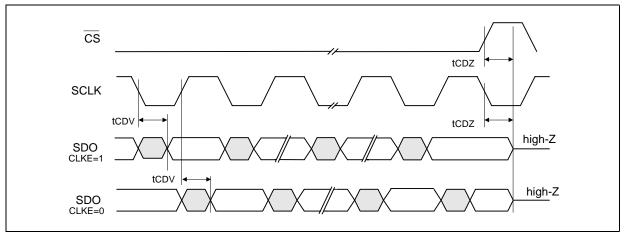

|   | 13 | LXT310 Serial Data Output Timing Diagram    | 24 |

|   | 14 | Package Specifications                      | 25 |

|   |    |                                             |    |

## **Tables**

| 1  | Pin Descriptions                                                        | 7  |

|----|-------------------------------------------------------------------------|----|

| 2  | CLKE Settings                                                           | 12 |

| 3  | LXT310 Serial Data Output Bits (See Figure 5)                           | 13 |

| 4  | LATN Output Coding                                                      | 15 |

| 5  | Approved Crystals and Transformers                                      | 15 |

| 6  | LXT310 Crystal Specifications (External)                                | 16 |

| 7  | Absolute Maximum Ratings                                                | 20 |

| 8  | Recommended Operating Conditions and Characteristics                    | 20 |

| 9  | Electrical Characteristics (Under Recommended Operating Conditions)     | 20 |

| 10 | Analog Characteristics (Under Recommended Operating Conditions)         | 21 |

| 11 | Pulse Mask Corner Point Specifications                                  | 21 |

| 12 | LXT310 Receive Timing Characteristics (See Figure 10)                   | 22 |

| 13 | LXT310 Master Clock and Transmit Timing Characteristics (See Figure 11) | 23 |

| 14 | LXT310 Serial I/O Timing Characteristics (See Figure 12 and Figure 13)  | 23 |

|    | •                                                                       |    |

# **1.0 Pin Assignments and Signal Descriptions**

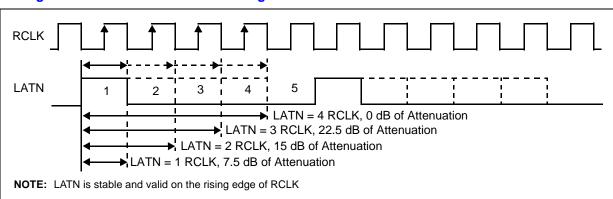

#### Figure 2. LXT310 Pin Assignments and Package Markings

#### Table 1. Pin Descriptions

| Pin #  | Sym                           | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------|-------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | MCLK                          | I   | <b>Master Clock.</b> A 1.544 MHz clock input used to generate internal clocks. Upon Loss of Signal (LOS), RCLK is derived from MCLK. If MCLK is not applied, this pin should be grounded.                                                                                                                                                                                                                                                                                                      |

| 2      | TCLK                          | I   | Transmit Clock. TPOS and TNEG are sampled on the falling edge of TCLK.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3      | TPOS/TDATA                    | I   | Transmit Data Input /Polarity Select. Input data to be transmitted on the twisted-pair line.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4      | TNEG/UBS                      | I   | Normally, pin 3 is TPOS and pin 4 is TNEG, the positive and negative sides of a bipolar input pair. However, if pin 4 is held High for at least 16 TCLK cycles (equivalent to 15 successive bipolar violations), the LXT310 switches to a unipolar I/O mode and transmit data is input on pin 3. The LXT310 returns to bipolar I/O mode when pin 4 goes Low.                                                                                                                                   |

| 5      | MODE                          | I   | <b>Mode Select.</b> Setting MODE High selects the Host mode. In Host mode, the serial interface is enabled for control and status reporting via a $\mu$ P. Setting MODE Low selects the Hardware (H/W) mode. In Hardware mode the serial interface is disabled; hard-wired pins control configuration and report status. Tying MODE to RCLK enables Hardware mode and the B8ZS encoder/decoder.                                                                                                |

| 6<br>7 | RNEG<br>RPOS<br>(Bipolar I/O) | 0   | <b>Receive Negative Data; Receive Positive Data.</b> In Bipolar Data I/O mode pins 6 and 7 are bipolar data outputs. A signal on RNEG corresponds to detection of a negative pulse on RTIP/RRING, and a signal on RPOS corresponds to a positive pulse on RTIP/RRING. RNEG/RPOS outputs are Non Return-to-Zero (NRZ). In Host mode, CLKE determines the clock edge at which these outputs are stable and valid. In Hardware mode both outputs are stable and valid on the rising edge of RCLK. |

| 6      | BPV<br>(Unipolar I/O)         | 0   | <b>Bipolar Violation.</b> In Unipolar Data I/O mode, pin 6 goes High to indicate receipt of a Bipolar Violation of the Alternate Mark Inversion (AMI) code.                                                                                                                                                                                                                                                                                                                                    |

| 7      | RDATA<br>(Unipolar I/O)       | 0   | Receive Data. In Unipolar mode, data received from the twisted-pair line is output at pin 7.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8      | RCLK                          | 0   | Recovered Clock. This is the clock recovered from the signal received at RTIP and RRING.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9      | XTALIN                        | I   | Crystal Input; Crystal Output. An external crystal (18.7 pF load capacitance, pullable)                                                                                                                                                                                                                                                                                                                                                                                                        |

| 10     | XTALOUT                       | ο   | operating at 6.176 MHz (four times the bit rate) is required to enable the jitter attenuation function of the LXT310. These pins may also be used to disable the jitter attenuator by connecting the XTALIN pin to the positive supply through a resistor, and leaving the XTALOUT pin unconnected.                                                                                                                                                                                            |

| 11     | JASEL                         | I   | <b>Jitter Attenuation Select.</b> Selects jitter attenuation location. When JASEL is High, the jitter attenuator is active in the receive path. When JASEL is Low, the jitter attenuator is active in the transmit path.                                                                                                                                                                                                                                                                       |

| 12     | LOS                           | 0   | <b>Loss of Signal.</b> LOS goes High when 175 consecutive spaces have been detected. LOS returns Low when the received signal reaches a mark density of 12.5% (determined by receipt of four marks within 32 bit periods). Received marks are output on RPOS and RNEG even when LOS is High.                                                                                                                                                                                                   |

| 13     | TTIP                          | 0   | Transmit Tip; Transmit Ring. Differential Driver Outputs. These outputs are designed to                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16     | TRING                         | 0   | drive a 50 - 200 $\Omega$ load. A transformer and line matching resistors can be selected to give the desired pulse height.                                                                                                                                                                                                                                                                                                                                                                    |

| 14     | TGND                          | -   | Transmit Ground. Ground return for the transmit drivers power supply TV+.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 15     | TV+                           | -   | <b>Transmit Power Supply.</b> +5 VDC power supply for the transmit drivers. TV+ must not vary from RV+ by more than ±0.3 V.                                                                                                                                                                                                                                                                                                                                                                    |

| 17     | EGL                           | I   | <b>Equalizer Gain Limit.</b> Sets equalizer gain. When EGL is Low, up to 36 dB of equalizer gain may be added. When EGL is High, equalizer gain is limited to no more than 26 dB.                                                                                                                                                                                                                                                                                                              |

| 18     | LATN                          | 0   | <b>Line Attenuation Indication (See Figure 3).</b> Encoded output. The LATN pulse width, relative to RCLK, indicates receive equalizer gain setting (line insertion loss at 772 kHz) in 7.5 dB steps. When LATN outputs 1 RCLK pulse, the equalizer is set at 7.5 dB gain, 2 pulses = 15 dB, 3 pulses = 22.5 dB and 4 pulses = 0 dB. LATN is valid on the rising edge of RCLK.                                                                                                                 |

#### Table 1. Pin Descriptions (Continued)

| Pin #    | Sym           | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                    |  |

|----------|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 19<br>20 | RTIP<br>RRING | 1   | <b>Receive Tip; Receive Ring.</b> The AMI signal received from the line is applied at these pins.<br>A 1:1 transformer is required. Data and clock from the signal applied at these pins are                                                                                                                                                                                                   |  |

| 20       | RRING         |     | recovered and output on the RPOS/RNEG and RCLK pins.                                                                                                                                                                                                                                                                                                                                           |  |

| 21       | RV+           | -   | <b>ceive Power Supply.</b> +5 VDC power supply for all circuits except the transmit drivers.<br>ansmit drivers are supplied by TV+.)                                                                                                                                                                                                                                                           |  |

| 22       | RGND          | -   | Receive Ground. Ground return for power supply RV+.                                                                                                                                                                                                                                                                                                                                            |  |

| 23       | NLOOP         | ο   | <b>Network Loopback (<i>H/W mode</i>).</b> When High, indicates Inband Network Loopback has been activated by reception of 00001 pattern for five seconds. NLOOP is reset by reception of 001 for five seconds, or by activation of RLOOP or LLOOP.                                                                                                                                            |  |

| 23       | INT           | 0   | <b>Interrupt (Host mode).</b> In Host mode INT goes Low to flag the host processor when LOS or NLOOP changes state. INT is an open-drain output and should be tied to power supply RV+ through a resistor. INT is reset by clearing the LOS or NLOOP register bit.                                                                                                                             |  |

|          | SDI           | I   | Serial Data In (Host mode). The serial data input stream is applied to this pin when the LXT310 operates in the Host mode. SDI is sampled on the rising edge of SCLK.                                                                                                                                                                                                                          |  |

| 24       | LBO1          | I   | <b>Line Build-Out Select 1</b> ( <i>H/W mode</i> ). In Hardware mode LBO1 works in conjunction with LBO2 to select the transmit line build-outs: $00 = 0 \text{ dB}$ , $01 = 7.5 \text{ dB}$ , $10 = 15 \text{ dB}$ , and $11 = 22.5 \text{ dB}$ .                                                                                                                                             |  |

| 25       | SDO           | 0   | <b>Serial Data Out</b> <i>(Host mode).</i> The serial data from the LXT310 register is output on this pin in Host mode. If CLKE is High, SDO is valid on the rising edge of SCLK. If CLKE is Low, SDO is valid on the falling edge of SCLK. This pin goes to a high-impedance state when the serial port is being written to and when $\overline{CS}$ is High.                                 |  |

|          | LBO2          | I   | Line Build-Out Select 2 (H/W mode). Refer to LBO1 signal description.                                                                                                                                                                                                                                                                                                                          |  |

|          | CS            | I   | <b>Chip Select (Host mode).</b> This pin selects the serial interface in the Host mode. For ear read or write operation, CS must transition from High to Low, and remain Low.                                                                                                                                                                                                                  |  |

| 26       | RLOOP         | I   | <b>Remote Loopback (H/W mode).</b> This pin controls loopback in the Hardware mode. Setting RLOOP High enables Remote Loopback. During Remote Loopback, in-line encoders and decoders are bypassed. Setting both RLOOP and LLOOP High, while holding TAOS Low, causes a Reset. Setting both RLOOP and LLOOP High, with TAOS High (or tying RCLK to RLOOP), enables Network Loopback detection. |  |

|          | SCLK          | I   | Serial Clock (Host mode). This clock is used in the Host mode to write data to or read data from the serial interface registers.                                                                                                                                                                                                                                                               |  |

| 27       | LLOOP         | I   | <b>Local Loopback (H/W mode).</b> This input controls loopback functions in the Hardware mode.<br>Setting LLOOP High enables the Local Loopback mode. Setting both LLOOP and RLOOP<br>High, while holding TAOS Low, causes a Reset.                                                                                                                                                            |  |

| 28       | CLKE          | I   | <b>Clock Edge Select (Host mode).</b> Setting CLKE High causes RPOS and RNEG to be valid on the falling edge of RCLK, and SDO to be valid on the rising edge of SCLK. When CLKE is Low, RPOS and RNEG are valid on the rising edge of RCLK, and SDO is valid on the falling edge of SCLK.                                                                                                      |  |

| 20       | TAOS          | I   | <b>Transmit All Ones (H/W mode).</b> When set High in the Hardware mode, TAOS causes the LXT310 to transmit a stream of marks at the TCLK frequency. Activating TAOS causes TPOS and TNEG inputs to be ignored. TAOS is inhibited during Remote Loopback. Setting TAOS, LLOOP and RLOOP High simultaneously enables Network Loopback detection.                                                |  |

# int<sub>el</sub>®

# 2.0 Functional Description

The LXT310 is a fully integrated PCM transceiver for 1.544 Mbps (T1) applications. It allows full-duplex transmission of digital data over existing twisted-pair installations.

The LXT310 interfaces with two twisted-pair lines (one pair for transmit, one pair for receive) through standard pulse transformers and appropriate resistors.

The figure on the front page of this section is a block diagram of the LXT310. The transceiver may be controlled by a microprocessor through the serial port (Host mode), or by individual pin settings (Hardware mode). The jitter attenuator may be positioned in either the transmit or receive path.

#### 2.1 **Power Requirements**

The LXT310 is a low-power CMOS device. It operates from a single +5 V power supply which can be connected externally to both the transmitter and receiver. However, the two inputs must be within  $\pm 0.3$  V of each other, and decoupled to their respective grounds separately. Refer to Application Information for typical decoupling circuitry. Isolation between the transmit and receive circuits is provided internally.

#### 2.1.1 Initialization and Reset Operations

Upon power up, the transceiver is held static until the power supply reaches approximately 3 V. Upon crossing this threshold, the device begins a 32 ms reset cycle to calibrate the transmit and receive delay lines and lock the Phase Lock Loop to the receive line. A reference clock is required to calibrate the delay lines. The transmitter reference is provided by TCLK. The crystal oscillator provides the receiver reference. If the crystal oscillator is grounded, MCLK is used as the receiver reference clock.

The transceiver can also be reset from the Host or Hardware mode. In Host mode, reset is commanded by simultaneously writing ones to RLOOP and LLOOP, and a zero to TAOS. In Hardware mode, reset is commanded by holding RLOOP and LLOOP High simultaneously for 200 ns while holding TAOS Low. In either mode, reset clears and sets all registers to 0.

#### 2.2 Receiver

The twisted-pair input is received via a 1:1 transformer. Recovered data is output at RPOS/RNEG (RDATA in unipolar mode), and the recovered clock is output at RCLK. Refer to Test Specifications for receiver timing.

The signal received at RPOS and RNEG is processed through the receive equalizer. The Equalizer Gain Limit (EGL) input determines the maximum gain that may be applied at the equalizer. When set Low, up to 36 dB of gain may be applied.

When EGL is High, gain is limited to no more than 26 dB providing for increased noise margin in shorter loop operation. Insertion loss of the line in 7.5 dB steps, as indicated by the receive equalizer setting, is encoded in the LATN output as shown in Figure 3.

Figure 3. LATN Pulse Width Encoding

The equalized signal is filtered and applied to the peak detector and data slicers. The peak detector samples the inputs and determines the maximum value of the received signal. A percentage of the peak value is provided to the data slicers as a threshold level to ensure optimum signal-to-noise ratio. The threshold is set to 50% of the peak value. The receiver is capable of accurately recovering signals with up to 36 dB of cable attenuation (from 2.4 V)

After processing through the data slicers, the received signal is routed to the data and timing recovery section, then to the B8ZS decoder (if selected) and to the LOS processor. The LOS Processor loads a digital counter at the RCLK frequency. The count is incremented each time a zero (space) is received, and reset to zero each time a one (mark) is received. Upon receipt of 175 consecutive zeros the LOS pin goes High, and a smooth transition replaces the RCLK output with the MCLK. Note that during LOS, if MCLK is not supplied and JASEL = 1, the RCLK output is replaced with the centered crystal clock.

Received marks will be output regardless of the LOS status, but the LOS pin will not reset until the ones density reaches 12.5%. This level is based on receipt of at least 4 ones in any 32-bit period.

#### 2.3 Transmitter

Input data (bipolar or unipolar) for transmission onto the line is clocked serially into the device. Bipolar data is input at pin 3 (TPOS) and pin 4 (TNEG). Unipolar data is input at pin 3 (TDATA) only. Unipolar mode is enabled by holding pin 4 high for 16 RCLK cycles. Input data may be passed through the Jitter Attenuator and/or B8ZS encoder, if selected. In Host mode, B8ZS is selected by setting bit D3 of the input data byte. In Hardware mode, B8ZS is selected by connecting the MODE pin to RCLK. Input synchronization is supplied by the transmit clock (TCLK). Timing requirements for TCLK and the Master Clock (MCLK) are defined in Test Specifications.

#### 2.3.1 Idle Mode

The LXT310 incorporates a transmit idle mode. This allows multiple transceivers to be connected to a single line for redundant applications. TTIP and TRING remain in a high- impedance state when TCLK is not present (TCLK grounded). The high-impedance state can be temporarily disabled by enabling either TAOS, Remote Loopback or Network Loopback.

The transmitted pulse shape is determined by Line Build Out (LBO) inputs LBO1 and LBO2 as follows:

| Line Build-Out Control | dB |     |    |      |  |

|------------------------|----|-----|----|------|--|

| Line Build-Out Control | 0  | 7.5 | 15 | 22.5 |  |

| LBO1                   | 0  | 1   | 0  | 1    |  |

| LBO2                   | 0  | 0   | 1  | 1    |  |

In Host mode, LBO is specified by setting the appropriate bits in the LXT310 register via the serial port. In the Hardware mode, LBO inputs are applied through individual pins (1 = High; 0 = Low). Shaped pulses meeting the various T1 CSU and ISDN PRI requirements are applied to the AMI line driver for transmission onto the line at TTIP and TRING. Refer to Test Specifications for T1 pulse mask specifications.

#### 2.3.2 Short Circuit Limit

The LXT310 transmitter is equipped with a short-circuit limiter. This feature limits to approximately 120 mA RMS the current the transmitter will source into a low-impedance load. The limiter trips when the RMS current exceeds the limit for 100  $\mu$ s (~ 150 marks). It automatically resets when the load current drops below the limit.

The LXT310 meets or exceeds FCC and AT&T specifications for CSU and NI applications, as well as ANSI T1E1, and CCITT requirements for ISDN PRI.

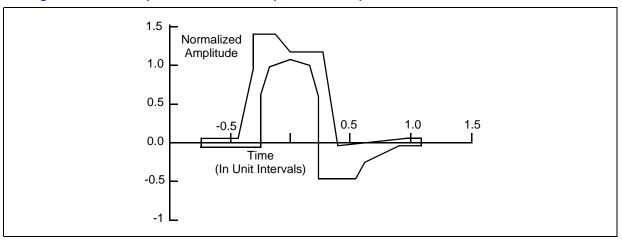

#### 2.3.3 Line Code

The LXT310 transmits data as a 50% AMI line code as shown in Figure 4. Power consumption is reduced by activating the AMI line driver only to transmit a mark. The output driver is disabled during transmission of a space. Biasing of the transmit DC level is on-chip.

#### 2.4 Jitter Attenuation

Jitter attenuation is provided by a Jitter Attenuation Loop (JAL) and an Elastic Store (ES). An external crystal oscillating at 4 times the bit rate provides clock stabilization. Refer to Table 6 for crystal specifications. The ES is a 32 x 2-bit register. When JASEL = 1, the JAL is positioned in the receive path. When JASEL = 0, the JAL is positioned in the transmit path.

Data (TPOS/TNEG / TDATA or RPOS/RNEG / RDATA) is clocked into the ES with the associated clock signal (TCLK or RCLK), and clocked out of the ES with the dejittered clock from the JAL. When the bit count in the ES is within two bits of overflowing or underflowing, the ES adjusts the output clock by 1/8 of a bit period. The ES produces an average delay of 16 bits in the associated path.

#### 2.5 Operating Modes

The LXT310 can be controlled by a microprocessor through a serial interface (Host mode), or through individual pins (Hardware mode). The mode of operation is set by the MODE pin logic level.

#### 2.5.1 Host Mode Operation

The LXT310 operates in the Host mode when MODE is set High. The 16-bit serial word consists of an 8-bit Command/Address byte and an 8-bit Data byte.

Table 3 lists the output data bit combinations. Figure 5 shows the serial interface data structure and timing. The Host mode provides a latched Interrupt output ( $\overline{INT}$ ) which is triggered by a change in the LOS or NLOOP bits. The Interrupt is cleared when the interrupt condition no longer exists, and the host processor writes a one to the respective bit in the serial input data byte.

Host mode also allows control of the serial data and receive data output timing. The Clock Edge (CLKE) signal determines when these outputs are valid, relative to the Serial Clock (SCLK) or RCLK as listed in Table 2.

#### Table 2. CLKE Settings

| Output    | Clock | CLKE = 0 | CLKE = 1 |

|-----------|-------|----------|----------|

| RPOS/RNEG | RCLK  | Rising   | Falling  |

| SDO       | SCLK  | Falling  | Rising   |

The LXT310 serial port is addressed by setting bit A4 in the Address/Command byte, corresponding to address 16. The LXT310 contains only a single output data register so no complex chip addressing scheme is required. The register is accessed by causing the Chip Select  $(\overline{CS})$  input to transition from High to Low. Bit 1 of the serial Address/Command byte provides Read/Write control when the chip is accessed. A logic 1 indicates a read operation, and a logic 0 indicates a write operation. Serial data I/O timing characteristics are shown in Table 14, and Figure 12 and Figure 13 in the Test Specifications section.

#### Table 3. LXT310 Serial Data Output Bits (See Figure 5)

| Bit<br>D5 | Bit<br>D6 | Bit<br>D7 | Status                                                                           |

|-----------|-----------|-----------|----------------------------------------------------------------------------------|

| 0         | 0         | 0         | Reset has occurred, or no program input.                                         |

| 0         | 0         | 1         | TAOS is active.                                                                  |

| 0         | 1         | 0         | Local Loopback is active.                                                        |

| 0         | 1         | 1         | TAOS and Local Loopback are active.                                              |

| 1         | 0         | 0         | Remote Loopback is active.                                                       |

| 1         | 0         | 1         | DPM has changed state since last Clear DPM occurred.                             |

| 1         | 1         | 0         | LOS has changed state since last Clear LOS occurred.                             |

| 1         | 1         | 1         | LOS and DPM have both changed state since last Clear DPM and Clear LOS occurred. |

#### 2.5.2 Hardware Mode Operation

In Hardware mode the transceiver is accessed and controlled through individual pins. With the exception of the INT and CLKE functions, Hardware mode provides all the functions provided in the Host mode. In the Hardware mode RPOS/RNEG or RDATA outputs are valid on the rising edge of RCLK. The LXT310 operates in Hardware mode only when MODE is set Low or connected to RCLK.

#### 2.5.3 Diagnostic Mode Operation

#### 2.5.3.1 Transmit All Ones

In Transmit All Ones (TAOS) mode, the TPOS and TNEG inputs to the transceiver are ignored and the transceiver transmits a continuous stream of ones at the TCLK frequency. If TCLK is not provided, TAOS is locked to the MCLK. This can be used as the Blue Alarm Indicator (AIS). In Host mode, TAOS is commanded by writing a one to bit D7 of the input data byte. In Hardware mode, TAOS is commanded by setting pin 28 High. TAOS can be commanded simultaneously with Local Loopback, but is inhibited during Remote Loopback.

#### 2.5.3.2 Local Loopback

Local Loopback (LLOOP) is designed to exercise the maximum number of functional blocks. During LLOOP operation, the RTIP/RRING inputs from the line are disconnected. Instead, the transmit outputs are routed back into the receive inputs. This tests the encoders/decoders, jitter attenuator, transmitter, receiver and timing recovery sections. In Host mode, Local Loopback is commanded by writing a one to bit D6 of the input data byte. In Hardware mode, Local Loopback is commanded by setting pin 27 High. If TAOS and LLOOP are both set, the All Ones pattern is transmitted onto the line while the TPOS/TNEG input data is looped back to the RPOS/RNEG outputs.

#### 2.5.3.3 Remote Loopback

In Remote Loopback (RLOOP) mode, the transmit data and clock inputs (TCLK and TPOS/TNEG or TDATA) are ignored, and the in-line encoders and decoders are bypassed. The RPOS/RNEG or RDATA outputs are looped back through the transmit circuits and output on TTIP and TRING at the RCLK frequency. Receiver circuits are unaffected by the RLOOP command and continue to output the RCLK and RPOS/RNEG or RDATA signals received from the twisted-pair line. In Host mode, Remote Loopback is commanded by writing a one to bit D5 of the input data byte. In Hardware mode, Remote Loopback is commanded by setting pin 26 High.

#### 2.5.3.4 Network Loopback

Network Loopback can be commanded from the network when the Network Loopback detect function is enabled. In Host mode, Network Loopback (NLOOP) detection is enabled by simultaneously writing ones to RLOOP, LLOOP and TAOS, then writing zeros in the next cycle. In Hardware mode, Network Loopback detection is enabled by holding RLOOP, LLOOP and TAOS High simultaneously for 200 ns then bringing them Low, or by tying RCLK to RLOOP. NLOOP detection may be disabled by resetting the chip.

When NLOOP detection is enabled, the receiver monitors the input data stream for the NLOOP data patterns (00001 = enable, 001 = disable). When an NLOOP enable data pattern is repeated for a minimum of five seconds (with 10-3 BER), the device begins remote loopback operation. The LXT310 responds to both framed and unframed NLOOP patterns. Once remote network loopback detection is enabled at the chip and activated by the correct data pattern, it is identical to remote loopback initiated at the chip. NLOOP is reset by receiving the disable pattern for 5 seconds, or by activation of RLOOP. NLOOP is temporarily interrupted by LLOOP, but the NLOOP state is not reset.

# 3.0 Application Information

#### 3.1 LATN Decoding Circuits and External Components

To conserve pins, the line attenuation output is encoded as a simple serial bit stream. Table 4 provides the decoded output for each equalizer setting. Figure 6 is a typical decoding circuit for the LATN output. It uses a 2-bit synchronous counter (half of a 4-bit counter) with synchronous reset, and a pair of flip-flops. Table 5 lists approved crystals and transformers.

#### Table 4. LATN Output Coding

| L1 L2 |   | Line Attenuation |

|-------|---|------------------|

| 0     | 0 | 0.0 dB           |

| 0     | 1 | -7.5 dB          |

| 1     | 0 | -15.0 dB         |

| 1     | 1 | -22.5 dB         |

#### Figure 6. Typical LATN Decoding Circuit

#### Table 5. Approved Crystals and Transformers

| Component              | Manufacturer                                                                                              | Part Numbers                                                                   |

|------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

|                        | M-Tron                                                                                                    | MP-1 3808-010 / 4144-002                                                       |

|                        | Monitor Products                                                                                          | MSC1311-01B                                                                    |

| Crystal<br>(6.176 MHz) | CTS Knights                                                                                               | 6176-180                                                                       |

| (0.170 Mil2)           | Valpey Fisher <sup>1</sup>                                                                                | VF49A16FN1                                                                     |

|                        | U.S. Crystal                                                                                              | U18-18-6176SP                                                                  |

|                        | should always verify the specifications of the qu<br>take certain that the crystal suits the desired appl | artz crystal against Intel's recommended specification <b>point-</b> lication. |

| Component                | Manufacturer      | Part Numbers                            |  |

|--------------------------|-------------------|-----------------------------------------|--|

|                          | Bell Fuse         | 0553-5006-IC                            |  |

|                          | FEE Fil-Mag       | 66Z1308                                 |  |

| Tx Transformer           | Midcom            | 671-5832                                |  |

| (1: 2)                   | Pulse Engineering | 65351, 65771                            |  |

|                          | Schott Corp       | 67127370 and 67130850                   |  |

|                          | HALO              | TD61-1205G and TD67-1205G (combo Tx/Rx) |  |

|                          | FEE Fil-Mag       | FE 8006-155                             |  |

| /                        | Midcom            | 671-5792                                |  |

| Rx Transformer<br>(1: 1) | Pulse Engineering | 64936 and 65778                         |  |

| ()                       | Schott Corp       | 67130840 and 67109510                   |  |

|                          | HALO              | TD61-1205G and TD67-1205G (combo Tx/Rx) |  |

|                          | -                 | •                                       |  |

#### Table 5. Approved Crystals and Transformers

1. The customer should always verify the specifications of the quartz crystal against Intel's recommended specification **point-by-point** to make certain that the crystal suits the desired application.

#### 3.1.1 Host Mode Applications

Figure 7 shows a typical T1 CSU application with the LXT310 operating in the Host mode (MODE pin tied high). A T1/ESF Framer provides the digital interface with the host controller. Both devices are controlled through the serial interface. In the Host mode, the LOS alarm is reported via the serial port so the LOS pin is allowed to float.

An LXP600A Clock Adapter (CLAD) provides the 2.048 MHz system backplane clock, locked to the recovered 1.544 MHz clock signal. The 6.176 MHz crystal across XTALIN and XTALOUT enables the JAL that is switched to the transmit side by the Low on JASEL. Refer to Table 5 for approved crystals and transformers. The power supply inputs are tied to a common bus with appropriate decoupling capacitors (68  $\mu$ F and 0.1  $\mu$ F) installed on each side.

The twisted-pair interfaces are relatively simple. A 100  $\Omega$  resistor across the input of a 1:1 transformer is used on the receive side, and a pair of 12.5  $\Omega$  resistors are installed in line with the 1:2 output transformer.

| Table 6. | LXT310 Crystal | Specifications | (External) |

|----------|----------------|----------------|------------|

|----------|----------------|----------------|------------|

| Parameter                   | Specification                                                                                              |

|-----------------------------|------------------------------------------------------------------------------------------------------------|

| Frequency                   | 6.176 MHz                                                                                                  |

| Frequency stability         | ± 20 ppm @ 25 °C<br>± 25 ppm from -40 °C to 85 °C<br>(Ref 25 °C reading)                                   |

| Pullability                 | CL = 11 pF to 18.7 pF, $+\Delta$ F = 175 to 195 ppm<br>CL = 18.7 pF to 34 pF, $-\Delta$ F = 175 to 195 ppm |

| Effective series resistance | 40 Ω Maximum                                                                                               |

| Crystal cut                 | AT                                                                                                         |

| Resonance                   | Parallel                                                                                                   |

#### Table 6. LXT310 Crystal Specifications (External)

| Parameter           | Specification                                       |

|---------------------|-----------------------------------------------------|

| Maximum drive level | 2.0 mW                                              |

| Mode of operation   | Fundamental                                         |

| Crystal holder      | HC49 (R3W), Co = 7 pF maximum<br>CM = 17 fF typical |

#### 3.2 LXT310 Hardware Mode Applications

Figure 8 is a typical 1.544 Mbps ISDN PRI application with the LXT310, a T1/ESF framer and an LXP600A clock adapter. The LXT310 is operating in the Hardware mode with B8ZS encoding enabled (MODE pin 5 tied to RCLK). As in the T1/CSU application, Figure 7, this configuration is illustrated with a single power supply bus. CMOS control logic is used to set both LBO pins high,

selecting the 22.5 dB LBO, and the EGL pin is tied low, allowing for full receiver gain. The TAOS, LLOOP and RLOOP diagnostic modes are individually controllable. The RCLK input to the OR gate at RLOOP allows for clocking of the RLOOP pin, which enables network loopback detection. The receive and transmit line interfaces are identical to the Host mode application shown in Figure 7.

## 4.0 Test Specifications

*Note:* The minimum and maximum values in Table 7 through Table 14 and Figure 9 through Figure 13 represent the performance specifications of the LXT310 and are guaranteed by test, except where noted by design

#### Table 7. Absolute Maximum Ratings

| Parameter                                     | Sym                     | Min               | Max       | Units |

|-----------------------------------------------|-------------------------|-------------------|-----------|-------|

| DC supply (referenced to GND)                 | RV+, TV+                | -0.3              | 6.0       | V     |

| Input voltage, any pin                        | Vin                     | RGND - 0.3        | RV+ + 0.3 | V     |

| Input current, any pin <sup>1</sup>           | lin                     | -10               | 10        | mA    |

| Ambient operating temperature                 | ТА                      | -40               | 85        | °C    |

| Storage temperature                           | Тѕтс                    | -65               | 150       | °C    |

| Caution: Operations at or beyond these limits | may recult in permanent | damage to the dou | ico       |       |

*Caution:* Operations at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

1. Transient currents of up to 100 mA will not cause SCR latch up. TTIP, TRING, TV+ and TGND can withstand a continuous current of 100 mA.

#### Table 8. Recommended Operating Conditions and Characteristics

| Parameter                              | Sym      | Min  | Тур | Max  | Units |

|----------------------------------------|----------|------|-----|------|-------|

| DC supply <sup>1</sup>                 | RV+, TV+ | 4.75 | 5.0 | 5.25 | V     |

| Ambient operating temperature          | TA       | -    | 25  | -    | °C    |

| 1. TV+ must not exceed RV+ by more tha | n 0.3 V. |      |     |      |       |

#### Table 9. Electrical Characteristics (Under Recommended Operating Conditions)

| Parameter                                                           | Sym | Min | Typ <sup>1</sup> | Max  | Units | Test Conditions                                     |

|---------------------------------------------------------------------|-----|-----|------------------|------|-------|-----------------------------------------------------|

| High level input voltage <sup>2,3</sup> (pins 1-5, 10, 23-28)       | Vін | 2.0 | -                | -    | V     |                                                     |

| Low level input voltage <sup>2,3</sup> (pins 1-5, 10, 23-28)        | Vil | -   | _                | 0.8  | V     |                                                     |

| High level output voltage <sup>2,3</sup> (pins 6-8, 11, 12, 23, 25) | Voн | 2.4 | -                | -    | V     | Ιουτ = -400 μΑ                                      |

| Low level output voltage <sup>2,3</sup> (pins 6-8, 11, 12, 23, 25)  | Vol | -   | -                | 0.4  | V     | IOUT = 1.6 mA                                       |

| Input leakage current                                               | Ill | 0   | -                | ±10  | μΑ    |                                                     |

| Three-state leakage current <sup>2</sup> (pin 25)                   | I3∟ | 0   | -                | ±10  | μA    |                                                     |

| Driver power down current <sup>4</sup>                              | IPD | -   | _                | ±1.2 | mA    | Direct connection to VCC or GND                     |

| Total power dissipation <sup>5</sup>                                | PD  | _   | 620              | -    | mW    | 100% ones density & maximum line length<br>@ 5.25 V |

1. Typical values are measured at 25 °C and are for design aid only; not guaranteed and not subject to production testing.

2. Functionality of pins 23 and 25 depends on mode. See Host/Hardware mode descriptions.

3. Output drivers will output CMOS logic levels into CMOS loads.

4. TTIP, TRING only in Idle or Power Down mode.

5. Power dissipation as shown in Figure 8 while driving a 100 Ω resistive load terminating transformer over operating temperature range. Includes device and load. Digital input levels are within 10% of the supply rails and digital outputs are driving a 50 pF capacitive load.

| Parameter                                              |                  | Min | Typ <sup>1</sup> | Max  | Units | Test Conditions                              |

|--------------------------------------------------------|------------------|-----|------------------|------|-------|----------------------------------------------|

| Recommended output load at TTIP and TRING              |                  | 50  | -                | 200  | Ω     |                                              |

| AMI Output Pulse Amplitudes                            |                  | 2.4 | 3.0              | 3.6  | V     |                                              |

|                                                        | 10 Hz - 8 kHz    | -   | -                | 0.02 | UI    |                                              |

|                                                        | 8 kHz - 40 kHz   | -   | -                | 0.02 | UI    | measured at the output<br>with LBO1 = 0, and |

| Jitter added by the transmitter <sup>2</sup>           | 10 Hz - 40 kHz   | -   | -                | 0.02 | UI    | LBO2 = $0$                                   |

| · · · · · · · · · · · · · · · · · · ·                  | Broad Band       | -   | -                | 0.04 | UI    | -                                            |

| Receive signal attenuation                             | Mode 1 (EGL = 1) | 0   | 26               | -    | dB    |                                              |

| range @ 772 kHz                                        | Mode 2 (EGL = 0) | 0   | 36               | -    | dB    |                                              |

| Allowable consecutive zeros bef                        | ore LOS          | 160 | 175              | 190  | -     |                                              |

| lanut litter televenes                                 | 10 kHz - 100 kHz | 0.4 | -                | -    | UI    |                                              |

| Input jitter tolerance                                 | 1 Hz             | 138 | -                | -    | UI    |                                              |

| Jitter attenuation curve corner frequency <sup>3</sup> |                  | -   | 3                | -    | Hz    |                                              |

| 1 Tunical values are measured                          |                  |     |                  |      |       |                                              |

#### Table 10. Analog Characteristics (Under Recommended Operating Conditions)

1. Typical values are measured at 25 °C and are for design aid only; not guaranteed and not subject to production testing.

2. Input signal to TCLK is jitter-free.

Guaranteed by characterization; not subject to production testing.

Circuit attenuates jitter at 20 dB/decade above the corner frequency.

#### Figure 9. 1.544 Mbps DS1 Pulse Mask (T1.403 - 1995)

#### Table 11. Pulse Mask Corner Point Specifications

| Maximum Curve |     | Minimu    | m Curve |

|---------------|-----|-----------|---------|

| Time (ns)     | % V | Time (ns) | % V     |

| 0             | 5   | 0         | -5      |

| 250           | 5   | 350       | -5      |

| 325           | 80  | 350       | 50      |

| 325           | 120 | 400       | 90      |

#### Table 11. Pulse Mask Corner Point Specifications

| Maximum   | Maximum Curve |           | Curve |

|-----------|---------------|-----------|-------|

| Time (ns) | % V           | Time (ns) | % V   |

| 425       | 120           | 500       | 95    |

| 500       | 105           | 600       | 90    |

| 675       | 105           | 650       | 50    |

| 725       | 5             | 650       | -45   |

| 1100      | 5             | 800       | -45   |

| 1250      | 5             | 896       | -26   |

|           |               | 1100      | -5    |

|           |               | 1250      | -5    |

#### Table 12. LXT310 Receive Timing Characteristics (See Figure 10)

| Parameter                                                           | Sym         | Min          | Typ <sup>1</sup> | Max           | Units |

|---------------------------------------------------------------------|-------------|--------------|------------------|---------------|-------|

| Receive clock duty cycle <sup>2</sup>                               | RCLKd       | 40           | 50               | 60            | %     |

| Receive clock period                                                | tPW         | 600          | 648              | 700           | ns    |

| Receive clock pulse width high                                      | tPWH        | -            | 324              | -             | ns    |

| Receive clock pulse width low                                       | tPWL        | 303          | 324              | 345           | ns    |

| RPOS/RNEG to RCLK rising setup time                                 | tSUR        | _            | 274              | -             | ns    |

| RCLK rising to RPOS/RNEG hold time                                  | tHR         | _            | 274              | -             | ns    |

| 1 Typical values are at 25 °C and are for design aid only: they are | onot quaran | teed and not | subject to pr    | oduction test | ina   |

Typical values are at 25 °C and are for design aid only; they are not guaranteed and not subject to production testing.

RCLK duty cycle widths will vary depending on extent of received pulse jitter displacement. Max and Min RCLK duty cycles are for worst case jitter conditions (0.4 UI clock displacement for 1.544 MHz).

#### Figure 10. LXT310 Receive Clock Timing Diagram

| Parameter                            | Sym               | Min              | Typ <sup>1</sup> | Max             | Units            | Notes       |

|--------------------------------------|-------------------|------------------|------------------|-----------------|------------------|-------------|

| Master clock frequency               | MCLK              | -                | 1.544            | -               | MHz              |             |

| Master clock tolerance               | MCLKt             | -                | ±100             | -               | ppm              |             |

| Master clock duty cycle              | MCLKd             | 40               | -                | 60              | %                |             |

| Crystal frequency                    | fc                | -                | 6.176            | -               | MHz              | LXT310 only |

| Transmit clock frequency             | TCLK              | -                | 1.544            | -               | MHz              |             |

| Transmit clock tolerance             | TCLKt             | -                | -                | ±100            | ppm              |             |

| Transmit clock duty cycle            | TCLKd             | 10               | -                | 90              | %                |             |

| TPOS/TNEG to TCLK setup time         | tSUT              | 50               | -                | -               | ns               |             |

| TCLK to TPOS/TNEG hold time          | tHT               | 50               | -                | -               | ns               |             |

| 1. Typical values are at 25 °C and a | re for design aid | only; they are i | not guaranteed   | and not subject | ct to production | on testing. |

#### Table 13. LXT310 Master Clock and Transmit Timing Characteristics (See Figure 11)

#### Figure 11. LXT310 Transmit Clock Timing Diagram

#### Table 14. LXT310 Serial I/O Timing Characteristics (See Figure 12 and Figure 13)

| Parameter                                                               | Sym        | Min          | Typ <sup>1</sup> | Max        | Units      | Test Conditions               |

|-------------------------------------------------------------------------|------------|--------------|------------------|------------|------------|-------------------------------|

| Rise/Fall time - any digital output                                     | tRF        | _            | -                | 100        | ns         | Load 1.6 mA, 50 pF            |

| SDI to SCLK setup time                                                  | tDC        | 50           | -                | -          | ns         |                               |

| SCLK to SDI hold time                                                   | tCDH       | 50           | -                | -          | ns         |                               |

| SCLK low time                                                           | tCL        | 240          | -                | -          | ns         |                               |

| SCLK high time                                                          | tCH        | 240          | -                | -          | ns         |                               |

| SCLK rise and fall time                                                 | tR, tF     | -            | -                | 50         | ns         |                               |

| $\overline{\mathrm{CS}}$ to SCLK setup time                             | tCC        | 50           | -                | -          | ns         |                               |

| SCLK to $\overline{CS}$ hold time                                       | tCCH       | 50           | -                | -          | ns         |                               |

| CS inactive time                                                        | tCWH       | 250          | -                | -          | ns         |                               |

| SCLK to SDO valid                                                       | tCDV       | -            | -                | 200        | ns         |                               |

| SCLK falling edge or $\overline{\mathrm{CS}}$ rising edge to SDO high Z | tCDZ       | -            | 100              | -          | ns         |                               |

| 1. Typical values are at 25° C and are                                  | for design | aid only; th | ey are not       | guaranteed | and not su | ubject to production testing. |

Figure 12. LXT310 Serial Data Input Timing Diagram

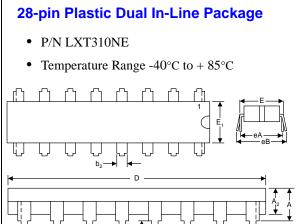

# 5.0 Mechanical Specification

#### Figure 14. Package Specifications

intel

| Dim | Inc       | hes                    | Millimeters |                        |  |  |

|-----|-----------|------------------------|-------------|------------------------|--|--|

|     | Min       | Мах                    | Min         | Max                    |  |  |

| А   | -         | 0.250                  | -           | 6.350                  |  |  |

| A2  | 0.125     | 0.195                  | 3.175       | 4.953                  |  |  |

| b   | 0.014     | 0.022                  | 0.356       | 0.559                  |  |  |

| b2  | 0.030     | 0.070                  | 0.762       | 1.778                  |  |  |

| D   | 1.380     | 1.565                  | 35.052      | 39.751                 |  |  |

| Е   | 0.600     | 0.625                  | 15.240      | 15.875                 |  |  |

| E1  | 0.485     | 0.580                  | 12.319      | 14.732                 |  |  |

| е   | 0.100 BSC | <sup>1</sup> (nominal) | 2.540 BSC   | (nominal)              |  |  |

| eA  | 0.600 BSC | <sup>1</sup> (nominal) | 15.240 BSC  | <sup>1</sup> (nominal) |  |  |

| eВ  | -         | 0.700                  | -           | 17.780                 |  |  |

| L   | 0.115     | 0.200                  | 2.921       | 5.080                  |  |  |

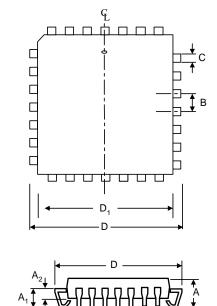

#### 28-pin Plastic Leaded Chip Carrier

- P/N LXT310PE

- Temperature Range  $-40^{\circ}$ C to  $+85^{\circ}$ C

| Dim                                  | Inches                          |       | Millimeters                     |        |

|--------------------------------------|---------------------------------|-------|---------------------------------|--------|

|                                      | Min                             | Max   | Min                             | Max    |

| А                                    | 0.165                           | 0.180 | 4.191                           | 4.572  |

| A1                                   | 0.090                           | 0.120 | 2.286                           | 3.048  |

| A2                                   | 0.062                           | 0.083 | 1.575                           | 2.108  |

| В                                    | .050 BSC <sup>1</sup> (nominal) |       | 1.27 BSC <sup>1</sup> (nominal) |        |

| С                                    | 0.026                           | 0.032 | 0.660                           | 0.813  |

| D                                    | 0.485                           | 0.495 | 12.319                          | 12.573 |

| D1                                   | 0.450                           | 0.456 | 11.430                          | 11.582 |

| F                                    | 0.013                           | 0.021 | 0.330                           | 0.533  |

| 1. BSC—Basic Spacing between Centers |                                 |       |                                 |        |