#### Dual T1/E1 Line Interface Unit

#### **Datasheet**

The LXT331 is a Dual Line Interface Unit (DLIU) optimized for North America 1.544 Mbps (T1) and international 2.048 Mbps (E1/CEPT) applications. It features a constant low output impedance transmitter for high return loss. Transmit pulse shape is selectable for various line lengths and cable types. The data recovery circuit also offers selectable slicer ratios for T1 or E1 applications.

The LXT331 offers both a serial interface (SIO) for microprocessor control and a hardware control mode for stand-alone operation.

The LXT331 offers a variety of advanced diagnostic and performance monitoring features. It uses an advanced double-poly, double-metal CMOS process and requires only a single 5-volt power supply.

### **Applications**

- Digital Access and Cross-connect Systems (DACS)

- T1/E1 Multiplexer

- SONET/SDH Multiplexers

- Digital Loop Carrier (DLC) terminals

- Cost efficient AFE for Digital Backend ASICS

- Analog LOS using PMRK/NMRK

### **Product Features**

- Complete line driver and data recovery functions

- Constant low output impedance transmitter with a programmable equalizer that shapes pulses to meet the DSX-1 pulse template from 0 to 655 ft.

- High transmit and receive return loss

- Meets or exceeds industry specifications including ITU G.703 and ANSI T1. 102-1993

- Compatible with industry standard framers

- Minimum receive signal of 500 mV, with selectable slicer levels (E1/DSX-1) to improve SNR

- Analog loopback function

- Transmit performance monitors with Driver Fail Monitor (DFM) output for transmit driver short circuit detection

- Transmit Driver Performance Monitor (DPM) output on external pins MTIP and MRING

- Available in 44-pin PLCC and 44-pin QFP packages

Order Number: 249074-001

January 2001

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The LXT331 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Third-party brands and names are the property of their respective owners.

| 1.0 | Pin A                  | Assignments & Signal Descriptions             | 6  |  |  |  |

|-----|------------------------|-----------------------------------------------|----|--|--|--|

| 2.0 | Functional Description |                                               |    |  |  |  |

|     | 2.1                    | Receiver                                      | 10 |  |  |  |

|     | 2.2                    | Transmitter                                   | 10 |  |  |  |

|     |                        | 2.2.1 Pulse Shape                             | 11 |  |  |  |

|     |                        | 2.2.2 Driver Performance Monitor              | 11 |  |  |  |

|     |                        | 2.2.3 Driver Failure Monitor                  | 12 |  |  |  |

|     | 2.3                    | Control Modes                                 | 12 |  |  |  |

|     |                        | 2.3.1 Host Mode Control                       | 13 |  |  |  |

|     |                        | 2.3.1.1 Serial Input Word                     | 13 |  |  |  |

|     |                        | 2.3.1.2 Serial Output Word                    |    |  |  |  |

|     |                        | 2.3.1.3 Interrupt Handling                    |    |  |  |  |

|     |                        | 2.3.2 Hardware Mode Control                   | 14 |  |  |  |

|     | 2.4                    | Diagnostic Mode Operation                     | 18 |  |  |  |

|     | 2.5                    | Initialization & Reset                        | 19 |  |  |  |

| 3.0 | App                    | lication Information                          | 20 |  |  |  |

|     | 3.1                    | Power Requirements                            | 20 |  |  |  |

|     |                        | 3.1.1 Line Interface Requirements             |    |  |  |  |

|     | 3.2                    | Line Protection                               | 21 |  |  |  |

|     |                        | 3.2.1 1.544 Mbps T1 Applications              | 21 |  |  |  |

|     |                        | 3.2.2 2.048 Mbps E1 Coax Applications         |    |  |  |  |

|     |                        | 3.2.3 2.048 Mbps E1 Twisted-Pair Applications |    |  |  |  |

| 4.0 | Test                   | t Specifications                              | 25 |  |  |  |

| 5.0 | Mec                    | hanical Specifications                        | 30 |  |  |  |

| _ |   | - | $\hat{}$ |   |

|---|---|---|----------|---|

|   |   |   | -        | - |

|   | • |   | •        | • |

|   |   |   |          |   |

**Tables**

| 1  | LXT331 Block Diagram                                                       | 5  |

|----|----------------------------------------------------------------------------|----|

| 2  | LXT331 44 Pin Assignments and Markings                                     | 6  |

| 3  | 50% AMI Coding                                                             | 11 |

| 4  | LXT331 Driver Performance Monitor                                          |    |

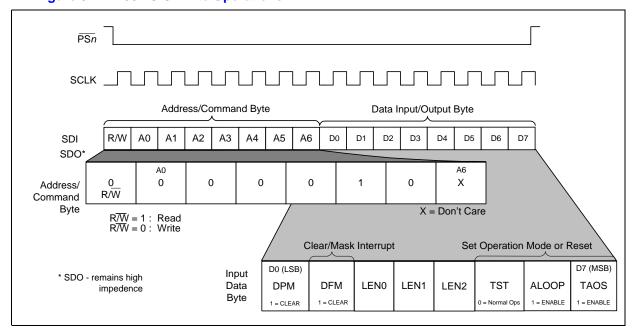

| 5  | LXT331 SIO Write Operations                                                |    |

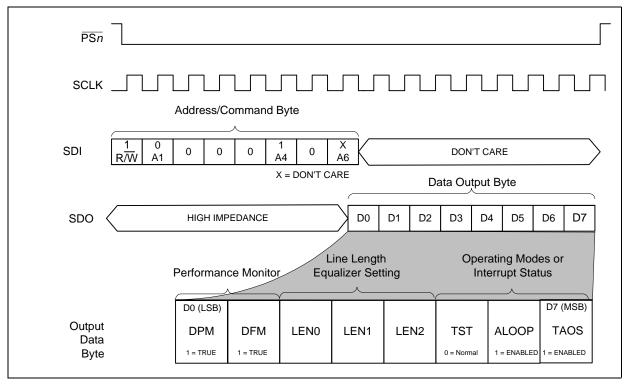

| 6  | LXT331 SIO Read Operation                                                  |    |

| 7  | LXT331 Interrupt Handling                                                  |    |

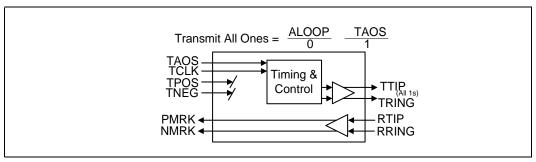

| 8  | Transmit All Ones Data Path                                                |    |

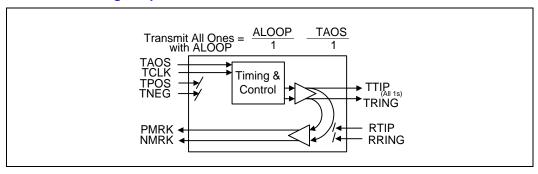

| 9  | TAOS with Analog Loopback                                                  |    |

| 10 | Analog Loopback                                                            |    |

| 11 | Line Interface for E1 Coax                                                 |    |

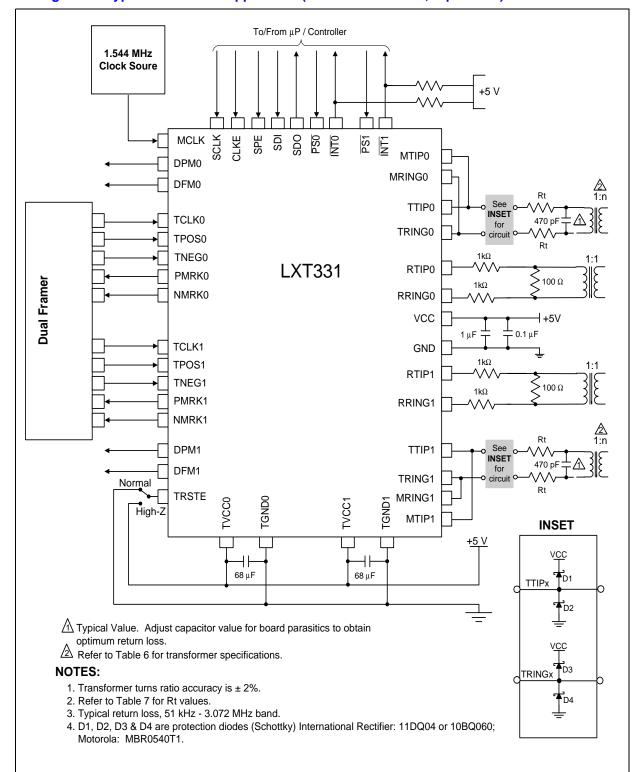

| 12 | Typical LXT331 T1 Application (Host Control Mode, Bipolar I/O)             |    |

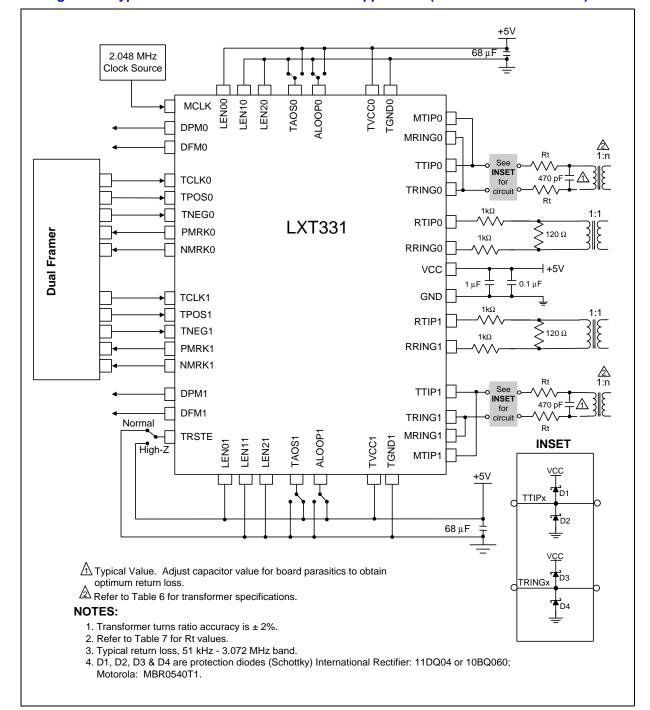

| 13 | Typical LXT331 E1 120 W Twisted Pair Application (Hardware Control Mode) . |    |

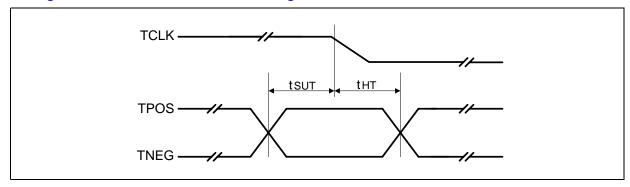

| 14 | LXT331 Transmit Clock Timing                                               |    |

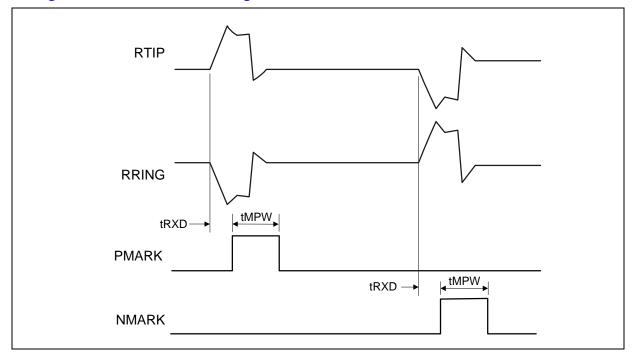

| 15 | LXT331 Receive Timing                                                      |    |

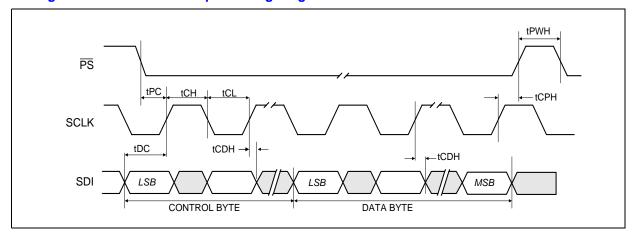

| 16 | LXT331 Serial Input Timing Diagram                                         |    |

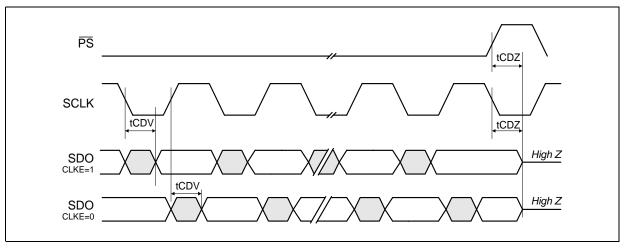

| 17 | LXT331 Serial Output Timing Diagram                                        |    |

| 18 | LXT331 PLCC Package Specification                                          |    |

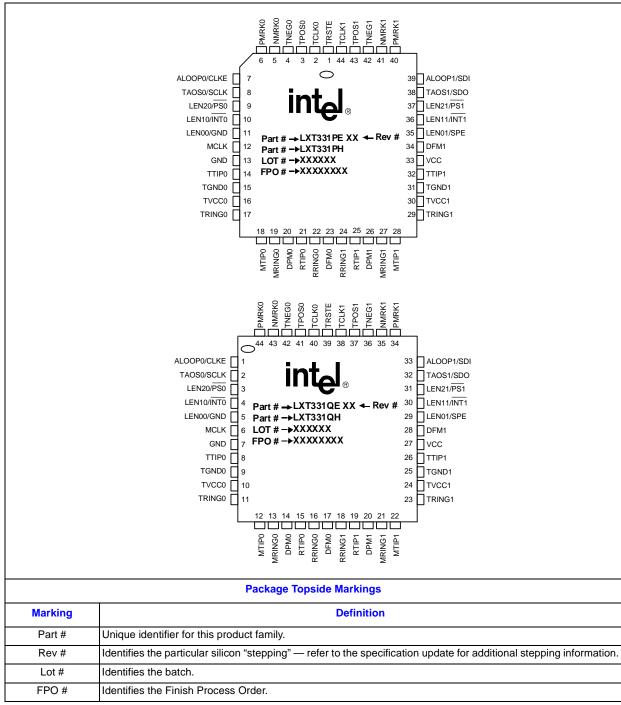

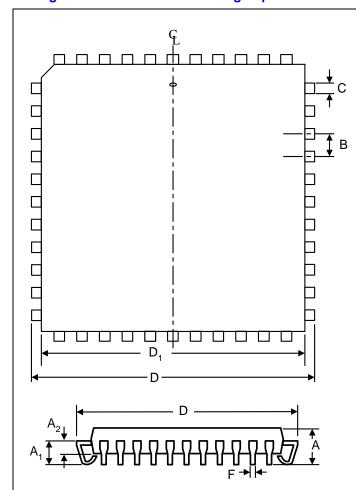

| 19 | LXT331 QFP Package Specification                                           | 31 |

| 1  | Pin Descriptions                                                           | 7  |

| 2  | Equalizer Control Inputs - Hardware Mode1                                  |    |

| 3  | SIO Input Bit Settings (See Figure 5)                                      |    |

| 4  | LXT331 Serial Data Output Bit Coding                                       |    |

| 5  | Hardware Mode Diagnostic Selection                                         |    |

| 6  | Recommended Transmit Transformer Values                                    |    |

| 7  | Transmit Transformer Combinations                                          |    |

| 8  | Absolute Maximum Ratings                                                   |    |

| 9  | Recommended Operating Conditions                                           |    |

| 10 | Electrical Characteristics (Over Recommended Operating Range)              |    |

| 11 | Analog Specifications (Over Recommended Operating Range)                   |    |

| 12 | LXT331 Master Clock and Transmit Timing Characteristics (See Figure 14)    |    |

| 13 | LXT331 Receive Characteristics (See Figure 15)                             |    |

| 14 | LXT331 Serial I/O Timing Characteristics (See Figure 16 and Figure 17)     |    |

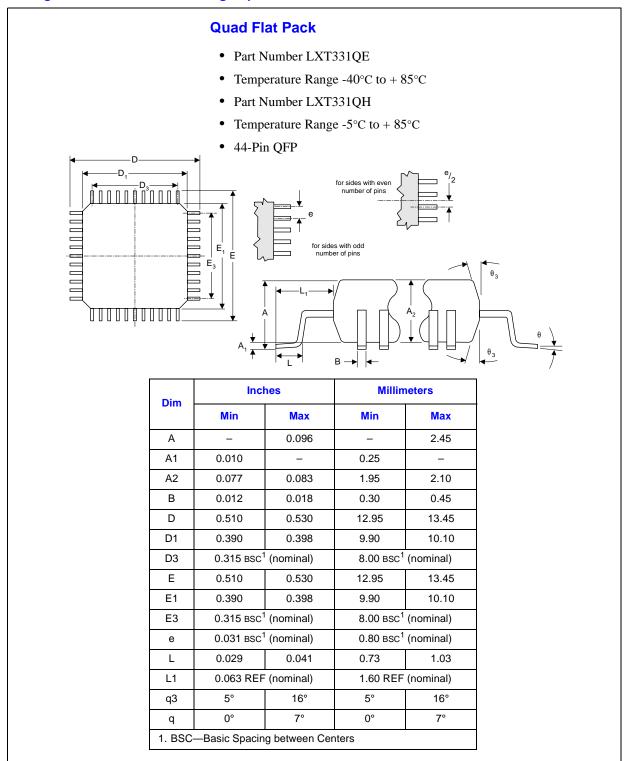

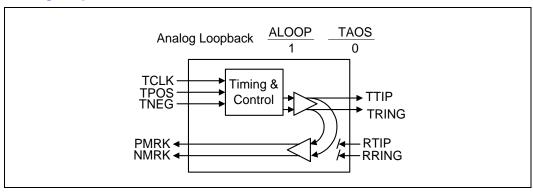

Figure 1. LXT331 Block Diagram

# 1.0 Pin Assignments & Signal Descriptions

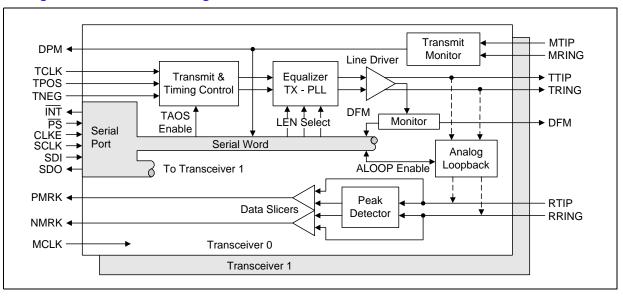

Figure 2. LXT331 44 Pin Assignments and Markings

**Table 1. Pin Descriptions**

| reset mode. Holds reset mode for 6 μs after TRSTE returns Low.  TCLK0  DI  TRANSMIT Clock — Port 0. 1.544 MHz for T1, 2.048 MHz for E1. The transmit data inputs are sampled on the falling edge of TCLK. If TCLK is pulled Low, the transmit drivers are powered down and TTIP and TRING transmit outputs go to a high impedance state.  TPOS0 TNEG0  DI  Transmit Positive and Negative Data, Port 0. These pins drive the positive and negative sides of the bipolar input pair for port 0. Data to be transmitted onto the line is input at these pins.  Receive Negative and Positive Marks, Port 0. These pins are the data outputs from port 0. A signal on PMRK corresponds to receipt of a negative pulse on RTIP/RRING. A signal on PMRK corresponds to receipt of a positive pulse on RTIP/RRING. NMRK PMRK outputs are Return-to-Zero (RZ).  CLKE  DI  Clock Edge Select (Host mode). When CLKE is High, SDO is valid on the rising edge of SCLK. When CLKE is Low, SDO is valid on the falling edge of SCLK.  Alalog Local Loopback Enable, Port 0 (Hardware mode). When ALOOP is High, the RTIP/RRING inputs from the port 0 twisted-pair line are disconnected and the transmit data outputs (TTIP/TRING) are routed back into the receiver. For normal operation, hold ALOOP Low.  SCLK  DI  Serial Clock (Host mode). Shifts data into or out of the serial interface register of the selected port.  Transmit All Ones Enable, Port 0 (Hardware mode). When TAOS is High, the TPOS/TNEG input is ignored and the selected port transmits a stream of ones at the TPOS/TNEG input is ignored and the selected port transmits as stream of ones at the TPOS/TNEG input is ignored and the selected port transmits as stream of ones at the TPOS/TNEG input is ignored and the selected port transmits as stream of ones at the TPOS/TNEG input is ignored and the selected port transmits as stream of ones at the TPOS/TNEG input is ignored and the selected port transmits as stream of ones at the TPOS/TNEG input is ignored and the selected port transmits as stream of ones at the TPOS/TNEG input is | Pin<br>PLCC | Pin<br>QFP | Symbol | I/O <sup>1</sup> | Description                                                                                                                                                                                                                                                                                |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|--------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TCLK0   DI   Inputs are sampled on the falling edge of TCLK. If TCLK is pulled Low, the transmit diverse are powered down and TTIP and TRING transmit outputs go to a high impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1           | 39         | TRSTE  | DI               | <b>Tristate Enable</b> . Forces all output pins to tri-state when held High and forces chip into reset mode. Holds reset mode for 6 $\mu$ s after TRSTE returns Low.                                                                                                                       |  |  |

| 4 42 TNEG0   DI   is input at these pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2           | 40         | TCLK0  | DI               | inputs are sampled on the falling edge of TCLK. If TCLK is pulled Low, the transmit drivers are powered down and TTIP and TRING transmit outputs go to a high                                                                                                                              |  |  |

| Social Clock (Host mode). Shifts data into or out of the serial interface register of the selected port. Transmit All Ones Enable, Port 0 (Hardware mode). When TAOS is High, the TCLK frequency. With no TCLK, the MCLK input becomes the transmit reference. For normal operation, hold ALOOP (Inc.) and inc. FSO must transmit set search read or write operation, PSO must transmit on Dol Enable. Port 0 (Hardware mode). When TAOS is High, the TCLK frequency. With no TCLK, the MCLK input becomes the transmit reference. For normal operation, but ADOS is possible to the selected port.    PSO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |            |        |                  | negative sides of the bipolar input pair for port 0. Data to be transmitted onto the line                                                                                                                                                                                                  |  |  |

| Port Select, Port 0 (Hardware mode). When TAOS is High, the TPOS/TNEG input is ignored and the selected port transmit as stream of ones at the TPOS/TNEG input is ignored and the selected port transmit of TAOS and TENERGY. Port 0 (Hardware mode). When ALOOP is High, the RTIP/RRING inputs from the port 0 twisted-pair line are disconnected and the transmit data outputs (TTIP/TRING) are routed back into the receiver. For normal operation, hold ALOOP Low.    SCILK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |            |        |                  | Receive Negative and Positive Marks, Port 0. These pins are the data outputs from port 0. A signal on NMRK corresponds to receipt of a negative pulse on RTIP/RRING. A signal on PMRK corresponds to receipt of a positive pulse on RTIP/RRING. NMRK/PMRK outputs are Return-to-Zero (RZ). |  |  |

| ALOOPO DI  the RTIP/RRING inputs from the port 0 twisted-pair line are disconnected and the transmit data outputs (TTIP/TRING) are routed back into the receiver. For normal operation, hold ALOOP Low.  SCLK DI  Serial Clock (Host mode). Shifts data into or out of the serial interface register of the selected port.  TAOSO DI  TRANSI All Ones Enable, Port 0 (Hardware mode). When TAOS is High, the TPOS/TNEG input is ignored and the selected port transmits a stream of ones at the TCLK frequency. With no TCLK, the MCLK input becomes the transmit reference. For normal operation, hold TAOS Low. Refer to page 18.  PSO DI  Port Select, Port 0 (Host mode). Selects the serial interface registers of Port 0. For each read or write operation, PSO must transition from High to Low, and remain Low.  LEN20 DI  Line Length Equalizer 2, Port 0 (Hardware mode). Determines the shape and amplitude of the transmit pulse. Refer to Table 2 on page 12  Interrupt, Port 0 (Host mode). Goes Low to flag the host processor that Port 0 has changed state. INTO is an open drain output and must be tied to VCC through a resistor.  GND DI  Line Length Equalizer 1, Port 0 (Hardware mode). Determines the shape and amplitude of the transmit pulse. Refer to Table 2 on page 12  LEN00 DI  LEN00 DI  Line Length Equalizer 0, Port 0 (Hardware mode). Determines the shape and amplitude of the transmit pulse. Refer to Table 2 on page 12  LEN00 DI  Master Clock. 1.544 MHz for T1, 2.048 MHz for E1. Can be held Low if TCLK is present.  Master Clock. 1.544 MHz for T1, 2.048 MHz for E1. Can be held Low if TCLK is designed to drive a 35-200 \( \text{Q} \) Dools and Line matching resistors and transformers can be selected to give the desired pulse height.                                                                                                                                                                                                                                                                                                                               |             |            | CLKE   | DI               |                                                                                                                                                                                                                                                                                            |  |  |

| Selected port.   Selected port.   Selected port.   Selected port   Selected port transmits a stream of ones at the TPOS/TNEG input is ignored and the selected port transmits a stream of ones at the TPOS/TNEG input is ignored and the selected port transmits a stream of ones at the TPOS/TNEG input is ignored and the selected port transmits a stream of ones at the TPOS/TNEG input is ignored and the selected port transmits a stream of ones at the TPOS/TNEG input is ignored and the selected port transmits a stream of ones at the TPOS/TNEG input is ignored and the selected port transmits a stream of ones at the TPOS/TNEG input is ignored and the selected port transmit reference. For normal operation, hold TAOS Low. Refer to page 18.      PSO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7 1         | 1          | ALOOP0 | DI               | the RTIP/RRING inputs from the port 0 twisted-pair line are disconnected and the transmit data outputs (TTIP/TRING) are routed back into the receiver. For normal                                                                                                                          |  |  |

| TAOSO  DI  TPOS/TNEG input is ignored and the selected port transmits a stream of ones at the TCLK frequency. With no TCLK, the MCLK input becomes the transmit reference. For normal operation, hold TAOS Low. Refer to page 18.  DI  Port Select, Port 0 (Host mode). Selects the serial interface registers of Port 0. For each read or write operation, PSO must transition from High to Low, and remain Low.  Line Length Equalizer 2, Port 0 (Hardware mode). Determines the shape and amplitude of the transmit pulse. Refer to Table 2 on page 12  INTO  DO  Interrupt, Port 0 (Host mode). Goes Low to flag the host processor that Port 0 has changed state. INTO is an open drain output and must be tied to VCC through a resistor.  LEN10  DI  Line Length Equalizer 1, Port 0 (Hardware mode). Determines the shape and amplitude of the transmit pulse. Refer to Table 2 on page 12  GND  DI  Unused (Host mode). Must be tied to Ground.  LEN00  DI  LEN00  DI  Line Length Equalizer 0, Port 0 (Hardware mode). Determines the shape and amplitude of the transmit pulse. Refer to Table 2 on page 12  Master Clock. 1.544 MHz for T1, 2.048 MHz for E1. Can be held Low if TCLK is present.  Master Clock. 1.544 MHz for T1, 2.048 MHz for E1. Can be held Low if TCLK is present.  Transmit Tip, Port 0. The TTIP and TRING pins are differential driver outputs designed to drive a 35-200 Ω load. Line matching resistors and transformers can be selected to give the desired pulse height.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |            | SCLK   | DI               | <b>Serial Clock (Host mode)</b> . Shifts data into or out of the serial interface register of the selected port.                                                                                                                                                                           |  |  |

| PSU   DI   each read or write operation, PS0 must transition from High to Low, and remain Low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8 2         | 2          | TAOS0  | DI               | TPOS/TNEG input is ignored and the selected port transmits a stream of ones at the TCLK frequency. With no TCLK, the MCLK input becomes the transmit reference. For                                                                                                                        |  |  |

| LEN20   DI   Line Length Equalizer 2, Port 0 (Hardware mode). Determines the shape and amplitude of the transmit pulse. Refer to Table 2 on page 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0           | 2          | PS0    | DI               | <b>Port Select, Port 0</b> ( <i>Host mode</i> ). Selects the serial interface registers of Port 0. For each read or write operation, PS0 must transition from High to Low, and remain Low.                                                                                                 |  |  |

| 10 4 INTO DO changed state. INTO is an open drain output and must be fied to VCC through a resistor.  LEN10 DI Line Length Equalizer 1, Port 0 (Hardware mode). Determines the shape and amplitude of the transmit pulse. Refer to Table 2 on page 12  GND DI Unused (Host mode). Must be fied to Ground.  LEN00 DI Line Length Equalizer 0, Port 0 (Hardware mode). Determines the shape and amplitude of the transmit pulse. Refer to Table 2 on page 12  MCLK DI Master Clock. 1.544 MHz for T1, 2.048 MHz for E1. Can be held Low if TCLK is present.  Transmit Tip, Port 0. The TTIP and TRING pins are differential driver outputs designed to drive a 35-200 Ω load. Line matching resistors and transformers can be selected to give the desired pulse height.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9           | 3          | LEN20  | DI               |                                                                                                                                                                                                                                                                                            |  |  |

| amplitude of the transmit pulse. Refer to Table 2 on page 12  GND DI Unused (Host mode). Must be tied to Ground.  LEN00 DI Line Length Equalizer 0, Port 0 (Hardware mode). Determines the shape and amplitude of the transmit pulse. Refer to Table 2 on page 12  Master Clock. 1.544 MHz for T1, 2.048 MHz for E1. Can be held Low if TCLK is present.  GROD S Ground. Ground return for VCC power supply.  Transmit Tip, Port 0. The TTIP and TRING pins are differential driver outputs designed to drive a 35-200 Ω load. Line matching resistors and transformers can be selected to give the desired pulse height.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10          | 4          | ĪNT0   | DO               | changed state. INTO is an open drain output and must be tied to VCC through a                                                                                                                                                                                                              |  |  |

| 11 5 LEN00 DI Line Length Equalizer 0, Port 0 (Hardware mode). Determines the shape and amplitude of the transmit pulse. Refer to Table 2 on page 12  12 6 MCLK DI Master Clock. 1.544 MHz for T1, 2.048 MHz for E1. Can be held Low if TCLK is present.  13 7 GND S Ground. Ground return for VCC power supply.  14 8 TTIPO AO Transmit Tip, Port 0. The TTIP and TRING pins are differential driver outputs designed to drive a 35-200 Ω load. Line matching resistors and transformers can be selected to give the desired pulse height.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |            | LEN10  | DI               |                                                                                                                                                                                                                                                                                            |  |  |

| LEN00 DI CHRISTIAN AO LEGISTIA ENGLY. Determines the shape and amplitude of the transmit pulse. Refer to Table 2 on page 12  12 6 MCLK DI Master Clock. 1.544 MHz for T1, 2.048 MHz for E1. Can be held Low if TCLK is present.  13 7 GND S Ground. Ground return for VCC power supply.  14 8 TTIPO AO Transmit Tip, Port 0. The TTIP and TRING pins are differential driver outputs designed to drive a 35-200 Ω load. Line matching resistors and transformers can be selected to give the desired pulse height.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |            | GND    | DI               | Unused (Host mode). Must be tied to Ground.                                                                                                                                                                                                                                                |  |  |

| present.  GND S Ground. Ground return for VCC power supply.  Transmit Tip, Port 0. The TTIP and TRING pins are differential driver outputs designed to drive a 35-200 Ω load. Line matching resistors and transformers can be selected to give the desired pulse height.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11          | 5          | LEN00  | DI               |                                                                                                                                                                                                                                                                                            |  |  |

| Transmit Tip, Port 0. The TTIP and TRING pins are differential driver outputs designed to drive a 35-200 Ω load. Line matching resistors and transformers can be selected to give the desired pulse height.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12          | 6          | MCLK   | DI               | ·                                                                                                                                                                                                                                                                                          |  |  |

| 14 8 TTIP0 AO designed to drive a 35-200 Ω load. Line matching resistors and transformers can be selected to give the desired pulse height.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13          | 7          | GND    | S                | Ground. Ground return for VCC power supply.                                                                                                                                                                                                                                                |  |  |

| 15 9 TGND0 S <b>Ground, Port 0 Transmit Driver.</b> Ground return for TVCC0 power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 14          | 8          | TTIP0  | АО               | designed to drive a 35-200 $\Omega$ load. Line matching resistors and transformers can be                                                                                                                                                                                                  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15          | 9          | TGND0  | S                | Ground, Port 0 Transmit Driver. Ground return for TVCC0 power supply.                                                                                                                                                                                                                      |  |  |

<sup>1.</sup> DI = Digital Input; DO = Digital Output; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output; S = Power Supply

**Table 1. Pin Descriptions (Continued)**

| Pin<br>PLCC | Pin<br>QFP | Symbol          | I/O <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-------------|------------|-----------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 16          | 10         | TVCC0           | S                | + 5 VDC Power Supply, Port 0 Transmit Driver. TVCC0 must not vary from TVCC or VCC by more than $\pm$ 0.3 V.                                                                                                                                                                                                                                                              |  |  |

| 17          | 11         | TRING0          | АО               | <b>Transmit Ring, Port 0</b> . The TTIP and TRING pins are differential driver outputs designed to drive a 35-200 $\Omega$ load. Line matching resistors and transformers can be selected to give the desired pulse height.                                                                                                                                               |  |  |

| 18<br>19    | 12<br>13   | MTIP0<br>MRING0 | AI<br>AI         | Monitor Tip and Ring, Port 0. These pins monitor tip and ring outputs of either its own, or those of an adjacent LXT331 on the same board. If the application does not use this feature, tie one of these pins to a clock source and the other to a mid-level (referenced to the clock signal) voltage. The clock frequency can range from 100 kHz to the TCLK frequency. |  |  |

| 20          | 14         | DPM0            | DO               | <b>Driver Performance Monitor, Port 0</b> . Goes High to indicate the detection of 63 consecutive zeros. Goes Low upon the receipt of a one on the transmit monitor loop (MTIP/MRING).                                                                                                                                                                                    |  |  |

| 21<br>22    | 15<br>16   | RTIP0<br>RRING0 | AI<br>AI         | Receive Tip and Ring, Port 0. RTIP and RRING comprise the receive line interface This input pair should be connected to the line through a 1:1 transformer.                                                                                                                                                                                                               |  |  |

| 23          | 17         | DFM0            | DO               | Driver Fail Monitor, Port 0. Goes High to indicate a driver output short condition.                                                                                                                                                                                                                                                                                       |  |  |

| 24<br>25    | 18<br>19   | RRING1<br>RTIP1 | AI<br>AI         | Receive Tip and Ring, Port 1. Refer to RRING0 and RTIP0 pins.                                                                                                                                                                                                                                                                                                             |  |  |

| 26          | 20         | DPM1            | DO               | Driver Performance Monitor, Port 1. Refer to DPM0 pin.                                                                                                                                                                                                                                                                                                                    |  |  |

| 27<br>28    | 21<br>22   | MRING1<br>MTIP0 | AI               | Monitor Tip and Ring, Port 1. Refer to MRING0 and MTIP0 pins.                                                                                                                                                                                                                                                                                                             |  |  |

| 29          | 23         | TRING1          | AO               | Transmit Ring, Port 1. Refer to TRING0 pin.                                                                                                                                                                                                                                                                                                                               |  |  |

| 30          | 24         | TVCC1           | S                | + 5 VDC Power Supply, Port 1 Transmit Driver. TVCC1 must not deviate from TVCC0 or VCC by more than ± 0.3 V.                                                                                                                                                                                                                                                              |  |  |

| 31          | 25         | TGND1           | S                | Ground, Port 1 Transmit Driver. Ground return for TVCC1 power supply.                                                                                                                                                                                                                                                                                                     |  |  |

| 32          | 26         | TTIP1           | AO               | Transmit Tip, Port 1. Refer to TTIP0 pin.                                                                                                                                                                                                                                                                                                                                 |  |  |

| 33          | 27         | VCC             | S                | + 5 VDC Power Supply Input for All Circuits Except Transmit Drivers.                                                                                                                                                                                                                                                                                                      |  |  |

| 34          | 28         | DFM1            | DO               | Driver Fail Monitor, Port 1. Refer to DFM0 pin.                                                                                                                                                                                                                                                                                                                           |  |  |

| 35          | 29         | SPE             | DI               | <b>Serial Port Enable (Host mode)</b> . SPE must be clocked with MCLK, TCLK0 or TCLK1 to enable Host mode control through the serial port.                                                                                                                                                                                                                                |  |  |

| 00          | 20         | LEN01           | DI               | <b>Line Length Equalizer 0, Port 1 (Hardware mode).</b> Determines the shape and amplitude of the transmit pulse. Refer to Table 2 on page 12                                                                                                                                                                                                                             |  |  |

|             |            | ĪNT1            | DO               | Interrupt, Port 1 (Host mode). Refer to INTO pin.                                                                                                                                                                                                                                                                                                                         |  |  |

| 36          | 30         | LEN11           | DI               | <b>Line Length Equalizer 1, Port 1 (Hardware mode).</b> Determines the shape and amplitude of the transmit pulse. Refer to Table 2 on page 12                                                                                                                                                                                                                             |  |  |

|             |            | PS1             | DI               | Port Select, Port 1 (Host mode). Refer to PS0 pin.                                                                                                                                                                                                                                                                                                                        |  |  |

| 37          | 31         | LEN21           | DI               | Line Length Equalizer 2, Port 1 (Hardware mode). Determines the shape and amplitude of the transmit pulse. Refer to Table 2 on page 12                                                                                                                                                                                                                                    |  |  |

| 38          | 32         | SDO             | DO               | Serial Data Output (Host mode). Read data from the LXT331 registers are output of this pin. When CLKE is High, SDO is valid on the rising edge of SCLK. When CLKE is Low, SDO is valid on the falling edge of SCLK.                                                                                                                                                       |  |  |

|             |            | TAOS1           | DI               | Transmit All Ones Enable, Port 1 (Hardware mode). Refer to TAOS0 pin.                                                                                                                                                                                                                                                                                                     |  |  |

DI = Digital Input; DO = Digital Output; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output; S = Power Supply

Table 1. Pin Descriptions (Continued)

| Pin<br>PLCC | Pin<br>QFP  | Symbol       | I/O <sup>1</sup> | Description                                                                                                                                |

|-------------|-------------|--------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 39          | 33          | SDI          | DI               | <b>Serial Data Input (Host mode).</b> Write data to the LXT331 registers are input on this pin. SDI is sampled on the rising edge of SCLK. |

|             |             | ALOOP1 I     |                  | Analog Local Loopback Enable, Port 1 (Hardware mode). Refer to pin ALOOP0.                                                                 |

| 40          | 34          | PMRK1        | DO               | Receive Negative and Positive Marks, Port 1. Refer to PMRK0 and NMRK0 pins.                                                                |

| 41          | 35          | NMRK1        | DO               | receive negative and Positive Marks, Port 1. Relei to Pivirko and Nivirko pins.                                                            |

| 42          | 36          | TNEG1        | DI               | Transmit Negative and Besitive Data Bort 1. Befor to TNECO and TDOSO pins                                                                  |

| 43          | 37          | TPOS1        | DI               | Transmit Negative and Positive Data, Port 1. Refer to TNEG0 and TPOS0 pins.                                                                |

| 44          | 38          | TCLK1        | DI               | Transmit Clock, Port 1. Refer to TCLK0 pin.                                                                                                |

| 1 DI – D    | igital Innu | t: DO - Digi | tal Outni        | it: DI/O = Digital Input/Output: AI = Analog Input: AO = Analog Output: S = Power                                                          |

DI = Digital Input; DO = Digital Output; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output; S = Power Supply

### 2.0 Functional Description

The LXT331 is a Dual Line Interface Unit (DLIU), which contains two ports. Refer to the simplified block diagram on page 1. The DLIU is designed for both 1.544 Mbps (DSX-1) and 2.048 Mbps (E1) applications. Both ports operate at the same frequency, which is determined by the TCLK input.

Each port's front end interfaces with two lines, one line for transmit, one line for receive. These two lines comprise a digital data loop for full-duplex transmission. Each port's back-end interfaces with a layer processor through bipolar data I/O channels.

The DLIU may either be controlled by a microprocessor via the serial port (Host mode), or by hardwired pins for stand-alone operation (Hardware mode).

#### 2.1 Receiver

The two receivers in the LXT331 DLIU are identical. The following paragraphs describe the operation of a single receiver.

The input signal is received via a 1:1 transformer. The receiver requires fully differential inputs which are internally self-biased into 2.5 V. Recovered data is output at PMRK and NMRK. Refer to Test Specifications for receiver timing.

The receive signal is processed through an adaptive peak detector and data slicers. The peak detector samples the received signal and determines its maximum value. A percentage of the peak value is provided to the data slicers as a threshold level to ensure optimum signal-to-noise ratio. For DSX-1 applications (line length inputs LEN0-LEN2  $\neq$  000 or 001), the threshold is set to 70% (typical) of the peak value.

This threshold is maintained above the specified level for up to 15 successive zeros over the range of specified operating conditions. For E1 applications (LEN0-LEN2 = 000 or 001) the threshold is 50% (typical).

The receiver is capable of accurately recovering signals with up to +13.6 dB of attenuation (from 2.4 V), corresponding to a received signal level of approximately 500 mV. Maximum line length is 1500 feet of ABAM cable (approximately 6 dB of attenuation). Regardless of received signal level, the peak detectors are held above a minimum level of 0.3 V (typical) to provide immunity from impulsive noise. Built in pulse stretching circuitry maintains a minimum positive and negative mark pulse width (see Table 13 and Figure 15 on page 28).

#### 2.2 Transmitter

The two transmitters in the LXT331 DLIU are identical. The following paragraphs describe the operation of a single transmitter.

Transmit data is clocked serially into the device at TPOS/TNEG. Input synchronization is supplied by the transmit clock (TCLK). The TPOS/TNEG inputs are sampled on the falling edge of TCLK. If TCLK is held Low, the transmitter remains powered down and the TTIP/TRING outputs are held in a high-Z state (except in TAOS mode if MCLK is available). Each output driver is provided with

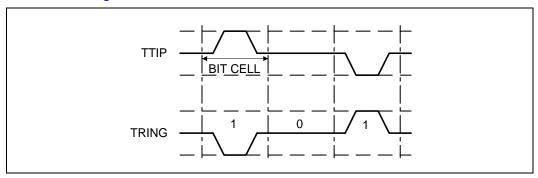

a separate power supply pin (TVCC0 or TVCC1). Current limiters on the output drivers provide short circuit protection. Refer to Test Specifications for TCLK timing characteristics. As shown in Figure 3, the LXT331 encodes transmit data using 50% Alternate Mark Inversion (AMI) line code.

Figure 3. 50% AMI Coding

#### 2.2.1 Pulse Shape

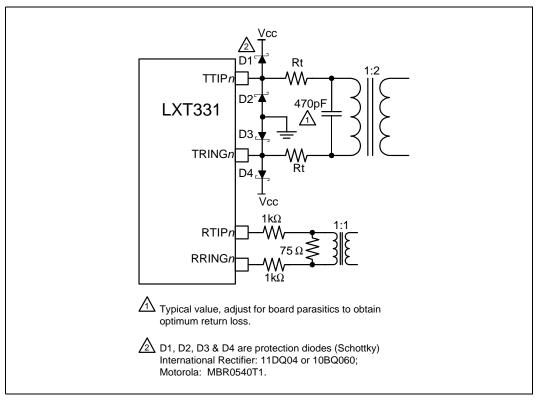

The transmitted pulse shape is determined by Line Length equalizer control signals LEN0 through LEN2. Equalizer codes are hard-wired in Hardware mode as shown in Table 2. In Host mode, the LEN control codes are input through the serial interface. Shaped pulses are applied to the AMI line driver for transmission onto the line at TTIP and TRING. The line driver provides a constant Low output impedance of  $< 3~\Omega$  (typical) regardless of whether it is driving marks or spaces or during transitions. This well-controlled impedance provides excellent return loss when used with external precision resistors ( $\pm 1\%$  accuracy). See Table 9 and Table 10 for recommended transformer specifications, turns ratios, series resistor (Rt) values, and typical return losses for various LEN codes. To minimize power consumption the DC blocking capacitor and the LXT331 can be connected directly to a 1:1.15 transformer without series resistors.

Pulses can be shaped for either 1.544 or 2.048 Mbps applications. 1.544 Mbps pulses for DSX-1 applications can be programmed to match line lengths from 0 to 655 feet of 22 AWG ABAM cable. A combination of 9.1  $\Omega$  resistors and a 1:2.3 transformer is recommended for maximum transmit return loss in DSX-1 applications. The LXT331 also matches FCC pulse mask specifications for CSU applications.

The LXT331 produces 2.048 Mbps pulses for both 75  $\Omega$  coaxial (2.37 V) or 120  $\Omega$  shielded twisted-pair (3.0 V) lines through an output transformer with a 1:2 turns ratio.

Refer to the "Application Information" on page 20 for details on interface circuitry.

#### 2.2.2 Driver Performance Monitor

The LXT331 incorporates a Driver Performance Monitor (DPM) as shown in Figure 4 on page 13. The DPM output goes High on receipt of 63 consecutive zeros (at MTIP and MRING) and returns Low on receipt of a transition. A reset command also drives the output signal Low.

The LXT331 uses its MTIP and MRING pins to monitor its own TTIP and TRING outputs or those of an adjacent chip. Mark detection involves two criteria:

1. Voltage threshold: a pulse must trip a threshold voltage above or below (depending on its polarity) the input bias voltage level. The LXT331 bias voltage is 2.5 V and the threshold for a mark is  $2.5 \pm 0.79$  V.

2. Pulse width: the monitor distinguishes between marks and noise pulses by the pulse width. LXT331 requires a mark pulse to be at least 120 ns wide (typical).

As shown in Figure 4 on page 13, there are two type of marks: "A" and "B". C1 and C2 detect "A" marks while the AND gate (A1) ensures that both mark signals are present at the same time. If the pulse widths are adequate, i.e. both a positive mark on MTIP and a negative mark on MRING, the A1 output goes High. Likewise C3 and C4 detect "B" marks. If the pulse meets the minimum width requirement, the AND gate (A2) output goes High when there are both a negative mark on MTIP and a positive mark on MRING. The OR gate (O1) passes the mark, as the signal "zero", on to the clock/counter circuit which controls the DPM output.

A latch samples the counter and goes High if the DPM circuit sees 63 consecutive zeros. Any mark resets the counter. The DPM signal goes High after the 63<sup>rd</sup> zero.

Table 2. Equalizer Control Inputs - Hardware Mode<sup>1</sup>

| LEN2 | LEN1 | LEN0 | Line Length <sup>2</sup> | Cable Loss <sup>3</sup> | Application               | Frequency  |

|------|------|------|--------------------------|-------------------------|---------------------------|------------|

| Low  | High | High | 0 - 133 ft ABAM          | 0.6 dB                  |                           |            |

| High | Low  | Low  | 133-266 ft ABAM          | 1.2 dB                  |                           |            |

| High | Low  | High | 266-399 ft ABAM          | 1.8 dB                  | DSX-1                     | 1.544 MHz  |

| High | High | Low  | 399-533 ft ABAM          | 2.4 dB                  |                           |            |

| High | High | High | 533-655 ft ABAM          | 3.0 dB                  |                           |            |

| Low  | Low  | Low  | ITU Recommend            | dation C 702            | E1 - Coax (75 Ω)          | 2.048 MHz  |

| Low  | Low  | High | 110 Recommend            | Jalion G.703            | E1 - Twisted-pair (120 Ω) | 2.040 NITZ |

| Low  | High | Low  | FCC Part 68,             | Option A                | CSU                       | 1.544 MHz  |

LEN0-2 inputs are shown as High or Low for Hardware mode. For Host mode serial inputs, High = 1 and Low = 0.

#### 2.2.3 Driver Failure Monitor

The transceiver incorporates an internal Driver Failure Monitor (DFM) that observes TTIP and TRING. Driver failure is detected with a capacitor that is charged as a function of driver output current, and discharged as a measure of the maximum allowable current. Shorted lines draw excess current, overcharging the cap. When the capacitor charge deviates outside the nominal charge window, a driver failure is reported. In Host mode the DFM bit is set in the serial word. In both Hardware and Host modes the DFM pin goes High. During a long string of spaces, a short-induced overcharge eventually bleeds off, clearing the DFM flag.